(5) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И АССОЦИАТИВНЫЙ НАКОПИТЕЛЬ ИНФОРМАЦИИ ДЛЯ НЕГО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1978 |

|

SU877616A1 |

| Ассоциативное запоминающее устройство | 1981 |

|

SU978196A1 |

| Ассоциативное запоминающее устройство | 1977 |

|

SU662972A1 |

| Ассоциативное оперативное запоминающее устройство | 1981 |

|

SU978197A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1043750A1 |

| Ассоциативное запоминающее устройство | 1981 |

|

SU976476A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU624296A1 |

1

Изобретение относится к запоминающим устройствам и может быть применено в различных устройствах обработки и преобразования информации для реали-зации ассоциативной записи и воспроизведения информации.

Известно ассоциативное запоминающее устройство,-содержащее входной и выходной регистры, матрицу ассоциативных запоминающих элементов 1. д

Однако это устройство не позволяет использовать его при решении задачи воспроизведения ранее записанной полной информации по ее произвольной части.15

Наиболее близким техническим реше- нием к данному изобретению является ассоциативное запоминл ющее устройство, содержащее матрицу ассоциативных зам20

поминающих элементов, входной и выходной регистры, причем входы и выходы ассоциативных запоминающих элементов соединены соответственно с одноименными выходами входного и входами Виходного регистров случайными равномерно распределенными по всей матрице связями, что позволяет воспроизводить ранее записанную полную информацию по ее произвольной масти 2J,

Однако эффективность работы этого устройства существенно зависит от количества ассоциативных запоминающих элементов, находящихся в матрице.

Для того, чтобы вероятность правильного -восстановления ранее записанной полной информации по ее произвольной части была бы равна единице или близка к ней, требуется значительное число ассоциативных запоминающих элементов, так как принцип работы этого-устройства основан на модели нейронной сети, способной к формированию условных рефлексов .З.

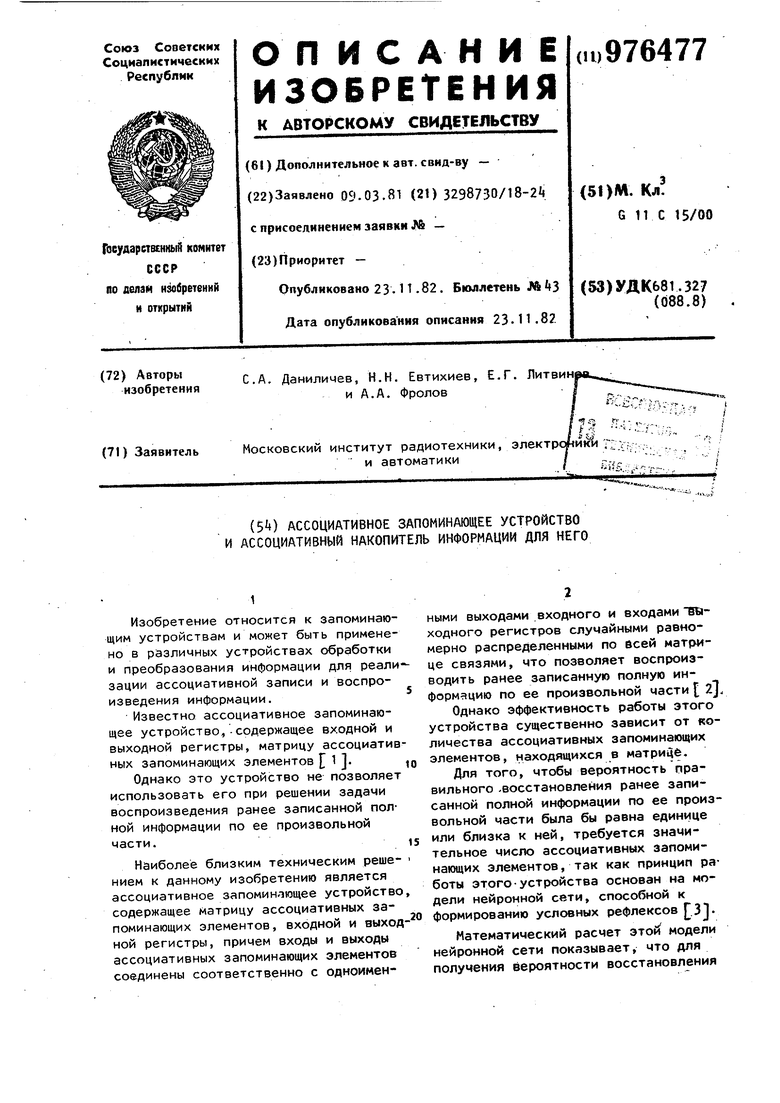

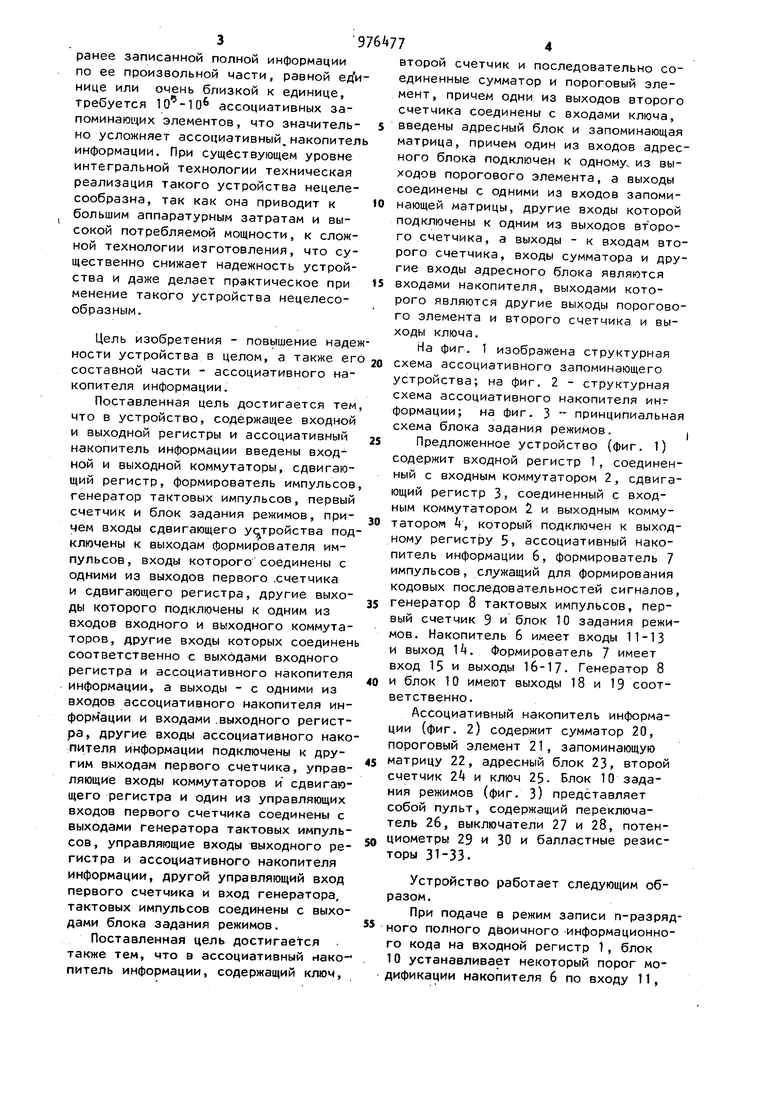

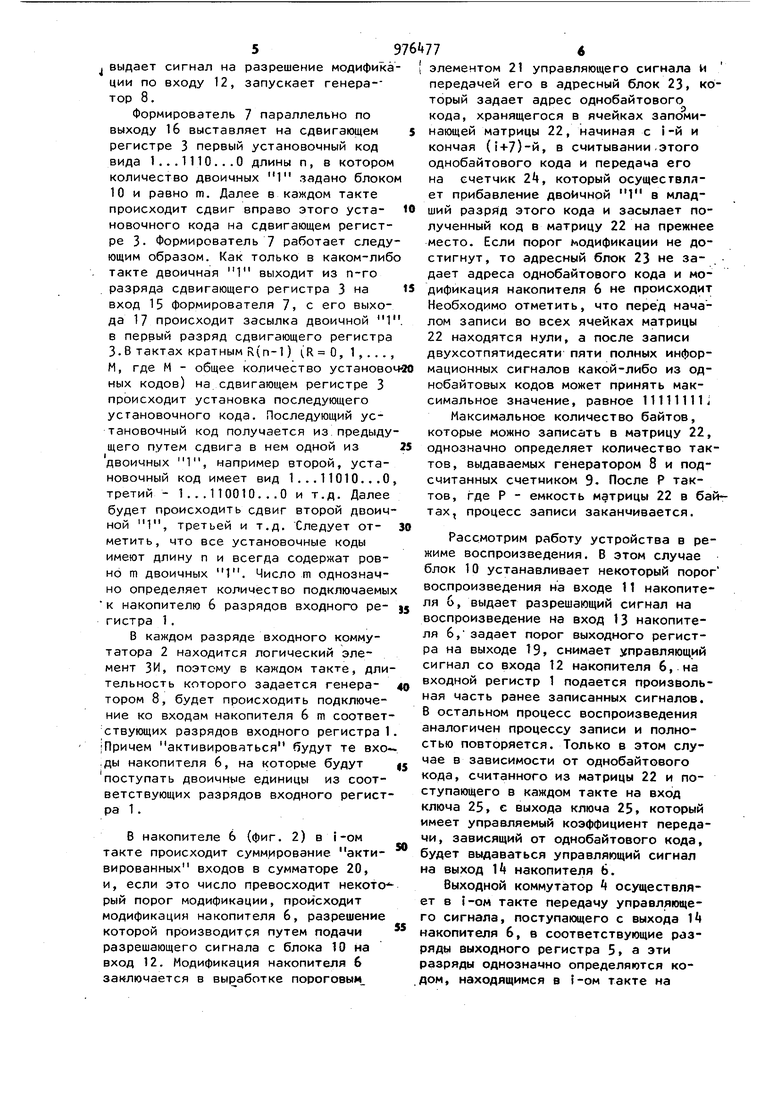

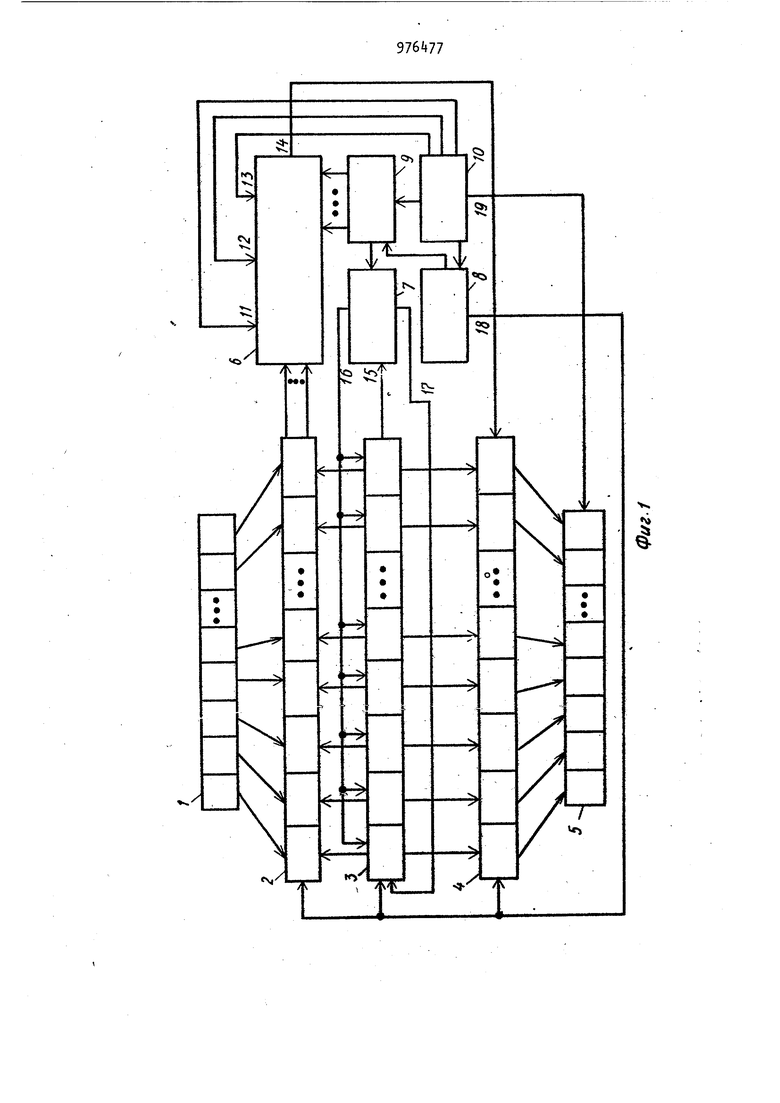

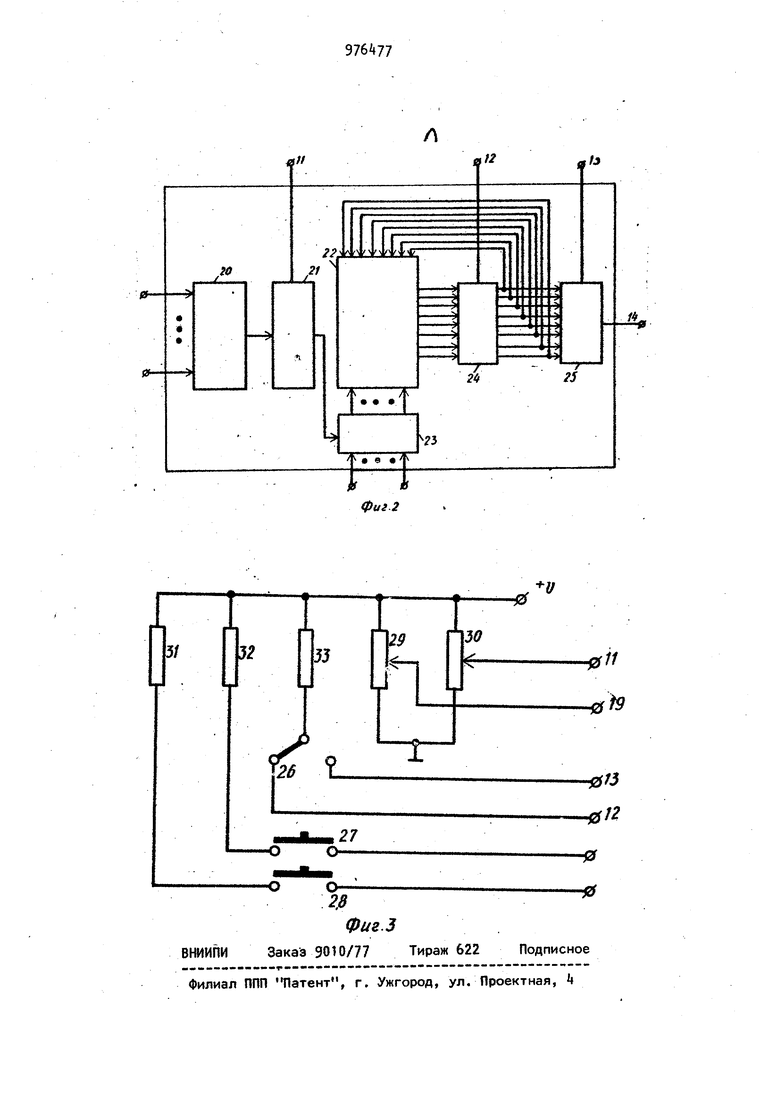

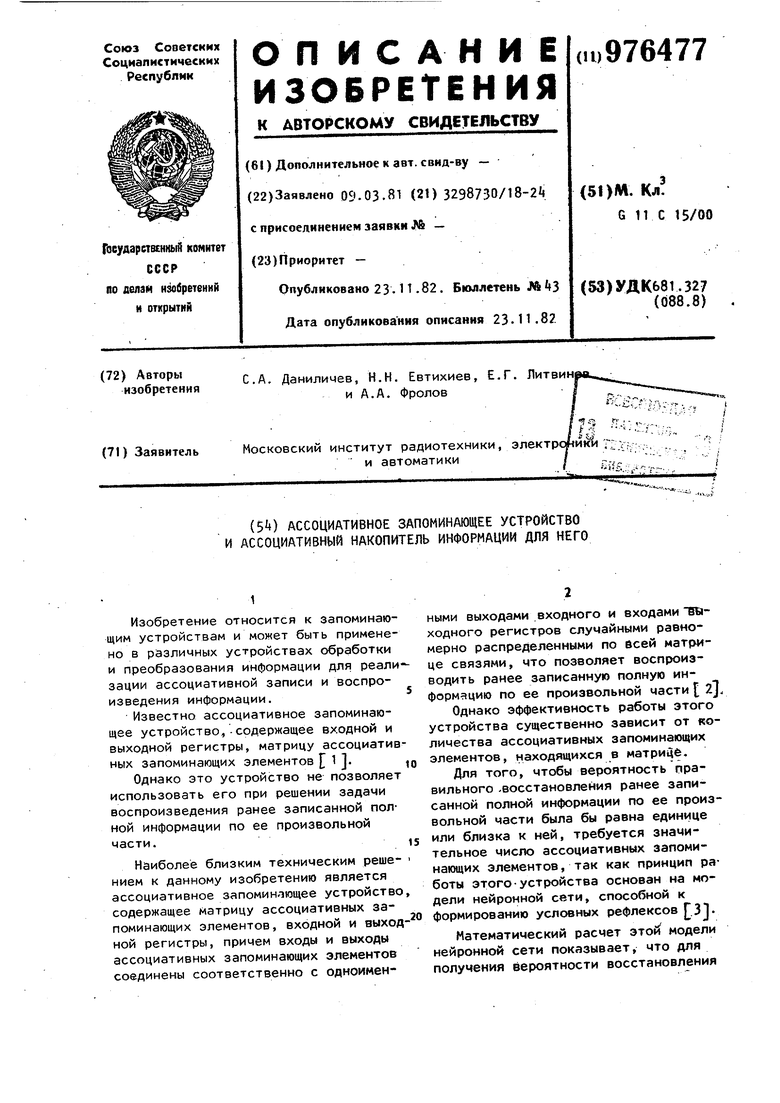

Математический расчет модели нейронной сети показывает, что для получения вероятности восстановления 39 ранее записанной полной информации по ее произвольной части, равной нице или очень близкой к единице, требуется ассоциативных запоминающих элементов, что значительно усложняет ассоциативный.накопител информации. При существующем уровне интегральной технологии техническая реализация такого устройства нецелесообразна, так как она приводит к большим аппаратурным затратам и высокой потребляемой мощности, к сложной технологии изготовления, что существенно снижает надежность устройства и даже делает практическое при менение такого устройства нецелесообразным. Цель изобретения - повьшение наде ности устройства в целом, а также ег составной части - ассоциативного накопителя информации. Поставленная цель достигается тем что в устройство, содержащее входной и выходной регистры и ассоциативный накопитель информации введены входной и выходной коммутаторы, сдвигающий регистр, формирователь импульсов генератор тактовых импульсов, первый счетчик и блок задания режимов, причем входы сдвигающего устройства под ключены к выходам формирователя импульсов , входы которого соединены с одними из выходов первого .счетчика и сдвигающего регистра, другие выходы которого подключены к одним из входов входного и выходного коммутаторов , другие входы которых соединен соответственно с выходами входного регистра и ассоциативного накопителя информации, а выходы - с одними из входов ассоциативного накопителя информации и входами .выходного регистра, другие входы ассоциативного нако пителя информации подключены к другим выходам первого счетчика, управляющие входы коммутаторов и сдвигающего регистра и один из управляющих входов первого счетчика соединены с выходами генератора тактовых импульсов , управляющие входы выходного регистра и ассоциативного накопителя информации, другой управляющий вход первого счетчика и вход генератора, тактовых импульсов соединены с выходами блока задания режимов. Поставленная цель достигается также тем, что в ассоциативный накопитель информации, содержащий ключ. 7 второй счетчик и последовательно соединенные сумматор и пороговый элемент, причем одни из выходов второго счетчика соединены с входами ключа, введены адресный блок и запоминающая матрица, причем один из входов адресного блока подключен к одному, из выходов порогового элемента, а выходы соединены с одними из входов запоминающей матрицы, другие входы которой подключены к одним из выходов второго счетчика, а выходы - к входам второго счетчика, входы сумматора и другие входы адресного блока являются входами накопителя, выходами которого являются другие выходы порогового элемента и второго счетчика и выходы ключа. На фиг. 1 изображена структурная схема ассоциативного запоминающего устройства; на фиг. 2 - структурная схема ассоциативного накопителя инг формации; на фиг. 3 принципиальная схема блока задания режимов. | Предложенное устройство (фиг. 1) содержит входной регистр 1, соединенный с входным коммутатором 2, сдвигающий регистр 3 соединенный с входным коммутатором 2 и выходным коммутатором k, который подключен к выходному регистру 5, ассоциативный накопитель информации 6, формирователь 7 импульсов, служащий для формирования кодовых последовательностей сигналов, генератор 8 тактовых импульсов, первый счетчик 9 и блок 10 задания режимов. Накопитель 6 имеет входы 11-13 и выход Н. Формирователь 7 имеет вход 15 и выходы 16-17. Генератор 8 и блок 10 имеют выходы 18 и 19 соответственно. Ассоциативный накопитель информации (фиг. 2) содержит сумматор 20, пороговый элемент 21, запоминающую матрицу 22, адресный блок 23, второй счетчик 24 и ключ 25. Блок 10 задания режимов (фиг. 3) представляет собой пульт, содержащий переключатель 26, выключатели 27 и 28, потенциометры 29 и 30 и балластные резисторы 31-33. Устройство работает следующим образом. При подаче в режим записи п-разрядного полного двоичного информационного кода на входной регистр 1, блок 10 устанавливает некоторый порог модификации накопителя 6 по входу 11, , выдает сигнал на разрешение модификации по входу 12, запускает генера-тор 8. Формирователь 7 параллельно по выходу 16 выставляет на сдвигающем регистре 3 первый установочный код вида 1 ... 1110... О длины п, в котором количество двоичных 1 задано блоком 10 и равно т. Далее в каждом такте происходит сдвиг вправо этого установочного кода на сдвигающем регистре 3- Формирователь 7 работает следующим образом. Как только в каком-либо такте двоичная 1 выходит из п-го разряда сдвигающего регистра 3 на вход 15 формирователя 7, с его выхода 17 происходит засылка двоичной 1 в первый разряд сдвигающего регистра 3.В тактах кратным R{n-1) (, 1,..., М, где М - общее количество установо ных кодов) на сдвигающем регистре 3 происходит установка последующего установочного кода. Последующий установочный код получается из предыду щего путем сдвига в нем одной из двоичных 1, например второй, установочный код имеет вид 1...11010...О третий - 1 ... 110010...0 и т.д. Далее будет происходить сдвиг второй двоич ной 1, третьей и т.д. Следует отметить, что все установочные коды имеют длину п и всегда содержат ровно m двоичных 1. Число m однозначно определяет количество подключаемы к накопителю 6 разрядов входного регистра 1. В каждом разряде входного коммутатора 2 находится логический элемент ЗИ, поэтому в каждом такте, дли тельность которого задается генератором 8, будет происходить подключение ко входам накопителя 6 m соответ ствующих разрядов входного регистра |Причем активироваться будут те вхо .ды накопителя 6, на которые будут поступать двоичные единицы из соответствующих разрядов входного регист ра 1. В накопителе 6 {фиг. 2) в i-ом такте происходит суммирование активированных входов в сумматоре 20, и, если это число превосходит некото рый порог модификации, происходит модификация накопителя 6, разрешение которой производится путем подачи разрешающего сигнала с блока 10 на вход 12. Модификация накопителя 6 заключается в выработке пороговым. элементом 21 управляющего сигнала И передачей его в адресный блок 23, который задает адрес однобайтового кода, хранящегося в ячейках запоминающей матрицы 22, начиная с i-и и кончая (+7}-й, в считывании-ЭТОГО однобайтового кода и передама его на счетчик 2, который осуществляет прибавление двоичной 1 в младший разряд этого кода и засылает полученный код в матрицу 22 на прежнее место. Если порог модификации не достигнут, то адресный блок 23 не задает адреса однобайтового кода и модификация накопителя 6 не происходит Необходимо отметить, что перед началом записи во всех ячейках матрицы 22 находятся нули, а после записи двухсотпятидесяти пяти полных информационных сигналов какой-либо из однобайтовых кодов может принять максимальное значение, равное 11111111J Максимальное количество байтов, которые можно записать в матрицу 22, однозначно определяет количество тактов, выдаваемых генератором 8 и подсчитанных счетником 9. После Р тактов, где Р - емкость матрицы 22 в бай тах, процесс записи заканчивается. Рассмотрим работу устройства в режиме воспроизведения. В этом случае блок 10 устанавливает некоторый порог воспроизведения на входе 11 накопите выдает разрешающий сигнал на воспроизведение на вход 13 накопителя 6, задает порог выходного регистра на выходе 19, снимает управляющий сигнал со входа 12 накопителя 6, на входной регистр 1 подается произвольная часть ранее записанных сигналов. В остальном процесс воспроизведения аналогичен процессу записи и полностью повторяется. Только в этом случае в зависимости от однобайтового кода, считанного из матрицы 22 и поступающего а каждом такте на вход ключа 25, е выхода ключа 25, который имеет управляемый коэффициент передачи, зависящий от однобайтового кода, будет выдаваться управляющий сигнал на выход И накопителя Ь. Выходной коммутатор i осуществляет в i-oM такте передачу управляющего сигнала, поступающего с выхода 1 накопителя 6, в соответствующие разряды выходного регистра 5, а эти разряды однозначно определяются кодом, находящимся в i-ом такте на 797 сдвигающем регистре 3. образом, в каждом такте входы и выход накопителя 6 оказываются соединенными соответственно с одноименными выходами входного 2 и входами выходного k регистров, а за Р тактов входы и выход накопителя 6 оказываются равномерно распределенными по всей длине входного и выходного регистров. В каждом разряде выходного регист ра 5 происходит последовательное сум мирование в каждом такте управляющих сигналов с выходного коммутатора k, После Р тактов происходит сравнение полученных сумм в каждом разряде с порогом выходного регистра блоком 10 Если порог достигнут, то в соответствующих разрядах выходного регистра 5 вырабатываются двоичные 1, в про тивном случае - нули. Таким образом, на выходе устройства получается полный восстановительный сигнал по произвольной его части. Предложенное устройство оказывает ся особенно эффективным в тех случаях, когда требуется обеспечить малые аппаратурные затраты, небольшую потребляемую мощность и при этом очень высокую вероятность правильного восстановления ранее записанных сигналов по их произвольным частям. Формула изобретения 1. Ассоциативное запоминающее уст ройство, содержащее входной и выходной регистры и ассоциативный накопитель информации, отличающе еся тем, что, с целью повышения надежности устройства, в него введен входной и выходной коммутаторы, сдвигающий регистр, формирователь импульсов тенератор тактовых импуль сов, первый и блок задания режимов, причем входы сдвигающего регистра подключены к выходам формирователя импульсов, входы которого соединены с одними из выходов первог счетчика и сдвигающего регистра, дру гие выходы которого подключены к одним из входов входного и выходного 7 коммутаторов, другие входы которых соединены соответственно с выходами входного регистра и ассоциативного накопителя информации, а выходы - с одними из входов ассоциативного накопителя информации и входами выходного регистра, другие входы ассоциативного накопителя информации подключены к другим выходам первого счетчика, управляющие входы коммутаторов и сдвигающего регистра и один из управляющих входов первого счетчика соединень с выходами генератора тактовых импульсов, управляющие входы выходного регистра и ассоциативного накопителя информации, другой управляющий вход первого счетчика и вход генератора, тактовых импульсов соединены с выходами блока задания режимов. 2. Ассоциативный накопитель информации содержащий ключ, второй счетчик и последовательно соединенные сумматор и пороговый элемент, причем одни из выходов второго счетчика соединены с входами ключа, отличающийся тем, что, с целью повышения надежности накопителя, в него введены адресный блок и запоминающая матрица, причем один из входов адресного блока подключен к одному из выходов порогового элемента, а выходы соединены с одними из входов запоминающей матрицы, другие входы которой подключрчы к одним из выходов второго счетчика а выходы - к входам второго счетчика, входы сумматора и другие входы адресного блока являются входами накопителя, выходами которого являются другие выходы порогового элемента и второго счетчика и выходы ключа. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 9t999, кл. G 11 С , 197. 2.Авторское свидетельство СССР по заявке № 26 6667/ f -2, кл. G 11 С 15/00, 1978 (прототип). 3. Биофизика, т. 23, ff 6, 1978, с. 1069.

/V /V

i

Sh

1ж

/

rv.

f

h

e

./

Авторы

Даты

1982-11-23—Публикация

1981-03-09—Подача