(5) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство и ассоциативный накопитель информации для него | 1981 |

|

SU976477A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU877616A1 |

| Устройство для ассоциативного сжатия информации | 1984 |

|

SU1170482A1 |

| НЕЙРОННАЯ СЕТЬ С ПОРОГОВОЙ (k, t) СТРУКТУРОЙ ДЛЯ ПРЕОБРАЗОВАНИЯ ОСТАТОЧНОГО КОДА В ДВОИЧНЫЙ ПОЗИЦИОННЫЙ КОД | 2008 |

|

RU2380751C1 |

| Устройство для ассоциативного сжатия информации | 1983 |

|

SU1120390A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| Нейроподобный элемент | 1991 |

|

SU1816325A3 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

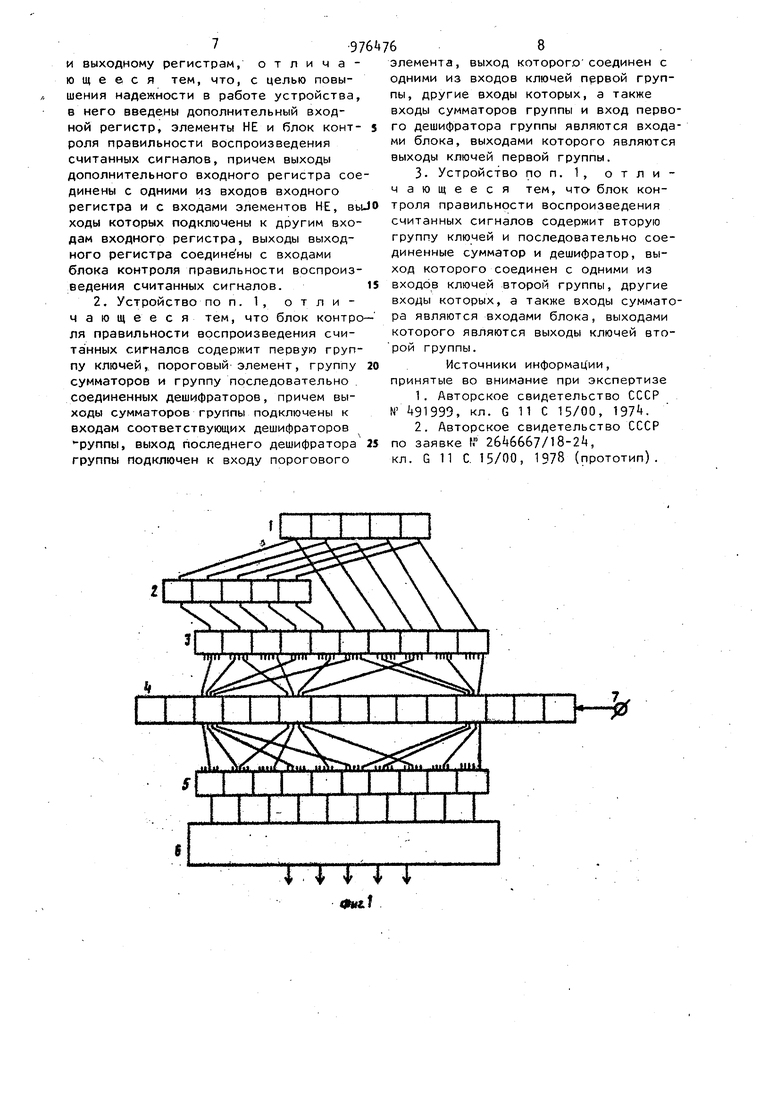

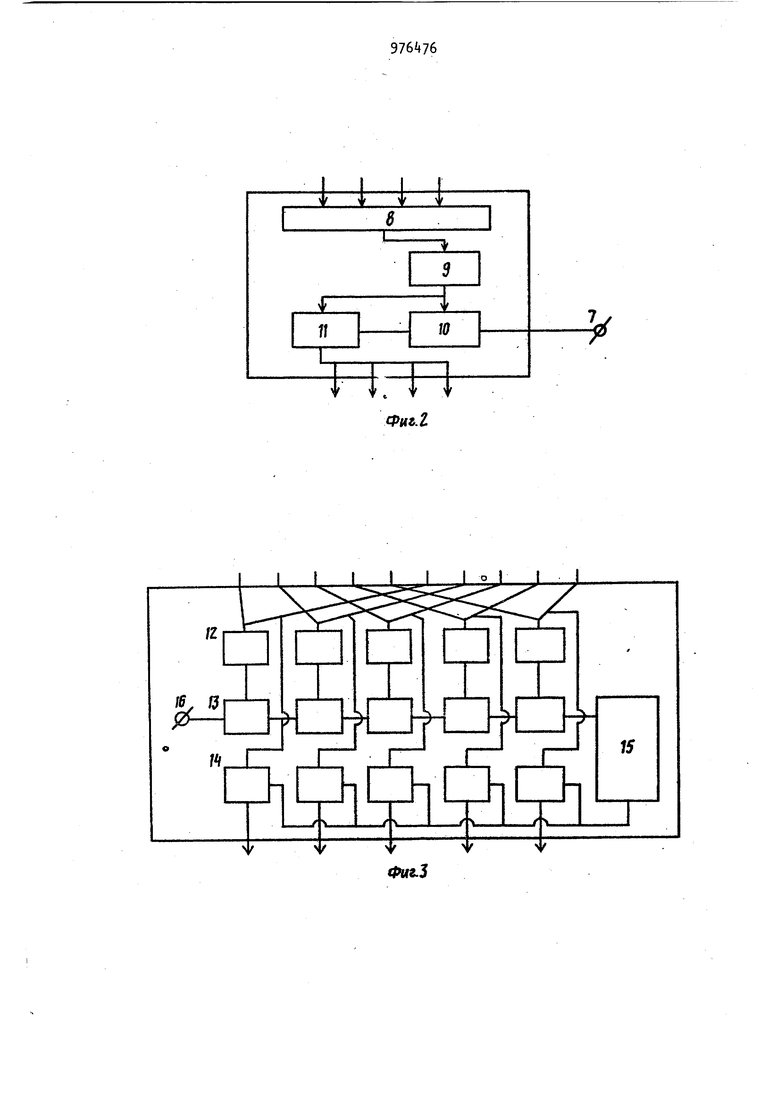

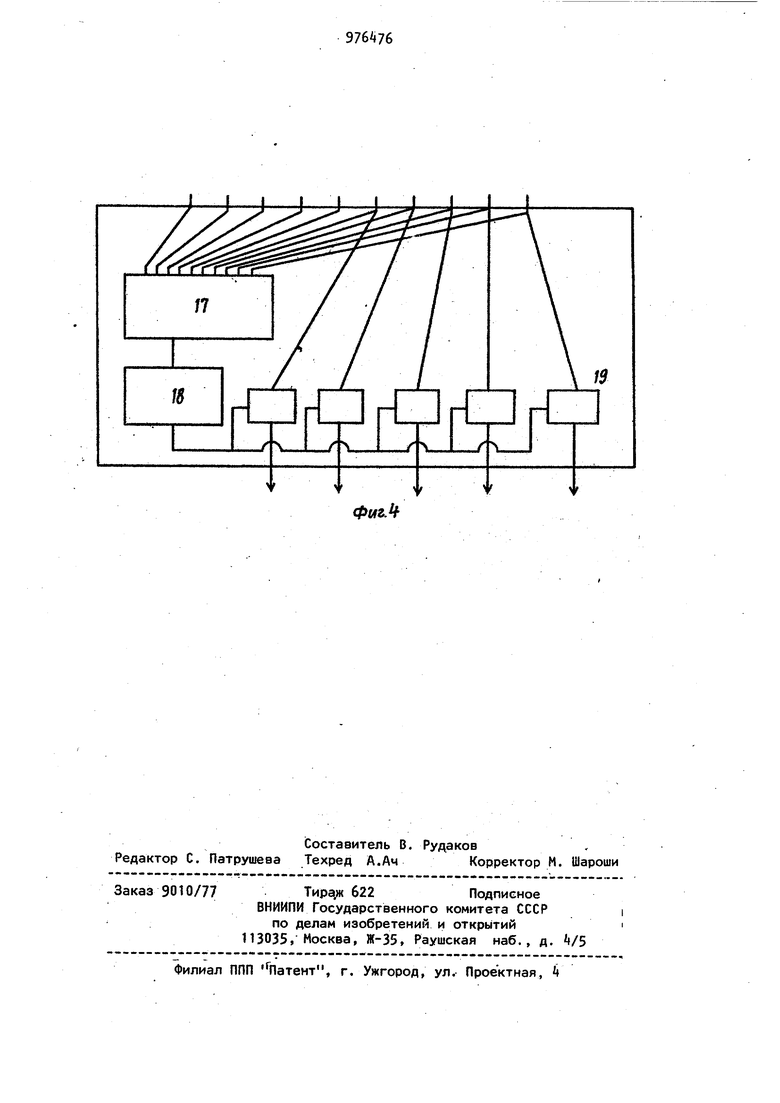

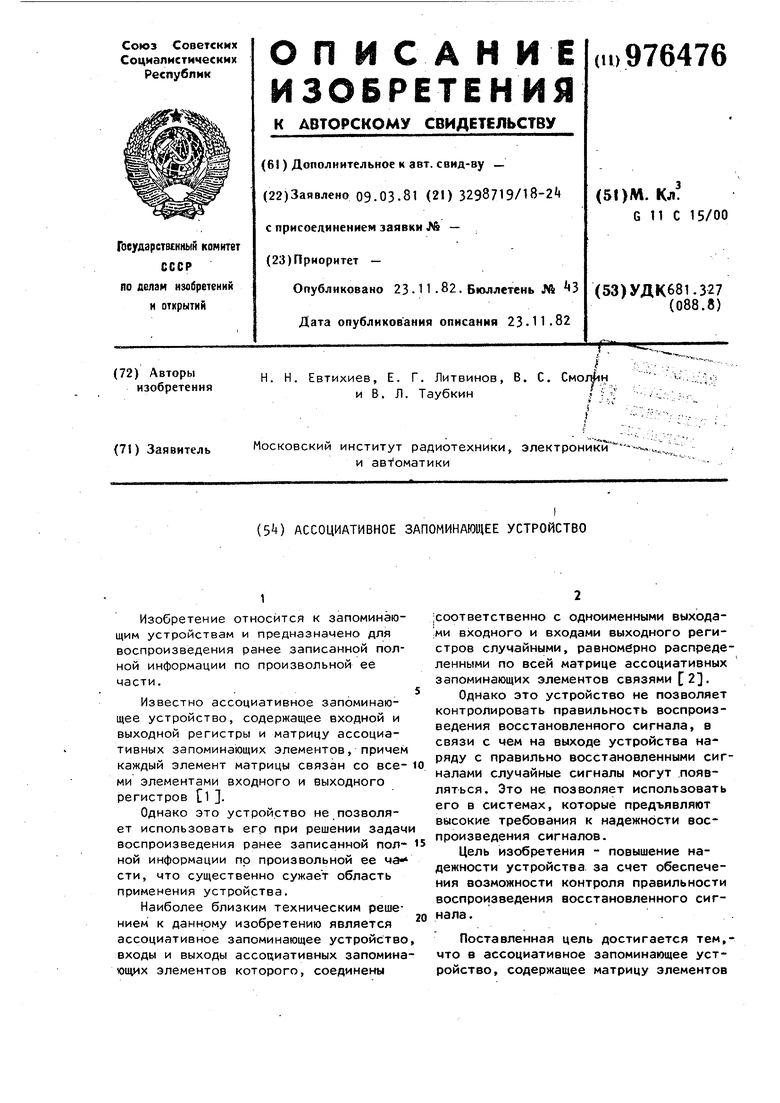

Изобретение относится к запоминающим устройствам и предназначено для воспроизведения ранее записанной полной информации по произвольной ее части. Известно ассоциативное запоминающее устройство, содержащее входной и выходной регистры и матрицу ассоциативных запоминающих элементов, причем каждый элемент матрицы связан со всеми элементами входного и выходного регистров Cl . Однако это устройство не позволяет использовать егр при решении задач воспроизведения ранее записанной полной информации по произвольной ее ча« сти, что существенно сужает область применения устройства. Наиболее близким техническим реше нием к данному изобретению является ассоциативное запоминающее устройство входы и выходы ассоциативных запомина ющих элементов которого, соединены |ссютветственно с одноименными выходами входного и входами выходного регистров случайными, равномерно распределенными по всей матрице ассоциативных запоминающих элементов связями 2. Однако это устройство не позволяет контролировать правильность воспроизведения восстановленного сигнала, в связи с чем на выходе устройства наряду с правильно восстановленными сигналами случайные сигналы могут появляться. Это не позволяет использовать его в системах, которые предъявляют высокие требования к надежности воспроизведения сигналов. Цель изобретения - повышение надежности устройства за счет обеспечения возможности контроля правильности воспроизведения восстановленного сигнала. Поставленная цель достигается тем,что в ассоциативное запоминающее устройство, содержащее матрицу элементов памяти, подключенную к входному и выходному регистрам, введены дополнительный входной регистр, элементы НЕ и блок контроля правильности воспроиз ведения считанных, сигналов, причем вы ходы дополнительного входного регистра соединены с одними из входов входного регистра и с входами элементов НЕ, выходы которых подключены к други входам входного регистра, выходы выходного регистра соединены с входами блока контроля правильности воспроизведения считанных сигналов, а также тем, что блок контроля правильности воспроизведения счетных сигналов содержит первую группу ключей, порого вый элемент, группу сумматоров и груп гту последовательно соединенных дешифраторов, причем выходы сумматоров группы подключены к входам соответствующих дешифраторов группы, выход последнего дешифратора группы подключен к входу порогового элемента, выход которого соединен с одними из входов ключей первой группы, другие входы которых, а также входы сумматоров группы и вход первого дешифратора группы являются входами блока, выходами которого являются выходы ключей первой группы. Кроме контроля правилькости воспроизведения сч| 1танных сигналов содержит вторую группу ключей и последовательно соединенные сумматор и дешифратор, выход которого соединен с одними из входов ключей вто рой группы, другие входы которы, а также входы сумматора являются входами блока, выходами которого являются выходы ключей второй группы. На фиг., t п0едставлена структурная схема предложенного устройства; на .фиг. 2 - структурная схема элемента памяти; на фиг. 3 - схема блока .контроля правильности воспроизведения считанных сигналов (первый вариа1 т исполнения); на фиг. k - схема второго варианта исполнения этого блока. Устройство содержит (фиг. 1) дополнительный входной регистр 1, Элементы НЕ 2, входной регистр 3, матрицу j элементов памяти, выходной регистр 5 блок 6 контроля правильности воспроизведения считанных сигналов, шину 7 разрешения модификации 7 Выходы регистра 1 соединены с поло виной входов входного регистра 3 и со входами элементов НЕ 2, .выходы которого соединены со входами второй оловины входного регистра 3. Входы выходы элементов памяти матрицы k оединены соответственно с одноимеными выходами входного 3 и входами выходного 5 регистров случайными, авномерно распределенными по всей атрице k связями. Элемент памяти ассоциативного апоминающего устройства содержит (фиг. 2) сумматор 8, пороговый элеент 9. счетчик 10 и ключ П. В первом варианте блок 6 содержит (фиг. 3) группу сумматоров 12, групу дешифраторов 13, первую группу ключей Ti, пороговый элемент 15, входную шину 16. Во втором варианте блок 6 содерит (фиг. 4) сумматор 17, дешифратор 18 и вторую группу ключей 19Устройство работает следующим образом. При подаче в режиме записи полнйго информационного кода на входной регистр 1 , на прямую половину входного регистра 3 поступает неизменный вход- ной сигнал, а на инверсную половину входного регистра 3 поступает сигнал, прошедший через инверторы. Таким образом, всегда ровно половина элементов входного регистра 3 возбуждается и активирует связи, соединяющие их с элементам.и памяти матрицы . Для каждого элемента памяти матрицы А суммируется число активированных входов, и если для некоторого элемента число превосходит, некоторый постоянный, конструктивно заданный порог записи и воспроизведения,, происходит модификация элемента памяти матрицы , разрешение на модификацию производится подачей сигнала по шине 7 разрешения модификации. При подаче части информационного сигнала в режиме воспроизведения на входной регистр 1, на входной регистр 3 поступает сигнал, представляющий из себя зашумленный информационный код, который, однако, обладает тем свойством, что имеет постоянную интенсивность (отношение числа возбужденных и невозбужденных элементов входного регистра всегда равно единице). В матрице t возбуждаются выходы тех модифицированных элементов памяти, для которых число активированных входов превосходит некоторый конструктивно заданный порог записи и воспроизведения. Сигналы с выходив матрицы it суммируются на каждом разряде выходного регистра 5, связанного с теми же элементами памяти матрицы 4, что и соответствующий разряд входного регистра 3- Если число активированных входов данного разряда выхо ного регистра 5 превышает некоторый конструктивно заданный порог, на выходе этого разряда возбуждается двоичная единица. Если сигнал, восстановленный на выходном регистре 5, воспроизводит один из ранее запоминаемых сигналов, то он обладает свойством инверсионного соответствия между прямой и инверсной составляющими, т. е. если на элементе прямой половины выходного регистра 5 воспроизведен двоичный ноль, то на соответствующем элементе инверсной половины воспроизведена дв ичная единица, и наоборот. Кроме того, он обладает тем свойством, что активирована ровно половина составляющих сигнала. J Восстановленный сигнал поступает на блок 6 контроля правильности воспроизведения считанных сигналов, кот рый осуществляет проверку на выполнение одного из названных свойств, причем выполнение первого свойства автоматически влечет за собой выполнение второго свойства (в то время Kafc при выполнении второго свойства первое может не выполняться). Элемент памяти матрицы 4 работает следующим образом. В режимах записи и воспроизведени на выходе сумматора 8 появляется сиг нал, однозначно определяющий число активированных входов элемента памят Этот сигнал подается на вход порогового элемента 9. Если число активированных входов превосходит заданный порог, то на выходе порогового элеме та 9 появляется сигнал, поступающий далее на счетчик 10 и ключ 11. В режиме записи при наличии сигнала на шине разрешения модификации 7 и сигнала на выходе порогового элемента 9 происходит модификация счетчика 10, заключаю1цаяся в том, что к коду числа, хранящегося в счетчике 10, добав ляется единица, при этом на его выхо де появляется сигнал, управляющий коэффициентом передачи ключа 11. В режиме воспроизведения сигнал с выхода порогового элемента 9 проходит через ключ 11 на выходы элемента памяти. 9 6 Блок 6 по первому варианту (фиг. 3J работает следующим образом. При подаче на блок 6 восстановленного (считанного) кода на выходе сумматоров 12 появляется сигнал, однозначно определяющий, сколько из двух входов сумматоров 12 активировано. В том случае, если активирован ровно один из входов соответствующего сумматора, дешифратор 13 увеличивает пропроводимость по цепочке, соединяющей пороговый элемент 15 с источником рабочего сигнала. Пороговый элемент 15 пропускает рабочий сигнал в случае, если сработало не менее, чем некоторое, наперед заданное число дешифраторов 13 (в частном случае - все). В этом случае открываются все ключи I и пропускают на выход схемы прямую составляющую установленного кода. Блок 6 по второму варианту (фиг. ) работает следующим образом. При подаче на вход блока восстановленного кода на выходе сумматора 17 появляется сигнал, однозначно определяющий число активированных входов схемы. Если это число отличается от половины количества.входов не более, чем на некоторую заданную величину (в частности равно), то дешифратор 18 посылает управляющий сигнал, который открывает ключи 19, и на выход схемы поступает нормальная составляющая восстановленного кода. Первый вариант реализации блока 6 обеспечивает контроль сигнала на свой ство соответствия примой и инверсной составляющей, а второй вариант - на свойство постоянства числа активированных составляющих правильно восстановленного сигнала, в связи с чем пер вый вариант блока 6 обеспечийает более высокую надежность контроля, а второй обладает тем преимуществом, что имеет более простую конструкцию. Технике-3 кономи чес кое преимущество предлагаемого устройства перед известным заключается в его повышенной надежности, что позволяет также значительно расширить область его применения, а частности использовать в системах, предъявляющих высокие требования к надежности воспроизведения запомненной информации. Формула изобретения 1. Ассоциативное запоминающее устройство, содержащее матрицу элементов памяти, подключенную к входному

и выходному регистрам, отличающееся тем, что, с целью повышения надежности в работе устройства, в него введены дополнительный входной регистр, элементы НЕ и блок коит- роля правильности воспроизведения считанных сигналов, причем выходы дополнительного входного регистра соединены с одними из входов входного регистра и с входами элементов НЕ, вьиЮ

ходы которых подключены к другим входам входного регистра, выходы выходного регистра соединены с входами блока контроля правильности воспроизведения считанных сигналов.

элемента, выход которогосоединен с одними из входов ключей первой группы, другие входы которых, а также входы сумматоров группы и вход первого дешифратора группы являются входами блока, выходами которого являются выходы ключей первой группы.

Источники информации, принятые во внимание при экспертизе

кл. G 11 С. 15/00, 1978 (прототип). троля правильности воспроизведения

У i

fI I I I I L I о I I

|риг.5 I

фаг.

Авторы

Даты

1982-11-23—Публикация

1981-03-09—Подача