ра, а катод первого диода и анод

ными входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования входного двоичного сигнала в телеграфный сигнал | 1984 |

|

SU1233293A1 |

| Устройство преобразования входного двоичного сигнала в телеграфный сигнал | 1985 |

|

SU1320909A1 |

| Устройство преобразования входного двоичного сигнала в телеграфный сигнал | 1988 |

|

SU1518907A2 |

| Цифровая полупроводниковая интегральная схема с тремя состояниями на выходе | 1980 |

|

SU900454A1 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2316891C1 |

| МОЩНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2092969C1 |

| Преобразователь логических уровней | 1990 |

|

SU1812634A1 |

| Усилитель мощности | 1977 |

|

SU733083A1 |

| Аналоговый N-канальный коммутатор широкополосных видеосигналов | 1988 |

|

SU1598153A1 |

| Усилитель | 1988 |

|

SU1720146A1 |

1. УСТРОЙСТВО ,ФТЯ ПРЕОБРАЗОВАНИЯ ВХОДНОГО ДВОИЧНОГО СИГНАЛА В ТЕЛЕГРАФНЫЙ СИГНАЛ, содержащее источник питания, источник Hanpiume- ния смещения и двухтактный выходной каскад, состоящий из двух транзисторов разного типа проводимостей, коллекторы которых объединеныИ являются выходом устройства, а также первый фазоинвертирующий п-р-п-транзистор, коллектор которого через первый резистор соединен с базой р-п-ртранзистора двухтактного выходного каскада, отличающееся тем, что, с целью уменьшения потребляемой мощности, введены два согласующих резистора, два нагрузочных резистора,два ограничителя тока, второй резистор и второй фазоинвертирзгющий р-п-р-транзистор, коллектор которого через второй резистор подключен к базе п-р-п-транзистора двухтактного выходного каскада, причем каждый ограничитель тока состоит из делителя напряжения, резистора и двух тpaнзиctopoв, база первого из них соединена с делителем . напряжения, который соединен с общей шиной, шиной источника питания, с одним выводом резистора и с коллектором второго транзистора, база которого соединена с другим выводом резистора и с коллектором первого транзистора, эмиттер которого соединен с эмиттером второго транзистора, при этом первый ограничитель тока на п-р-п-транзисторах и второй ограничитель тока на р-п-р-транзисторах включены соответственно между плюсовой шиной источника питания и эмиттером р-п-р-транзистора двухтактного выходного каскада и минусовой шиной источника питания и эмиттером п-р-п-транзистора двухтактного выходного, каскада, а база первого фаэоинвёртирующего п-р-птранзистора через последовательно соединенные первый и второй согласующие резисторы соединена с базой второго фазоинвертирующего р-п-р. транзистора, эмиттеры фазоинвертирующих п-р-п и р-п-р-транзисторов соединены с соответствующими шинами 11сточника напряжения смещения, при. чем коллекторы фазоинвертирующих П-р-п и р-п-р-транзисторов через нагрузочные резисторы соединены соответственно с плюсовой и минусовой шинами источника питания, а соответствующие выводы согласующих резисторов являются входом устройства. 2. Устройство для преобразования входного двоичного сигнала в телеграфный сигнал ПОП.1, отличающееся тем, что, с целью повышения надежности, введены два .диода, при этом анод первого диода и катод второго диода соединены соответственно с базами первого фазоинвертирующего п-р-п-транзистора и второго

Изобретение относится к электросвязи и может использоваться для сопряжения источников цифровой информации с телеграфными каналами связи. .

Известно устройство преобразования входного двоичного сигнсша в телеграфный сигнал с защитой от перегрузки и встречного напряжения, содержащее коммутационный мост, генератор возбуждения, два транзисторных ключа, соединенных с входом устройства, два трансформатора, подключенных к базовьм цепям транзисторов, являющихся плечами моста, тиристор, включенный в выходную цепь устройства и резисторы-ограничители тока PJ .

Однако наличие трансформаторов в данном устройстве приводит к снижению надежности, увеличению габаритов устройства ик ухудшению формы выходного сигнала.

Наиболее близким техническим решением к изобретению является устройство для преобразования входного двоичного сигнала в. телеграфный сигнал, содержащее источник питания, источник напряжения смещения и двухтактный выходной каскад, состоящий из двух транзис.торов разного типа проводимостей, коллекторы которых объединены и являются выходом устройства, а также первый фазоинвертирующий п-р-п-транзистор, коллектор fcoToporo через первый резистор соединен с базой р-п-р-транзистора двухтактного выходного каскада, а также содержащее два токооГраничивающих резистора, лключенньпс в эмиттёрные цепи двухтактного выходного каскада 2 .

Недостатком этого устройства является большая потребляемая мощность при коротком замыкании в линии или при появлении в ней встречного напряжения, что требует использования в двухтактном выходном каскаде мощных транзисторов и токоограничивающих резисторов.

Кроме того, недостатком обоих, известных устройств является отсут5 ствие режима, при котором можно объединить входы и выходы двух или более однотипных устройств в целях повьпиения надежности за счет резервирования.

0. Цель изобретения - уменьшение потребляемой мощности и повышение надежности устройства.

Указанная цель достигается тем,

5 что в устройство для преобразования входного двоичного сигнала в телеграфный сигнал, содержащее источник питания, источник напряжения смещения и двухтактный -выходной каскад,

0 состоящий из двух транзисторов разного типа проводимостей, коллекторы которых объединены и являются выходом устройства, а также первый фазойнвертирующий п-р-п транзистор, 5 коллектор которого через первый резистор соединен с базой р-п-р транзистора двухтактного выходного каскада, введены два согласующих резистора, два нагрузочных резистора, два

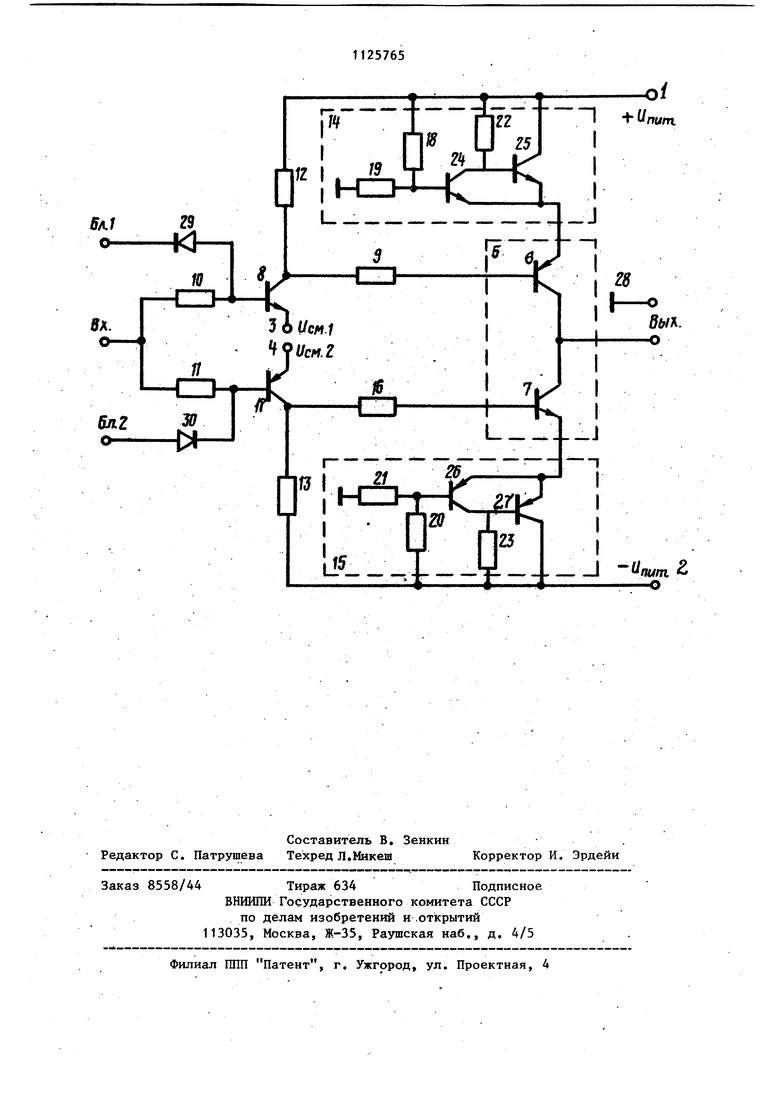

о ограничителя тока, второй резистор и второй фазойнвертирующий р-п-р транзистор, коллектор которого через второй резистор подключен к базе п-р-п транзистора двухтактного выходного каскада, причем каждьй ограничитель тока состоит из делителя налряжения, резистора и двух транзисторов, база первого из них соединена с ; делителем напряжения, который соеQ Динен с общей шиной, шиной источника питания, с одним выводом резис.тора и с коллектором второго транзистора, база которого соединена с другим выводом резистора и с коллек, тором первого транзистора, эмиттер которого соединен с эмиттером втоiрого транзистора, при этом первый ограничитель тока на п-р-п транзисторах и второй ограничитель тока на р-п-р транзисторах включены соответственно между плюсовой шиной источника питания и эмиттером р-п-р транзистора двухтактного выходного каскада и минусовой шиной источника питания и эмиттером п-р-п транзистора двухтактного вьпсодного каскада, а база первого фазоинвертирующего п-р-п тран;истора через последовательно соединенные первый и второй согласующие резисторы соединена с базой второго фазоинвертирую щего р-п-р транзистора, эмиттеры фазоинвертирующих п-р-п и р-п-р транзисторов соединены с соответствующими шинами источника напряжения смещения, причем коллекторы фазоинвертирующих п-р-п и р-п-р транзисторов через нагрузочные резисторы соединены соответственно с плюсовой и минусовой шинами источника питания, а соответствующие выводы согла сующих резисторов являются входом устройства. Кроме того, введены два диода, при этом анод первого диода и катод второго диода соединены соответ ственно с базами первого фазоинвертирующего п-р-п транзистора и вто- рого фазоинвертирующего р-п-р транзистора, а катод первого диода и анод второго диода являются блокиро вочными входами устройства. Введение ограничителей тока на транзисторах позволило резко уменьшить ток, потребляемый от источника питания при коротком замыкании или появлении встречного напряжения на выходе устройгтва, а введение второго фазоинвертирующего транзистора диодов и .соответствуницих связей позволило получить режим, при котором возможно параллельное включение по входам и выходам двух или более устройств, необходимое для резервирования. На чертеже приведена электричес- кая принципиальная схема устройства Устройство для преобразования входного двоичного сигнала в телеграфный сигнал -содержит источники 1 и 2 питания, источники 3 и 4 напряжения смещения, двухтактный выход ной каскад 5 на двух транзисторах 6 и 7 разного типа проводимостей, коллекторы которых объединены и являются выходом устройства, первый азоинвертйрующий п-р-п транзистор 8, оллектор Которого через первый езистор 9 соединен с базой р-п-р ранзистора 6 двухтактного выходного каскада 5, а также содержит два согласующих резистора 10 и 11, два нагрузочных резистора 12 и 13, два ограничителя 14 и 15 тока, второй резистор 16, второй фазоинвертйрующий р-п-р транзистор 17, коллектор которого через второй резистор 16 подключ ен к базе п-р-п транзистора 7 двухтактного выходного каскада 5, причем каждый ограничитель 14 (15) тока состоит из делителя 18 и 19 (20 и 21) напряжения, резистора 22 (23) и двух транзисторов 24 и 25 (26 и 27), база первого 24 (26) из них соединена с делителем 18 и 19 (20 и 21) напряжения, который соединен с общей шиной 28, шиной 1(2) источника питания, с одним выводом резистора 22(23) и с коллектором второго транзистора 25(27), база которого соединена с другим выводом резистора 22(23) и с коллектором первого тринзистора 24(26),, эмиттер которого соединен с эмиттером второго транзистора 25(27), при этом первый ограничитель 14 тока на п-р-п транзисторах 24. и 25 и второй ограничитель 15 тока на р-п-р транзисторах 26 и 27 включены соответственно между плюсовой шиной 1 источника аитания и эмиттером р-п-р транзистора 6 .двухтактного выходного каскада 5 и минусовой шиной 2 источника питания и эмиттером п-р-п транзистора 7 двухтактного выходного каскада 5, а база первого фазоинвертирующего n-n-n транзистора 8 через последовательно соединенные первый 10 и второй 11 согласующие резисторы соединена с базой второго фазоинвертирзпощего р-п-р транзистора 17, эмиттеры фазоинвертирук щих п-р-п и транзисторов 8 и 17 соединены с шинами 3 и 4 источника напряжения смещения, причем коллекторы фазоинвертирующих п-р-п и р-п-р транзисторов через нагрузочные резисторы 12 и 13 соединены соответственно с плюсовой 1 и минусовой 2 шинами источника питания, а соответствующие выводы согласующих резисторов 10 и 11 являются входом устройства. Устройство содержит также два диода 29 и 30, причем анод первого диода 29 и катод второго диода 30 соединены соответственно базами первого фазоинвертирующего n-p-h транзистора 8 и второго фазо инвертирующего р-п-р транзистора 1 а катод первого диода 29 и анод второго, диода 30 являются блокировочными входами устройства. Устройство работает следукнцим образом. В режиме преобразования входног двоичного сигнала в телеграфный сигнал на блокирующие входы уст.ройства подаютсянапряжения «6M tcMH«U6A,2«UcM.2, при которых диоды 29 и 30 закрыты. При наличии на входе устройства логической единицы 8xUcM..HO,c 6.9. нас. фазоинвертируниций п-р-п транзистор 8 открыт и насыщен, а транзисторы .24 и 25 ограничителя 14 тока и р-п-р транзистор 6 выходного двухтактного каскада 5 находятся в активном режиме и представляют собой источник тока. На выходе устройств присутствует сигнал положительной полярности, равный разности напряж ния на плюсовой дшне 1 источника питания и падений напряжения на тр зисторе 25 и р-п-р транзисторе 6 выходного двухтактного каскада 5. При наличии на входе устройства сигнала логического нуля .2.но.с1Гиб.,.кас.;: фазоинвертирующий р-п-р транзистор 17 открыт и насыщен, а транзисторы 26 и 27 ограничителя 15 тока и n-p транзистор 7 выходного двухтактног каскада 5 находятся в активном режиме, представляя собой, как и в первом случае, источник тока. На выходе устройства сигнал отрицател ной полярности. При перегрузке, вызванной корот ким замыканием в линии, или при по явлении встречного напряжения происходит следующее. Если на- входе устройства действует сигнал логической единицы, то при перегрузке потенциал в точке соединения змит- теров траняисторов 24 и 25 ограничителя 14 тока уменьшается. При этом первый транзистор 24 ограничителя 14 тока открывается больще, закрывая тем самым второй транзистор 25 ограничителя 14 трка. В результате через р-п-р транзистор 6 выходного двухтактного каскада 5 протекает небольшой ток, величина которого зависит от величины резистора 22. Аналогичные процессы происходят при наличии на входе, устройства сигнала логического нуля, когда открыты второй ограничитель 15 тока и п-р-п транзистор 7 выходного двухтактного каскада 5. При параллельном включении по входам и выходам двух или более устройств с целью повьшения надежности за счет резер вирования на блокировочные входы резервных устройств необходимо подать напряжения, открывающие диоды 29 и 30 VnUcM.rVp.)sA.c«.2(JA.np., где Ugn -.падение напряжения на открытом диоде. Таким образом, включение в эмитг: терные выходного двухтактного каскада ограничителей тока на транзисторах позволило снизить потребяемую устройством мощность. Так в оминальном режиме работы при напряении питания)и„1 22 - 30 В и нарузке 1, 900 - 1100 Ом потреблямая мощность не превьшает 0,1 ВА, при коротком замыкании на выходе стройства или при появлении встречого напряжения потребляемая мощость не превьшает 0,12 ВА, что поволяет реализовать устройство в иде гибридной микросхемы.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вывода телеграфных сигналов с защитой от перегрузки и встречного напряжения с линии | 1972 |

|

SU439934A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ оценки остаточного ресурса рабочего колеса гидротурбины на запроектных сроках эксплуатации | 2019 |

|

RU2721514C1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-11-23—Публикация

1983-07-28—Подача