(54) РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 1991 |

|

RU2015543C1 |

| Мажоритарное устройство | 1980 |

|

SU892732A1 |

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

| Устройство для мажоритарного выбора сигналов | 1991 |

|

SU1833876A1 |

| Многоканальное устройство для резервирования линии связи | 1976 |

|

SU698175A1 |

| Трехканальное мажоритарно-резервированное устройство | 1990 |

|

SU1795461A1 |

| Мажоритарно-резервированное устройство | 1979 |

|

SU1001529A1 |

| Трехканальное резервированное устройство | 1983 |

|

SU1115256A2 |

| Резервированное устройство | 1980 |

|

SU922751A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

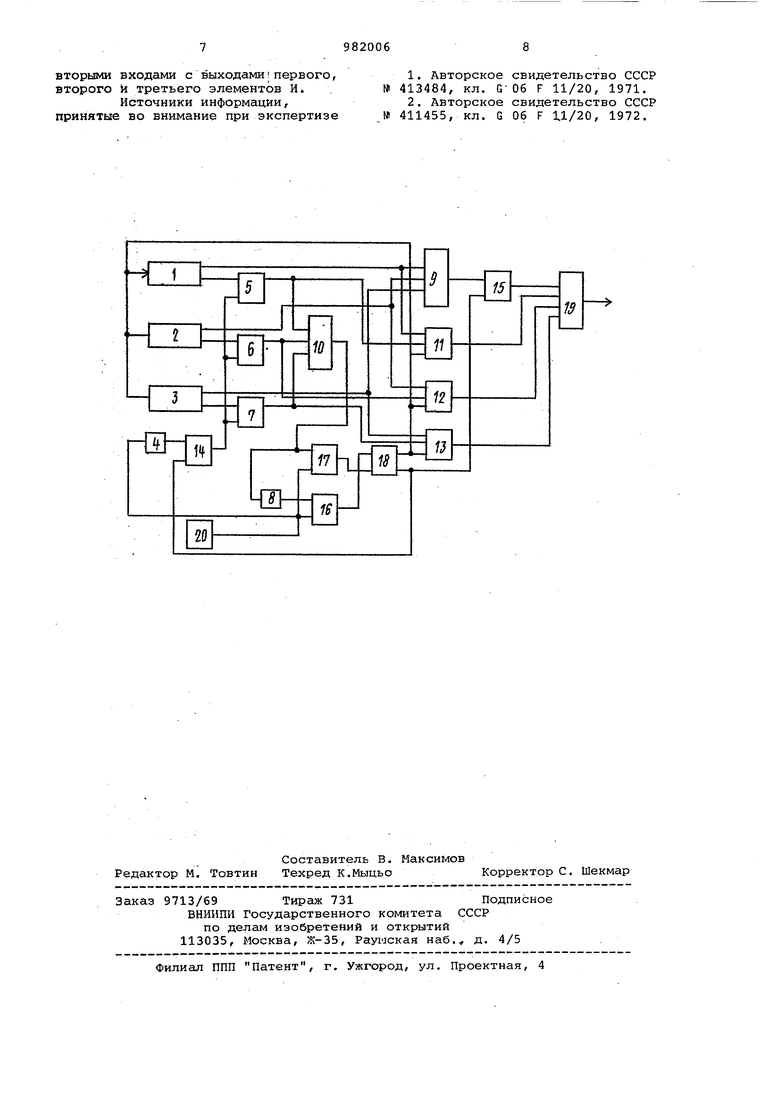

Изобретение относится к автомати ке и вычислительной технике и может быть использовано при разработке цифровых устройств и вычислительных машин с повышенными требованиями к надежности. Известно резервированное устройство, содврхгащее три резервируемых блока, соединенных с мажоритарныгл блоком, источник разрешающего сигна ла, выход которого соединен с соответствующими входами ключевых элементов, и дополнительные ключевые элементы, через которые элементы И подсоединены к элементу ИЛИ f 1/j. Недостаток устройства состоит в неполной определенности исправности канала и в том, что при последовате ных отказах в двух каналах вероятность исправной работы всего устрой ства сохраняется лишь с вероятностью 0,5. Наиболее близким техническим решением к изобретению ярляется резер вированное устройство, содержащее резервируемые блоки, соединенные с индикаторагли отказов и мажоритарным элементом, переключателе режима, управляющий вход которого через диф ференцирующую цепочку соединен с выходом счетного триггера, на вход которого через элемент ИЛИ поступают сигналы от индикаторов отказов. При отказе двух каналов переключатель режима отключает выход мажоритарного элемента и подключит выход исправного канала. При последовательном поступлении двух сигналов от индикаторов отказа на выходе дифференцирующей цепочки появляется сигнал, устанавливающий переключатель режима в состояние, соответствующее отключенному мажоритарному элементуи подключенному исправному каналу С 2. Недостаток устройства состоит в том, что оно не может восстановить первоначальный принцип работы после отказа двух каналов даже в том случае, если отказы более не наблюдаются (саглоустраняющиеся отказы) , Кроме того, если: отказ в двух каналах наступит одновременно,то сигналы от индикаторов отказа воспримутся счетным триггером как один сигнал и не приведут к перестройке структуры устройства. Цель изобретения - повышение надежности работы резервируекюго устройства, в частности обеспечение возможности восстановления работы устройства в мажоритарном режиме пос ле исчезновения отказов хотя бы в одном из двух отказавших каналов и сохранения достоверной информации на выходе устройства при одновременном отказе двух каналов. . Поставленная цель достигается тем, что резервированное устройство, содержащее индикаторы отказов, переключатель режима, элемент ИЛИ и первый и второй и третий резервируемый блоки, первые выходы которых соединены со входами первого мажоритарного элемента, содержит семь элементов И, элемент НЕ, элемент задержки источник импульсов опроса и второй мажоритарный элемент, входы которого соединены с первыми входами первого второго и третьего элементов И и с eдиничны 1и выходами соответствующих индикаторов отказов, а выход через четвертый элемент И - с нулевым входом переключателя режима и через элемент НЕ - с первым входом пятого элемента И, подключенного выходом к единичному входу переключателя режима, нулевой выход которого соединен с первыми входами шестого и седь мого элементов И, а единичный выход - со вторыми входами первого, второго и третьего элементов И и со входами резервируемых блоков, вторые выходы которых соединены с единичными входами индикаторрв отказов, а первые выходы - с третьими входами первого, второго и третьего элементов И, выход источника импульсов опроса соединен со вторыми входами чеТ вертого и пятого элементов И и чере элемент задержки - со вторым входом шестого элемента И, связанного выходом с нулевыми входами индикаторов отказов, причем второй вход седьмог элемента и подключен к выходу первого мажоритарного элемента, а выход к первому входу элемента ИЛИ, соединенного вторыми входами с выходами первого, второй и третьего элементов И. На чертеже приведена блок-схема устройства. Резервированное устройство содер жит первый, второй и.третий резерви руемые блоки 1-3 (представляющие собой вычислительные машины), элемент 4 задержки, индикаторы 5-7 отказов, выполненные на триггерах исправности, элемент 8 НЕ, первый 9 и второй 10 мажоритарные элементы, первый 11, второй 12, третий 13, ше той 14, седьмой 15, пятый 16 и чет.. вертый 17 элементы .И, переключатель 18 режима, элемент ИЛИ 19 и источник 20 опроса импульсов. Для индикации исправной работы каналов используется то обстоятельство, что цифровая вычислительная машина по соответствующей програмгле выдает управляющие сигналы во внешние устройства строго по времени. Для этого в составе машины имеется устройство форглирования временных интервалов, это же устройство может быть использовано для формирования . импульсов опроса, пеоиод следования которых равен периоду выдачи управляющих сигналов. Перед выдачей управляющих сигналов во внешние устройства просчитывается контрольный тест с последующей выдачей сигнала прохождения теста каждого канала на соответствующие индикаторы отказов 5-7 каналов, состояния которых определяют режим работы устройства. Резервированное устройство работает в двух решениях, нет отказов или отказ в одном резервируемом блоке (блок неисправен или произошел сбой) и отказ в двух блоках (два блока неисправны, одновременные неисправность и сбой или сбой в двух блоках). При наличии отказа в одном резервируемом блоке (или при отсутствии отказа) сигналы прохождения контрольного теста с выходов блоков 1-3 поступают в единичные входы индикаторов 5-7 соответственно и устанавливают их в единичное состояние (при одном отказавшем блоке в единичное состояние не будет установлен соответствующий индикатор отказа). При этом на выходе элемента 10 появится сигнал, соответствующий исправности большинства (или всех) резервируемых блоков и разрешит работу элемента И 17, одновременно запретит работу элемента И 16. Сигнал от источника 20 поступает на входы элементов И 17, 16 и на вход элемент 4, при этом элемент И 17 срабатывает и сбросит (или подтвердит сброс) переключатель 18. Сигнал нулевого выхода переключателя 18 разрешит работу элементов И 14 и 15, одновременно сигнал единичного выхода этого переключателя запретит работу элементов И 11-13 и поступит в блоки , как сигнал исправности большинства (или Всех) каналов. Получив информацию об исправности, блоки 1-3 выдают код управляющего сигнала, который через элемент 9 (по большинству), элемент И 15 и элемент ИЛИ 19 поступает на выход устройства. Задержанный элементом 4 сигнал поступает на вход элемента И 14, ас выхода этого элемента на нулевые входы индикаторов 5-7 и производит их сброс. Таким образом, устройство возвращается в исходное состояние.. В случае отказа в двух каналах сигнал прохохсдения контрольного теста поступает только из исправного канала, поэтому в единичное состоя ние установлен только один индикатор отказа (например 5) канала. Та как единичные выходы индикаторов 5-7 соединены со входами элементов И 11-13, соответственно, то на вход одного из элементов И (например на входе элемента Н 11) появится разрешающий потенциал. На входе элемента 10 появится сигнал, соответствующий неисправности (два индика тора отказов б и 7 находится в сос тоянии соответствующему неисправно ти), который запретит работу элеме та И 17 и разреишт работу элемента И 16. По приходу сигнала от источника 20 элемент И 16 срабатывает и сигналом, поступающим на единичный вход переключателя 18, устанавливае его в единичное состояние. Сигнал с нулевого выхода переключателя 18 запрещает работу элементов Н 14 и тем ftaMbn.i запрещает сброс индикато ров 5-7 и блокирует работу элемента 9 . С другой стороны сигнал с единичного выхода переключателя 18 поступает на входы элементов И 11как разрешающий и одновременно поступает на входы каналов, где воспринимается как сигнал прерывания. Программа прерывания производит восстановление ячеек оперативной памяти отказавших каналов, повторный просчет контрольного теста, а при выходе из программы прерывания разрешается выдача кода управляющего сигнала во внешние устройства. Так как выходы каналов соединены с входают элементов 11-13 соот ветственно, то код управляющего сигнала поступит на выход только через тот элемент И, работа которог разрешена индикатором отказа,(в примере через элемент И 11) и дале через элемент ИЛИ 19. I Если в результате прерывания был восстановлены отказавшие ранее каналы (или один канал), то код управ ляющего сигнала может поступить через все (или два) разрешенные элементы И 11-13 и элемент ИЛИ 19 на выход, так как в данном цикле выдачи управляющего сигнала переключатель 18 находится в единичном состоянии и блокирует работу элемента Сброс переключателя 18 при восстановлении каналов произойдет в следующем цикле выдачи и работа устрой ства в мажоритарном режиме восстано вится Таким образом, резервированное устройство позволяет восстанавливат мажоритарный режим работы после отказа двух резервируемых блоков и последующем самоустранении хотя бы одного из отказов, а также лишнего недостатков известных устройств, не реагирующих на совпадающие по времени отказы в двух блоках. Кроме, того, при резервировании цифровых вычислительных машин с помощью предлагаемого устройства возможно восстановление работоспособности при наличии отказов в трех каналах одновременно, но при условии, что хотя бы в одном из каналов был отказ, носящий характер сбоя. Поиск исправного канала при этом осуществляется программнЕлми. средствами. Использование мажоритарного и логических элементов для управления переключением мажоритарного и одноканального режимов вместо счетного триггера с дифференцирующей цепочкой, предложенных в прототипе, значительно расширяет возможности резервированного устройства с точки зрения сохранения работоспособности. Формула изобретения Резервированное устройство, содержащее индикаторы отказов, переключатель режима, элемент ИЛИ и первый, второй и третий резервируемый блоки, первые выходы которых соединенных со входами первого мах оритарного элемента, отличающееся тем, что, с целью повышениА надежности устройства, оно содержит семь элементов И, элемент НЕ, элемент задержки, источник импульсов опроса и второй мажоритарный элемент, входы которого соединены с первыми входами первого, второго и третьего элементов И и с единичными выходами соответствующих индикаторов отказов, а выход через четвертый элемент И с нулевыг/1 входом переключателя режима и через элемент НЕ - с первыг входом пятого элемента И, подключенного выходом к единичного входу переключателя режима, нулевой выход которого соединен с первыми входами шестого и седьмого элементов И, а единичный выход - со вторыми входами первого, второй и третьего элементов И и со входагл резервируег-плх блоков, вторые выходы которых соединены с единичньи-ш входаг.ш индикаторов отказов, а первые выходы - с третьими входами первого, второго и третьего элементов И, выход источ-. ника импульсов опроса соединен со вторыми входами четвертого и пятого элементов И и через элемент задержки - со вторым входом шестого элемента И, связанного выходом с нулевыми входами индикаторов отказов, причем второй вход седьмого элемента И подключен к выходу первого мажоритарного элемента, а выход - к первому входу .элемента ИЛИ, соединенного

вторыми входами с выходами:первого, второго и третьего элементов И.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-12-15—Публикация

1981-06-15—Подача