(54) МАЖОРИТАРНО-РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарно-резервированное устройство | 1980 |

|

SU1032600A1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Мажоритарно-резервированное устройство | 1982 |

|

SU1042217A1 |

| Мажоритарно-резервированное устройство | 1979 |

|

SU955539A1 |

| Дешифратор с коррекцией ошибок | 1981 |

|

SU1012262A1 |

| Резервированное устройство | 1981 |

|

SU982006A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| Многоканальное устройство для резервирования линии связи | 1976 |

|

SU698175A1 |

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

Изобретение относится к вычислительной технике и может быть исполь- , зовано для построения систем с высокими показателями надежности.

Известно резервированное устройство, содержащее резервированные блоки, мажоритарный элемент, индикаторы отказов, блок перестройки структуры, причем каждый резервируемый блок содержит элементы И, одноканальный и многоканальный счетчики, схемы контроля, схемы анализа нулевого состояния и регистр. Такое устройство . обеспечивает повышение надежности за счет того, что в нем отказ классифицируется как серия следующих друг за другом сбоев, а также за счет перестройки структуры tl.

Наиболее близким по технической сущности к предлагаемому является резервированное устройство, содержащее мажоритарный элемент, входы которого соединены с выходами резервированных блоков и входами индикаторов отказов, выходы которых связаны через элементы ИЛИ с соответствующими входами реверсивного счетчика, который через дешифратор и весовые датчики подключен к входам мажоритарного элемента. Устройство реализует мажоритарнуто функцию при любом числе отказавших блоков, причем выбор большинства каждый раз производится из совокупности, имеющей в своем составе большинство достоверны сигналов С 2.

Недостаток устройства состоит в сложности регшизации.

Цель изобретения - упрощение уст10ройства.

Поставленная цель достигается тем, что мажоритарно-резервированное устройство, содержащее резервируемые блоки, выходы которых подключены к

15 индикаторам-отказов, содержит первый двоичный сумматор, два блока сумматоров единиц и элементы И, выходы которых подключены к входам первого блока сумматоров единиц, первые вхо20ды - к выходам соответствующих резервируемых блоков, а вторые входы к выходам соответствующих; ии51икаторов отказов и к входам второго блока сумматоров Гединиц , соединенного ин25версным выходом с вторым входом первого двоичного сумматора, инверсный выход которого подключен к выходу ;устройства. Каждый из блоков сумматоров единиц выполнен в виде п«-ступен3fQ 1чатой пирамиды вторых двоичных суматоров, причем разрядность вторых воичных сумматоре, -ой ступени равна I количество .вторых, двоичных сумматрров i-ой ступени не превышает входы вторых двоичных сумматоов первой ступени совместно с вхоами переноса всех вторых двоичных сумматоров соединены с входами блока, выходы сумм и переносов вторых воичных сумматоров каждой из первых (п-1) ступеней поразрядно подключены к входам вторых двоичных сумматоров последующих ступеней, а прямые и инверсные выходы второго двоичного сумматора п-ой ступени соединены соответственно с прямыми и инверсными выходами блока.. .

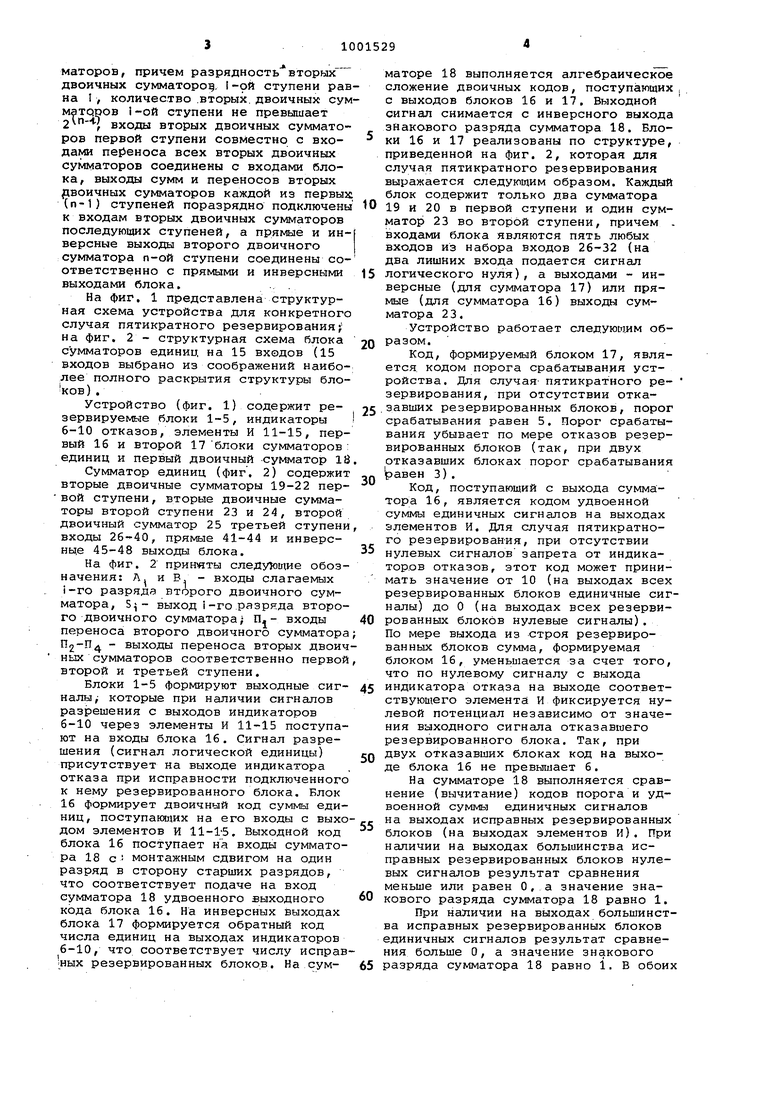

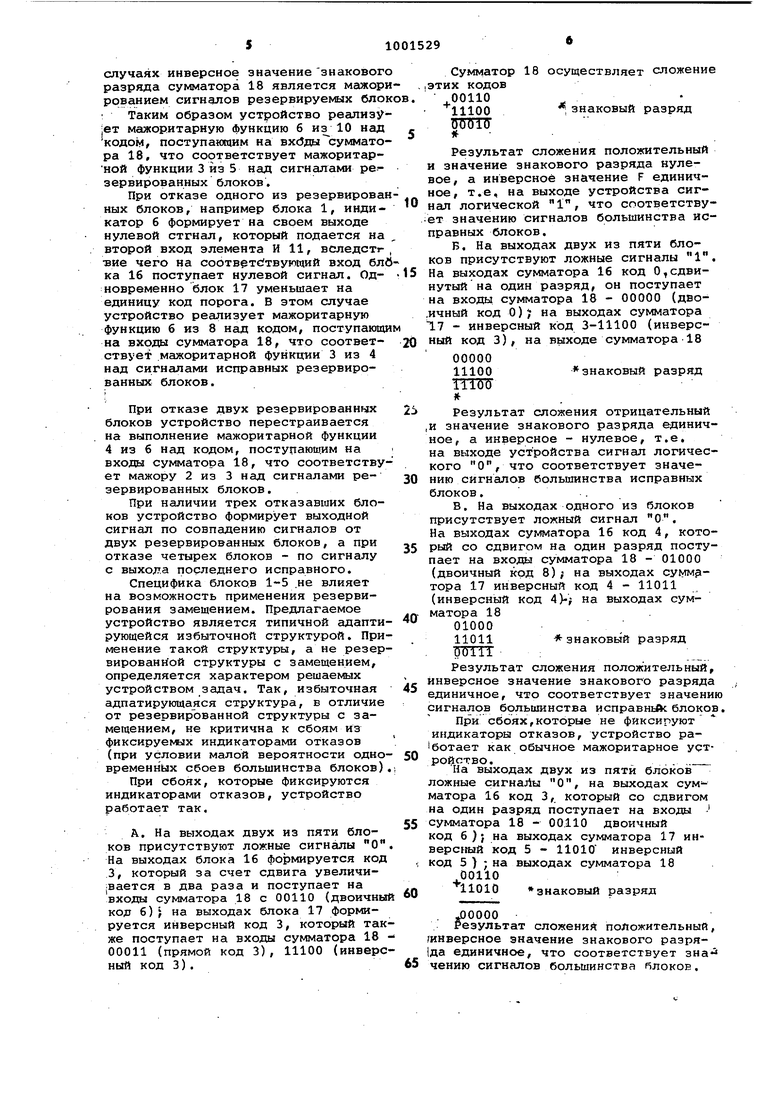

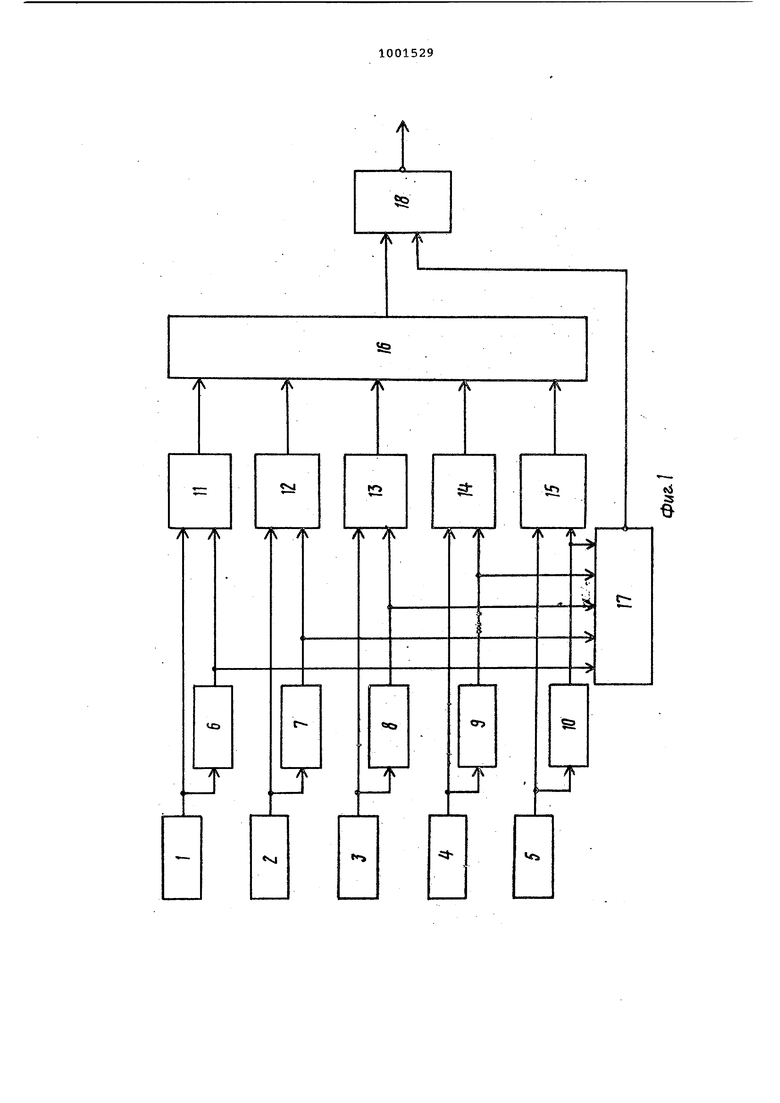

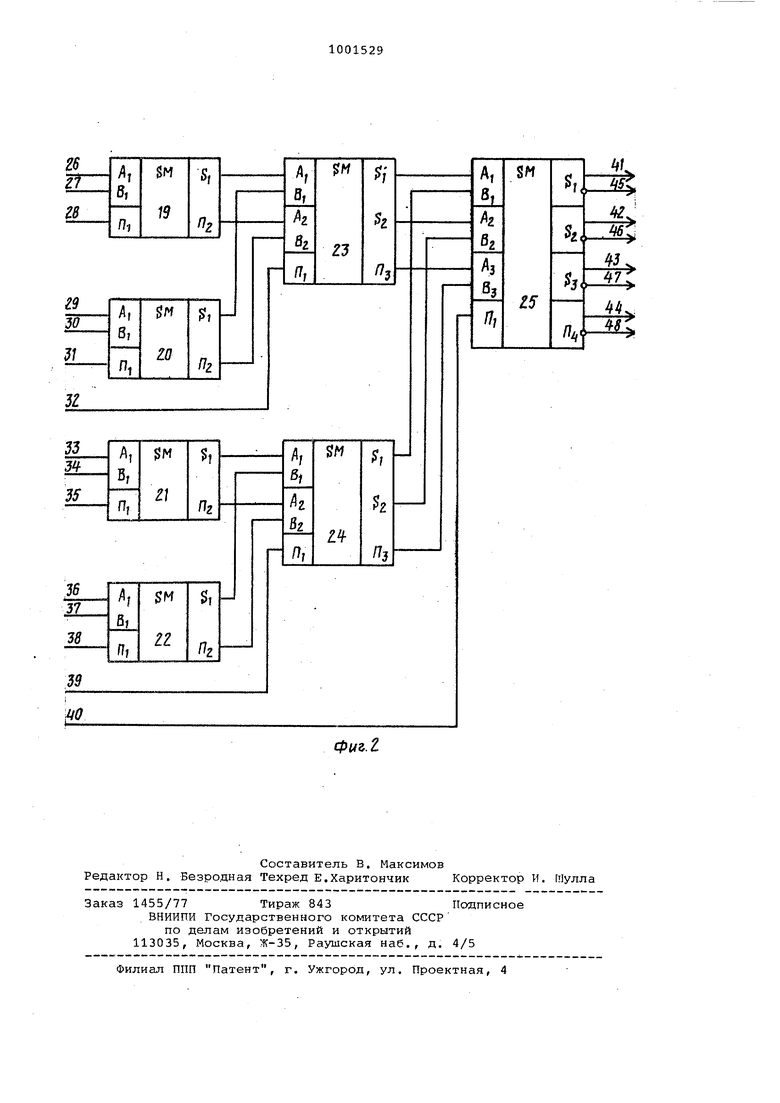

На фиг, 1 представлена структурная схема устройства для конкретного случая пятикратного резервирования на фиг. 2 - структурная схема блока сумматоров единиц на 15 входов (15 входов выбрано из соображений наибоее полного раскрытия структуры блоков) .

Устройство (фиг. 1) содержит резервируемые блоки 1-5, индикаторы i 6-10 отказов, элементы И 11-15, первый 16 и второй 17 блоки сумматоров: единиц и первый двоичный сумматор 18.

Сумматор единиц (фиг. 2) содержит вторые двоичные сумматоры 19-22 первой ступени, вторые двоичные сумматоры второй ступени 23 и 24, второй двоичный сумматор 25 третьей ступени, входы 26-40, прямые 41-44 и инверсны.е 45-48 выходы блока.

На фиг. 2 приняты следующие обозначения: Л, и В, - входы слагаемых i-ro разряда второго двоичного сумматора, выход i-го разряда второго двоичного сумматора; П.- входы переноса второго двоичного сумматора; П2-П4 - выходы переноса вторых двоичных сумматоров соответственно первой, второй и третьей ступени.

Блоки 1-5 формируют выходные сигналы j которые при наличии сигналов разрешения с выходов индикаторов 6-10 через элементы и 11-15 поступают на входы блока 16. Сигнал разрешения (сигнал логической единицы) присутствует на выходе индикатора отказа при исправности подключенного к нему резервированного блока. Блок 16 формирует двоичный код суммы единиц, поступающих на его входы с выходом элементов и 11-15. Выходной код блока 16 поступает на входы сумматора 18 с монтажным сдвигом на один разряд в сторону старших разрядов, что соответствует подаче на вход сумматора 18 удвоенного выходного кода блока 16. На инверсных выходах блока 17 формируется обратный код числа единиц на выходах индикаторов 6-10, что соответствует числу исправных резервированных блоко.в. На сумматоре 18 выполняется алгебраическое сложение двоичных кодов, поступающих с выходов блоков 16 и 17. Выходной сигнал снимается с инверсного выхода знакового разряда сумматора 18. Блоки 16 и 17 реализованы по структуре, приведенной на фиг. 2, которая для случая пятикратного резервирования выражается следующим образом. Каждый блок содержит только два сумматора 19 и 20 в первой ступени и один сумматор 23 во второй ступени, причем . входами блока являются пять любых входов из набора входов 26-32 (на два лишних входа подается сигнал логического нуля), а выходами - инверсные (для сумматора 17) или прямые (для сумматора 16) выходы сумматора 23.

Устройство работает следующим образом.

Код, формируемый блоком 17, является кодом порога срабатывания устройства. Для случая пятикратного резервирования, при отсутствии отка.завших резервированных блоков, порог срабатывания равен 5. Порог срабатывания убывает по мере отказов резервированных блоков (так, при двух отказавших блоках порог срабатывания 1равен 3) .

Код, поступающий с выхода сумматора 16, является кодом удвоенной суммы единичных сигналов на выходах элементов И. Для случая пятикратного резервирования, при отсутствии нулевых сигналов запрета от индикатор.ов отказов, этот код может принимать значение от 10 (на выходах всех резервированных блоков единичные сигналы) до О (на выходах всех резервированных блоков нулевые сигналы). По мере выхода из строя резервированных блоков сумма, формируемая блоком 16, уменьшается за счет того, что по нулевому сигналу с выхода индикатора отказа на выходе соответствующего элемента И фиксируется нулевой потенциал независимо от значения выходного сигнала отказавшего резервированного блока. Так, при двух отказавших блоках код на выходе блока 16 не превышает 6.

На сумматоре 18 выполняется сравнение (вычитание) кодов порога и удвоенной суммы единичных сигналов на выходах исправных резервированных блоков (на выходах элементов И). При наличии на выходах большинства исправных резервированных блоков нулевых сигналов результат сравнения меньше или равен О, а значение знакового разряда сумматора 18 равно 1.

При наличии на выходах большинства исправных резервированных блоков единичных сигналов результат сравнения больше О, а значение знакового разряда сумматора 18 равно 1. В обои случаях инверсное значение знаковог разряда сумматора 18 является мгясор ррванием сигналов резервируемых бло : Таким образом устройство реализу ;ет мажоритарную функцию б из 10 над кодом, поступающим на вхбды суммато ра 18, что соответствует мажоритарной функции 3 из 5 над сигналами резервированных блоков. При отказе одного из резервирова ных блоков, например блока 1, индикатор 6 формирует на своем выходе нулевой стгнал, который подается на второй вход элемента И 11, вследстгвие чего на соответствующий вход бл ка 16 поступает нулевой сигнал. Одновременно блок 17 уменьшает на единицу код порога. В этом случае устройство реализует мажоритарную функцию б из 8 над кодом, поступающ на входы сумматора 18, что соответствует мажоритарной функции 3 из 4 над сигналами исправных резервированных блоков. При отказе двух резервированных блоков устройство перестраивается на выполнение мажоритарной функции 4 из б над кодом, поступающим на входы сумматора 18, что соответству ет мажору 2 из 3 над сигналами резервированных блоков. При наличии трех отказавших блоков устройство формирует выходной сигнал по совпадению сигналов от двух резервированных блоков, а при отказе четырех блоков - по сигналу с выхода последнего исправного. Специфика блоков 1-5 .не влияет на возможность применения резервирования замещением. Предлагаемое устройство является типичной адапти рующейся избыточной структурой. При менение такой структуры, а не резер вирован ой структуры с замещением, определяется характером решаемых устройством задач. Так, избыточная адпатирующаяся структура, в отличие от резервирЪванной структуры с замещением, не критична к сбоям из фиксируемых индикаторами отказов (при условии малой вероятности одно временных сбоев большинства блоков) При сбоях, которые фиксируются индикаторами отказов, устройство работает так. А. На выходах двух из пяти блоков присутствуют ложные сигналы О На выходах блока 16 формируется код 3, который за счет сдвига увеличи|Вается в два раза и поступает на входы сумматора 18 с 00110 (двоичны код 6) на выходах блока 17 формируется инверсный код 3, который так же поступает на входы сумматора 18 00011 (прямой код 3), 11100 (инверс ный код 3). Сумматор 18 осуществляет сложение .этих кодов .00110 , знаковый разряд Результат сложения положительный и значение знакового разряда нулевое, а инверсное значение F единичное, т.е, на выходе устройства сигнал логической 1, что соответствует значению сигналов большинства исправных блоков. Б. На выходах двух из пяти блоков присутствуют ложные сигналы 1. На выходах сумматора 16 код О,сдвинутый на один разряд, он поступает на входы сумматора 18 - 00000 (дво,ичный код О)J на выходах сумматора Т.7 - инверсный код 3-11100 (инверсный код 3), на выходе сумматора 18 знаковый разряд Результат сложения отрицательный ,и значение знакового разряда единичное, а инверсное - нулевое, т.е, на выходе устройства сигнал логического О, что соответствует значению сигналов большинства исправных блоков. В. На выходах одного из блоков присутствует ложный сигнал О. На выходах сумматора 16 код 4, который со сдвигом на один разряд поступает на входы сумматора 18 - 01000 (двоичный код 8); на выходах суммэтора 17 инверсный код 4 - 11011 (инверсный код 4Х; на выходах сумматора 18 11011 знаковый разряд рощ : Результат сложения положительный, инверсное значение знакового разряда единичное, что соответствует значению сигналов большинства исправньАс блоков. При сбоях,которые не фиксируют индикаторы отказов, устройство ра1ботает как обычное мажоритарное устройство. На выходах двух из пяти блоков ложные сигналы О, на выходах сумматора 16 код 3, который со сдвигом на один разряд поступает на входы сумматора 18 - 00110 двоичный код б); на выходах сумматора 17 инверсный код 5 - 11010 инверсный код 5 ) ; на выходах сумматора 18 .00110 11010 знаковый разряд . J30000 Результат сложений положительный, гинверсное значение знакового разря|да единичное, что соответствует значению сигналов большинства блоков.

При сбоях, фиксируемых и не фик.сируемых индикаторами отказов на выходах двух из пяти блоков-ложные

,сигналы О и неисправность этих блоков зафиксирована индикаторами отказов, кроме того, на выходе еше одного бока- ложный сигнал причем его неисправность не зафиксиро.вана индикатором; отказа. На выходах

блока 16 - код 2, его удвоенное значение подается на вход сумматора 18-00100 (двоичный код 4), на выходах блока 17 - инверсный код

3 - 11100 (инверсный код 3)/ на выходах сумматора 18 00100 11100 знаковый разряд

066ЙО , ....

Результат сложения положительный инверсное значение знакового разряд единичное, что соответствует значению большинства исправных блоков.

Таким образом, затраты на реализаций многократного резервирования в предлагаемом устройстве существен .но снижены.

Формула изобретения 1. Мажоритарно-резервированное устройство, содержащее резервируемы блоки, выходы которых подключены к индикаторам отказов, отличающееся тем, что, с целью упрощения устройства, оно содержит первый двоичный сумматор, два блока сумма.торов единиц и элементы И, выходы крторых подключены к входам первого блока сумматоров единиц, первые входы - к выходам соответствующ,их резервируемых блоков, а вторые входы к выходам соответствующих индикаторов отказов и к входам второго блока . .сумматоров единиц, соединенного ин5 версным выходом с вторым входом первого двоичного сумматора, инверотый выход которого подключен к выходу устройства.

Q 2. Устройство по п. 1, отличающееся тем, что каждый из БЛОКОВ сумматоров единиц выполнен . в виде п-ступенчатой пирамиды вторых двоичных сумматоров, причем разряд. ность вторых двоичных сумматоров I-и ступени равна i, количество вторых двоичных сумматоров i-й ступени не превьлиает входы вторых двоичных сумматоров первой ступени совместно с входами переноса всех вторых

0 двоичных сумматоров соединены с входами блока, выходы сумм и переносов вторых двоичных сумматоров каждой из первых (п-1) ступеней поразрядно подключены к входам вторых двоичных

5 сумматоров последующих ступеней, а прямые и инверсные выходы второго ДВОИЧНОГО сумматора п-ой ступени соединены соответственно с прямыми и инверсными выходами блока.

0 Источники информации,

принятые во внимание при экспертизе

fпрототип).

UD

J

«VI

,Т ,2Г

7

i

Фиъ.1

Авторы

Даты

1983-02-28—Публикация

1979-12-07—Подача