(54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВРЕМЕН-Й ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ДВИЖЕНИЯ ПРОВОДОВ И КАБЕЛЕЙ | 1999 |

|

RU2170436C2 |

| Корреляционный дискриминаторВРЕМЕННОгО СдВигА | 1979 |

|

SU817732A1 |

| КОРРЕЛЯЦИОННЫЙ РАСХОДОМЕР | 1991 |

|

RU2010167C1 |

| Коррелятор с аппроксимацией двухпараметрическими моделями | 1977 |

|

SU643906A1 |

| Устройство для оценки интервала корреляции | 1983 |

|

SU1129628A1 |

| Корреляционное устройство для определения импульсной переходной функции объекта | 1982 |

|

SU1096665A1 |

| Аналого-цифровой коррелятор | 1981 |

|

SU1019462A1 |

| УСТРОЙСТВО ЗОНДИРОВАНИЯ СТРОИТЕЛЬНЫХ КОНСТРУКЦИЙ | 2012 |

|

RU2533311C2 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР | 2002 |

|

RU2227321C2 |

| Устройство для контроля параметров процесса бурения | 1986 |

|

SU1461882A1 |

Изобретение относится к измерительной технике и может быть использовано при исследовании линий задержки .

Известно устройство измерения в емени задержки, содержащее блок регулируемой задержки, блок умножения и фильтр 1.

Известное устройство характеризуется низким быстрсщействи 4.

.Наиболее близким к предлагаемому устройству является устройство, содержащее блок регулируемой задержки, блок постоянной задержки, два блока умножения, два фильтра, блок вычитания и усилитель, причем первый вход устройства совмещен с входом блока регулируемой задержки, вькод которого соединен с первым входом первого и через блок постоянной задержки с первым входом второго блоков умножения, вторые входы которых через исследуемую линию задержки подключены к входу устройства, а выходы блоков умножения через соответствующие Фильтры, блок вычитания и усилитель соединены с управляющим входом блока регулируемой задержки (2.

Устройство вычисляет взаимно корреляционную функцию входных сигналов

и взаимную корреляционную функцшо, сдвинутую относительно первой на постоянную величину. По сигналу сравнения, этих функций перестраивается регулируемая линия задержки, величина которой в состоянии равновесия характеризует запаздывание сигнала, прошедшего через линию задержки.

Однако наличие блока регулируемой

1Q задержки черезмерно усложняет известное устройство.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем,

is что в устройство, содержащее блок постоянной задержки, блок вычитания, два блока умножения и два фильтра, причем вход блока постоянной задеркки подключен к входу устройства, а

20 выходы блоков умножения соединены с входами соответствующих фильтров, введены блок вычитания и блок деления, причем первый вход дополнительного блока вычитания соединен с выходом блока постоянной задержки,

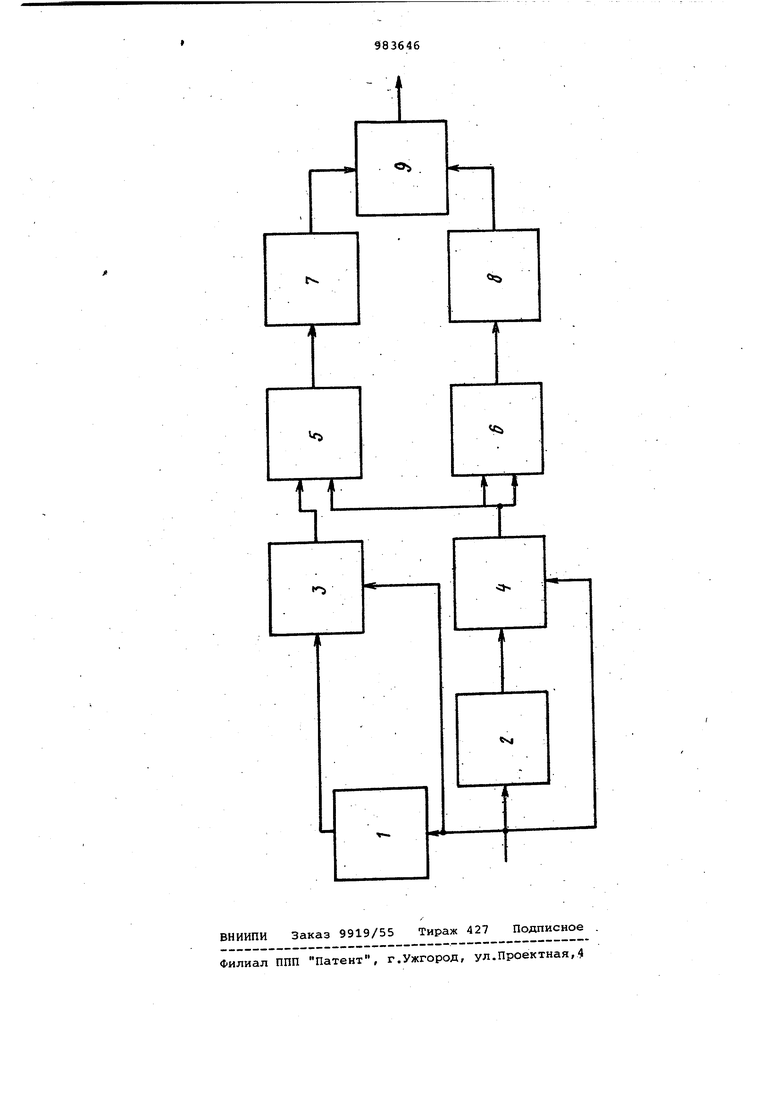

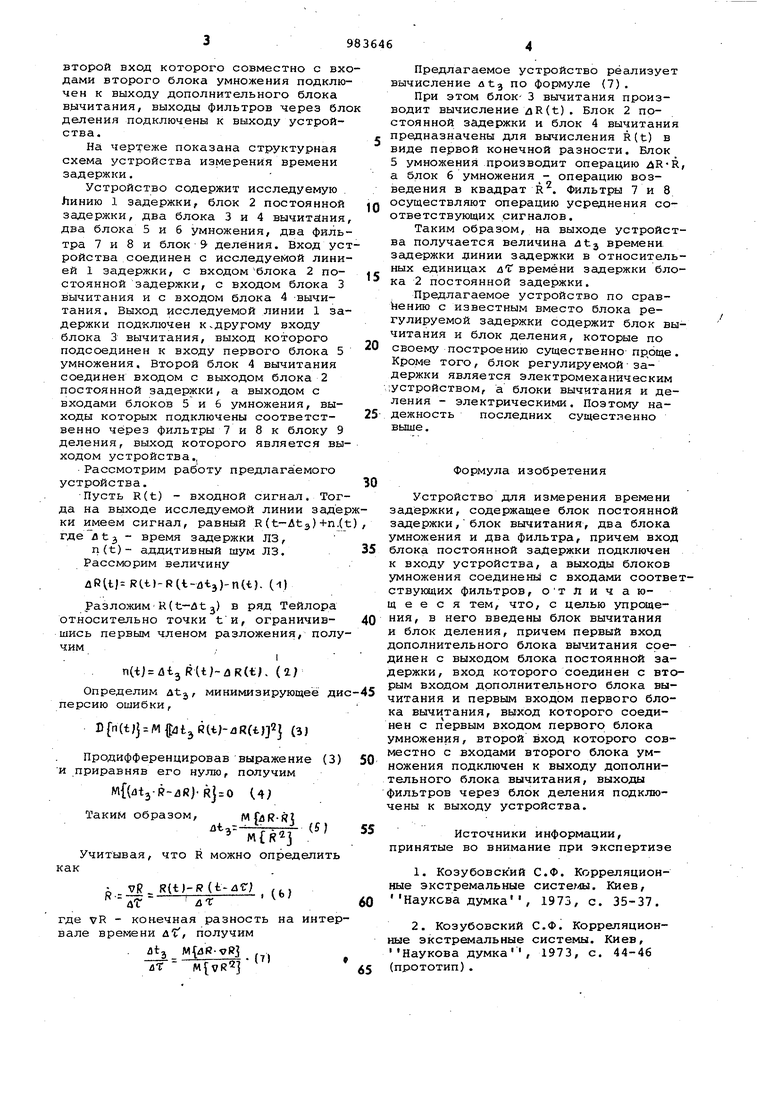

вход которого соединен с вторым входом дополнительного блока вычитания и первым входом liepBoro блока вычитания,, выход которого соединен с первым входом первого блока умножения. второй вход которого совместно с вх дами второго блока умножения подклю чен к выходу дополнительного блока вычитания, выходы фильтров через бл деления подключены к выходу устройства, На чертеже показана структурная схема устройства измерения времени задержки. Устройство содержит исследуемую Линию 1 задержки, блок 2 постоянной задержки, два блока 3 и 4 вычитания два блока 5 и 6 умножения, два филь тра 7 и 8 и блок 9 деления. Вход ус ройства соединен с исследуемой лини ей 1 задержки, с входом блока 2 постоянной задержки, с входом блока 3 вычитания и с входом блока 4 -вычитания. Выход исследуемой линии 1 за держки подключен к.другому входу блока 3 вычитания, выход которого подсоединен к входу первого блока 5 умножения. Второй блок 4 вычитания соединен входом с выходом блока 2 постоянной задержки, а выходом с входами блоков 5 и 6 умножения, выходы которых подключены соответственно через фильтры 7 и 8 к блоку 9 деления, выход которого является вы ходом устройства,, Рассмотрим работу предлагаемого устройства, Пусть R(t) - входной сигнал. Тог да на выходе исследуемой линии заде ки имеем сигнал, равный R (t-Atj)+n.( где дЪз - время задержки ЛЗ, п(t)- аддитивный шум ЛЗ, Рассморим величину ARit|-RCt)-R(.i-at3)-n(b разложимR(t-At3) в ряд Тейлора относительно точки tH, ограничившись первым членом разложения, полу чим nC-tjrdtjRUb KCtb (а; Определим utj, минимизирующее ди Персию ошибки, D|;n(tj| M{{kjtjR(t;-dR(t)2} (3) Продифференцировав выражение (3) И приравняв его нулю, получим Mfldtj-R-dRj-RJzO (4; Таким образом, яА - i -irrFf Учитывая, что R можно определить VI, R(t)-ff(t-dc; ,(,, N- , 4Тл (. где VR - конечная разность на интер вале времени ut, получим dtj M{dR--gRj . ТГ M{VR2 Предлагаемое устройство реализует вычисление atg по формуле (7), При этом блок- 3 вычитания производит вычисление лR(t), Блок 2 постоянной задержки и блок 4 вычитания предназначены для вычисления R(t) в виде первой конечной разности. Блок 5 умножения производит операцию R-R/ а блок 6 умножения - операцию возведения в квадрат R, фильтры 7 и 8 осуществляют операцию усреднения соответствующих сигналов. Таким образом, на выходе устройства получается величина dtj времени задержки задержки в относительных единицах лТ времени задержки блока 2 постоянной задержки. Предлагаемое устройство по срав ению с известным вместо блока регулируемой задержки содержит блок вычитания и блок деления, которые по своему построению существенно проще. Кроме того, блок регулируемойзадержки является электромеханическим устройством, а блоки вычитания и деления - электрическими. Поэтому надежность последних суаестпенно выше, Формула изобретения Устройство для измерения времени задержки, содержащее блок постоянной задержки,блок вычитания, два блока умножения и два фильтра, причем вход блока постоянной задержки подключен к входу устройства, а выходы блоков умножения соединены с входами соответствующих фильтров, оТ л и ч а ющ е е с я тем, что, с целью упрощения, в него введены блок вычитания и блок деления, причем первый вход дополнительного блока вычитания соединен с выходом блока постоянной задержки, вход которого соединен с вторым входом дополнительного блока вычитания и первым входом первого блока вычитания, вьаход которого соединен с первым входом первого блока умножения, второй вход которого совместно с входами второго блока умножения подключен к выходу дополнительного блока вычитания, выходы фильтров через блок деления подключены к выходу устройства. Источники информации, принятые во внимание при экспертизе 1.Козубовский С.Ф, Корреляционные экстремальные систе/лл, Киев, Науксва думка , 1973, с, 35-37, 2,Козубовский С,Ф. Корреляционные экстремальные системы, Киев, Наукова думка , 1973, с, 44-46 (прототип).

fJ

О

Авторы

Даты

1982-12-23—Публикация

1981-07-23—Подача