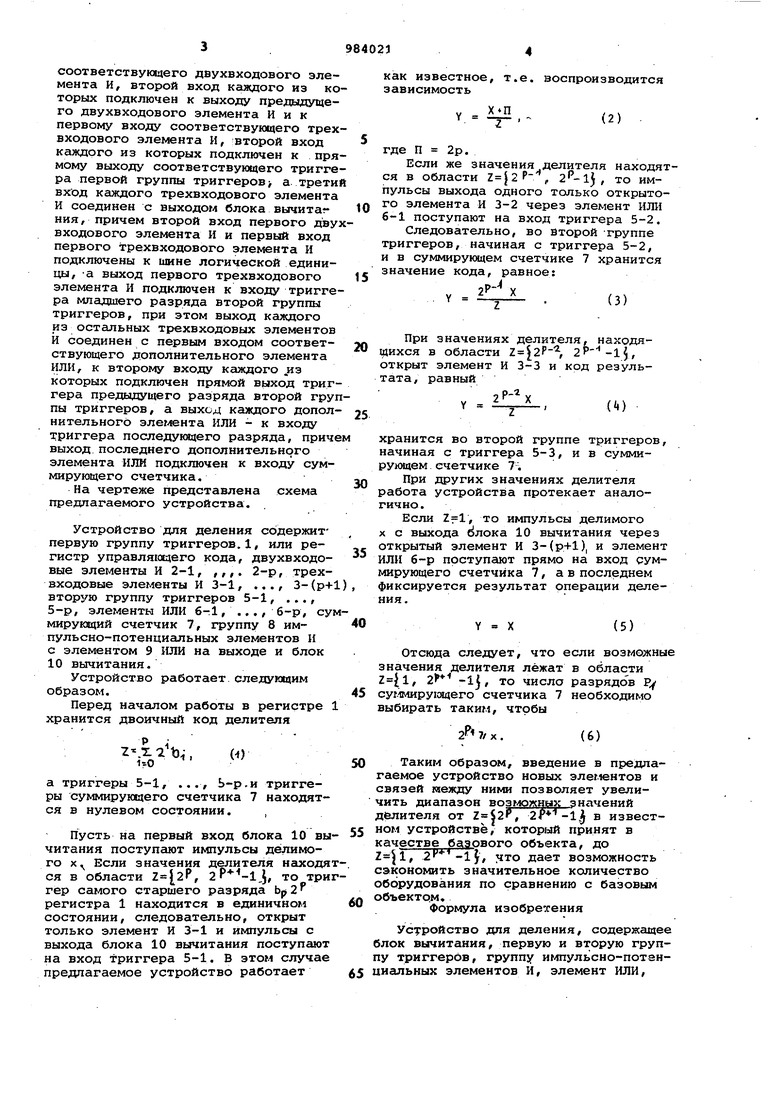

соответствуквдего двухвходового элемента И, второй вход каждого из ко торых подключен к выходу предыдущего двухвходового элемента И и к первому входу соответствующего трех входового элемента И, второй вход каждого из которых подключен к пря мому выходу соответствующего тригге ра первой группы триггеров а трети вход каждого трехвходового элемента И соединен с выходом блока вычитаг ния, причем второй вход первого дву входового элемента И и первый вход первого трехвходового эле1и1ента И подключены к шине логической единицы, -а выход первого трехвходового элемента И подключен к входу тригге ра младшего разряда второй группы триггеров, при этом выход каждого из остальных трехвходовых элементов И соединен с первым входом соответствующего дополнительного элемента ИЛИ, к второму входу каждого .из которых подключен прямой выход триг гера предыдущего разряда второй гру пы триггеров, а выход каждого допол нательного элеглента ИЛИ - к входу триггера последукхцего разряда, прич выход последнего дополнительного элемента ИЛИ подключен к входу суммирующего счетчика. На чертеже представлена схема предлагаемого устройства. Устройство для деления содержитпервую группу триггеров.1, или регистр управляющего кода, двухвходовые элементы И 2-1, ,,,. 2-р, трехвходовые элементы И 3-1, ..., 3-(р+ вторую группу триггеров 5-1, ..., 5-р, элементы ИЛИ 6-1, .,., б-р, су мирующий счетчик 7, группу 8 импульсно-потенциальных элементов И с элементом 9 ИЛИ на выходе и блок 10 вычитания. Устройство работает следующим образом. Перед началом работы в регистре хранится двоичный код делителя а триггеры 5-1, ..., Ь-р.и триггеры суммирующего счетчика 7 находятся в нулевом состоянии. , Пусть на первый вход блока 10 вы читания поступают импульсы делимого х Если значения делителя находя ся в области , J, то три гер самого старшего разряда Ьр 2 регистра 1 находится в единичном состоянии, следовательно, открыт только элемент И 3-1 и импульсы с выхода блока 10 вычитания поступают на вход триггера 5-1. В этом случае предлагаемое устройство работает как известное, т.е. воспроизводится зависимость где П 2р. Если же значения делителя находятся в области , 2-l5, то импульсы выхода одного только открытого элемента И 3-2 через элемент ИЛИ 6-1 поступают на вход триггера 5-2. Следовательно, во второй группе триггеров, начиная с триггера 5-2, и в суммирующем счетчике 7 хранится значение кода, равное: При значениях делителя, находя111ИХСЯ в области Z |2P-, , открыт элемент И 3-3 и код результата, равный Р- X Y V, , (i.) хранится во второй группе триггеров, начиная с триггера 5-3, и в суммирующем счетчике 7. При других значениях делителя работа устройства протекает аналогично. Если Zfl, то импульсы делимого X с выхода ёлока 10 вычитания через открытый элемент И 3-(р+1)| и элемент ИЛИ б-р поступают прямо на вход суммирующего счетчика 7, а в последнем фиксируется результат операции деления , Y X(5) Отсюда следует, что если возможные значения делителя лежат в области , -1 j , то число разрядов Ру сугФшругадего счетчика 7 необходимо выбирать таким, чтобы 2 7/ X. Таким образом, введение в предлагаемое устройство новых элементов и связей между ними позволяет увеличить диапазон возм22 аШ1 Эначений делителя от , -1,J в известном устройстве, который принят в качестве базового объекта, до , -ij что дает возможность сэкономить значительное количество оборудования по сравнению с базовым объектом. Формула изобретения Устройство для деления, содержащее блок вычитания, первую и вторую группу триггеров, группу импульсно-потэнциальных элементов И, элемент ИЛИ,

ВЫХОД которого подключен к входу блока вычитания, а входы,- к выходам импульсно-потенциальных элементов И, управля1оий1е входы которых соединены с прямыми выходами триггеров первой группы, а сигнальтде входы - с прямыми выходс1ми триггеров второй группы, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены двухвходовые элементы И, трехвходрвые элементы И, суммирующий счетчик и дополнительные элементы ИЛИ, причем инверсный выход каждого триггера первой группы триггеров, кроме триггера младшего разряда; подключен к первому входу соответствующего двухвходового Э5|емента И, второй вход каждого из которых подключен к выходу предыдущего двухвходового элемента И . и к первому входу соответствующего трехвходового элемента И, второй вход каждого из которых подключен к прямому выходу соответствующего триггера первой группы триггеров , а третий вход каиждого трехвходового элемента И соединен с выходом блока вычитания, причем второй вход

первого двухвходового элемента И и первый вход первого трехвходового элемента И подключены к шине логической едщницы, а выход первого трехвходово.го элемента И подключен к входу .триггера tлaдшeгo разряда второй группы триггеров, при этом выход каходого из остальных трехвходовых элементов И соединен с первым входом соответствующего дополнительного

элемента ИЛИ, к второму йходу каждого из которых подключен прямой выход триггера предыдущего разряда втор.ой группы триггеров, а выход каждого дополнительного элемента

ИЛИ - к входу триггера последующего разряда, причем выход последнего дополнительного элемента ИЛИ подключен, к входу суммирующего счетчика.

Источники информации,

принятые во внимащ1е при экспертизе

1.Авторское свидетельство СССР

№ 398960, кл. Н 03 К 5/156, 11.11.71.

2.Мельников А.А. и др. Обработка частотных и временныхимпульсных

сигналов. М., Энергия, 1976, с. 6566.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ ПОМЕХОУСТОЙЧИВОСТИ ПРИЕМНИКА ВИДЕОСИГНАЛОВ | 1993 |

|

RU2048680C1 |

| Устройство для деления | 1984 |

|

SU1226444A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМ МАССОВОГО ОБСЛУЖИВАНИЯ | 2011 |

|

RU2465647C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1182514A1 |

| Измеритель амплитудно-частотных характеристик | 1980 |

|

SU951184A1 |

| Устройство для исправления арифметических ошибок | 1978 |

|

SU679985A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| АССОЦИАТИВНЫЙ ВЫЧИСЛИТЕЛЬ СМЕЩЕНИЯ ЦЕНТРА ТЕКУЩЕГО ИЗОБРАЖЕНИЯ ОТ ЦЕНТРА ЭТАЛОННОГО | 1991 |

|

RU2029358C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ПРОГРАММНО-УПРАВЛЯЕМОЙ СРЕДЫ | 1997 |

|

RU2132081C1 |

Авторы

Даты

1982-12-23—Публикация

1981-07-20—Подача