Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах, системах для ассоциативной обработки массивов информации, в цифровых системах поиска информации и в системах технического зрения.

Известно устройство для матричной обработки данных [1], содержащее блок памяти опорных признаков, блок сравнения, блок памяти учетных данных, причем выход блока памяти опорных признаков подключен к первому входу блока сравнения, второй вход которого подключен к выходу блока памяти учетных данных. За счет перечисленных блоков и связей между ними обеспечивается формирование r двумерных таблиц в соответствии с заданными опорными признаками.

Недостатками данного устройства являются невысокое быстродействие, обусловленное последовательной обработкой опорных признаков, невозможность определения тех матриц данных, степень совпадения которых с матрицами опорных признаков задана некоторым порогом, а также неспособность автоматической настройки на максимальное значение порога.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для ассоциативной обработки двумерных массивов [2] , содержащее блок памяти опорных признаков, блок памяти учетных данных, блок сравнения, блок буферной памяти, блок распределения синхросигналов, m пороговых блоков строки на n входов и n выходов каждый, m регистров-мультиплексоров строки, m-разрядный параллельный регистр без сдвига, пороговый блок матрицы на m входов и m выходов, регистр-мультиплектор матрицы.

Однако данное устройство не позволяет провести неоднократное сравнение матрицы размером m x n текущего изображения с матрицей размером MxN эталонного изображения, выявить при этом максимальный результат совпадений и положение участка размером m x n в матрице MxN (причем M>m, N>n), имеющего это максимальное совпадение.

Цель изобретения - расширение функциональных возможностей - заключается в выявлении того участка m x n в эталонной матрице MxN, степень совпадения которого с матрицей m x n текущего изображения имеет максимальное значение, и в вычислении координат центра этого участка.

Цель достигается тем, что в вычислитель, содержащий блок памяти текущего изображения емкостью m x n одноразрядных двоичных чисел, блок памяти эталонного изображения емкостью MxN одноразрядных двоичных чисел, блок сравнения, введены блок подсчета числа совпадений, блок выбора максимального числа совпадений, блок управления считыванием информации, первый регистр для хранения координат смещения по Х, второй регистр для хранения координат смещения по Y, первая группа ключей из m x n двухвходовых элементов И, вторая и третья группы ключей из 1+]log2((M-m)+1)[ и 1+]log2((N-n)+1[ соответственно двухвходовых элементов И.

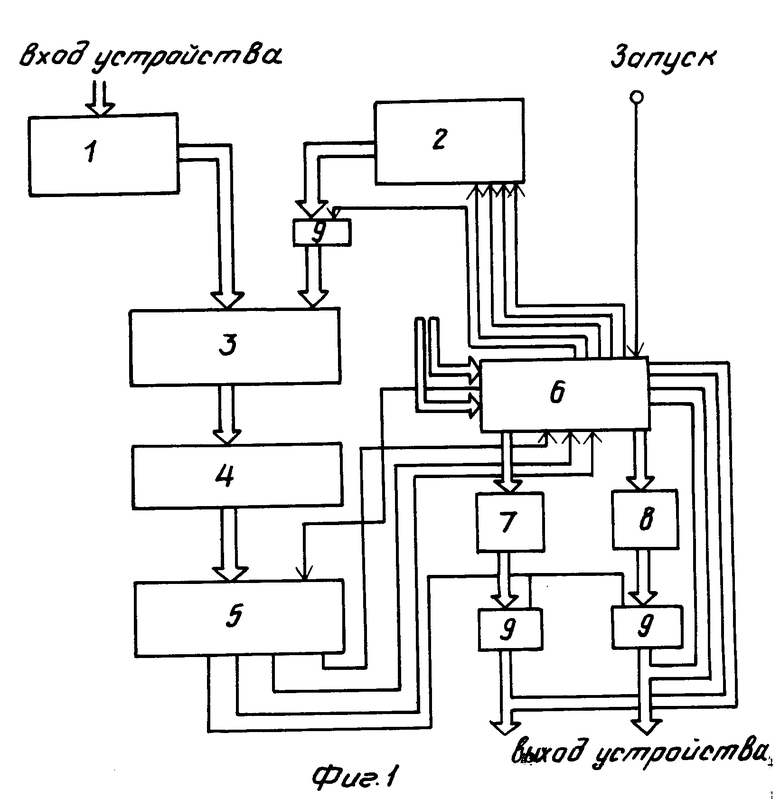

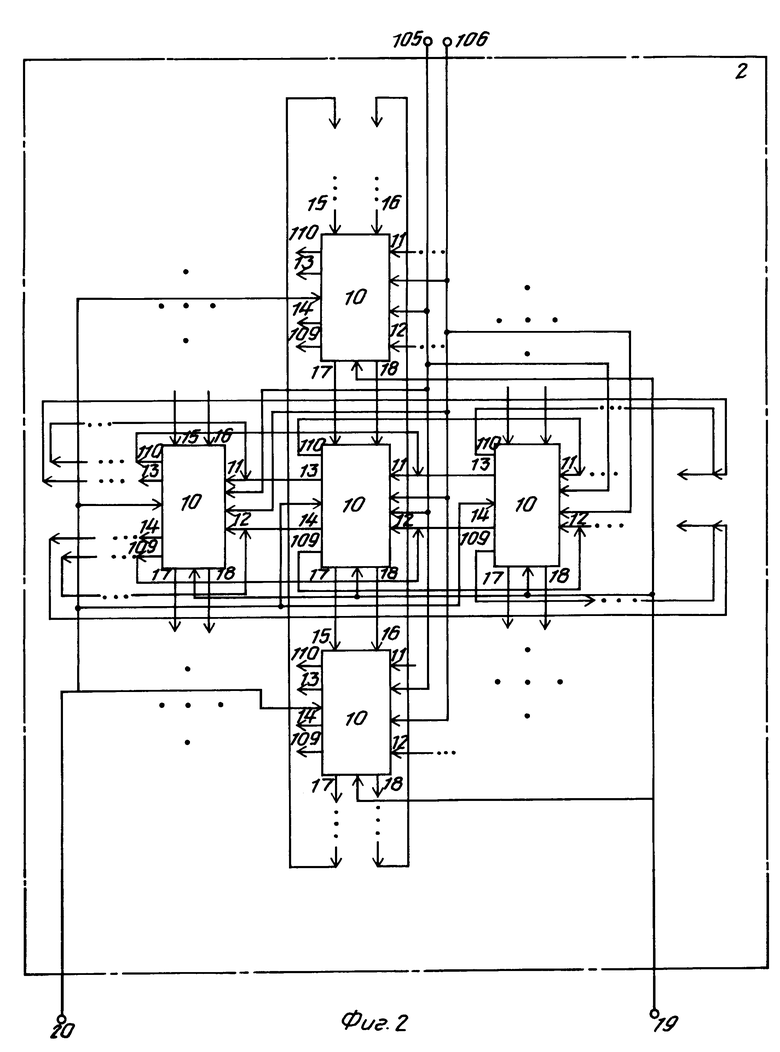

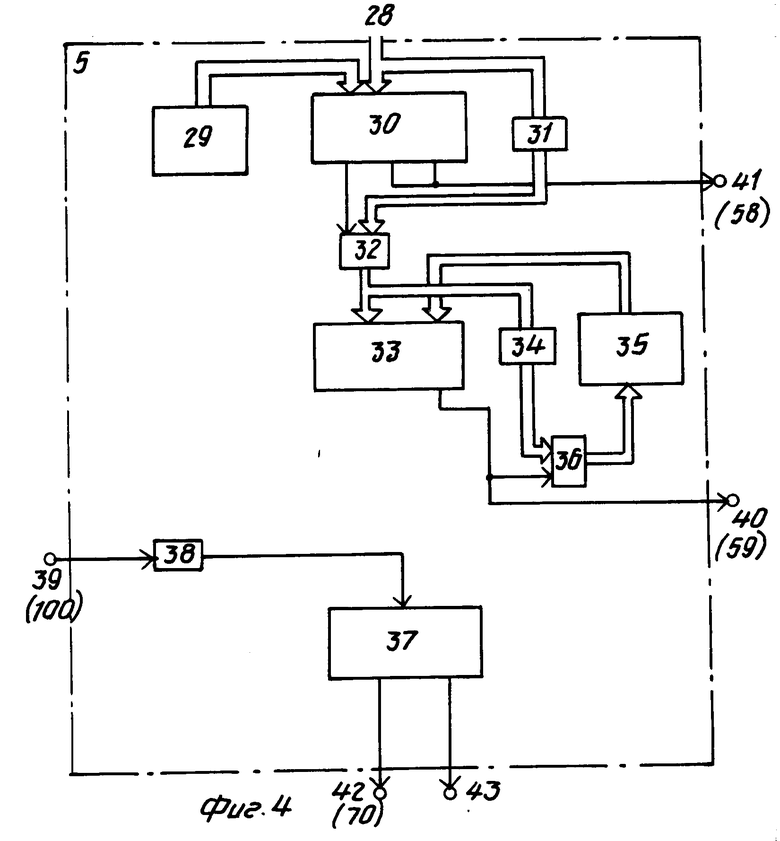

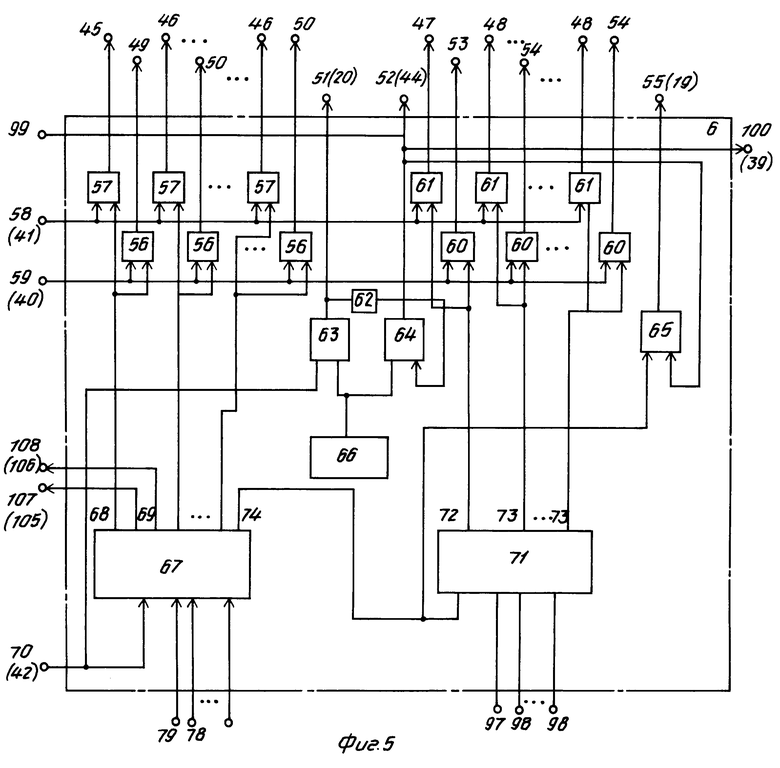

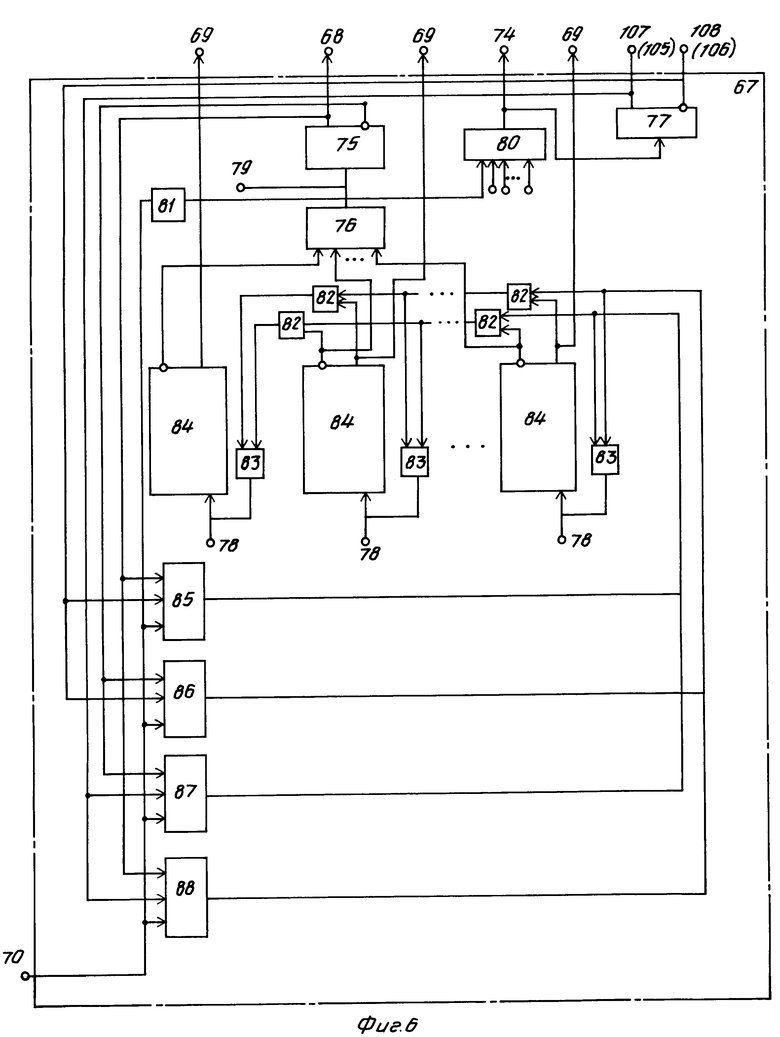

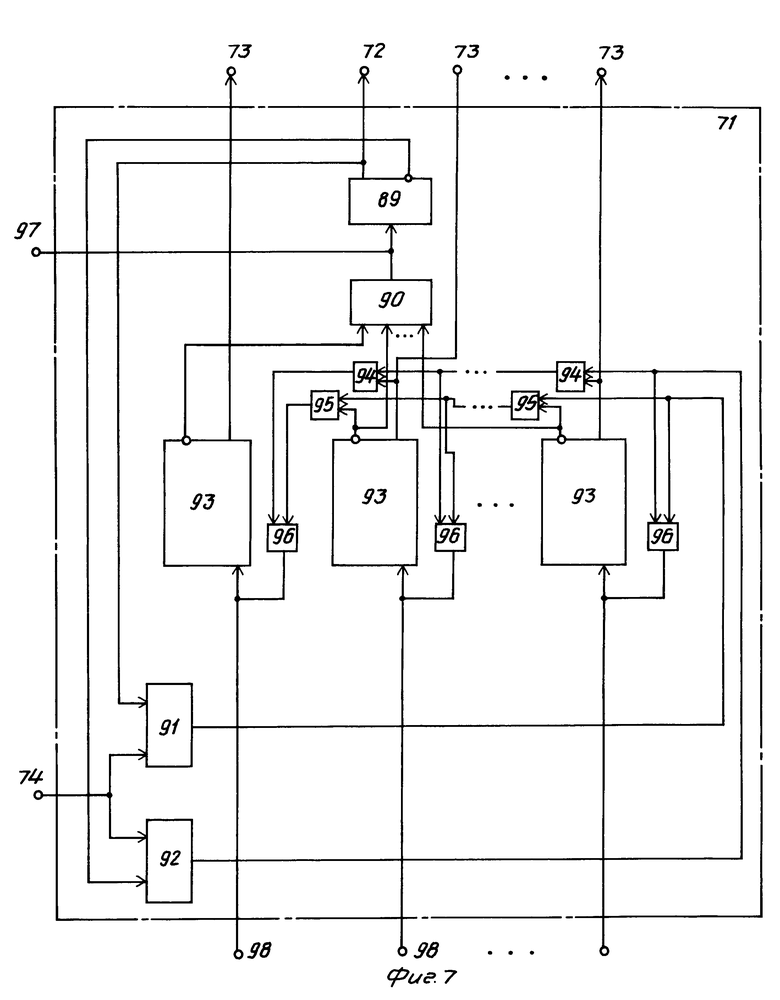

На фиг.1 приведена структурная схема вычислителя; на фиг.2 - структурная схема блока памяти эталонного изображения; на фиг.3 - функциональная схема элемента памяти этого блока; на фиг.4 - структурная схема блока выбора максимального числа совпадений; на фиг.5 - структурная схема блока управления считыванием информации; на фиг. 6 - структурная схема счетчика координат смещения по горизонтали (Х); на фиг.7 - структурная схема счетчика координат смещения по вертикали (Y).

Ассоциативный вычислитель смещения центра текущего изображения от центра эталонного содержит (фиг.1) блок 1 памяти текущего изображения емкостью m x n разрядов, блок 2 памяти эталонного изображения емкостью MxN, блок 3 сравнения, блок 4 подсчета числа совпадений, блок 5 выбора максимального числа совпадений, блок 6 управления считыванием информации, регистры 7 и 8 для хранения координат смещения по Х и Y соответственно, три группы 9 ключей, первая из которых предназначена для считывания информации из блока памяти эталонного изображения в блок сравнения, вторая и третья группы по 1+] log2((M-m)+1)[ и 1+] log2((N-n)+1)] ключей - для считывания координат смещения из регистров 7 и 8 соответственно.

Блок 2 памяти эталонного изображения (фиг.2) имеет в своем составе MxN элементов 10 памяти с входами 11 и 12, осуществляющими прием информации из соседнего по горизонтали (i, j + 1) элемента памяти, и выходами 13 и 14, осуществляющими передачу информации из данного (i, j) элемента памяти в следующий за ним по горизонтали (i, j-1) элемент памяти. Входы 15 и 16 осуществляют перенос информации из соседнего по вертикали (i-1, j) элемента памяти в данный (i, j), а с помощью выходов 17 и 18 происходит перенос информации из данного (i, j) элемента памяти в соседний (i+1, j) элемент памяти. Вход 19 блока памяти эталонного изображения управляет сдвигом информации, записанной в блоке, в вертикальном направлении, а вход 20 - сдвигом в горизонтальном направлении.

Элемент 10 памяти (фиг.3) состоит из вентилей 21, пропускающих управляющие импульсы на синхровход триггера 22, ключей (элементы И) 23 - 27, причем ключ 25 входит в состав первой группы 9 ключей.

Через вход 28 информация подается в блок 5 выбора максимального числа совпадений (фиг.4), который состоит из регистра 29 хранения максимально возможного числа совпадений, компаратора 30, элемента 31 задержки с временем задержки, равным времени срабатывания компаратора 30, элемента И 32, компаратора 33 на ]log2(m x n)[ разрядов по каждой группе входов, элемента 34 задержки, с временем задержки, равным времени срабатывания компаратора 33, асинхронного регистра 35 для хранения максимального числа совпадений, элемента И 36, пересчетной схемы 37 с коэффициентом пересчета [(M-m)+1]x[(N-n)+1], элемента 38 задержки, время задержки в котором равно времени сравнения массивов. Вход 39 через элемент 38 задержки соединен с входом схемы 37. С выхода 40 подается сигнал для записи информации в регистры 7 и 8, с выхода 41 подается сигнал для вывода координат смещения из блока управления считыванием информации на выходы вычислителя, с выхода 42 поступает сигнал для приращения координаты смещения в горизонтальном направлении, с выхода 43 подается сигнал на считывание информации из регистров 7 и 8 на выходы вычислителя.

Вход 44 (фиг.3) предназначен для обеспечения считывания информации из "окна" блока 2 памяти эталонного изображения.

Блок 6 управления считыванием информации (фиг.5) имеет выходы 45-48, соединенные в выходами вычислителя, причем выходы 45 и 47 - выходы знаковых разрядов координат Х и Y соответственно, а выходы 46 и 48 - выходы значащих разрядов координат Х и Y соответственно. Выходы 49, 50 - выходы соответственно знаковых и значащих разрядов координаты Х смещения по горизонтали для записи ее в регистр 7. Выход 51 управляет сдвигом информации в блоке 2 в горизонтальном направлении. Выход 52 управляет считыванием информации из блока 2. Выходы 53 и 54 являются выходами знакового и значащих разрядов соответственно координаты смещения по вертикали Y для записи ее в регистр 8. Выход 55 управляет сдвигом информации в блоке 2 в вертикальном направлении. Блок 6 управления считыванием информации состоит из групп ключей 56 и 57, к которым подключены управляющие входы 59 и 58, групп ключей 60 и 61 с управляющими входами 59 и 58 соответственно, элемента 62 задержки, время задержки в котором равно времени сдвига информации в блоке 2, трех двухвходовых управляющих элементов И 63, 64 и 65, генератора 66 импульсов, реверсивного счетчика 67, служащего для подсчета координат Х смещения в горизонтальном направлении, с выходом 68 знакового разряда, выходом 69 значащих разрядов, управляющим входом 70, 1+]log2((N-n)+1)]-разрядного реверсивного счетчика 71, служащего для подсчета координат смещения в вертикальном направлении с выходами знакового разряда 72 и значащих разрядов 73, управляющим входом 74.

Счетчик 67 (фиг. 6) содержит триггер 75 знакового разряда, ]log2((M-m)+1)[-входовый элемент И 76, управляющий триггер 77. Дополнительные входы 78 и 79 предназначены для записи в счетчик 67 начального состояния. В состав счетчика 67 входят также ]log2((M-m)+1)[-входовый элемент И 80, элемент 81 задержки (tзад=tсрабатсч. 67), группы из 2х(]log2((M-m)+1)[-1) элементов И 82 и ]log2((M-m)+1)[ элементов ИЛИ 83, обеспечивающие работу счетчика в различных режимах, ]log2((M-m)+1)[ триггеров 84 значащих разрядов, трехвходовые элементы И 85-88, обеспечивающие выбор режима работы счетчика.

Счетчик 71 (фиг. 7) состоит из триггера 89 знакового разряда, (] log2((N-n)+1)[-входового элемента И 90, двухвходового элемента И 91 и элемента И 92, обеспечивающих выбор режима работы счетчика, ]log2((N-n)+1)[-триггеров 93 значащих разрядов, группы из ]log2((N-n)+1)[-1 двухвходовых элементов И 94, ] log2((N-n)+1)[-1) двухвходовых элементов И 95 и ]log2((N-n)+1)[ двухвходовых элементов ИЛИ 96, обеспечивающих работу счетчика. Входы 97 и 98 предназначены для записи начального состояния в счетчик 71.

Вход 99 блока 6 (фиг.5) предназначен для первоначального считывания информации из блока 2 памяти эталонного изображения. Выход 100 блока 6 (фиг. 5) соединен с управляющим входом блока выбора максимального числа совпадений для перевода схемы 37 пересчета в следующее состояние.

Двухвходовые элементы И 101 и 102, входящие в состав элемента 10 памяти (фиг. 3) предназначен для выбора направления смещения информации в блоке 2 памяти эталонного изображения, а аналогичные элементы И 103 и 104 - для считывания информации из (i,j)-го элемента памяти в (i, j+1)-й. На входы 105 и 106 поступают сигналы с управляющих выходов 107 и 108 блока 6 управления считыванием информации. Через выходы 109 и 110 информация смещается слева направо, т.е. из (i, j)-го элемента 10 памяти в (i, j+1)-й.

В качестве блока 1 памяти текущего изображения могут быть использованы n m-разрядных регистров для хранения и считывания информации. Блок 3 сравнения реализован аналогично блоку сравнения в прототипе, за исключением того, что выходы комбинационных полусумматоров инвертированы.

Вычислитель работает следующим образом.

При поступлении управляющего сигнала запуска вычислителя на вход 99 (фиг. 5) блока 6 управления считыванием информации он передается на входы первой группы 9 ключей (фиг.4), разрешающих считывание информации из блока 2 памяти эталонного изображения на входы блока 3 сравнения. Работа блока 3 аналогична работе блока сравнения прототипа, причем на выходах комбинационных полусумматоров, выполняющих функции сравнивающих элементов, при совпадении кодов появляется сигнал "1", при несовпадении - "0".

Далее эти сигналы поступают на входы блока 4 подсчета числа совпадений. Данный блок суммирует поступившее на его входы количество "1". Далее полученное число количества совпадений поступает на входы 28 блока 5 выбора максимального числа совпадений и подается на вторую группу входов логического компаратора 30, где сравнивается с максимально возможным числом совпадений, хранящимся в регистре 29, выходы которого соединены с первой группой входов логического компаратора 30. Если эти числа равны, то на выходе 41 формируется сигнал, поступающий на вход 58 блока 6 управления считыванием информации, разрешающий считывание координат смещения на выходы вычислителя. Если подсчитанное число количества совпадений меньше максимально возможного числа совпадений, то на входы группы из ]log2(m x n)[ двухвходовых элементов И 32 поступает сигнал с компаратора 30, разрешающий прохождение информации (количества совпадений), поступившей на входы 28 и прошедшей группу из элементов 31 задержки. Далее эта информация подается на первую группу входов логического компаратора 33. На вторую группу входов этого компаратора подается максимальное число совпадений, полученное в ходе предыдущих сравнений. Если первое число больше второго, то на первые входы группы из ]log2(m x n)[ двухвходовых элементов И 36 поступает управляющий сигнал с компаратора 33, разрешающий прохождение двоичного числа количества совпадений, поступающего с выходов группы элементов 34 задержки, на запись в регистр 35. Управляющий сигнал подается также через выход 40 на вход 59 блока 6 управления считыванием информации и разрешает запись координат Х и Y текущего смещения центра окна в регистры 7 и 8 соответственно. Если количество совпадений меньше или равно максимальному числу совпадений, полученному в ходе предыдущих сравнений, состояние регистров 35, 7 и 8 не меняется, т.е. в них остается прежнее значение.

Сравнение чисел в компараторе 33 логически завершается подачей на вход 39 блока 5 выбора максимального числа совпадений сигнала с выхода 100 блока 6 управления считыванием информации, проходящего элемент 38 задержки и переводящего пересчетную схему 37 в следующее состояние. По достижении схемой 37 заданного коэффициента пересчета, соответствующего количеству всех возможных сравнений, с выхода 43 поступает управляющий сигнал на вторые входы третьей и второй групп ключевых элементов, разрешая считывание координат смещения из регистров 7 и 8 на выходы вычислителя. В противном случае управляющий сигнал с пересчетной схемы подается на выход 42, который соединен с управляющим входом 70 блока 6 управления считыванием информации. Его работа заключается в следующем.

При запуске вычислителя с входа 99 на выход 52 поступает сигнал, разрешающий первоначальное считывание информации из блока 2 памяти эталонного изображения. Одновременно с этим через входы 78, 79 и 97, 98 в счетчики 67 и 71 соответственно записываются значения координат смещения, соответствующие положению окна в левом нижнем углу эталонного изображения (т.е.

X = -  X

X = -

= -  ; Y = -

; Y = - Y

Y = -

= -  ). После завершения первого сравнения макс, если полученное число совпадений меньше максимального числа совпадений, то на вход 70 блока 6 поступает управляющий сигнал, который переводит счетчик 67 в состояние Хi+1=Xi+1. Этот же сигнал поступает на первый вход двухвходового элемента И 63, на второй вход которого подается импульс с генератора 66, при этом элемент И 63 открывается и пропускает управляющий сигнал через выход 51 на вход 20 блока 2 памяти эталонного изображения, происходит сдвиг информации в блоке 2 на один разряд влево. Управляющий сигнал с выхода элемента И 63 поступает также через элементы 62 задержки (tзад= t сдвига информации в блоке 2) на вход двухвходового элемента И 64, на второй вход которого поступают импульсы с генератора 66. При этом элемент 64 открывается и через выход 52 управляющий импульс поступает на входы 44 первой группы двухвходовых элементов И 9 (из m x n двухвходовых элементов И 25) и разрешает считывание информации из блока 2.

). После завершения первого сравнения макс, если полученное число совпадений меньше максимального числа совпадений, то на вход 70 блока 6 поступает управляющий сигнал, который переводит счетчик 67 в состояние Хi+1=Xi+1. Этот же сигнал поступает на первый вход двухвходового элемента И 63, на второй вход которого подается импульс с генератора 66, при этом элемент И 63 открывается и пропускает управляющий сигнал через выход 51 на вход 20 блока 2 памяти эталонного изображения, происходит сдвиг информации в блоке 2 на один разряд влево. Управляющий сигнал с выхода элемента И 63 поступает также через элементы 62 задержки (tзад= t сдвига информации в блоке 2) на вход двухвходового элемента И 64, на второй вход которого поступают импульсы с генератора 66. При этом элемент 64 открывается и через выход 52 управляющий импульс поступает на входы 44 первой группы двухвходовых элементов И 9 (из m x n двухвходовых элементов И 25) и разрешает считывание информации из блока 2.

При появлении управляющего сигнала на входе 59 блока 6 информация из счетчика 67 через двухвходовые элементы И 56 подается на выходы 49 (знакового) и выходы 50 (значащих разрядов), которые связаны с входами асинхронного регистра 7 для хранения координат смещения по Х. Информация из счетчика 71 через двухвходовые элементы И 60 поступает на выходы 53 (знакового разряда) и 53 (значащих разрядов), которые связаны с входами асинхронного регистра 8 для хранения координат смещения по Y. При появлении управляющего сигнала на входе 58 блока 6 информация из счетчика 67 через двухвходовые элементы И 57 подается на выходы 45 (знакового разряда) и 46 (значащих разрядов), которые связаны с первой группой информационных выходов вычислителя, а информация из счетчика 71 через двухвходовые элементы И 61 подается на выходы 47 знакового и 48 значащих разрядов, которые связаны с второй группой информационных выходов вычислителя. По достижении счетчиком 67 значения координаты смещения X = Xмакс=  с его выхода поступает сигнал на вход 74 счетчика 71, который переводится при этом в состояние Yi+1=Yi+1. Этим же сигналом открывается двухвходовый элемент И 65, на второй вход которого поступает сигнал с выхода элемента И 64. Сигнал с выхода 55 элемента И 65 поступает на вход 19 блока 2 памяти эталонного изображения и осуществляет сдвиг информации в вертикальном направлении. Кроме того, по достижении счетчиком 67 значения Xмакс=

с его выхода поступает сигнал на вход 74 счетчика 71, который переводится при этом в состояние Yi+1=Yi+1. Этим же сигналом открывается двухвходовый элемент И 65, на второй вход которого поступает сигнал с выхода элемента И 64. Сигнал с выхода 55 элемента И 65 поступает на вход 19 блока 2 памяти эталонного изображения и осуществляет сдвиг информации в вертикальном направлении. Кроме того, по достижении счетчиком 67 значения Xмакс=  меняется режим его работы и координаты меняются по формуле Хi+1=Xi-1 до тех пор, пока X > -

меняется режим его работы и координаты меняются по формуле Хi+1=Xi-1 до тех пор, пока X > -  . По достижении счетчиком 67 этого значения происходит смещение информации в блоке 2 в вертикальном направлении и вновь меняется режим работы счетчика на первоначальный. Этот цикл происходит до тех пор, пока "окно" не "пройдет" по всему эталонному изображению.

. По достижении счетчиком 67 этого значения происходит смещение информации в блоке 2 в вертикальном направлении и вновь меняется режим работы счетчика на первоначальный. Этот цикл происходит до тех пор, пока "окно" не "пройдет" по всему эталонному изображению.

Его исходное состояние следующее: в триггерах 84 значащих разрядов (их количество К=]log2((M-m)+1)[) записано значение X = -  , т.е. в триггер 75 знакового разряда записывается "1", что соответствует отрицательному знаку координаты Х, управляющий триггер 77 также находится в нулевом состоянии. При поступлении управляющего сигнала на вход 70 открывается трехвходовый элемент И 85, при этом из значащей части числа вычитается единица.

, т.е. в триггер 75 знакового разряда записывается "1", что соответствует отрицательному знаку координаты Х, управляющий триггер 77 также находится в нулевом состоянии. При поступлении управляющего сигнала на вход 70 открывается трехвходовый элемент И 85, при этом из значащей части числа вычитается единица.

По достижении счетчиком 67 значения X = -  открывается элемент И 76 иасинхронный триггер 75 переводится в нулевое состояние, что соответствует положительному знаку координаты Х. При этом открывается трехвходовый элемент И 86 и к значащей части числа прибавляется единица. По достижении значения координаты X =

открывается элемент И 76 иасинхронный триггер 75 переводится в нулевое состояние, что соответствует положительному знаку координаты Х. При этом открывается трехвходовый элемент И 86 и к значащей части числа прибавляется единица. По достижении значения координаты X =  , т. е. при завершении прохода "окна" по данной строке, открывается ] log2((M-m)+1)[-входовый элемент И 80, на первый вход которого подается управляющий сигнал с входа 70 через элемент 81 задержки работа счетчика для сложения или вычитания), а остальные ]log2((M-m)+1)[ входов подключены к соответствующим выходам триггеров 84 так, чтобы при наличии в значащей части счетчика числа Х=Хмакс на входах элемента И 80 были единицы. Сигнал с выхода элемента И 80 поступает на выход 74, а также на вход управляющего триггера 77, который при этом переводится в единичное состояние. В результате открывается трехвходовый элемент И 87 и осуществляется работа счетчика по вычитанию единицы из значащей части числа. По достижении значащей частью числа нулевого состояния открывается ]log2((M-m)+1)[-входовый элемент И 76 и триггер 75 знакового разряда переводится в единичное состояние, что соответствует отрицательному знаку координаты Х. При этом открывается трехвходовый элемент И 88 и осуществляется прибавление единицы к значащей части числа. По достижении значащей частью числа значения Xмакс= -

, т. е. при завершении прохода "окна" по данной строке, открывается ] log2((M-m)+1)[-входовый элемент И 80, на первый вход которого подается управляющий сигнал с входа 70 через элемент 81 задержки работа счетчика для сложения или вычитания), а остальные ]log2((M-m)+1)[ входов подключены к соответствующим выходам триггеров 84 так, чтобы при наличии в значащей части счетчика числа Х=Хмакс на входах элемента И 80 были единицы. Сигнал с выхода элемента И 80 поступает на выход 74, а также на вход управляющего триггера 77, который при этом переводится в единичное состояние. В результате открывается трехвходовый элемент И 87 и осуществляется работа счетчика по вычитанию единицы из значащей части числа. По достижении значащей частью числа нулевого состояния открывается ]log2((M-m)+1)[-входовый элемент И 76 и триггер 75 знакового разряда переводится в единичное состояние, что соответствует отрицательному знаку координаты Х. При этом открывается трехвходовый элемент И 88 и осуществляется прибавление единицы к значащей части числа. По достижении значащей частью числа значения Xмакс= -  открывается элемент И 80,схема возвращается в исходное состояние и цикл повторяется до тех пор, пока "окно" не пройдет всех строк по матрице эталонного изображения, с прямого выхода управляющего триггера 77 информация поступает на выходе 107, а с инверсного - на выход 108. Это необходимо для обеспечения выбора направления смещения информации в блоке 2 памяти эталонного изображения по горизонтали. При нулевом состоянии триггера 77 информация в блоке 2 сдвигается справа налево, а при единичном - слева направо.

открывается элемент И 80,схема возвращается в исходное состояние и цикл повторяется до тех пор, пока "окно" не пройдет всех строк по матрице эталонного изображения, с прямого выхода управляющего триггера 77 информация поступает на выходе 107, а с инверсного - на выход 108. Это необходимо для обеспечения выбора направления смещения информации в блоке 2 памяти эталонного изображения по горизонтали. При нулевом состоянии триггера 77 информация в блоке 2 сдвигается справа налево, а при единичном - слева направо.

Исходное состояние счетчика 71 следующее: триггер знакового разряда находится в единичном состоянии, что соответствует отрицательному знаку координаты Y, а в триггерах значащей части записано значение Yмакс=  .Принцип работы этого счетчика аналогичен принципу работы счетчика 67, за исключением того, что в связи с упрощением функциональных возможностей он осуществляет только операции вычитания единицы из значащей части числа при отрицательном знаке и прибавления единицы при положительном знаке.

.Принцип работы этого счетчика аналогичен принципу работы счетчика 67, за исключением того, что в связи с упрощением функциональных возможностей он осуществляет только операции вычитания единицы из значащей части числа при отрицательном знаке и прибавления единицы при положительном знаке.

Блок 2 памяти эталонного изображения (фиг.2) состоит из матрицы размером М x n элементов 10 памяти. При поступлении на вход 20 управляющего сигнала с выхода 51 блока 6 управления считыванием информации осуществляется сдвиг информации, записанной в блоке 2 в горизонтальном направлении. Сигнал с входа 20 проходит на открытый для него вентиль 21 и поступает на синхровход триггера 22 (фиг.3), а также проходит на первые входы двухвходовых элементов И 101 и 102, на вторые входы которых поступают сигналы с входов 105 и 106 соответственно. С помощью этих элементов осуществляется выбор направления смещения информации по горизонтали. Если открыт элемент И 101, то информация из (i, j)-го элемента 10 памяти переносится в (i,j+1)-й элемент памяти через открывающиеся при этом двухвходовые элементы И 103 и 104 и выходы 109 и 110 соответственно. Если открыт элемент И 102, то информация из (i, j)-го элемента 10 памяти переносится в (i, j-1)-й элемент памяти через открывающиеся при этом двухвходовые элементы И 26 и 27 и выходы 13 и 14 соответственно.

При поступлении управляющего сигнала на вход 19 с выхода 55 блока 6 управления считыванием информации происходит сдвиг информации, записанной в блоке 2 в вертикальном направлении. Сигнал проходит открытый для него вентиль 21 и поступает на синхровход триггера 22. Одновременно с этим он открывает двухвходовые элементы И 23 и 24 и информация с выходов 18 и 17 (i, j)-го элемента 10 памяти поступает на входы 15 и 16 соответственно (i+1, j)-го элемента памяти. Информация из последнего в данной строке (столбце) элемента памяти поступает на первый в данной строке (столбце) элемент памяти и наоборот.

Матрица из m x n элементов 10 памяти, находящихся в левом нижнем углу матрицы эталонного изображения, имеет дополнительные ключевые элементы 9 для считывания информации в блоке 3 сравнения с помощью двухвходовых элементов И 25, на первые входы которых подается информация с прямого выхода триггера 22, а на вторые - управляющий сигнал с входа 44, соединенного с выходом 52 блока 6 управления считыванием информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕКОНФИГУРАЦИИ МНОГОМАШИННОГО ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА | 1991 |

|

RU2022342C1 |

| УСТРОЙСТВО ТЕРМОКОМПЕНСАЦИИ КВАРЦЕВОГО ГЕНЕРАТОРА | 1990 |

|

RU2007839C1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010431C1 |

| УСТРОЙСТВО ЗАЩИТЫ ПАМЯТИ | 1990 |

|

RU2022343C1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| ТЕРМОКОМПЕНСИРОВАННЫЙ ГЕНЕРАТОР | 1991 |

|

RU2030091C1 |

| УСТРОЙСТВО ДЛЯ ОТСЛЕЖИВАНИЯ КОНТУРОВ ДВУМЕРНЫХ ОБЪЕКТОВ | 1991 |

|

RU2050594C1 |

| УНИВЕРСАЛЬНЫЙ ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ПО МОДУЛЮ M - ДЕШИФРАТОР КОЛИЧЕСТВА ЕДИНИЦ В N-РАЗРЯДНОМ ДВОИЧНОМ КОДЕ | 1991 |

|

RU2020744C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ T-КОДОВ | 1991 |

|

RU2026608C1 |

Изобретение позволяет расширить функциональные возможности вычислителя путем выявления того участка в эталонном бинаризованном изображении, которое в максимальной степени совпадает с предъявленным для распознавания, а также определить координаты центра этого участка относительно центра эталонного изображения. Для этого вычислитель содержит блок подсчета числа совпадений, блок выбора максимального числа совпадений, блок управления считыванием информации, два регистра для хранения координат смещения, три группы ключей, блок памяти текущего изображения, блок памяти эталонного изображения и блок сравнения. 3 з.п.ф-лы, 7 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для ассоциативной обработки двумерных массивов | 1986 |

|

SU1392556A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-02-20—Публикация

1991-05-16—Подача