Изобретение относится к области цифровой вычислительной техники, в частности к вычислительным специализированным устройствам для деления, и может быть использовано в различн областях народного хозяйства, разлиных системах моделирования, автоматического управления, везде, где требуется осуществлять операцию деления п-разрядных кодов чисел.

Цель изобретения - повышение быстродействия. ,

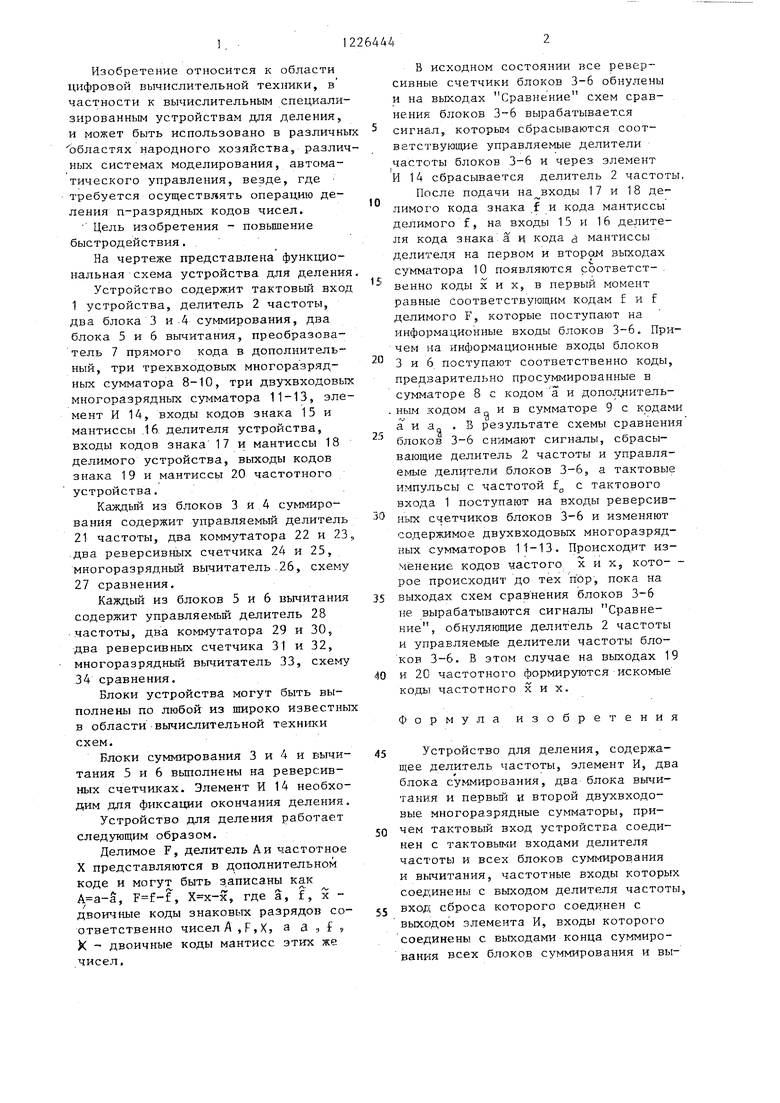

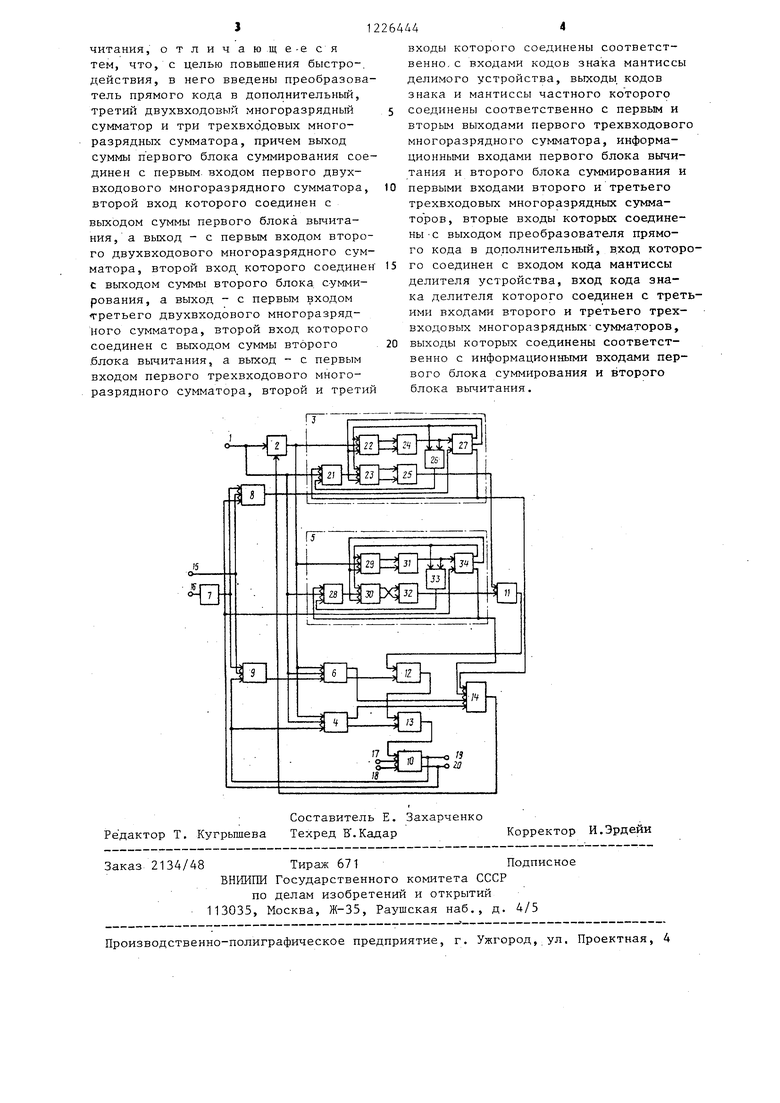

На чертеже представлена функхщо- пальная схема устройства для делени

Устройство содержит тактовый вхо 1 устройства, делитель 2 частоты, два блока 3 и-4 суммирования, два блока 5 и 6 вычитания, преобразователь 7 прямого кода в дополнительный, три трехвходовых многоразрядных сумматора 8-10, три двухвходовы многоразрядных сумматора 11-13, элемент И 14, входы кодов знака 15 и мантиссы .16- делителя устройства, входы кодов знака 17 и мантиссы 18 делимого устройства, выходы кодов знака 19 и мантиссы 20 частотного устройства.

Каждый из блоков 3 и,4 суммирования содержит управляемый делитель 21 частоты, два коммутатора 22 и 23 -Два реверсивных счетчика 24 и 25, многоразрядный вычитатель .26, схему 27 сравнения.

Каждый из блоков 5 и 6 вычитания содержит управляемьй делитель 28 частоты, два коммутатора 29 и 30, два реверсивных счетчика 31 и 32, многоразрядный вычитатель 33, схему 34 сравнения.

Блоки устройства могут быть выполнены по любой из широко известны в области вычислительной техники схем.

Блоки суммирования 3 и 4 и вычитания 5 и 6 вьшолнены на реверсивных счетчиках. Элемент И 14 необходим для фиксации окончания деления.

Устройство для деления работает следующим образом.

Делимое F, делитель Аи частотное X представляются в дополнительном коде и могут быть з.аписаны как , , , где а, f, х - двоичные коды знаковых разрядов соответственно чиселА,Р,Х5 а а , f , X - двоичные коды мантисс этих же чисел.

0

S

0

. з

0

5

0

5

0

В исходном состоянии все реверсивные счетчики блоков 3-6 обнулены и на вькодах Сравнение схем сравнения блоков 3-6 вырабатывается сигнал, которым сбрасываются соответствующие управляемые делители частоты блоков 3-6 и через элемент И 14 сбрасывается делитель 2 частоты,

После подачи на входы 17 и 18 делимого кода знака f и кода мантиссы делимого f, на входы 15 и 16 делителя кода знака а и кода а мантиссы делителя на первом и второе выходах сумматора 10 появляются соответст- . венно коды X и X, в первый момент равные соответствующим кодам f и f делимого F, которые поступают на информационные входы блоков 3-6. Причем на информационные входы блоков 3 и 6 поступают соответственно коды, пред)зарительно просуммированные в сумматоре 8 с кодом а и дoпoл итeль- . ным кодом а„ и в сумматоре 9 с кодами а и а„ . В результате схемы сравнения блоков 3-6 снимают сигналы, сбрасывающие делитель 2 частоты и управляемые делители блоков 3-6, а тактовые импульсы с частотой f с тактового входа 1 поступают на входы реверсивных счетчиков блоков 3-6 и изменяют содержимое двухвходовых многоразрядных сумматоров 11-13. Происходит изменение кодов частого х и х, кото- - рое происходит до тех пор, пока на выходах схем сравнения блоков не вырабатываются сигналы Сравнение, обнуляющие делитель 2 частоты и управляемые делители частоты блоков 3-6. В зтом случае на выходах 19 и 20 частотного формируются искомые коды частотного х и х.

Формула изобретения

Устройство для деления, содержащее делитель частоты, элемент И, два блока суммирования, два блока вычитания и первый я второй двухвходо- вые многоразрядные сумматоры, причем тактовый вход устройства соединен с тактовыми входами делителя частоты и всех блоков суммирования и вьгчитания, частотные входы которых соединены с выходом делителя частоты, вход сброса которого соединен с выходом элемента И, входы которого соединены с выходами конца суммирования всех блоков суммирования и вычитания, отличающе-еся тем, что, с целью повьппения быстро-, действия, в него введены преобразователь прямого кода в дополнительный, третий двухвходовый многоразрядный сумматор и три трехвходовых многоразрядных сумматора, причем выход суммы первого блока суммирования соединен с первым, входом первого двух- входового многоразрядного сумматора, второй вход которого соединен с выходом суммы первого блока вычитания, а выход - с первым входом второго двухвходового многоразрядного сумматора, второй вход которого соединен с выходом суммы второго блока суммирования, а выход - с первым входом третьего двухвходового многоразрядного сумматора, второй вход которого соединен с выходом суммы второго .блока вычитания, а выход - с первым входом первого трехвходового многоразрядного сумматора, второй и третий

входы которого соединены соответственно, с входами кодов знака мантиссы делимого устройства, выходы кодов знака и мантиссы частного которого соединены соответственно с первым и вторым выходами первого трехвходовог многоразрядного сумматора, информационными входами первого блока вычитания и второго блока суммирования и первыми входами второго и третьего трехвходовых многоразрядных сумматоров, вторые входы которых соединены -с выходом преобразователя прямого кода в дополнительный, в.ход которго соединен с входом кода мантиссы делителя устройства, вход кода знака делителя которого соединен с третими входами второго и третьего трехвходовых многоразрядных-сумматоров, выходы которых соединены соответственно с информационными входами первого блока суммирования и второго блока вычитания.

Составитель Е. Захарченко Редактор Т, Кугрьшева Техред К.КадарКорректор И.Эрдейи

Заказ 2134/48Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для возведения в квадрат | 1984 |

|

SU1239713A1 |

| Устройство для умножения числа на постоянный коэффициент | 1984 |

|

SU1168928A1 |

| Вычислительное устройство | 1985 |

|

SU1259256A1 |

| Умножитель | 1984 |

|

SU1171784A1 |

| Цифровой вероятностный фильтр | 1972 |

|

SU479117A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

Изобретение относится к области цифровой вычислительной техники, в частности к вычислительным специализированным устройствам для деления, и может быть исцользовано в системах моделирования, автоматического управления, т.е. везде, где требуется осуществлять операцию деления разрядных кодов чисел. Цель изобретения - увеличение быстродействия при делении кодов чисел, представляющих собой дискретные значения непрерывно меняющихся функций. Устройство для деления содержит делитель частоты, два блока управляемых суммирующих реверсивных счетчиков, два блока управляемых вычитающих реверсивных счетчиков, блок преобразования прямого кода в дополнительный, два трехвходовых многоразрядных сумматора, три двухвходовых многоразрядных сумматора, многоразрядный сумматор, блок фиксации окончания деления, четьфе управляемых делителя частоты, восемь коммутаторов, восемь реверсивных счетчиков, четыре узла сравнения и четыре комбинационных вьгчитателя. Новым в устройстве является то, что оно содержит делитель частоты, два блока управляемых суммирующих реверсивных счетчиков, два блока управляемых вычитающих реверсивных счетчиков,- блок преобразования прямого кода в дополнительный, два трехвходовых многоразрядных сумматора, три двухвходовых многоразрядных сумматора, многоразрядньй сумматор, четыре управляемых делителя частоты, восемь коммутаторов, восемь реверсивных счетчиков, четыре узла сравнения и .четыре комбинационных вычитателя, связанных между собой соответствующими связями. 1 ил. i СЯ ю ьс 05 4 4 4:

| Устройство для деления | 1979 |

|

SU809176A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Умножитель | 1984 |

|

SU1171784A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-05-14—Подача