(54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования нейрона | 1981 |

|

SU963003A1 |

| Устройство для моделирования нейрона неокортекса | 1987 |

|

SU1464181A1 |

| Устройство для моделирования нейрона | 1974 |

|

SU512478A1 |

| Устройство для моделирования нейрона | 1987 |

|

SU1501101A1 |

| Устройство для моделирования нейрона | 1988 |

|

SU1585811A1 |

| Устройство для морфодинамического моделирования нейрона | 1991 |

|

SU1815658A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2028669C1 |

| Устройство для моделирования нейрона | 1987 |

|

SU1425731A1 |

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU736130A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2093889C1 |

. -- -

.. Изобретение относится к устройствам

моделирования нервной системы и может быть использовано в системах распознавания образов и управления.

Известно устройство для. моделирования нейрона, состоящее из блока сравн&ния, формирователя выходных импульсов, формирователя порога, блока управления резисторными элементами, аддитивного сумматора, соединенных с ним блоков моделирования синаптическйх элементов, каждый из которых включает резиотсфный элемент, соединённый с ним выходом накопитель, входы которого соединены с внешним входом устройства для моделирования нейрона и с блоком управления резисторными элементами 1.

Недостатком известного устройства является невозможность осуществления нелршейного анализа пространственно- , временных образов. Так как это ус- ройство не способно распознавать вр&менные образы и в нем отсутствует взаимодействие между блоками моделироваНИИ синаптическйх элементов, то суммарный сигнал, сравниваемый с пороговым значением, равен сумме входшлх сигнг - лов, каждый из которых взят с учетом состояния соответствующего ему резне- торного элемента и без учета других сигналов, что является свидетельством линейности анализа пространственных образов.-

Недостатком известного устройства $шляется также низкая динамичность за поминания, так как изменение состояний резисторных элементов происходит тол1гко после проведения полного анализа распознаваемого образа.

Наиболее близким техническим реш&нием к изофетению является устройство для моделирования нейрона, соде % а1иее И аддитивных сумматоров, cxei сра&нения, выход которой подключен непосредственно к входу формирователя сигнала управления резисторными элементами, через формирователь порога - к первому своему.входу и через формирователь выходног-о сигнала - к выходу устгюйс1ва, и и групп блоков моделиропа1шя синапса, причем кпждый блок моделирования силалса состоит из элемента задержки и накопителя, выход которого подключен к управлшошему входу реэнсторного элемента, вход которог через буферный каскад соединен с соответствующрм входом устройства | 2 j .

Недостатком этого устройства является линейность анализа образов, так как оно представляет собой устройство, линейно объединяклцее посредством сум матора более простые устройства, в которых также с пороговым значением сравнивается сумма сигналов, каждый из которых взят с учетом состояния соответствующего ему резисторного элемента независимо от других сигналов, что доказывает линейность анализа, распозна1гаемого образа.

К недостаткам этого известного устройства также относ11тся низкая динамичность запоь/тнания, потому, что соотояние резисторных элементов изменяется также только нод действием выходного сигнала.

Поль Изобретения - пог ышение точности к{оделирова)1ия за счет обеспечения нелинейности анализа пространственно-временных обршзов и повышения динамичности запоминания.

Поставленная цель достигается тем, что в устройстве, содержащем И аддитивных сумматоров, схему управления, выход которой подключен непосредственно к входу формирователя, сигнала управления резисторными элементами, через формирователь порога - к первому своему входу и через формирователь выходного сиг-нала - к выходу устрОЧства, и У1 грунп модел1фования синапса, причем каждый блок моделирования синапса состоит из элемента задержки и накопителя, выход которого подключен к управляющему входу резисторного элемента, вход которого через бу4)ерный каскад соединен с соответствующим входом устройства, введены элементы задержки, а в каждый блок моделирования синапса - элементы И, аддитивные с тлматоры через элементы задеряски соединены последователг но, выход послед})его аддитивного сумматора подк;пс - чен к второму входу схем1л сра1 нения, выход (}хзрм1фователя сигнала управления резисторными элементами соединен с первыми вxoдa ffl накопителеfi псюпедней группы блоков моделирования синапса и входом последовательно соединенных элементов задержки, выход каждого из которых соединен с первыми входами накопителей соответствующей группы блоков моделирования синапса, выход резисторного элемента каждого блока , моделирования синапса через соответст- вуклщий элемент задержки подключен к

0 соответствующему входу соответствующего аддитивного сумматора, выход которого соединен с первыми входами элементов И соответствующей группы блоков моделирования синапсов, вход бу-

5 ферного каскада каждого блока моделирования синапса подключен к второму входу элемента И, выход которого соединен с вторым входом накопителя.

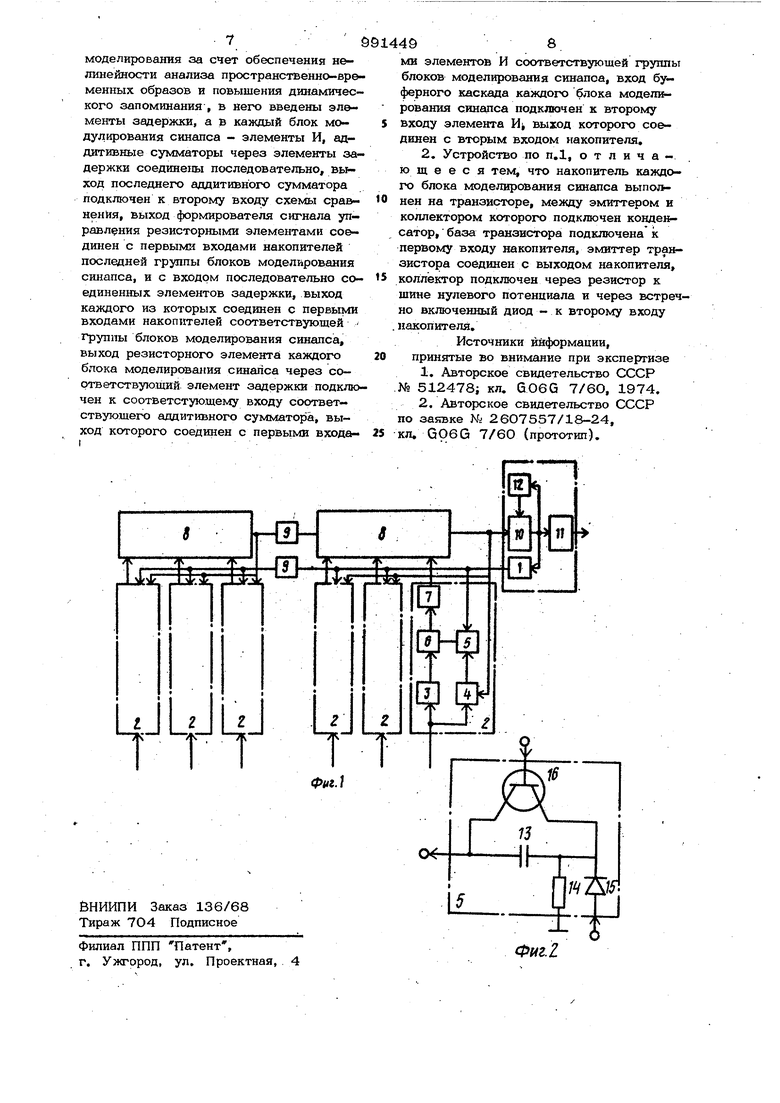

QКроме того, накопитель каждого блока моделирования синапса выполнен на транзисторе, между эмиттером и коллектором которого подключен конденсатор, база транзистора подключена к первому

входу накопителя, эмиттер соединен с выходом накопителя, а коллектор подключен через резистор к шине потенциала и через встречно включенный диод - к второму входу накопителя.

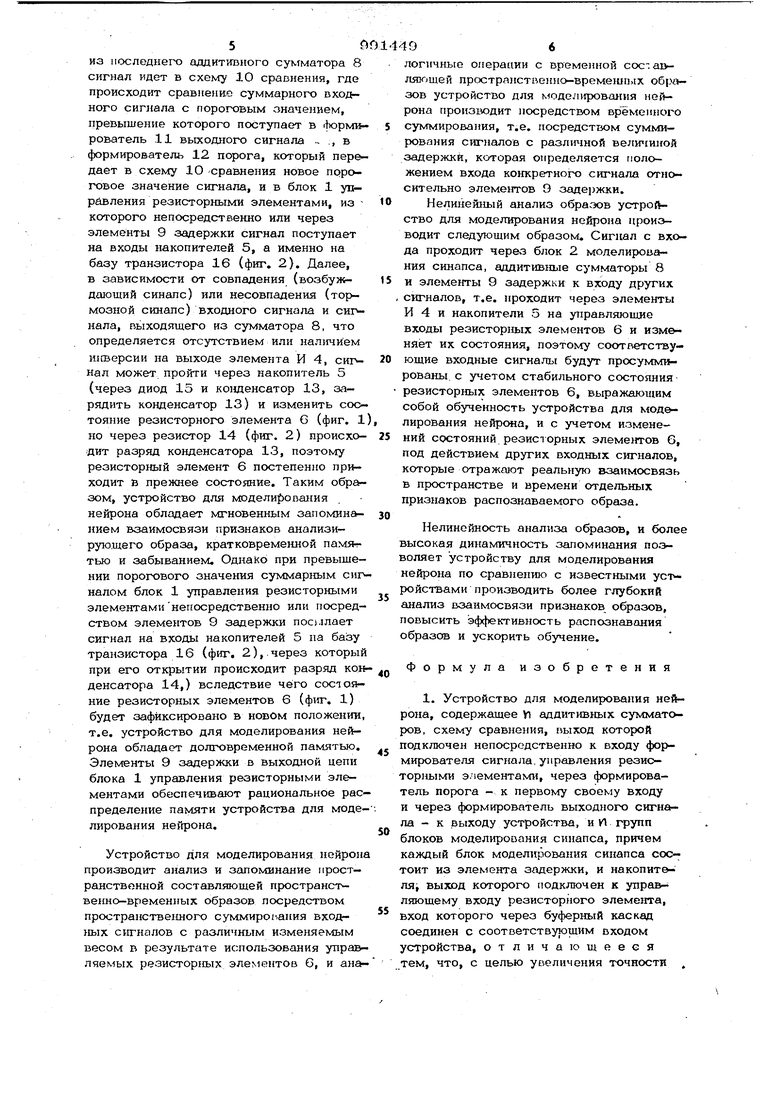

На фиг. 1 изображена блок-схема устройства для моделирования нейрона; на фиг. 2 - принципиальная схема накопителя.

Устройство для моделирования нейрона состоит из формирователя 1 сигнала управления резнсторными элементами; блоков 2 моделирования синапсов (фиг. 1), содержащих буферные каскады 3, эле менты И 4, .накопители 5. резисторные элементы G, элементы 7 задержки, аддитивных сумматоров 8, элементов 9 задержки, схемы 10 сравнения, фор(трователя 11 выходного сигнала, и (}юрми- рователя 12 порога. Накопитель 5(фиг. 2) состоит из конденсатора 13, релчстора 14, диода 15 и транзистора 16.

Устройство для моделирования нейрона работает следующим образом.

На входы блоков 2 моделирования синапсов поступают входные сигналы и

° инвертированные (тормозные синапсы) или неинвертированные (возбуждающие . синапсы) в буферных каскадах 3 проходят через резисторные элементы G и элементы задержки 7 в аддит тные сум-

5 маторы 8, где происходит их сложение по амплитуде и знаку, и суммарный сигнал через элементы 9 задержки, проходит в следующий аддитивный сумматор 8, а из последнего аддитквного сумматора 8 сигнал идет в схему 10 сравнения, где происходит сравнение суммарного входного сигнала с пороговым значением, превышение которого поступает в Ьормирователь .11 выходного сигнала ., в формирователь 12 порога, который передает в схему Ю -сравнения новое пороговое значение сигнала, и в блок 1 упрйвления резисторкыми элементами, из которого непосредственно или через элементы 9 задержки сигнал поступает на входы накопителей 5, а именно на базу транзистора 16 (фиг. 2), Далее, в зависимости от совпадения (возбуждающий синапс) или несовпадения (тормозной синапс) входного сигнала и сиг нала, выходящего из сумматора 8, что определяется отсутствием или наличием И1Шерсии на выходе элемента И 4, сиг- нал может пройти через накопитель 5 (через диод 15 и конденсатор 13, зарядить конденсатор 13) и изменить состояние резисторного элемента G (фиг. 1 но через резистор 14 (фиг. 2) происходит разряд конденсатора 13, поэтому резисторный элемент 6 постепенно приходит в прежнее состояние. Таким образом, устройство для моделирования нейрона обладает мгновенным запоминанием взаимосвязи признаков анализирующего образа, кратковременной памяттью и забыванием. Однако при превышении порогового значения суммарным сип налом блок 1 управления резисторными элементаминепосредственно или посредством элементов 9 задержки посылает сигнал на входы накопителей 5 на базу транзистора 16 (фиг. 2), через который при его открытии происходит разряд кон денсатора 14,) вследствие чего состоя ние резисторных элементов 6 (фиг. 1) будет зафиксировано в новом положении, т.е. устройство для моделирования нейрона обладает долговременной памятью. Элементы 9 задержки в выходной цепи блока 1 управления резисторными элементами обеспечивают рациональное рас пределение памяти устройства для моделирования нейрона. Устройство для моделирования нейрон производит анализ и запоминание пространственной составляющей прюстранст- венно-временных образов посредством пространстве1шого суммирования входных српгналов с различным изменяемым весом в результате использования управляемых резисторных элементов 6, и ана- логичные операции с временной сос. aivЛ51к-)щей простра11ствен)1о-времеш1)1Х o6pivзов устройство для моде.пфования нейрона производит посредством временного суммирования, т.е. посредством суммирования сиг}1алов с различной BeJimmirofi задержки, которая определяется положением входа конкретного сигнала относительно элементов 9 задержки. Нелинейный анализ обра:зов устройство для моделирования нейрона производит следующим образом. Сигнал с входа проходит через блок 2 моделирования синапса, аддитивные сумматоры 8 и элементы 9 задержки к входу других сигналов, т.е. проходит через элементы И 4 и накопители 5 на управляющие входы резисторных элементов 6 и изм&няёт их состояния, поэтому соответству- ю.щие входные сигналы будут просуммированы, с учетом стабильного состояния резисторных элементов 6, выражающим собой обученность устройства для моделирования нейрона, и с учетом изменений состояний резиспорных элементов 6, под действием других входных сигналов, которые отражазот реальную взаимосвязь в пространстве и времени отдельных признаков распознаваемого образа. Нелинейность анализа образов, и более высокая динамичность запоминания позволяет устройству для моделирования нейрона по срав}1еник-) с известными уст рюйствами производить более глубокий анализ взаимосвязи признаков образов, повысить эффективность распознавания образов и ускорить обучение. Формула изобретения 1. Устройство для моделирования нейрона, содержащее У1 аддитивных сумматоров, схему сравнения, выход которой подключен непосредственно к входу формирователя сигнала.управления резиоторными э.чементами, через формирователь порога - к первому своему входу и через формирователь выходного сигнала - к выходу устройства, и И групп блоков модел1фования синапса, причем каждый блок моделирования синапса состоит из элемента задерхски, и накопит ля выход которого подключен к упра ляющему входу резисторного элемента, вход которого через буферный каскад соединен с соответствующим входом устройства, отличающееся тем, что, с целью увеличения точности .

Авторы

Даты

1983-01-23—Публикация

1980-02-28—Подача