1

Изобретение относится к области бионики и вычислительной техники и может быть использовано в качестве элемента адаптивных нейтронных сетей, для моделирования биологических процессов, в устройствах распознавания образов, .а также в качестве элемента структур, предназначенных для решения систем алгебраических уравнений, задач исследования операций, краевых задач теории поля.

Известно устройство для моделирования нейрона,, содержащее п входов, блоки моделирования синапса, специальные входы, управляющие изменение синаптических весов, специальные входы, управляющие характеристикой обучения, аддитивный сумматор, формирователь порога, блок управления резисторным элементом, преобразователь напряжения в частоту, блок сравнения, первый, и второй интеграторы, блок управления синапсом, формирователь аьасодных сигналов и источник питания 1

Недостаток такого устройства - пocтoннство таких параметров, как вес резупьтата Пространственного суммирования, длительность временного суммирования, вес пороговой добавки при адаптации по входу, длительность периода возбуждения, вес пороговой добавки при адаптации по выходу, длительность периода адаптации, длительность периода обучения и вес длительности периода обучения, которое значительно ограничивает функциональные возможности устройства, так как не поз10воляет без изменения конфигурации связей между его элементами перестраиваться на различные режимы функционирования.

Наиболее близким техническим решением к изобретению является устройство

15 для моделирования адаптивного нейрона, содержащее аддитивный сумматор, вькод которого соединен с в :одом переменной интегрирования первого цифрового интегратора, выход которого подключен к пер20вому входу первого сумматора, второй вход которого соединен с выходом второ го цифрового интегратора, вход переменной интегрирования которого подключен к выходу третьего цифрового интегратора, вход подынтегральной фун1шии которого подключен к выходу первого сумматора и к первому входу второго сумматора, выход которого соединен с входом по.аы-нтегральной функции четвертого цифротго интегратора, выход которого подключен к входу блока сравнения, выход которого является выходом устройства и соединен с входом переменной интегрирования пя- того цифрового интегратора, выход которо го подключен к первому входу третьего сумматора, второй вход которого соединен с выходом шестого цифрового инте- .гратора, вход переменной интегрирования которого соединен с выходом седьмого цифрового интегратора, вход подынтег1ральной функции которого подключен к прямому выходу третьего сумматора, инверсный выход которого соединен с вторым входом вто рого сумматора, восьмой,цифровой итчэ- гратор, выход которого подключен к третьему входу третьего сумматора, четвертый вход которого соединен с выходом Девятого цифрового интегратора, вход переменной интегрирования которого под- 1Шючен к выходу третьего цифрового ин тегратора, входы переменной интегркрова ния третьего, четвертого, седьмого и восьмого цифровых интеграторов под1шюче ны к первому управляющему входу устрой ства, входы ггадынтегральной функции первого, второго, пятого, шестого, восьмого и девятого цифровых интеграторов соединены с вторым, третьим, четве;р гым, пятым, шестым и седьмым управляю щими входами устройства соответственно и входные цифровые интеграторы на каждый устройства, входы переменной интегрирования которых являются устройства, входы подынтегральных функций входных цифровых интеграторов образуют группу управляющих входов устртй ства. Причем, выходы входных цифровых интеграторо)а подключены, к входам аддитивного сумматораГЗ Недостаток устройства отсутствие в модели учета, зависимости эфф ективности синаптичёской передачи от частоты входных воздействий и от состояний нейрона в данный момент времени. Цепь наобретения - повьпление точности моделирования адаптивного нейрона yKftaaiuiaH цель достигается тем, что в устройство для моделирования адаптив ного нейрона, содержаилее аддитивный cyMMMXJp, выход которого соединен с входок-г пе{5емен 1Ой HHTerpT-ipoBaHHH перво цифрового интегратора, выход которог-о подключе к первому входу первогх) сумматора, второй Бход которого соединен с выходом второго цифрового интегратора, вход переменной интегрирования которого подключен к выходу третьего цифрового интегратора, вход подинтегральной функции которого подключен к выходу первого сумматора и к первому входу второго сумматора, выход которого соединен с входом подинтегральной функции четвертого цифрового интегратора, выход которого подключен к входу блока сравнения, ВЫХОД которого является выходом устройства и соединен с входом переменной интегрирования пятого цифрового интегратора, выход которого подключен к первому входу третьего сумматора, второй вход которого соединен с выходом шестого цифрового интегратора, вход переменной интегрирования которого соединен с выходом седьмого цифрового интегратора, вход подинтегральной функции которого подключен к прямому выходу третьего сумматора, инверсный выход которого соединен с вторым входом второго сум матора, восьмой цифровой интегратор, выход которого подключен к третьему входу третьего сумматора, четвертый вход которого соединен с выходом девятого Ц5 фрового интегратора, вход переменной интегрирования которого подключен к выходу третьего цифрового интегратора, входьг неременной интегрирования третьего, четвертого, седьмого и восьмого цифровых интеграторов подключены к первому управляющему входу устройства, входы подинтегральной функции первого, второго, пятого, щестого, восьмого и девятого цифровых интеграторов соединены с вторым, третыш, четвертым пятым, шестым и седьмьш управляюи;ими входами устройства соответственно и входные цифровые интеграторы по числу входов устройства, входы переменной интегрирования которых являются входами устройства, входы подинтегральной . ции входных цифровых интеграторов являются управляющими входами устройства, введены десятый цифровой интегратор и по числу входов устройства - входной сук-магор м два сйнаптических цифровых интегратора, -выход каждого входного цифрового интегратора соединен с первым входом соответствующего входного сумматора, Быход которого подключен к входу подинтегральной функции первогхэ синаптического цифрового интегратора, выход

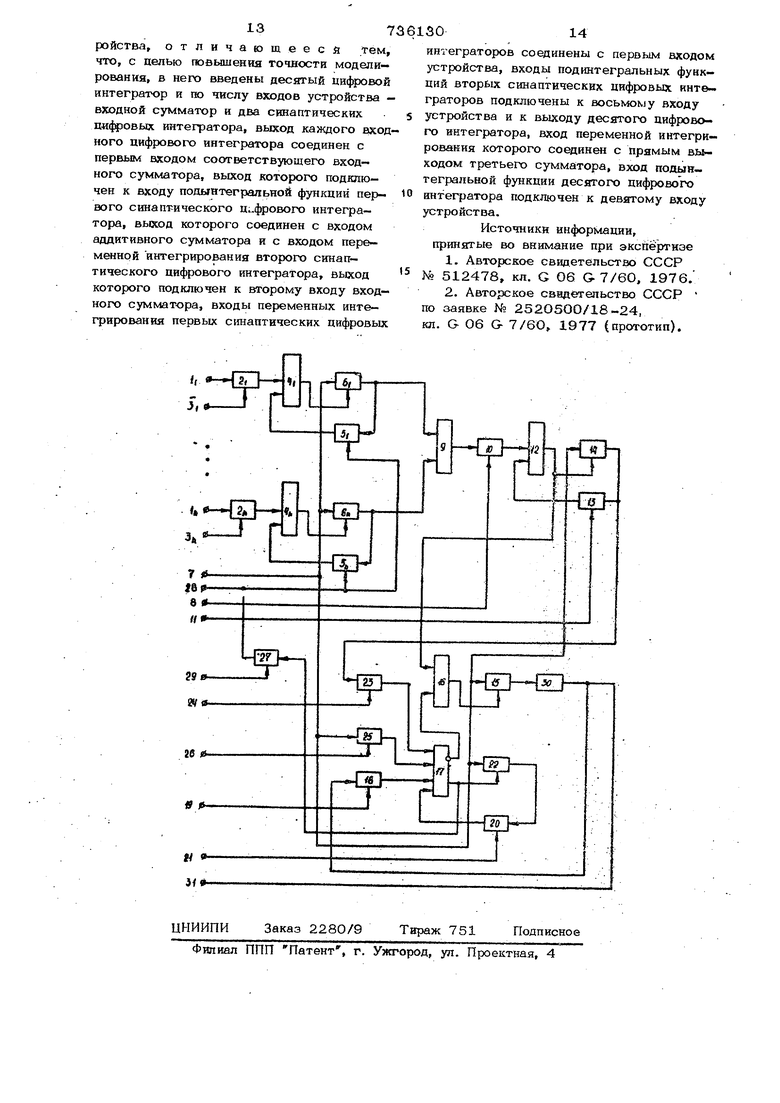

которого соединен с входом аддитивного сумматора и с входом переменной инте- гриро ния второго синаптического цифрового интегратора, выход которого подключен к второму входу входного сумматора, входы переменных интегрирования первых синаптическик цифровых интеграторов соединены с первым входом устройства, входы подинтегральных функций вторых синаптических цифровых интеграторов подключены Ю к восьмому входу устройства и к выходу десятого цифрового и 1тегратора, вход переменной интегрирования которого соединен с прямым выходом третьего суммато- ра, вход подинтегральной функции десятого цифрового интегратора подключен к девятому входу устройства. На чертеже приведена структурная схема устройства. Устройство содержит входы 1, -iVi , входные цифровые интеграторы 2i -2 входы подинтегральных функций которых подсоединены к группе управляющих входов 3i -3гг. 1 управляющих изменением синаптических весов, входные сумматоры 4/ -4 , 2т1 синаптических цифровых интеграторов 5i -5пиб1 - Q-к . котфые совместно с интеграторами 21 2 tt. и сумматорами 4 -4 п. представля ют собой блоки моделирования синапса, реализующие зависимость эффективности синаптической передачи от частоты входных воздействий и от состояния нейрона в данный момент времени, первый управляющий вход 7, управляющий изменением длительности периода возбуждения, второ управляющий вход 8, управляющий измене нием веса пространственного суммирования; аддитивный сумматор 9, реализующий пространственное суммирование взве- щенных входных сигналов, первый цифровой интегратор 10, третий управляющий вход 11, управляющий изменением длител ности временного суммирования, первый сумматор 12, второй, третий и четверты цифровые интеграторы 13 14 и 15, второй и третий сумматоры 16 и 17, пятый цифровой интегратор 18, вход подинтегральной функции которого подключен к четвертому управляющему входу 19, управляющему изменением веса поро говой добавки при адаптации по выходу, щестой цифровой интегратор 20, вход подинтегральной функции которого подклю чен к пятому управляющему входу 21, управляющему изменением длительности периода адаптации, седьмой цифровой ннтегратор 22, девятый цифровой интегратор 23, вход подынтегральной функции которого подсоединен к шестому управляю- щему входу 24, управляющему изменением

:веса пороговой добавки при адаптации по входу, восьмой цифровой интегратор

25, вход подынтегральной функции которого подключен к седьмому управляющему входу 26, управляющему изменением значения порога, десятый цифровой интегратор 27, выход которого подключен к восьмому управляющему входу 28, управляющему изменением начального значения длительности периода обучения, а вход подинтегральной функции подключен к девятому управля ощему входу 29, управляющему изменением веса длительности пер1юда обучения, блок 30 сравнения и выход 31. Цифровой интегратор 14, который совместно с интегратором 13 и сумматором 12 образует блок временного суммирования входных сигналов. Цифровой интегратор 15 совместно с блоком 30 сравнения и сумматором 16 образует , выходное устройство, реализующее пороговый эффект. Устройство работает следующим образом. Для задания режима функционирования на входы.3i -Зтг , 28, 8, 11, 24, 26, 21, 29 и 19 подаются соответствующие значения синаптических весов, начального значения длительности периода обучения, веса пространственного суммирования, длительности временного суммирования, веса пороговой добавки при адаптации по входу порога, длительности периода а;даптации, веса длительности периода обучения и веса пороговой добавки при адаптации по выходу. После этого на вход 7 подаются значения длительности периода возбуждения. С этого момента устройство готово к приему входных сигналов, поступающих с выходов других элементов, объединенных с Данным элементом в нейроноподобную сеть. Входные сигналы через входы 1 -Iri модели поступают на входы переменных интегрирования цифровых интеграторов-2 -2 ц , в которых умножаются на соответствую- щие значения синаптических весов, хранящихся в регистрах подынтегральных функций этих интеграторов, полученные произведения поступают на первые входы цифровых сумматоров 4 , этот же момент времени значения взвещенных входных величин, полученные на предьщущем шаге (на первом шаге они равны нулю) и хранящиеся в регистрах, .подынтегральных функций цифровых интеграторов 6i , ..., 6п. умнойсаются в них на значение длительности периода всзбуж- дения (задаваемое с входа 7) и поступаю на входы переменных интегрирования 11и4 ровых интеграторов 5i , ..., , в которых дополнительно умножаются на значений длительности периода обучения, полученные на предьщущем шаге (на первом шаге все -они равны начальному значению длительности периода обучения, задаваемому с входа 28) и передаются на вторы . Й1ачения входы сумматоров 4 взвешенных входных величин, полученные на предьщущем шаге и умноженные в интеграторах 6i , ..., бп. на значение длительности периода возбулодения, поступают на входы аддитивного сумматора 9, 6 которок они суммируются и полученная сумма передается на вход переменной интегрирования интегратора 10, после чего умножается в нем на значение веса пространственного суммирования, храняще гося в регистре подь1нтегральной функции этого интегратора. Полученное произведе- ние с выхода интегратора 1О посту11ает . на первый вход сумматора 12. Значение результата временного суммирование, полученное на предыдущем maire (на первом шаге оно равно нулю) и хранящееся в регистре подынтегральной ф5т:-1кдии интегратора 14, умножается в нем на значение длительности периода .возбуждения (подаваемое с входа 7) и постудаег на вход переменной интегрирования интеграто ра 19, в котором дополнительно умножаегся на значение длительности врем;енного суммирования (х.ран{ацееся в регистре подынтегральной функции этого интегратора) и передается на второй вход сумматора 12, а1ачение результата временного с -ммйрования, полученное на предьщущем шаге и умноженное в интеграторе 14 на значение длительности периода возбухсдения, поступает, кроме того, на вход пере . менной интегрирования интегратора 23, В котором умножается на значение веса пороговой добавки при адаптации по входу . и полученное произведение подается на третий вход сумматора 17, на четвертый вход которого с выхода интегратора 25 поступает произведение значений псрога (хранящегося в регистре подынтегральной функци 1 интегратора 25) и длительности периода возбуждения (подаваемое с входа 7). В этот же момент времени текущее значение порога, полученное на предьщу- ем шаге (на первом шаге оно равно нулю) и хранящееся в регистре подынтеграль- ной функции интегратора 22 умножается в нем на значение длительности периода возбуждения (подаваемое с входа 7) и поступает на вход переменной интегрирования интегратора 20, в котором дополнительно умножается на значение длительности периода адаптации (хранящееся в регистре подынтегральной функции этого интегратора) и передается на второй вход сумматора 17. Одновременно с сигналами, поступившими на второй, третий и четвертый входы сумматора 17, на его первый вход с выхода интегратора 18 поступает произведение значений выходной величины (подаваемое с выхода 31 модели) и веса пороговой добавки при адаш-ации по выходу (хранящееся в регистре подынтегральной функции интегратора 18). Суммарные значения, получившиеся в сумматорах 12 и 17, с прямого вьасода сумматора 12 и.инверсного выхода сумматора 17, поступают соответственно на первый и второй входы сумматора 16, где дополнительно суммируются. Сумма, полученная в сумматоре 17, с прямого выхода этого сумматора поступает на вход переменной интегрирования интегратора 27, в котором умножается на значение веса длительности периода обучения, и полученное произведение подается на входы подьтнтегральных функций (служащие для управления характеристикой обучения) интеграторов 5i S ....,571, . Значение суммы, полученной в сумматоре 16, поступает на вход подынтегральной функции интегратора 15. В интеграторе 15, поступившая сумма умножается на значение длительности периода возбуждения и полученное произведение поступает на вход блока 30 сравнения, в котором сравнивается с нулем. Если это произведение больще нуля, то оно появляется на выходе 31 модели. Если произведение меньше нуля, то сигнал на выходе 31 модели отсутствует. Процесс адаптации по выходному сигналу и по входному производит блок моделирования адаптации, содержащий интеграторы 18, 2О, 22, 23, 25 и сумматор 17, который в случае неизменности во времени интенсивности входного возбуждения сиг нала обеспечивает медленное понижение, в зависимости от величины длитель-. ности периода адаптации (задаваемое с входа 21) выходной реакции устройства. 97 Изменение эффективности синаптическо передачи в зависимости от частоты поступления входных возбуждающих воздействий, т.е. процесс обучения устройства, реализуют блоки моделирования сигналов состоящие из сумматоров 4i , ..., 4п. и интеграторов 2i , ..., 2«. , 5i , .... 5п . 6 i , ..., бп. . При частном появлении Haj-M входе модели -( 1...,п.) входного сигнала, j--b;;i блок моделирования синапса обеспечивает возрастание взвешенного значения входной величины (т.е. увеличение эффективности j -ой синапти- ческой передачи ), в зависимости от значения длительности периода обучения, хранящегося в регистре подынтегральной функции интегратора 5 . Ебли на вход , модели перестают поступать входные воздействия , то j -ый блок моделирования синапса производит уменьщение взвешенного значения входной величины (хранящееся в регистре подынтегральной функции интегратора 6 J ) вплоть до нуля, в зависимости от значения длитель- .ности периода обучения, т.е. эффективност -ой синаптической передачи снижается до нуля и данная связь вообще отмирает Й1ачения длительности периода обучения (хранящиеся в регистрах подынтегральных функций интеграторов 5 ,..., 5 а следовательно и эффективность синапсов зависят от состояния самого нейронопо- добного элемента в данный момент време ни. Зту зависимость восп1эоизводит блок моделирования адаптации (интеграторы 18, 20, 22, 23, 25 и сумматор 17) и интегратор 27. Работа модели обучающегося нейрону описывается следующей системой разностных уравнений:. -&tij (,+o(39(-1) fe-njut -Xgyyut; Р At ,Е i At ; (U ut+ Piut; i Д. (,йt+,,Увы,.LЛt; LVeb)x.(l4D4t max{o,:yi,-enut} -, где J- - начальное значение длитель ности периода обучения; «j - вес длительности периода обучения; v(i-i)- текущее значение порога, полученное в предыдущем ша t(-i) J - значение взвешенной входной величины, по- 10 лученное в предьадущем шаге; At - длительность периода возбуждения; XL, - входные воздействия поступающие на i -м щаге; Yj - синаптический вес i -го входа; Р - вес пространственного суммирования; с/, - длительность временного суммирований; (1-|) - значение временной суммы, полученное в предыдущем щаге; c/j - длительность периода адаптации; 0(5 - вес пороговой добавки при адаптации по входу; 6(j - значение порога; - вес пороговой добавки, при адаптация по выходу; wvl- значение выходной величины в I -м щаге. в системе (1) с равным 1, О, (X 5 равньш О, а i , и Л t в интервапе от нуля получаем следуюшз о систему . -«;c{iAtt Piui; i4).x.UvAt; t m.ax{0,Cyi-ei3ut}, ностью совпадает с моделью го по выходу нейрона. Полагая в системе (1) равным 1, о(з равным О, Xi равным О, а значения {I, , с{ у , ai интервале от нуля до единицы, получаем модель нейрона адаптивного по входу, так как в этом случае работа модели описывается следующей системой разнсютных уравнений:rP:dt.| Xiji-j-at; .)At /Pr:ut; Д В| -,1 Sji.., д t + бо ut «yii.-,)5 Д i .Vgwx.(i.i)ut i«aK{0,Ly;-0iIut. Далее положив с/о равным 1, 0(3 равным О, ц равным О, s 5 равным О, о(;, ре иым 1, (, равн,ым 1 и At равным 1, решение системы (1) принимает вид V.«(,i J-&ol, гО где &tg-n/.-ti приг,0, что совпадает с алгоритмом работы формального нейрона. Если о((5 равно Is dj равно О, о(г ра но О, ц равно О, о у равно О, рав но 1 и At равно 1, то решение системы (1) принимает вид V8b,x(tM), что совпйдает с алгоритмом работы нейрона,, реализующего механизм временно го суммирования. Если положить равным l,o(j равным 1, o(j равным О, 1 равным О, ( J равным О, а о(, и и t в интервале от О до 1, то решение системы (1) аппроксимирует решение следующей сист мы дифференциальнь х уравнений; ( t ,Xj(t)yj, Увых()тах{0,Ие)-9Л}, которая описывает работу аналогового , нейрона., Кроме того, полагая с/о pзfi. ным 1, о( равным О, с/з равным О, о(( равным О, с/5 равным О, «i равным О,Jb равным 1, а Л i интервала-от О до 1, найдем, что решение системы (1) примет следующий вид: y(r; I (XjVJj-e)u-t; (x (i)) At- ma)C -{0, i(L.i) ut , что соответствует алгоритму работы обы ного цифрового интегратора, работающег по формуле прямоугольников, имеющего блок выделения положительных приращений на выходе и комбинационный на входе. Благодаря введению новых блоков и связей между ними Повыщается точнэсть моделирования за счет возможности реа лизации зависимости эффективности сина передачи от частоты входнг 30 воздействий и от состояния нейрона в данный момент времени. Формула изобретения Устройство для моделирования адаптивного нейрона, содержащее аддитивный сумматор, выход которого соединен с входом переменной интегрирования первого цифрового интегратора, выход которого подключен к первому входу первого сумматора, второй вход которого соединен с выходом второго цифрового интегратора, вход переменной интегрирования которого подключен к выходу третьего цифрового интегратора, вход подынтегральной функции которого подключен к выходу первого сумматора и к первому входу второго сумматора, выход которого соединен с входом подынтегральной фу 1кции четвертого цифрового интегратора, выход которого подключен к входу блока сравнения, выход которого является выходом устройства и соединен с входом переменной интегрирования пятого цифрового интегратора, выход которого подключен к первому входу третьего сумматора, второй вход которого соединен с выходом шестого цифро вого интегратора, вход переменной интегрирования которого соединен с.выходо1у1 седьмого цифрового интегратора, вход подынтегральной функции которого подключен к прямому выходу третьего сумматора, инверсный выход которого соединен с вторым входом второго сумматора, восьмой цифровой интегратор, выход которого подключен к третьему входу третьего сумматора, четвертый вход которого соединен с выходом девятого цифрового интегратора, вход переменной интегрирования которого подключен к выходу третьего цифрового интегратора, входы переменной интегрирования третьего, четвертого, седьмого и восьмого цифровых интеграторов подключены к первому управляющему входу устройства, входы подынтегральной функции первого, второго, пятого, шестого, восьмого и девятого цифровых интеграторов соединены с вторым, третьим, четвертым, пятым, шестым И седьмым управляющими входами устройства соответственно и входные цифровые интеграторь; по числу входов устройства, входы переменной интегрирования которых являются входами устройства, входы подынтегральной функции входных цифровых интеграторов являются управляющими входами уст

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU708369A1 |

| Модель адаптивного нейрона | 1978 |

|

SU765823A1 |

| Устройство для моделирования нейрона | 1978 |

|

SU767788A1 |

| Устройство для моделирования нейрона | 1977 |

|

SU682910A1 |

| Устройство для моделирования нейрона | 1979 |

|

SU883927A2 |

| Устройство для моделирования нейрона | 1988 |

|

SU1596356A2 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2029368C1 |

| Устройство для моделирования нейронных ансамблей | 1980 |

|

SU903910A1 |

| Цифровой интегратор | 1976 |

|

SU651371A1 |

| Устройство для моделирования нейрона | 1987 |

|

SU1479944A1 |

Авторы

Даты

1980-05-25—Публикация

1977-12-09—Подача