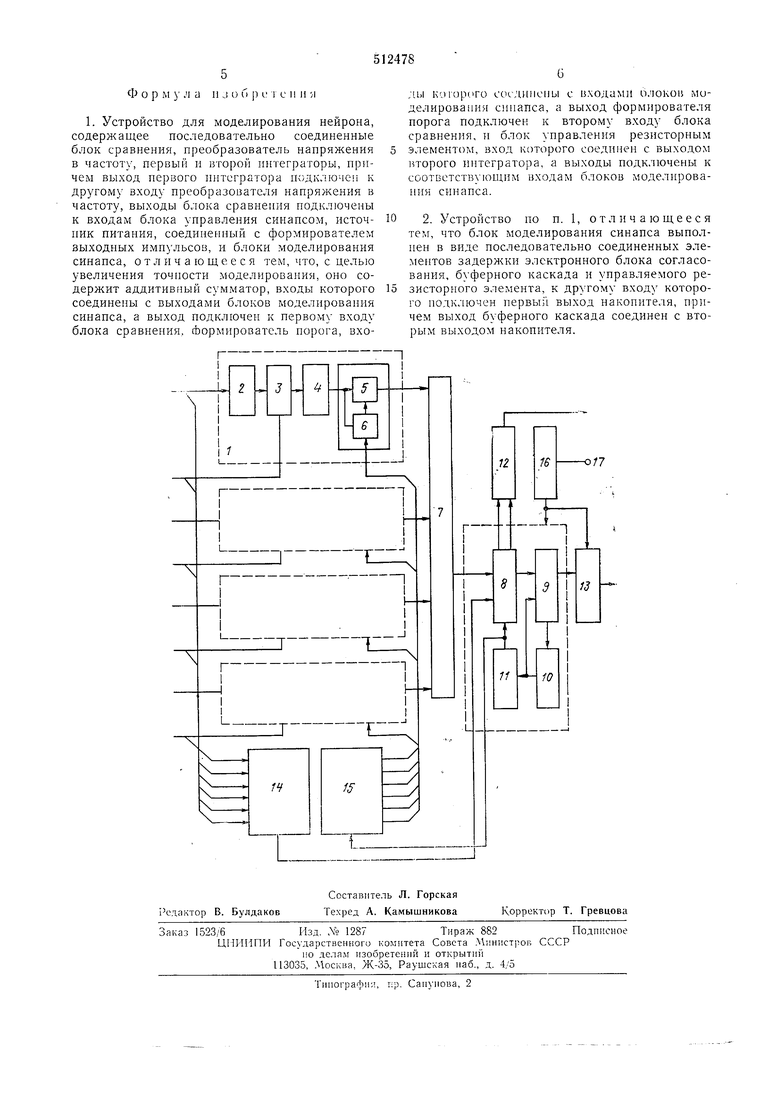

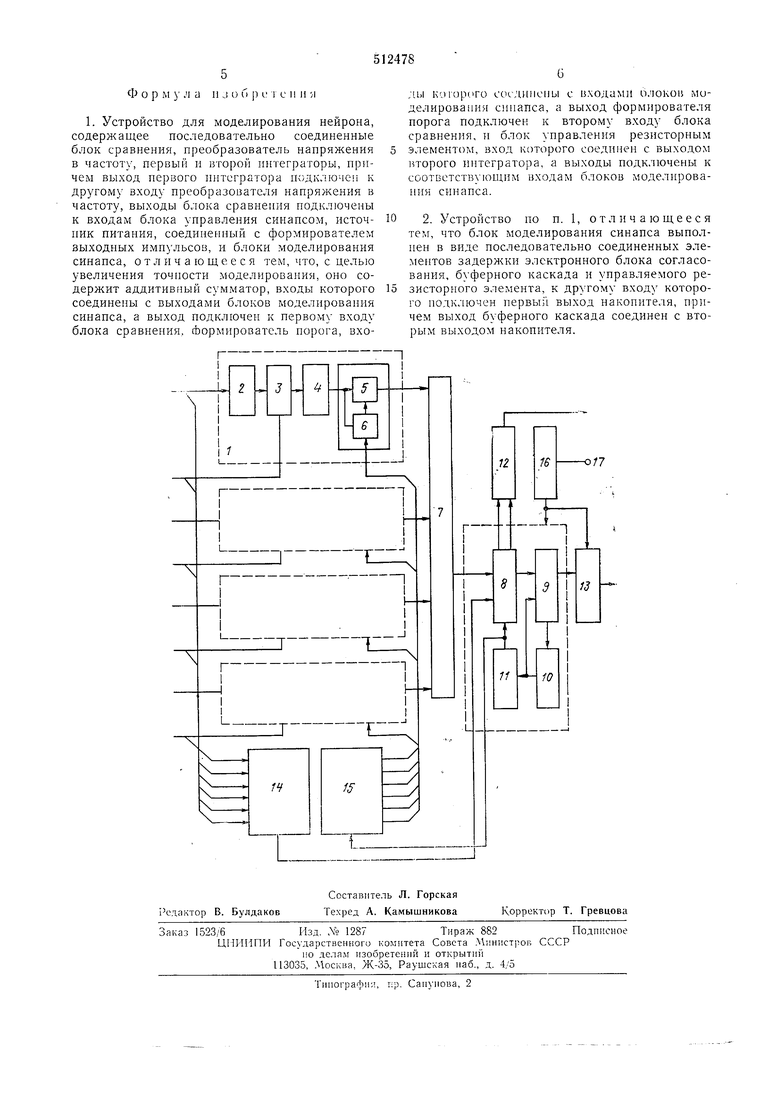

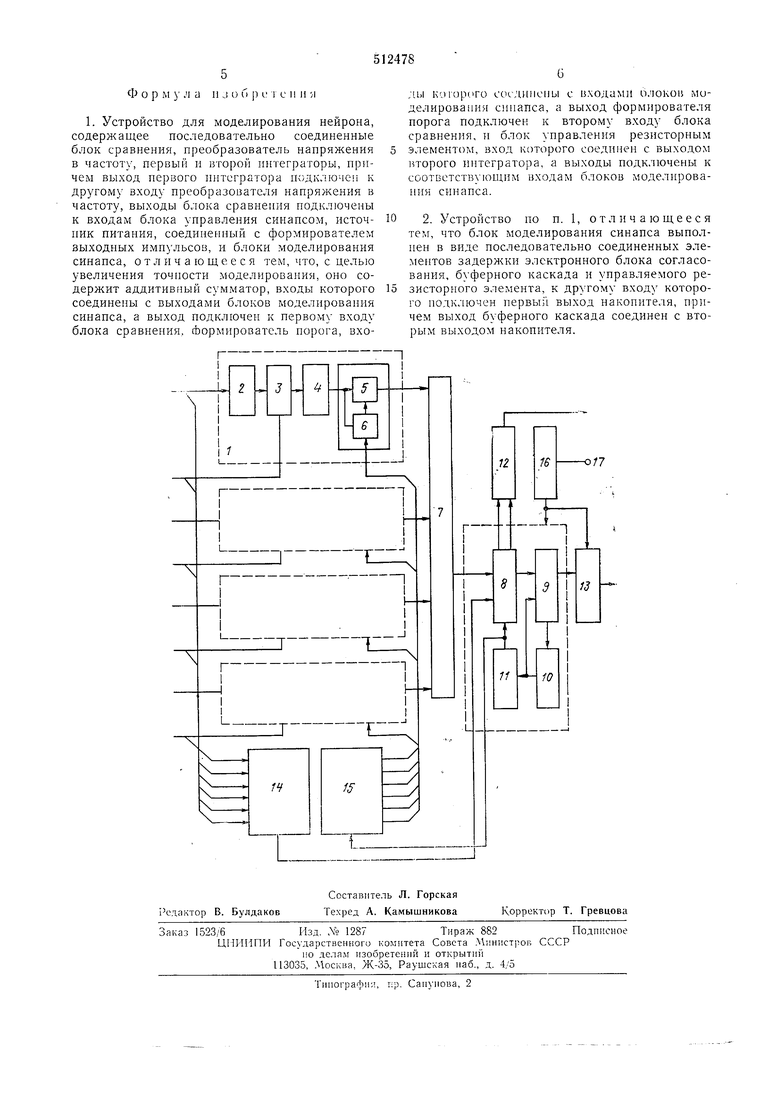

рования нейрона и в зависимости от активного состояния этих блоков входные сигналы, инвертированные (тормозной синапс) или неинвертированные (возбуждающий синапс), последовательно через буферный каскад 4 и управляемый резисторный элемент 5 поступают на аддитивный сумматор 7.

Просуммированные по амплитуде и зпаку в блоке 7 входные сигналы далее поступают на блок сравнения 8, где они сравниваются с пороговым уровнем, и разностное напряжение поступает на преобразователь напряжения в частоту 9, выходные импульсы которого формируются в импульсы нормированной длительности в формирователе выходных импульсов 13 и являются выходом данного устройства.

Процессы внутренней пассивной адаптации по выходпой реакции па входпой спгиал производит первый интегратор 10, охватывающий отрицательной обратной связью преобразователь напряжения в частоту 9; второй контур обратной связи на интеграторе 11, являющемся памятью внутреннего состояния элемента, охватывает блок 9, интегратор 10 и через интегратор 11 второй контур обратной связи замыкается на блок сравнения 8. Здесь необходимо соблюдение условия, что где тц - постоянная времени второго контура обратной связи (положительная обратная связь), TI - постоянная времени первого контура обратной связи (отрицательиая обратная связь).

Таким образом, в случае неизменности но времени интенсивности входного возбуждающего сигнала, интенсивность выходной реакции элемента медленно понижается в зависимости от первого контура обратной связи, а увеличение возбудимости нейроноподобного элемента после предшествовавшего пе 511ода активности или от частоты ее употребления в единицу времени моделирует второй контур обратной связи с постоянной временн.

Механизм активного обучения формируется блоком 15 управления резисторным элементом и формирователем порога 4, которые, дифференцируя самые активные синаптические элементы, согласовывают его с возбудимостью данного устройства. Вес связи синапса (значение весового сопротивления) формируется на управляющем резисторном элементе 5 из суммы управляющих сигналов, пост -пающих из блока 15 управления резисторным элементом, и значения интенсивности входного сигнала, выделенного на паконителе 6. Значение потенциала на выходе второго контура положительной обратной связи (значение внутреннего состояния данного нейроноподобного элемента) с интегратора 11 усиливается и инвертируется блоком 15 управления резисторным элементом, осуществляющим общее интегральное регулирование всеми управляемыми резисторными элементами 5, а индивидуальное управление весом связи конкретного синапса дополнительно производится

накопительным элементом 6 в виде накопления заряда энергии входных импульсов.

Таким образом, при поступлении па входы блоков .моделирования синапса (при ощутимом большинстве возбуждающих или тормозны.х синапсов) импульсов большой интенсивности данное устройство генерирует импульсы соответственно большой интенсивности,

которые при постоянстве с} ммарной входной интенсивности уменьшают выходную частоту со скоростью, зависящей от постоянной времени интегратора 10. При частой активации данного устройства интегратор 11 снижает порог возбуждения, т. е. при большой частоте задействования в сети устройства для моделирования нейрона увеличивается его возбудимость или готовность к последующей активации. И если интенсивность входных импульсов на всех синапсах увеличивается, то значение внутреннего состояния устройства с выхода интегратора 11, инвертируясь в блоке 15 управления резисторпым элементом, производит уменьшение весов связи всех синапсов

интегрально. , при больших интепсивностях входных импульсов на всех блоках 1 умепьшается проходимость сигнала интегрально по всем блокам и выделяются блоки с наибольшими интенсивностями входных импульсов с помощью накопителей 6.

Формирователь порога 14, суммируя потенциалы управления синапсов (возбуждающий или тормозной) на в.ходе устройства или знака весовых коэффициентов синапсов предыдущих нейронов, формирует значение порога по входу, которое поступает на блок сравнения 8 и складываясь по абсолютпой величине со значением потенциала впутренпего состояния нейрона с выхода интегратора 11 формирует

пороговый (нулевой) уровень управляемого генератора. Такое фор мирование порогового уровня позволяет в сети из пейроноподобных элементов ноддерживать число возбужденных элементов в допустимых пределах.

Блок управления синапсом 12 формирует с разностных сигналов уровня порога и потенп,иала па аддитивном сумматора 7, поступающих с блока сравнения 8. потенциал }-правлепия активным состоянием (возбужденного или

заторможенного) синапса данного нсйропоподобного элемента, разветвляющегося па другие подобные устройства ;;ейроппой сети.

С целью поддержания в динамическом диапазоне энергетических характеристик устройства, чтобы не было перенасыщения возбуждения или торможения по выходной реакции элемента, питание блоков 8, 9, 10, 11 и формирователя выходных импульсов 13 осуществляется от емкостного источника питания

16, которое во время «молчапия устройства аккумулируется от внешнего источника питания 17, а во время генерирования импульса разряжается, и в режиме достижеиия максимальной частоты он может обесточиваться или

истощаться.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования нейрона | 1974 |

|

SU512479A1 |

| Устройство для моделирования нейрона неокортекса | 1987 |

|

SU1464181A1 |

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU736130A1 |

| Устройство для морфодинамического моделирования нейрона | 1991 |

|

SU1815658A1 |

| Устройство для моделирования нейронных структур | 1973 |

|

SU478329A1 |

| Устройство для моделирования адаптивного нейроно-глиального комплекса | 1979 |

|

SU773649A1 |

| Устройство для моделирования нейрона | 1988 |

|

SU1585811A1 |

| ИМПУЛЬСНЫЙ НЕЙРОН, БЛИЗКИЙ К РЕАЛЬНОМУ | 2015 |

|

RU2598298C2 |

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU708369A1 |

| ОДНОСЛОЙНЫЙ ПЕРЦЕПТРОН, МОДЕЛИРУЮЩИЙ СВОЙСТВА РЕАЛЬНОГО ПЕРЦЕПТРОНА | 2015 |

|

RU2597496C1 |

Авторы

Даты

1976-04-30—Публикация

1974-06-26—Подача