1

Изобретение относится к импульсной технике и может быть использовано в аппаратуре передачи данных.

Известно устройство для вычитания и добавления импульса, содержащее триггер, два элемента И, элемент НЕ и два элемента ИЛИ 1.

Для нормальной .работы известного устройства необходимо, чтобы импульсы коррекции заканчивались позже импульсов корректируемой последовательности, что ограничивает область при-, менения известного устройства.

Наиболее близким по технической сущности к изобретению является устройство для вычитания и добавления импульса, содержащее два триггера и элемент И 2.

Для нормсшьной работы известного устройства необходимо чтобы импульсы коррекции заканчивались позже импульсов корректируемой последовательности, что ограничивает область применения известного устройства.

Целью изобретения является расширение области применения устройства.

Поставленная цель достигается тем, что в устройство для вычитания и добавления импульса, содержащее два D триггера и элемент И, введены

два элемента И-НЕ, элемент ИЛИ-НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом элемента И, а первый вход - с шиной корректируемой последовательности импульсов и с первым входом первого элемента И-НЕ, выход которого подключен ко входу С первого триггера, а второй вход - к инверсному

10 выходу иSходу О второго триггера, входы R триггеров подключены к шине управления, а вход С второго триггера соединен с инверсным входом и входом D первого триггера и

15 с первым входом элемента ИЛИ-НЕ, второй вход которого подключен к шине командных импульсов и к первому входу второго элемента И-НЕ, второй вход которого соединен с пря20мым выходом первого триггера, а выход - с вторым входом элемента И.

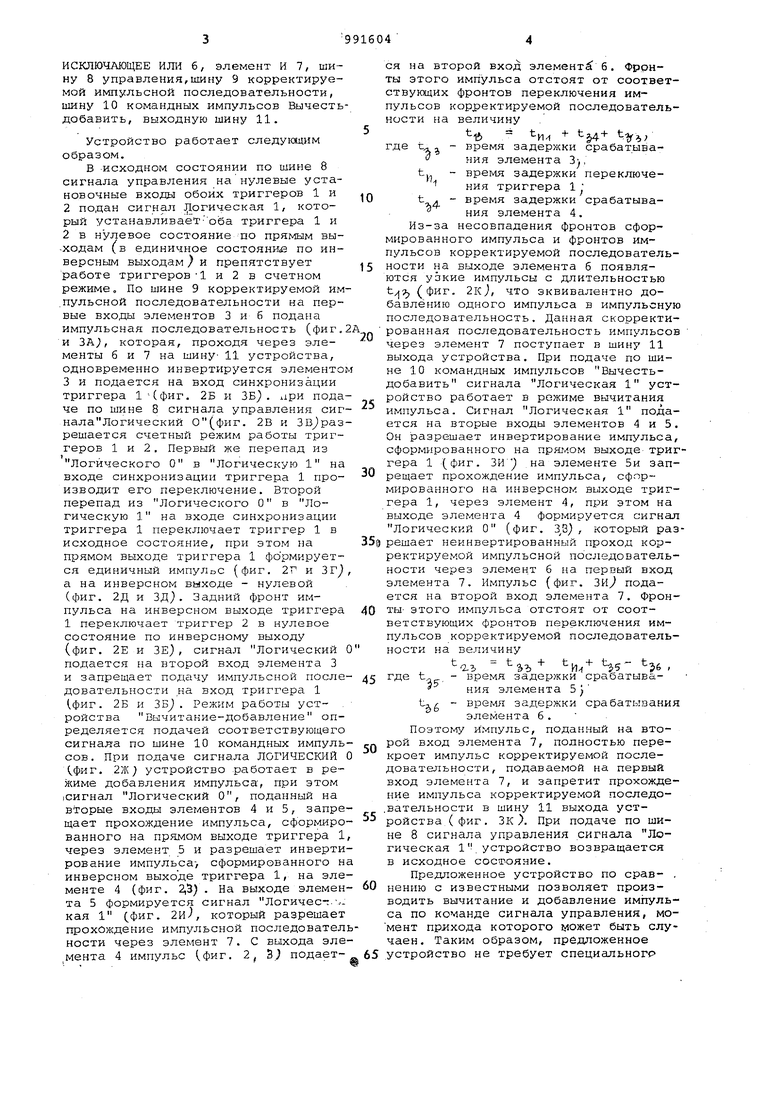

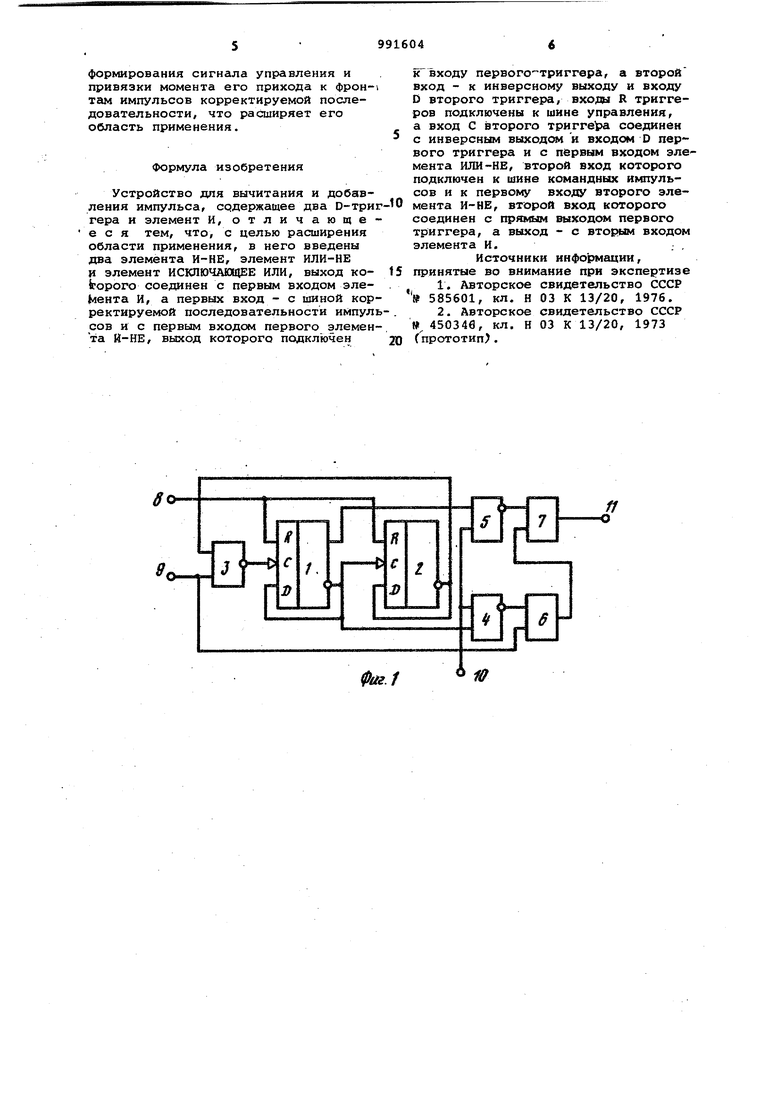

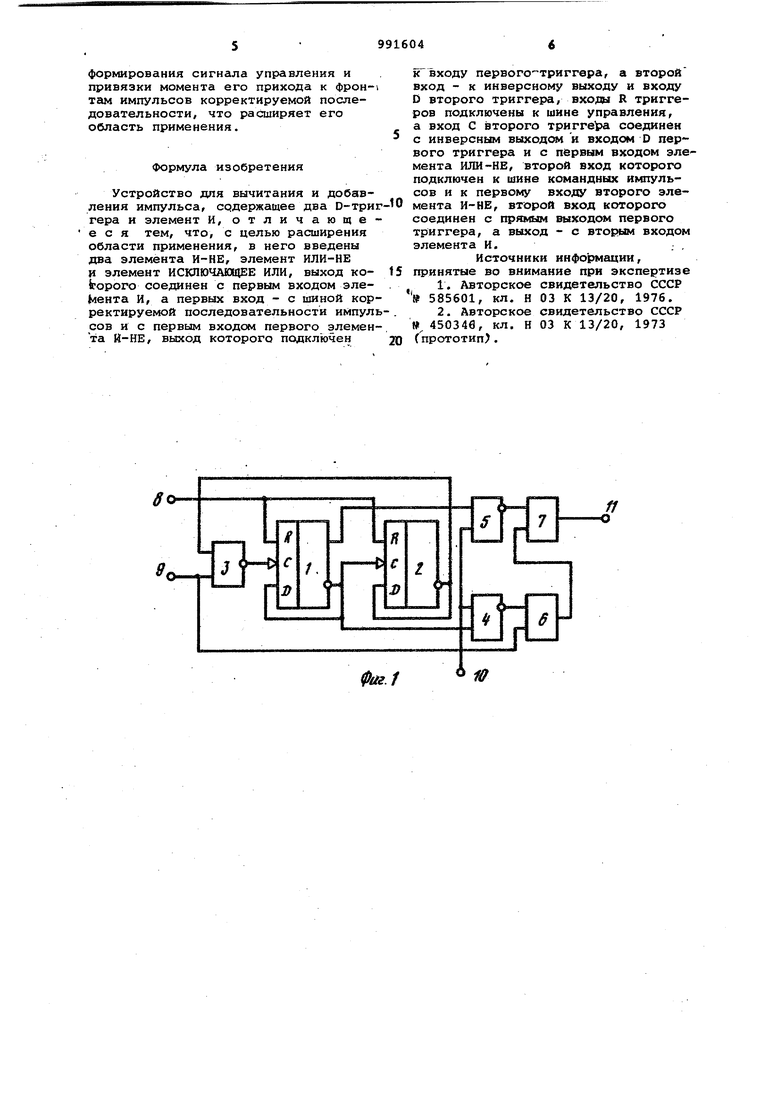

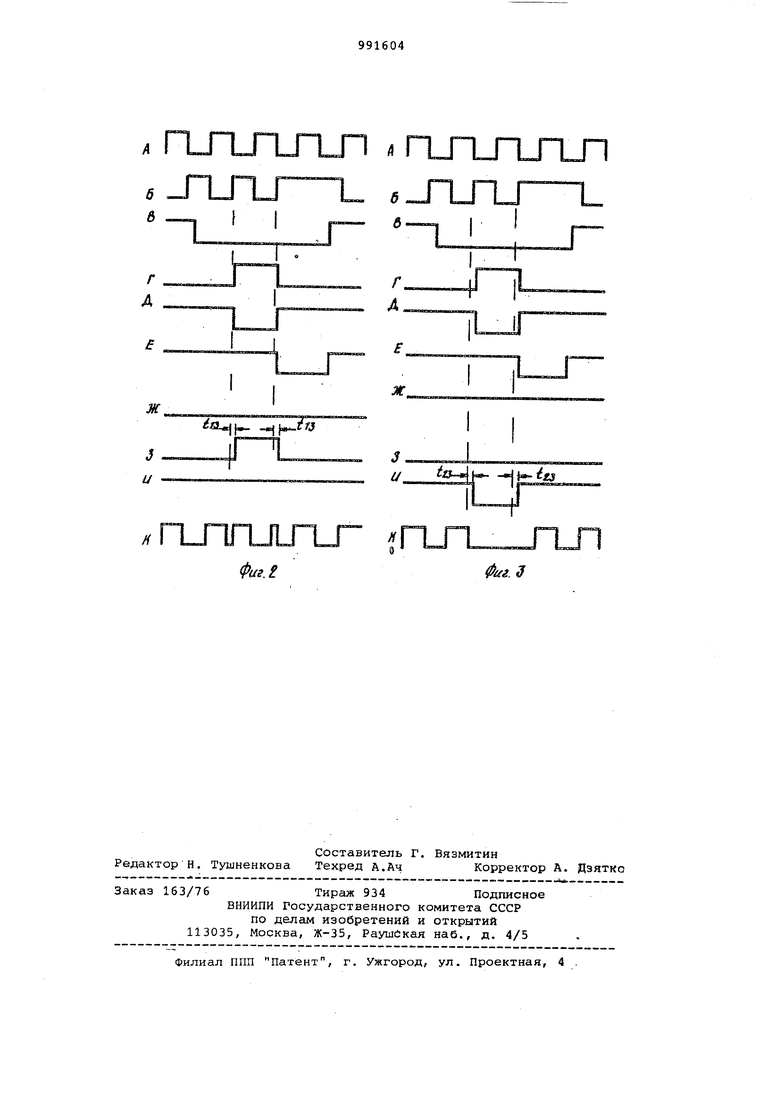

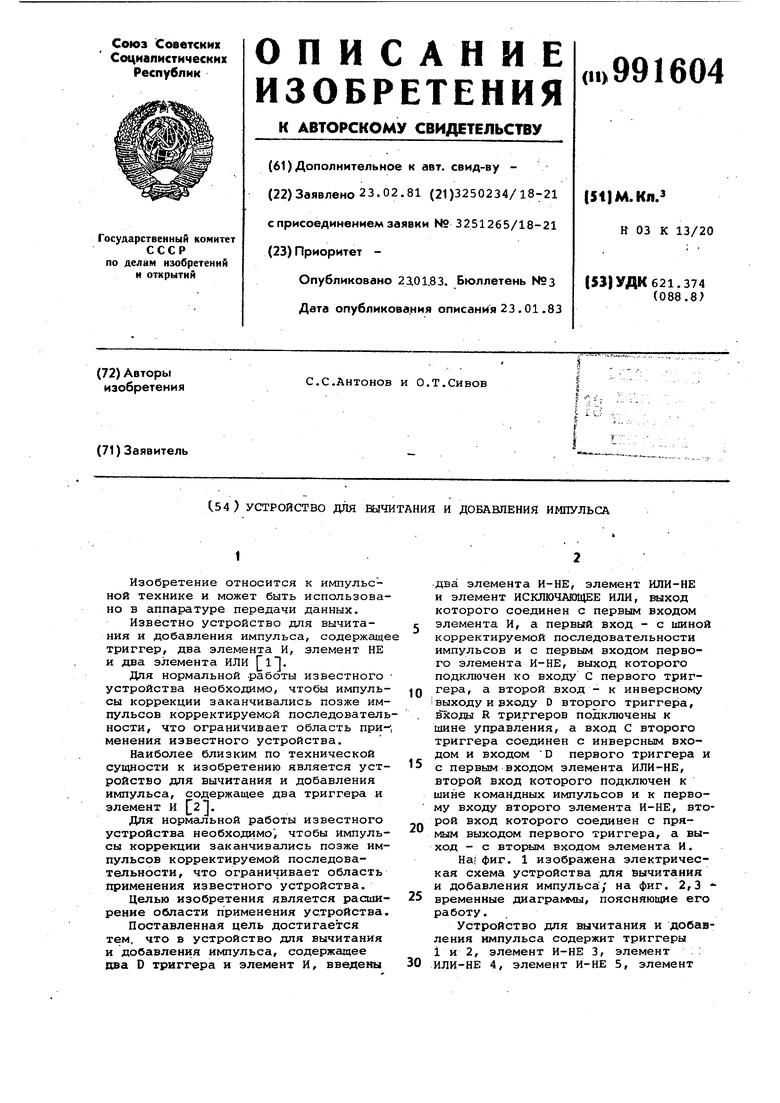

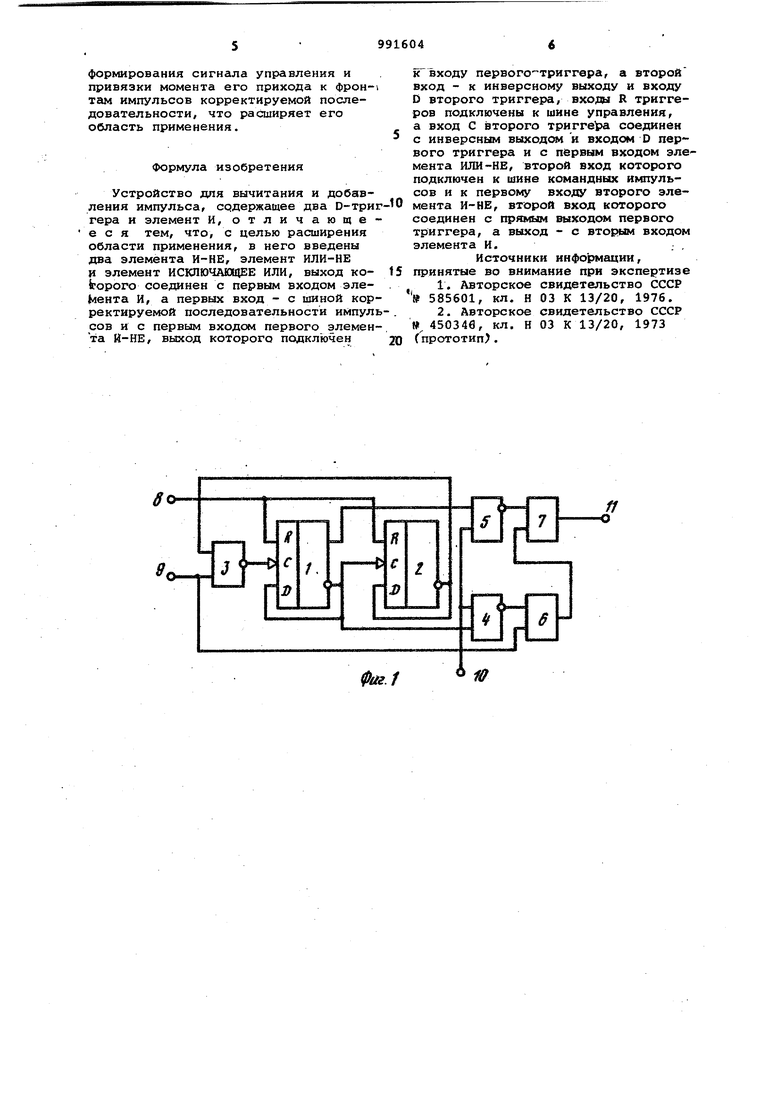

На фиг. 1 изображена электрическая схема устройства для )вычитания и добавления импульса/ на фиг. 2,3 25временные диаграммы, поясняющие его работу.

Устройство для вычитания и добавления импульса содержит триггеры 1 и 2, элемент И-НЕ 3, элемент ::

30 ИЛИ-НЕ 4, элемент И-НЕ 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ б, элемент И 7, шину 8 управления,шину 9 корректируемой импульсной последовательности, шину 10 командных импульсов Вычесть добавить, выходную шину 11. . Устройство работает следуюдим образом. В исходном состоянии по шине 8 сигнала управления на нулевые установочные входы обоих триггеров 1 и 2 подан сигнал :51огическая 1, который устанавливает-оба триггера 1 и 2 в нулевое состояние по прямым вы.ходам (в единичное состояние по инверсным выходам ) и препятствует работе триггеров-1 и 2 в счетном режиме. По шине 9 корректируемой им пульсной последовательности на первые входы элементов 3 и 6 подана импульсная последовательность (фиг, и ЗА, которая, проходя через элементы б и 7 на шину- 11 устройства, одновременно инвертируется элементо 3 и подается на вход синхронизации триггера 1-(фиг. 2Б и ЗБ}. ири пода че по шине 8 сигнала управления сиг нала Логический О (фиг. 2В и ЗВ раз решается счетный режим работы триггеров 1 и 2. Первый же перепад из Логического О в Логическую 1 на входе синхронизации триггера 1 про . изводит его переключение. Второй перепад из Логического О в Логическую 1 на входе синхронизации триггера 1 переключает триггер 1 в исходное состояние, при этом на прямом выходе триггера 1 формируется единичный импулос (фиг. 2Г и ЗГ а на инверсном выходе - нулевой (фиг. 2Д и ЗД. Задний фронт импульса на инверсном выходе триггера 1 переключает триггер 2 в нулевое состояние по инверсному выходу (фиг. 2Е и ЗЕ), сигнал Логический подается на второй вход элемента 3 и запрещает подачу импульсной после довательности на вход триггера 1 (фиг. 2Б и ЗБ . Режим работы уст- , ройства Вычитание-добавление определяется подачей соответствующего сигнала по шине 10 командных импуль сов. При подаче сигнала ЛОГИЧЕСКИЙ Лфиг. 2Ж; устройство работает в режиме добавления импульса, при этом 1сигнал Логический О, поданный на вторые входы элементов 4 и 5, запре щает прохождение импульса, сформиро ванного на прямом выходе триггера 1 через элемент 5 и разрешает инверти рование импульса-, сформированного н инверсном выходе триггера 1, на эле менте 4 (фиг. 2,3) . На выходе элемен та 5 формируется сигнал Логичес-:..кая 1 (фиг. 2И-, который разрешает прохождение импульсной последовател ности через элемент 7. С выхода эле мента 4 импульс (фиг. 2 BJ подается на второй вход элемент 6. Фронты этого импульса отстоят от соответствующих фронтов переключения импульсов корректируемой последовательности на величину И Cxi - время задержки срабатыва Т- И 7 n TvlPiHT Л Тния элемента 3, t, - время задержки переключения триггера 1 ; - время задержки срабатывания элемента 4. Из-за несовпадения фронтов сформированного импульса и фронтов импульсов корректируемой последовательности на вьлходе элемента б появляются узкие импульсы с длительностью t, (фиг. 2KJ, что эквивалентно добавлению одного импульса в импульсную последовательность. Данная скорректированная последовательность импульсов через элемент 7 поступает в шину 11 выхода устройства. При подаче по шине 10 командных импульсов Вычестьдобавить сигнала Логическая 1 устройство работает в режиме вычитания импульса. Сигнал Логическая 1 подается на вторые входы элементов 4 и 5. Он разрешает инвертирование импульса, сформированного на прямом выходе триггера 1 (фиг. ЗИ на элементе 5и запрещает прохождение импульса, сформированного на инверсном выходе триггера 1, через элемент 4, при этом на выходе элемента 4 формируется сигнал Логический О (фиг. 3.3) , который разрешает неинвертированный проход корректируемой импульсной последовательности через элемент б на первый вход элемента 7. Импульс (фиг. ЗИ подается на второй вход элемента 7. ФронТЫ этого импульса отстоят от соответствующих фронтов переключения импульсов корректируемой последовательности на величину гг. аъ + И-,+ Ч Ъ( где t. - время задержки срабатыва ния элемента 5) - время задержки срабатывания элемента 6. Поэтому импульс, поданный на второй вход элемента 7, полностью перекроет импульс корректируемой последовательности, подаваемой на первый вход элемента 7, и запретит прохождение импульса корректируемой последо.вательности в шину 11 выхода устройства (фиг. ЗК). При подаче по шине 8 сигнала управления сигнала Логическая 1.устройство возвращается в исходное сос гояние. Предложенное устройство по срав- . нению с известными позволяет производить вычитание и добавление импульса по команде сигнала управления, момент пр:ихода которого может быть случаен. Таким образом, предложенное устройство не требует специальногр формирования сигнгша управления и привязки момента его прихода к фронтам импульсов корректируемой последовательности, что расширяет его область применения. Формула изобретения Устройство для вычитания и добавления импульса, срдержащее два D-три гера и элемент И, отличающе еся тем, что, с целью расширения области применения, в него введены два элемента И-НЕ, элемент ИЛИ-НЕ И элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход коfcoporo соединен с первым входом элеМента И, а первых вход - с шиной кор ректируемой последовательности импул сов и с первым входом первого злемен та Й-НЕ, выход которого подключен к входу первого триггера, а второй вход - к инверсному выходу и входу D второго триггера, входы R триггеров подключены к шине управления, а вход С второго триггер соединен с инверсным выходом и входом О первого триггера и с первым входом эле мента ИЛИ-НЕ, второй вход которого подключен к шине командных импульсов и к первому входу второго элемента И-НЕ, второй вход которого соединен с прямым выходом первого триггера, а выход - с вторым входом элемента И. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 585601, кл. Н 03 К 13/20, 1976. 2. Авторское свидетельство СССР 450346, кл. Н 03 К 13/20, 1973 (прототип).

. ГгПЛЛЛ rLrLTLTLn в JTJTJ L Гии

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ФАЗЫ | 1992 |

|

RU2028727C1 |

| Фазоимпульсный компаратор | 1986 |

|

SU1370761A1 |

| Формирователь импульсов (его варианты) | 1990 |

|

SU1837387A1 |

| Устройство генерации импульсов управления шаговым двигателем с электронной коррекцией | 1991 |

|

SU1829022A1 |

| Устройство для вычитания и добавления импульсов | 1989 |

|

SU1676077A1 |

| Формирователь импульсов | 1980 |

|

SU1083349A1 |

| ЦИФРОВОЙ АНАЛИЗАТОР ВРЕМЕИНЫХ ХАРАКТЕРИСТИК ТРАНЗИСТОРНЫХ СХЕМ | 1971 |

|

SU297011A1 |

| Устройство для вычитания и добав-лЕНия иМпульСОВ | 1979 |

|

SU815730A1 |

| Устройство для вычитания и добавления импульсов | 1986 |

|

SU1370755A1 |

| Устройство для формирования импульсных сигналов | 1990 |

|

SU1800599A1 |

Г

Д

Г, Л,

. X.

а

n ririJLri r

фаг.

кЯ жкхспсет

Авторы

Даты

1983-01-23—Публикация

1981-02-23—Подача