Изобретение относится к цифровой обработке сигналов и может быть использовано в системах цифровой фильтрации,в автоматизированных радиотехнических комплексах обработки информации и системах распознавания образов../

Известен цифровой фильтр с последовательной обработкой сигнала, содержсцций два регистра, один из которых служит для хранения коэффициентов фильтра, другой - для приема входных сигналов и задержки их на длительность , определяемую частотой поступления входных сигналов. С целью образования произведения входных сигналов на соответствующие коэффициенты, цифровой фильтр содержит также последовательные умножители, которые пре-, дусматривают наличие хотя бы одного сдвигового регистра, конъюнкторов и счетчиков. Выходы счетчиков подключены к параллельному многоразрядному сумматору, результат с которого заносится в аккумулятор. Последний формирует выходной сигнал, представленный параллельным двоичным кодом

Однако обработка входного сигнала, представленного последовательным двоичным кодом, начинается со старших разрядов. В силу этого невозможно сформировать значение i-го разряда выходного сигнала, не ожидая приема всех двоичных разрядов входного сигнала, что существенно сьижает : быстродействие фильтра. Кроме того, не предусмотрены средства для реализации алгориттиюв рекурсивной цифровой фильтрации, так как значение выходного сигнала представляется па10раллельным кодом, а обработка сигна лов производится последовательно. Преобразование параллельного двоичног6 кода в последовательный требует до- i полнительного времени.

15

Известен также рекурсивный цифровой фильтр, содержащий последовательно включенные первый сумматор,регистр задержки и второй сумматор, второй вход которого объединен- с первым вхо20дом первого сумматора, а выход подключен к второму входу первого сумматора и является выходом устройства 23.

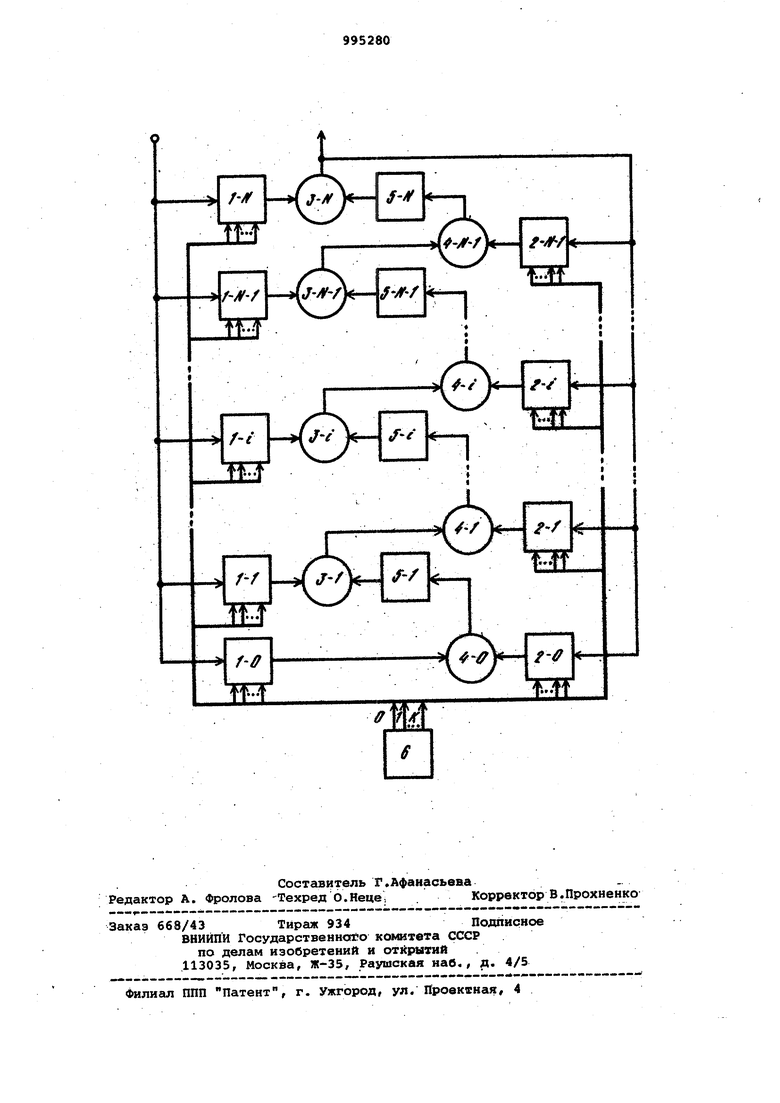

Улучшить амплитудно-частотную ха25рактеристику фильтра возможно путем увеличения его порядка. Известные соединения фильтров.первого порядка в систему цифровой фильтрации приводят к снижению быстродействия обра30ботки сигналов. Цель изобретения - повышение быс родействия. Поставленная цель досткгается те что в рекурсивный цифровой фильтр,с держащий последовательно соединенные первый умножитель,-первый cyhiMaTop, другой вход которого подключен к выходу регистра задержки, второй умножитель и второй сумматор, другой вход которого подключен к выходу третьего умножителя, вход которого объединен с входом первого умножителя и является входом устройства,введено (N-1)-цепей (где И - порядок фильтра , каждая из которых состоит из последовательно соединенных первого дополнительного умножителя,вход которого объединен с входом первого умножителя, первого дополнительного сумматора, к другому входу которого подключен выход дополнительного регистра задержки, и второго дополнительного сумматора, к. другому входу которого подключен выход второго допол ительного умножителя, вход которого объединен с входом второго умножителя, при этом вход дополнительного регистра задержки первой цепи подключен к выходу второго сукматора, вход дополнительного регистра за 1ержки i-ой цепи (где I 2, 3,.,.,14-1 подключен к выходу второго дополнительного сумматора U1)-ой цепи, а выход второго допол нительного сумматора {М--.1)-ой цепи подключен к входу регистра задержки На чертеже представлена структурная электрическая схема рекурсивного цифрового фильтра. Рекурсивный цифровой фильтр содержит умножители 1-0 - 1-N, из кото рах и-М)-ый является первьм умножителем, { -О-ый - третьим умножителем, а (l-l - 1-М-1)-ые г- первыми дополнительными умножителями введенных (N-1) цепей, умножители 2-0 2-N-1, из которых (2-0)-ой являются вторыми умножителями, а (2-1 2-N-i)- вторыми дополнительными умножителями введенных (N-1) цепей, сумматоры 3-1 - 3-и, из которых(3-1 3-N-l)-ыe являются первыми дополнительными умножителями введенных (М-1) цепей, а сумматор 3-Я- первым сумматором, сумматоры 4-0 - 4-N-1, из которых сумматор 4-0 является вто рым, а сумматоры (4-1 -4-N-1) - вторыми дополнительными, регистры задержки 5-1-5-N, из которых регистры 5-1 - ) задержки являются дополнительными , и кольцевой регистр б предназначенный для управления рабол той умножителей 1-0 - l-Nn 2-0 -2-Мт1, .Цифровой фильтр работает следующим образом. На его вход в моменты времени t тТ;пГГ + Го .,.,тТ+4Г ,...,тГ + и-.(К -1)Тпоступает последовательность двоичных ЦИФР T( |(т),... ,f..H, котсфая задает m -и отсчет входного сигнала х(т) в соответствии с выражением .lni). isO В ЭТИ моменты времени на выходе цифрового фильтра формируется последовательность двоичный цифр (Ь ) , ) 1 --jli) которая является двоичным представлением т-го значения выходного сиг-, нала. fc-t . /iXTOJ-EIiitw, , - где ,Т - интервал дискретизации, Г - интервал времени между последовательно поступающими i-м и (1-И)-м двоичными разрядами, к - количество двоичных разрядов в кодах сигналов. Фильтр реализует зависимость между входным и выходньокш сигналами вида N N тЬ1 oU)x(m-j)-C i(j)v(), jcOjrl где a(j) и.b((j) - коэффициенты фильтра, а N - порядок фильтра. Коэффициенты a(j)K ЪУ) , представ л брнные в виде двоичн;: чисел o()J ,(fb cto(j)(.(n ic-2U - PoO) ° ответственно, хранятся в умножителях в следухкцем порядке: умножитель 1-N содержит коэффициент а(0), умножитель l-1-aU) (где 1,2,.. .,N-1) , умножитель 1-0-а(М, умножитель ) (где I 1,2,...,N-1}, умножитель 2-0-WNK Входной сигнал xlm) поступает на входы умножителей 1-0 - 1-N поразрядно, начиная с млгцдшего разряда fod), где производятся поразрядные умножения на соответствующие коэффициенты с последовательной выдачей результатов произведения на соответствующие бходы сукматоров 3-1 3-N и 4-0. На другие входы сумматоров 3-1 - 3-Н также последовательным кодом синхронно С; выходами умножителей 1-1 - 1-м выдаются двоичные числа промежуточных вычислений из соответствующих регистров задержки 5-15-М. В результате на выходе сумматора 3-М происходит поразрядная выдача выходного сигнала :/(т, начиная 9 мпсцфпего |раэряда ({«(т). Этот сигнал по цепи обратной связи аналогично

входному сигналу поступает на входы умножителей 2-0 - 2-N-1, где производится поразрядное умножение на боответствующие коэффициенты с последо вательной выдачей результатов пронэведения в соответствукнцие сумматоры 4-0- 4-N-1, на входы KOTOptjix последовательным кодЬм поступают результаты вычислений сукматора 3-N-1 и умножит1еля 1-0 соответственно. Результаты сложения также последовательным кодом записываются соответствующие регистры 5-1 - 5-N задержки, выталкивая поразрядно предыдущие значен1;я промежуточных вычислений.

Достоинством предлагаемого устройства, является выЬбкое быстродействие последовательной обработки сигнала, которое не зависит от порядка фильтрации. В свою очередь, возмож ность увеличения порядка фильтра позволяет достичь требуемой ацдаитудночастотной ха.рактернстики. Особенно эффективно использование устройства в 1Д1фРОВьос системах, s которых до „и после цифрового производится последовательная обработка данншс, начиная с мяадцшх разрядов. Такие систекол обладают заметным преимуществен по аппаратурным затратам по сравнению с системами с параллельной, обработкой данЫх.

Формула изобретения

Рекурсивный цифровой фильтр, со держащий последовательно соединенные первый умножитель, первый сумматор.

другой вход которого подключен к выходу регистра задержки, второй умножитель и второй суммат.ор, другой вход которого подключен к ВЕЛХОДУ третьего умножителя, вход которого . объединен с входом первого уьроясителя и является входом устройства, о тл и ч а ю щ и и с я тем, что,, с целью повышения быстродействия, в нехЧ) введено (N- цепей Л где N - порядок фильтра}, кгикдая из -которь

состоит из последовательно соединен- ных первого дополнительного умножи-. теля, вход которого oбvвдинвн с вхо-. дом первого умножителя, первого . дополнительного сумматора к другому

входу которого подключен В1лсод дополнительного регистра задержки, а вточ-.: рого дополнительного су Ф«атора, к г другому входу которого подключен выход второго дополнительного умножителя, входзГ которого объединен с входом втсфого умножителя, при этом вход дополнительного- регистра задержки первой цепи подключен к выходу второ го сумматора, вход дополнительного.

регистра задержки i -И цепи (где :

i 2,3,...,N-1} подключен к выходу второго дополнительного сумматора (.1-1)й цепи, а выход второго дополнительного сумматора IN-1)-и цепи подключен к входу регистра задержки.

Источники информации,

принятые во внимание при экспертизе

1.Патент США 3732409 кл. 235-164, 1973.

2.Финкельштейн М.И. Гребенчатые фнльтры. И., Советское радио, 1969,

с. 58, рис. 2.4.4;i (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Рекурсивный цифровой фильтр | 1985 |

|

SU1264307A1 |

| Цифровой рекурсивный фильтр | 1985 |

|

SU1328925A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| СПОСОБ ЦИФРОВОЙ РЕКУРСИВНОЙ ПОЛОСОВОЙ ФИЛЬТРАЦИИ И ЦИФРОВОЙ ФИЛЬТР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 2011 |

|

RU2460130C1 |

| Рекурсивный цифровой фильтр | 1986 |

|

SU1385264A1 |

| Арифметическое устройство | 1978 |

|

SU763894A1 |

| Цифровой фильтр | 1985 |

|

SU1244786A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

Авторы

Даты

1983-02-07—Публикация

1980-07-10—Подача