Изобретение относится к вычислительной технике и может быть использовано в измерительных устройствах систем автоматического управления, связи и акустической технике.

Известен рекурсивный цифровой фильтр второго порядка, содержащий элементы задержки, матричные блоки умножения, преобразователи кода и сумматор на пять входов. Данный фильтр имеет высокое быстродействие (1 мкс) благодаря применению матричных блоков умножения и выполнению остальных операций в параллельных кодах. Однако он имеет фиксированные связи, т. е. настроен на передаточную функцию одного вида, причем с большими аппаратурными затратами. Сложность фильтра обусловлена применением пяти матричных блоков умножения, а также тем, что умножение выполняется в прямых кодах, а алгебраическое сложение - в дополнительных. Поэтому на выходах блоков умножения введены преобразователи прямого кода в дополнительный, а на выходе сумматора происходит преобразование дополнительного кода в прямой. Блок управления в указанном фильтре отсутствует, но его функции по организации последовательности выполнения операций распределены между дополнительными элементами задержки, связанными с выходами блоков умножения. С учетом упомянутых элементов задержки входных и выходных сигналов общее количество элементов задержки достигает одиннадцати, причем каждый из них выполнен в виде многоразрядного регистра.

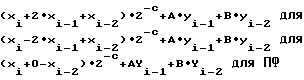

Недостатки вышеуказанного фильтра частично устранены в программируемом рекурсивном цифровом фильтре второго порядка, содержащим регистры, два блока умножения, блок синхронизации, сумматоры, мультиплексоры, а также два сдвиговых регистра, дешифратор, два блока инвертирования знака, регистр константы и триггер. В этом фильтре создается возможность оперативной перестройки частотных характеристик, причем не только путем смещения частот среза, но и путем преобразования формы характеристик. Фильтр реализует систему разностных уравнений цифровых фильтров второго порядка, в том числе полосового фильтра (ПФ), фильтра нижних частот (ФНЧ) и фильтра верхних частот (ФВЧ):

;

;  где Хi и Yi - текущие значения входного и выходного сигналов;

где Хi и Yi - текущие значения входного и выходного сигналов;

Хi-1, Хi-2, Yi-1, Yi-2 - предшествующие значения переменных;

А, В - весовые коэффициенты;

С - константа масштабирования.

Возможность оперативной трансформации передаточной функции и сброса содержимого регистров хранения и элементов задержки расширяет класс решаемых задач, например, в адаптивных системах автоматического регулирования.

Однако наличие выходного регистра фиксации результата уменьшает быстродействие фильтра. Кроме того, масштабирующий множитель выбран фиксированным, что затрудняет работу фильтра при скачкообразном изменении отношения сигнал/шум на его входе. Наиболее близким по технической сущности к предлагаемому является программируемый рекурсивный цифровой фильтр второго порядка, включающий в себя четыре регистра, два мультиплексора, регистр константы, дешифратор, три блока умножения, два блока инвертирования знака, три сдвиговых регистра, блок синхронизации, три сумматора, блок суммирования, состоящий из комбинированного сумматора и триггера округления результатов вычисления.

Недостатком данного фильтра является недостаточно высокое качество фильтрации.

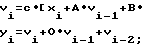

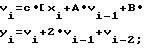

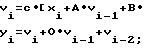

Цель изобретения - повышение качества фильтрации за счет введения двойной обратной связи по ошибке квантования. Фильтр реализует систему разностных уравнений цифровых фильтров второго порядка, в том числе ПФ, ФНЧ и ФВЧ с двойной обратной связью по ошибке квантования:

vi-2-K1·li-1-K2·li-2] ; (2)

vi-2-K1·li-1-K2·li-2] ; (2)

vi-2-K1·li-1-K2·li-2] ; (3)

vi-2-K1·li-1-K2·li-2] ; (3)

vi-2-K1·li-1-K2·li-2] ; (4) где Vi, Vi-1, Vi-2 - текущие значения переменных;

vi-2-K1·li-1-K2·li-2] ; (4) где Vi, Vi-1, Vi-2 - текущие значения переменных;

li-1, li-2 - текущие значения ошибки квантования;

K1, K2 - весовые коэффициенты умножителей по ошибке квантования.

Возможность реализации одной из трех систем уравнений (2) - (4) обеспечивается благодаря дешифратору кода передаточной функции фильтра, мультиплексорам, первому, второму и третьему сумматорам. Использование преобразователей параллельного кода в последовательный и трех блоков умножения создает возможность смены весовых коэффициентов и константы масштабирования. Инверторы знака и блок суммирования позволяют перестраивать рекурсивную часть систем уравнений (2) - (4).

Несмотря на очевидное достоинство используемых в прототипе и в предлагаемом фильтре умножителей, вследствие усечения с округлением результата умножения двух операндов для того, чтобы разрядность результата умножения была равна разрядности множителя и множимого (в нашем случае N = 10), возникают шумы квантования, которые существенно влияют на такие параметры фильтра, как динамический диапазон, отношение сигнал/шум и другие точностные показатели. Наиболее явно эффект усечения выходного сигнала проявляется при подаче на вход программируемого рекурсивного цифрового фильтра второго порядка слабых сигналов, т. е. при малых отношениях сигнал/шум. Возможный путь для устранения этого недостатка - применение операндов двойной длины. Однако техническая реализация таких устройств приводит к удвоению аппаратурных затрат. В предложенном фильтре указанный недостаток устранен введением двойной обратной связи по ошибки квантования.

Обозначим через Yi выходной сигнал фильтра без усечения, а через  усеченный выходной сигнал. Выразим

усеченный выходной сигнал. Выразим  через входной сигнал Хi и ошибку усечения li. Сигнал Yi связан с усеченным выходом

через входной сигнал Хi и ошибку усечения li. Сигнал Yi связан с усеченным выходом  и ошибкой усечения выражением

и ошибкой усечения выражением

Y(i) =  (i) + l(i). (5)

(i) + l(i). (5)

В случае введения двойной обратной связи по ошибке квантования разложенное уравнение для реализации программируемых фильтров второго порядка приобретает вид

y(i)=  ai·x(n-i)+

ai·x(n-i)+ b

b (n-1)-

(n-1)- Ki·l(n-i)

Ki·l(n-i) . (6)

. (6)

Как видно из выражения (6), сигнал ошибки сначала задерживается, а затем возвращается на сумматор умноженным на коэффициенты Ki. Коэффициенты K1 и K2 выбраны равными соответственно 0,5 и 0,25. В этом случае умножение сводится к простому сдвигу соответственно на один и два разряда в сторону младших разрядов. В частотной области выражение (6) можно представить в общем виде так (Z)= X(Z) [(

(Z)= X(Z) [( ai·Z-1)/(1-

ai·Z-1)/(1- bi·Z-1)] -E(Z)[(1)/(1-

bi·Z-1)] -E(Z)[(1)/(1- Ki·Z-1)] . (7)

Ki·Z-1)] . (7)

Уравнение (7) показывает, что спектр усеченного выходного сигнала равен спектру входного, умноженного на передаточную функцию идеального фильтра, минус спектр E(Z) ошибки усечения, умноженный на некоторую "функцию ошибки". Как видно из выражения (6), в предельном случае коэффициенты Ki могут быть выбраны равными значениям полюсов (коэффициенты bi). В этом случае нет усиления Е(Z) полюсами фильтра, что особенно эффективно в звуковых системах, в частности в проигрыва- телях компакт-дисков. Кроме того, в таких устройствах особую осторожность нужно соблюдать на граничных частотах, т. е. частотах, близких к положению полюсов и частоте Найквиста, где сказываются эффекты близости комплексно-сопряженных полюсов. Необходимо заметить, что введение дополнительной обратной связи по ошибке квантования ухудшает отношение сигнал/шум, так как в младших разрядах выходного слова содержится аддитивная смесь сигнала с шумом. Этот недостаток устраняется предложенным фильтром за счет увеличения значения константы масштабирования.

Перестройка фильтра производится после записи промасштабированного вектора состояния во второй регистр хранения. Время перестройки определяется задержкой на сумматорах комбинационного типа и равно для ИМС 564 серии примерно 50 -80 нс. В cлучае применения матричных БИС типа Н1537ХМ1 время перестройки уменьшается до 10-15 нс. В первом аналоге длительность цикла в 1 мкс достигается за счет сокращения процесса умножения до одного такта, но для этого требуются матричные блоки умножения, каждый из которых (а их в фильтре всего пять) при выполнении в виде БИС на базовых матричных кристаллах соизмерим по габаритам с предложенным фильтром. Кроме того, при большой сложности он имеет фиксированные связи между блоками, т. е. настроен на передаточную функцию одного вида.

По сравнению с вторым аналогом заявляемый фильтр обладает более высоким быстродействием, так как при его использовании отсутствует необходимость в выходном регистре фиксации результата, что сокращает цикл вычисления на 0,5 такта. Кроме того, сокращаются аппаратурные затраты, что имеет существенное значение при проектировании БИС на базовых матричных кристаллах. Во-вторых, путем введения третьего множительного устройства устраняется другой существенный недостаток второго аналога, в котором масштабирующий множитель выбирается фиксиро- ванным. В заявляемом фильтре коэффициент масштабирования можно менять от 0 до 1. Это особенно важно в случае скачкообразного изменения отношения сигнал/шум входного сигнала.

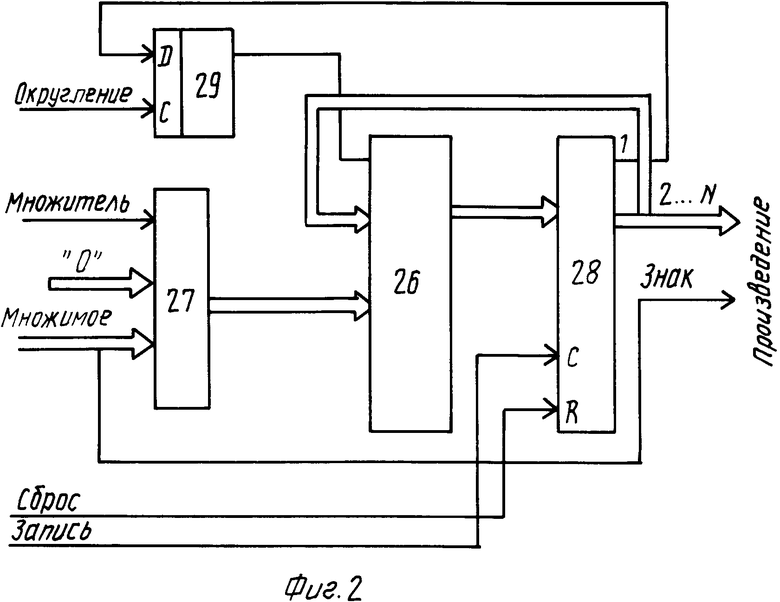

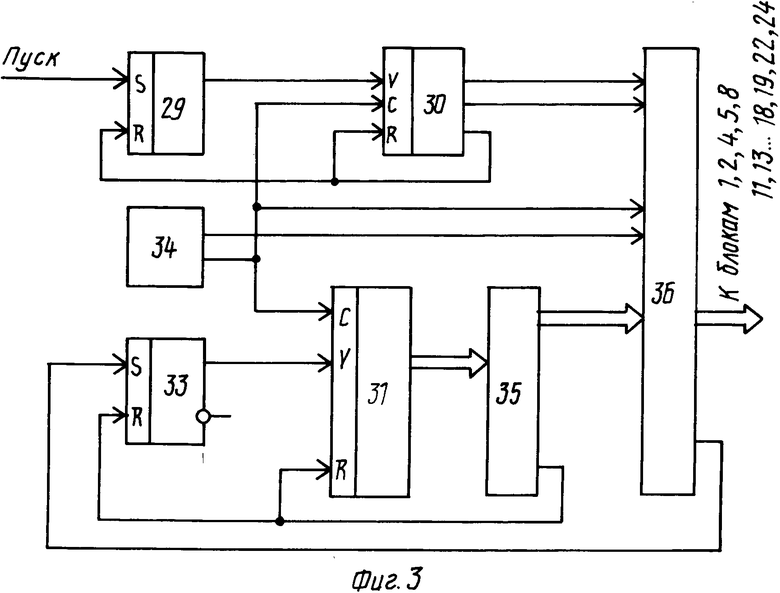

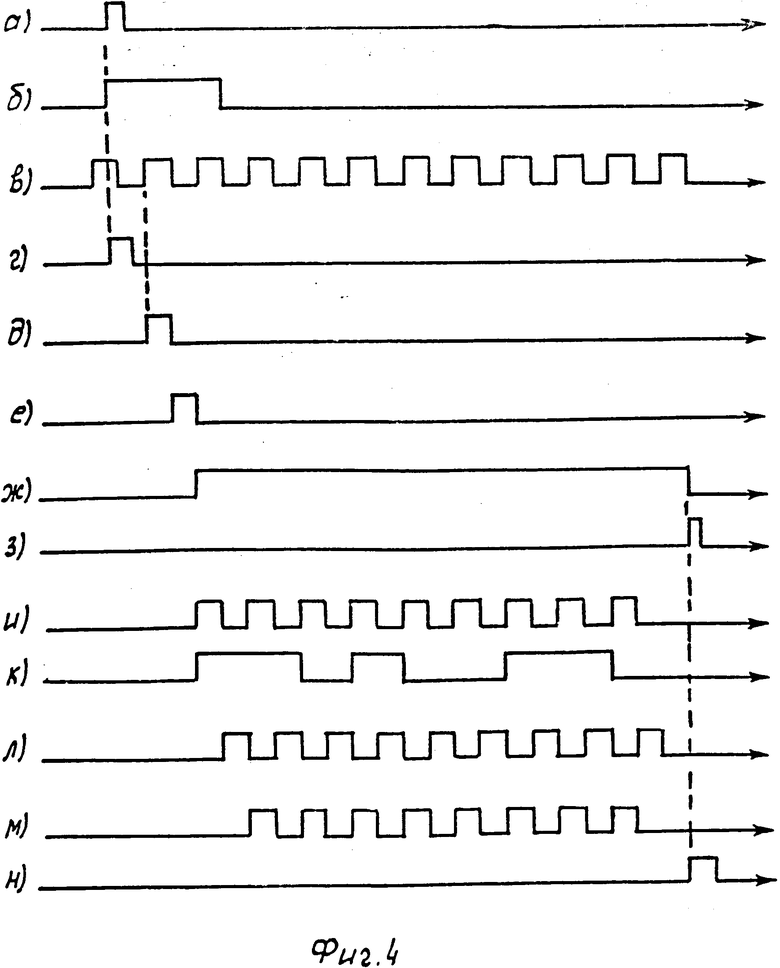

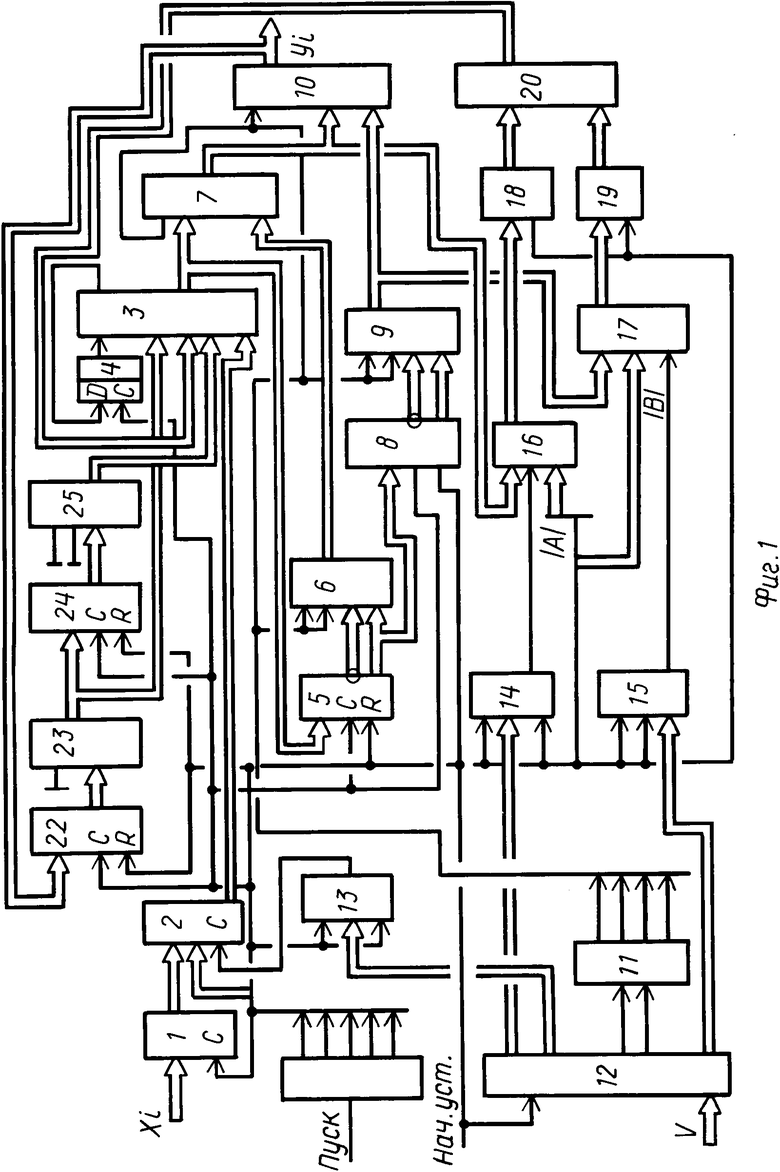

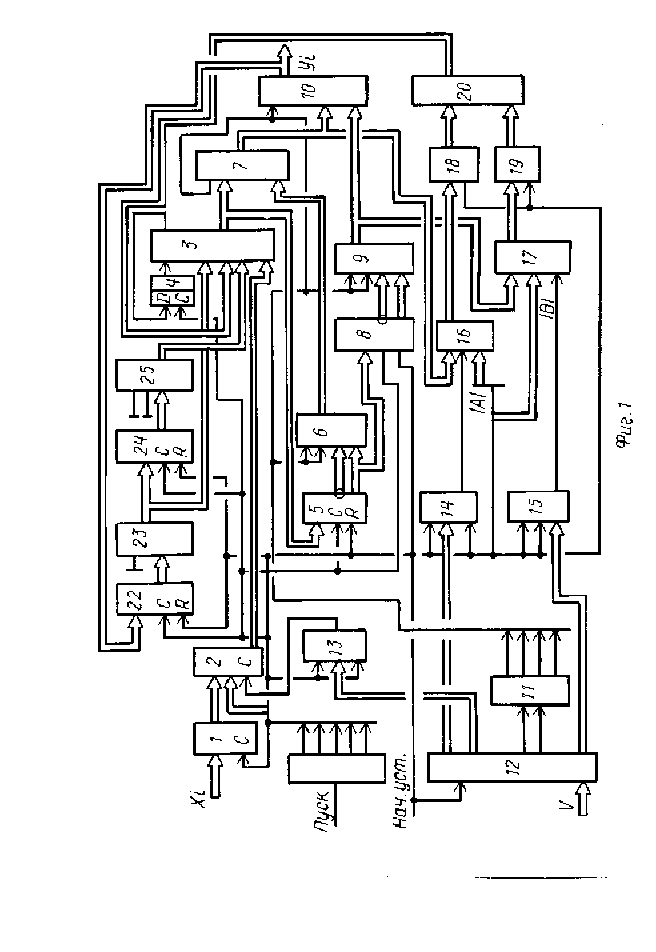

На фиг. 1 представлена функциональная схема программируемого цифрового фильтра; на фиг. 2 - схема блока умножения; на фиг. 3 - функциональная схема блока синхронизации; на фиг. 4 - временная диаграмма работы фильтра.

Программируемый цифровой фильтр содержит регистр 1 хранения текущего значения входного сигнала, выходом соединенный с входом множимого блока 2 умножения, выход которого соединен с вторым информационным входом комбинационного сумматора 3. Выход первого разряда сумматора 3 подключен к информационному входу D-триггера 4, выходом соединенного с входом переноса этого сумматора. Выходы остальных разрядов сумматора 3 соединены с информационным входом регистра 5, прямой и инверсный выходы которого соединены через мультиплексор 6 с первым информационным входом комбинационного сумматора 7. Прямой выход регистра 5 соединен с регистром 8, прямой выход которого соединен с информационным входом мультиплексора 9. Выход сумматора 7 и выход мультиплексора 9 соединены соответственно с первым и вторыми входами комбинационного сумматора 10. Выход сумматора 10 является выходом фильтра. Регистры 1, 5, 8, мультиплексоры 6 и 9 содержат N двоичных разрядов (в нашем примере N = 8). В разрядной сетке сумматоров 7 и 10 N+2 разряда, а сумматор 3 имеет N+1 разряд. Входы управления мультиплексоров 6 и 9 и входы переноса сумматоров 7 и 10 соединены с выходами дешифратора 11, соединенного с четвертым выходом регистра 12 хранения вектора состояния фильтра. Третий, второй и первый выходы регистра 12 хранения вектора состояния фильтра соединены с информационными входами преобразователей 13, 14, 15 параллельных кодов коэффициентов в последовательные коды множителей. Выходы сумматора 7 и мультиплексора 9 подключены к числовым входам множимого блоков 16 и 17 умножения соответственно. Выходы блоков 16 и 17 умножения связаны через блоки управляемых 18 и 19 инверторов с входами комбинационного сумматора 20, выход которого соединен с первым информационным входом сумматора 3. Входы управления блоков 18 и 19 соединены с выходами знаковых разрядов регистра 12. Входы множителей блоков 2, 16, 17 соединены с выходами преобразователей 13, 14, 15. Входы управления регистров 1, 5 и 8, преобразователей 13, 14 и 15 кода, блоков 2, 16, 17 умножения и тактовый вход D-триггера 4 соединены с соответствующими выходами блока 21 синхронизации, вход которого служит входом пуска цифрового фильтра. Младшая часть информационных разрядов (например, младшие пять разрядов) с выхода сумматора 10, который является выходом фильтра, поступает на информационный вход регистра 22, выход которого подключен к информационному входу комбинационного сумматора 23 со сдвигом на один разряд в сторону младших разрядов, что соответствует умножению на коэффициент 0,5. Выход комбинационного сумматора 23 подсоединен одновременно к третьему информационному входу комбинационного сумматора 3 и информационному входу регистра 24. Выход данного регистра подключен к входу комбинационного сумматора 25 со сдвигом на два разряда в сторону младших разрядов, что соответствует умножению на коэффициент 0,25. Выход сумматора 25 соединен с четвертым информационным входом комбинационного сумматора 3. Тактовые входы регистров 22 и 24 подключены к второму выходу блока 21 синхронизации, при этом установочные входы регистров 22 и 24 соединены с установочным входом регистра 12 константы.

Каждый из блоков 2, 16 и 17 умножения (фиг. 2) включает в себя разрядный комбинационный сумматор 26, мультиплексор 27, регистр-аккумулятор 28 и D-триггер 29. Выход мультиплексора 27 соединен с первым числовым входом сумматора 26, выход которого соединен с числовым входом регистра-аккумулятора 28, первым разрядом выходного слова подключенного к D-входу триггера 29, выход которого соединен с входом переноса сумматора 26. Остальные разряды регистра 28 соединены с разрядами 1. . . N+1 второго числового входа сумматора 26 с расширением (N-1)-го разряда на N-й разряд. Первый числовой вход мультиплексора 27 подключен к выходу регистра 1 хранения, выходу сумматора 7 или мультиплексора 9, а разряды второго числового входа соединены с шиной логического "0". Вход управления мультиплексора 27 служит входом множителя в прямом последовательном коде и соединен с выходом преобразователя 13, 14 и 15 кода соответственно. Входы записи и сброса регистра 28 подключены к соответствующим выходам блока 21 синхронизации. Выходы разрядов 2. . . N и знаковый разряд мультиплексора 27 образуют N-разрядный выход произведения в дополнительном коде.

Блок 21 синхронизации (фиг. 3) содержит двухразрядный счетчик 30, четырехразрядный счетчик 31, триггеры 32 и 33, тактовый генератор 34 и дешифраторы 35, 36. Тактовые входы счетчиков 30 и 31 соединены с выходом генератора 34, а входы управления - с выходами триггеров 32 и 33. S-вход триггера 32 служит входом импульса "Пуск" фильтра. Выход переполнения счетчика 30 соединен с входами триггера 32 и счетчика 30. Выходы счетчика 30 соединены со входом дешифратора 36, входы которого, кроме этого, соединены с парафазными выходами генератора 34, а также с выходами дешифратора 35, входом подключенного к выходу счетчика 31. Отдельный выход дешифратора 35 подключен к входам сброса счетчика 31 и триггера 33.

Преобразователи 13, 14 и 15 кода могут выполняться в виде регистра сдвига с параллельной записью весового коэффициента.

Предпочтительной элементной базой для реализации фильтра является полузаказная матричная БИС на базовых матричных кристаллах, выполненная по КМОП-технологии. Поэтому макет прототипа целесообразно изготовить на элементах 564 серии средней степени интеграции. Серия содержит функциональные блоки, используемые в предлагаемом фильтре, в том числе регистры хранения и сдвига, мультиплексоры, комбинационные сумматоры.

Предлагаемый цифровой фильтр работает следующим образом.

Для настройки фильтра на выбранную передаточную функцию в регистр 12 импульсом "Начальная установка" вводится вектор состояния V(F, А, B, С), где F - двухразрядный код передаточной функции. Тем же импульсом стирается содержимое регистров 5, 8, 22, 24. Содержимое регистра 12 сохраняется на время работы с заданной передаточной функцией фильтра. Результатом начальной установки является выбор одной из трех систем уравнений (2)-(4), которые можно записать следующим образом:

ll-1K2·li-2] ; где α, β- переменные на выходе дешифратора 11, зависящие от кода F, который принимает значение 01 для ФНЧ, 10 для ФВЧ и 11 для ПФ. Дешифратор 11 обеспечивает формирование функций α(F) и β(F):

ll-1K2·li-2] ; где α, β- переменные на выходе дешифратора 11, зависящие от кода F, который принимает значение 01 для ФНЧ, 10 для ФВЧ и 11 для ПФ. Дешифратор 11 обеспечивает формирование функций α(F) и β(F):

и F= 10; Константа масштабирования С не зависит от кода F и определяется расчетнымпутем в зависимости от вида сигнала на входе и величины модуля передаточной функции фильтра.

и F= 10; Константа масштабирования С не зависит от кода F и определяется расчетнымпутем в зависимости от вида сигнала на входе и величины модуля передаточной функции фильтра.

При настройке на ФНЧ между блоками фильтра устанавливаются следующие связи: мультиплексор 6 подключает прямой выход регистра 5 к второму входу сумматора 7, мультиплексор 9 соединяет прямой выход регистра 8 с вторым входом сумматора 10, на входы переноса сумматоров 7 и 10 из дешифратора 11 подается потенциал логического "0".

При настройке на ФВЧ мультиплексор 6 соединяет инверсный выход регистра 5 с входом сумматора 7, а мультиплексор 9 - прямой выход регистра 8 с входом сумматора 10, на вход переноса сумматора 7 из дешифратора 11 поступает потенциал логической "1", а на вход переноса сумматора 10 - потенциал логического "0".

При выборе ПФ мультиплексор 6 запирается и выдает нули по всем разрядам на вход сумматора 7, мультиплексор 9 соединяет инверсный вход регистра 8 с входом сумматора 10, на вход переноса сумматора 7 из дешифратора 11 поступает потенциал логического "0", а на вход переноса сумматора 10 - потенциал логической "1".

В любом из рассмотренных вариантов настройки ЦФ завершается не более чем через 0,1. . . 0,15 мкс после записи вектора состояния в регистр 12.

Текущее значение переменной Yi на выходе фильтра вычисляется циклически с частотой выборки входной переменной Хi. Эта частота зависит от быстродействия внешнего источника информации. Последний по мере готовности нового значения Хi на входе регистра 1 посылает импульс "Пуск" на вход блока 21 синхронизации (фиг. 4а) и с этого момента начинается цикл работы фильтра. В блоке синхронизации триггер 32 переходит в состояние "1" (фиг. 4б) и остается в нем в течение двух тактов генератора 34 (фиг. 4в). Импульс "Пуск" используется и как команда пересылки числа из регистра 5 в регистр 8, а из регистра 22 через сумматор 23 в регистр 24.

В результате в регистре 8 записывается значение Vi-1, а в регистре 24 - значение ошибки квантования li-2 (фиг. 4г). Дешифратор 36 по первому тактовому импульсу формирует импульс передачи содержимого регистра 1 в регистр 5 и младших разрядов с выхода сумматора 10 в регистр 22 (фиг. 4д), благодаря чему запоминаются новые значения Vi-1 и li-1 соответственно. В первой половине второго такта дешифратор 36 формирует импульс записи очередного значения в регистр 1 (фиг. 4е). Этим же импульсом производятся сброс регистров 28 в блоках 2, 16 и 17 умножения, а также запись младших весовых коэффициентов А, В и С в прямом коде в преобразователи 13, 14 и 15. Во втором такте дешифратор 36 переводит триггер 33 в состояние "1" (фиг. 4ж), триггер 32 возвращается в нулевое состояние импульсом переполнения счетчика 30. Триггер 33 разрешает работу счетчика 31, с помощью которого формируется серия управляющих импульсов для преобразователей 13, 14 и 15 и блоков 2, 16 и 17 умножения. Серия заканчивается в начале (N+2)-го такта работы счетчика 31, когда дешифратор 35 фиксирует такт с указанным номером и возвращает триггер 33 в нулевое состояние (фиг. 4ж, з). В рассматриваемом примере блок 21 синхронизации выполнен для десятиразрядных коэффициентов А, В и С. Поэтому серия управляющих импульсов включает в себя девять импульсов сдвига для преобразователей 13, 14 и 15 (фиг. 4и), из которых модули коэффициентов А, В, С выходят младшими разрядами вперед (фиг. 4к), девять импульсов записи чисел из сумматоров 26 - в регистры 28 (фиг. 4л), восемь импульсов записи содержимого первого разряда регистра 28 - в триггер 29 (фиг. 4м), импульс округления результата - в сумматор 3 (фиг. 4н).

Так как сумматоры 3, 7, 10, 23, 25 комбинационного типа, то тотчас после выполнения масштабирования входной переменной с помощью блока 2 умножения на выходе сумматора 3 появляется число Хi = Vi, на выходе сумматора 7 - число VK + α˙VK-1, на выходе сумматора 10 - число Vi + α˙Vi-1 + β˙Vi-2 = Yi, на выходе сумматора 23 - число Ki˙ li-1, а на выходе сумматора 25 - число K2 ˙li-2. В соответствии с выбранной передаточной функцией на выходе сумматора 10 получают значение выходного сигнала.

Операции умножения на коэффициенты А, В, С выполняются синхронно тремя умножителями следующим образом. Двоичная цифра последовательного кода множителя А, В, С управляет состоянием соответствующего мультиплексора 27 в блоках 2, 16 и 17 умножения. Если цифра множителя aj = = 0 (bj = 0), где j = 0,1,2. . . 8, то на выходе регистра-аккумулятора 28 будет число "0", а если aj = 1 (bj = 1) - число Vi-1 (в блоке 16), Vi-2 (в блоке 17) или Хi (в блоке 2). На выходе сумматора 26 в блоке 16 умножения в j-м такте образуется сумма

Zi,j = Vi-1˙ Aj + 0,5 ˙Zi,j-1 + qi-1 , где Zi,j-1 - число в регистре 24 к началу j-го такта;

qi-1 - цифра в триггере 29 к началу j-го такта.

Умножение на коэффициент 0,5 в указанных уравнениях обеспечивается за счет косых связей между выходами регистра-аккумулятора 28, т. е. за счет смещения содержимого регистра 28 на один разряд вправо. При таком сдвиге отбрасываемая цифра первого разряда записывается в триггер 29 и учитывается в следующем такте как цифра переноса в сумматоре 26. В середине каждого такта умножения число с выхода сумматора 26 записывается в регистр 28. К конце девятого такта умножения в блоке 16 умножения формируется число I А I˙Vi-1, в блоке 17 умножения - число I В I˙Vi-2, а в блоке 2 умножения - C˙ Хi. Если коэффициенты А и В принимают отрицательное значение, то произведение инвертируется по всем разрядам, а к содержимому младшего разряда добавляется единица. В результате число остается в дополнительном коде, но его знак меняется на противоположный. Если знак коэффициента положительный, то произведение передается через блок 18 или 19 без изменения, В случае работы блока 2 умножения блок инвертирования отсутствует, так как коэффициент С всегда положительный. Из условия устойчивости рекурсивного цифрового фильтра второго порядка модуль коэффициента А выбирается в пределах от 0 до 2, коэффициент В - от 0 до 1. Так как число А может быть больше единицы, то все множители приходится уменьшать вдвое. Поэтому сумма произведений передается с выхода регистра 28 на блок инверторов со сдвигом влево на один разряд. Кроме того, при передаче результата из блока 2 умножения, а из сумматора 20 соответственно на первый и второй входы сумматора 3 необходимо произвести сдвиг слагаемых на один разряд влево, т. е. тем самым восстановить истинные значения произведений на выходе блоков умножения. Во второй половине последнего такта работы блока 21 синхронизации число на выходе сумматора 3 округляется путем записи содержимого первого разряда этого сумматора в триггер 4 (фиг. 4н) с последующим добавлением этой цифры к содержимому младшего разряда по входу переноса. После округления число с выходов 2. . . N+1 подается на вход комбинационного сумматора 7, выход которого соединен с входом выходного сумматора 10, т. е. после сложения получается результирующее значение Yi выходного сигнала фильтра. При этом данный управляющий импульс возвращает триггер 4 в нулевое состояние и тем самым переводит цифровой фильтр в ждущий режим. Результирующее значение на выходе сумматора 10 получают в дополнительном коде.

Цикл работы фильтра от момента прихода импульса "Пуск" до получения результирующего значения Yi на выходе сумматора 10 включает в себя 1,5 такта формирования нерекурсивной части системы уравнений (2) - (4), М тактов умножения, 0,5 такта округления результата. Следовательно, длительность цикла составляет

tц = (2+М)˙ Т, где Т - период повторения импульсов тактового генератора 34;

М - количество разрядов модуля множителя.

В макете цифрового фильтра, выполненного на микросхемах 564 серии, при М = = 9 и тактовой частоте 2,1 МГц (Т = 0,476 мкс) на вычисление очередного значения Yi затрачивается время

tц = (2+9) ˙0,476 ≈5,24 (мкс)

С переходом на элементную базу БИС на базовых матричных кристаллах Н1537ХМ1 тактовая частота равна 10 МГц, так как длина связей между элементами на кристалле на 3-4 порядка меньше, чем в макете, это позволяет сократить цикл работы до 1,1 -1,2 мкс.

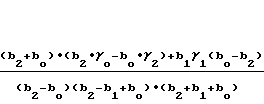

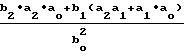

По сравнению с прототипом предложенный фильтр, во-первых, не уступает в быстродействии за счет того, что значение задержек отсчетов обратной связи по ошибке квантования li-1 и li-2 вычисляется одновременно с отсчетами Vi-1 и Vi-2. Во-вторых, предложенный фильтр превышает прототип по точности. Как показано, для вычисления суммарной дисперсии I шумов квантования фильтра второго порядка с передаточной функцией вида

H(Z)= [(bo+b1·Z-1+b2Z-2)/(1+a1·Z-1+a2Z-2)] применяется формула

I= [(1)/2πj)]  Y(Z)·Y(Z-1)dZ/Z .

Y(Z)·Y(Z-1)dZ/Z .

Так как данная формула довольно сложна для расчетов, требует вычисления вычетов и, как следствие, видов полюсов передаточной функции, расчетные соотношения для вычисления суммарной дисперсии 1 фильтра второго порядка следующие:

где γo= a2·ao/bo; γ1= [(a2·a1+a1·ao)/bo] -[(b1·a2·ao)/b

где γo= a2·ao/bo; γ1= [(a2·a1+a1·ao)/bo] -[(b1·a2·ao)/b

γ2=  _

_  +

+

Рассмотрим пример расчета ПФ с коэффициентами

bo = 0,125; ao = 1;

b1 = 0; a1 = -1,4375;

b2 = -1; а2 = 0,75.

Тогда расчетные значения соответственно равны γ0= 6, γ1= -2, γ2= 76,55.

Суммарное значение дисперсии шумов квантования равно

I = 35,46.

Значение дисперсии шумов квантования в децибеллах равно

σвых2 = 10 lg I = 15,49 (дБ)

В случае введения двойной обратной связи по ошибке квантования передаточная функция системы выражается формулой (7). Предположим, что Е(Z) - белый шум с равномерным распределением, тогда передаточную функцию обратной связи можно представить как

H′(Z)= 1/(1-K1·Z-1-K2·Z-2) ,

K2 = 0,25.

Это означает, что коэффициенты передаточной функции равны bo = 1, b1 = 0, b2 = 0, аo = 1, а1 = 0,5, а2 = 0,25.

Тогда γ0 = 0,25; γ1 = -0,375; γ2 = 1,875.

В этом случае значение суммарной дисперсии

I′= 1, 375.

Значение дисперсии в децибеллах равно

σ

Процентное соотношение дисперсии шума фильтра с обратной связью и без обратной связи (как в прототипе) выражается так

L = (I″/I)100% = (15,49-13,8)/15,49100% ≈10,9% .

Таким образом, введение двойной обратной связи уменьшает дисперсию шумов квантования и, как следствие, повышает качество фильтрации цифровых сигналов приблизительно на 11% .

Результаты экспериментов показывают, что в предлагаемом фильтре более высокая устойчивость коэффициентов передаточной функции и, как следствие, фильтра в целом по сравнению с прототипом, так как исчезают "мертвые" зоны на границах треугольника устойчивости, которые имели место в прототипе из-за нескомпенсированности шумов квантования. (56) Авторское свидетельство СССР N 1374244, кл. G 06 F 15/353, 1988.

Авторское свидетельство СССР

N 1592855, кл. G 06 F 15/353, 1990.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Программируемый цифровой фильтр | 1986 |

|

SU1374244A1 |

| Устройство для вычисления выражения вида @ | 1989 |

|

SU1644135A1 |

| Вычислительное устройство | 1984 |

|

SU1180883A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

Изобретение относится к вычислительной технике и может найти применение в системах автоматического регулирования и звуковой техники, в частности в проигрывателях компакт-дисков. Изобретение позволяет уменьшить суммарную дисперсию шумов квантования на выходе фильтра за счет введения двойной обратной связи по ошибке квантования и, как следствие, повысить качество фильтрации входных сигналов, увеличить функциональные возможности фильтра за счет оперативной трансформации передаточной функции и смены весовых коэффициентов. Отсчеты входного сигнала запоминаются в регистрах 1, 5 и 8. Масштабирование сигнала происходит с помощью блока 2 умножения. Вектор состояния фильтра вводится в регистр 12. Код передаточной функции поступает на вход дешифратора 11, а весовые коэффициенты в прямом параллельном коде - на вход преобразователей 13, 14 и 15 кода. Мультиплексоры 6 и 9 устанавливают связь между блоками, формирующими нерекурсивную часть системы разностных уравнений. Рекурсивная часть системы уравнений формируется блоками 16 и 17 умножения, блоками 18 и 19 управляемых инверторов и сумматором 20. Обе части уравнения объединяются сумматором 3, значение выходных сигналов вычисляется сумматором 10. Двойная обратная связь по ошибке квантования реализуется за счет задержки младшей части информационных разрядов с помощью регистров 22 и 24 и умножения на коэффициенты, кратные двойке, за счет сдвига соответственно на один и два разряда в сторону младших разрядов в сумматорах 23 и 25. Выходы сумматоров 23 и 25 соединены с соответствующими входами сумматора 3. 4 ил.

ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР, содержащий три регистра, два мультиплексора, регистр константы, дешифратор, три блока умножения, два блока управляемых инверторов, три преобразователя параллельного кода в последовательный, блок синхронизации, четыре сумматора, D-триггер, причем выход первого сумматора является выходом фильтра, первый информационный вход первого сумматора соединен с входом множимого первого блока умножения и с выходом первого мультиплексора, информационные входы которого соединены с прямым и инверсным выходами первого регистра, информационный вход которого соединен с прямым выходом второго регистра и первым информационным входом второго мультиплексора, второй информационный вход которого подключен к инверсному выходу второго регистра, выход второго мультиплексора соединен с первым информационным входом второго сумматора, выход которого соединен с вторым входом первого сумматора и входом множимого второго блока умножения, выход которого соединен с входом первого блока управляемых инверторов, выход которого соединен с первым информационным входом третьего сумматора, второй информационный вход которого соединен с выходом второго блока управляемых инверторов, информационный вход которого соединен с выходом первого блока умножения, входы множителя первого и второго блоков умножения соединены с информационными выходами соответственно первого и второго преобразователей параллельного кода в последовательный, входы которых соединены с первым и вторым выходами регистра константы, информационный вход которого является входом задания константы фильтра, входом запуска которого является вход запуска блока синхронизации, первый выход которого соединен с тактовым входом третьего регистра, тактовыми входами первого, второго регистров, D-триггера, выход которого соединен с входом переноса четвертого сумматора, выход первого разряда которого соединен с D-входом D-триггера, первый и второй информационные входы четвертого сумматора соединены соответственно с выходами третьего сумматора и третьего блока умножения, вход множимого которого соединен с выходом третьего регистра, вход множителя третьего блока умножения соединен с выходом третьего преобразователя параллельного кода в последовательный, информационный вход которого соединен с третьим выходом регистра константы, информационный вход третьего регистра соединен с одноименным входом фильтра, управляющие входы первого, второго и третьего блоков умножения соединены с вторым выходом блока синхронизации, третий выход которого соединен с тактовым входом первого, второго и третьего преобразователей параллельного кода в последовательный, четвертый выход регистра константы соединен с входом дешифратора, первый, второй, третий и четвертый выходы которого соединены с входами переноса второго и первого сумматоров, управляющими входами первого и второго мультиплексоров соответственно, информационный вход второго регистра соединен с выходом четвертого сумматора и вторым информационным входом второго сумматора , установочный вход регистра константы соединен с установочными входами первого и второго регистров и является установочным входом фильтра, четвертый и пятый выходы блока синхронизации соединены с управляющими входами соответственно первого и второго блоков управляемых инверторов, отличающийся тем, что фильтр дополнительно содержит четвертый и пятый регистры, пятый и шестой сумматоры, причем младшая часть разрядов выходного слова фильтра соединена с информационным входом пятого регистра, выход которого соединен с числовым входом пятого сумматора, выход которого соединен с третьим информационным входом четвертого сумматора и информационным входом четвертого регистра, выход которого соединен с информационным входом шестого сумматора, выход которого соединен с четвертым информационным входом четвертого сумматора, тактовые входы четвертого и пятого регистров соединены с первыми выходами блока синхронизации, установочные входы четвертого и пятого регистров соединены с установочным входом регистра константы.

Авторы

Даты

1994-01-30—Публикация

1991-10-28—Подача