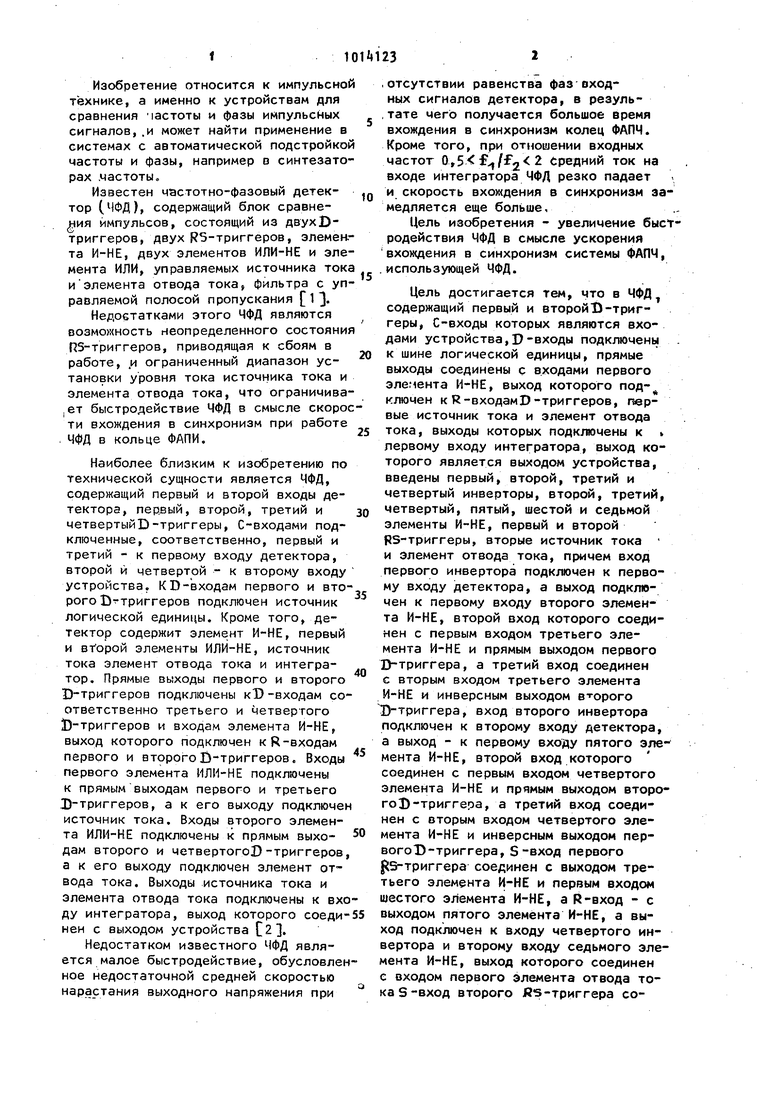

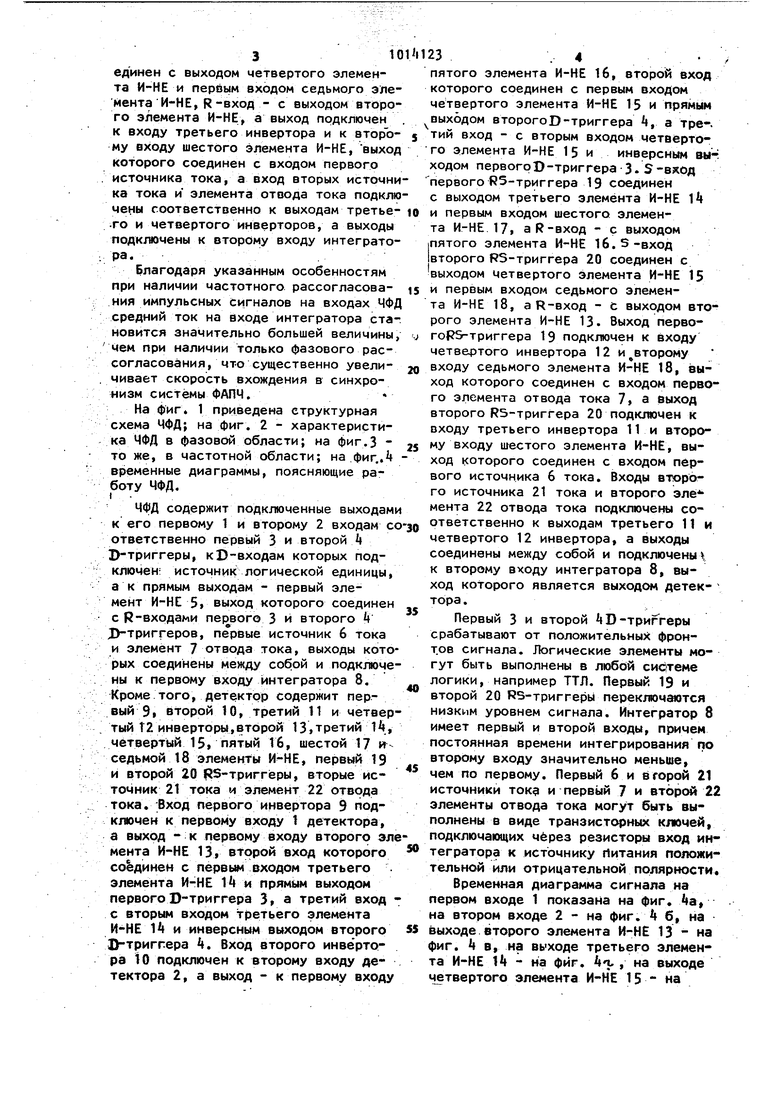

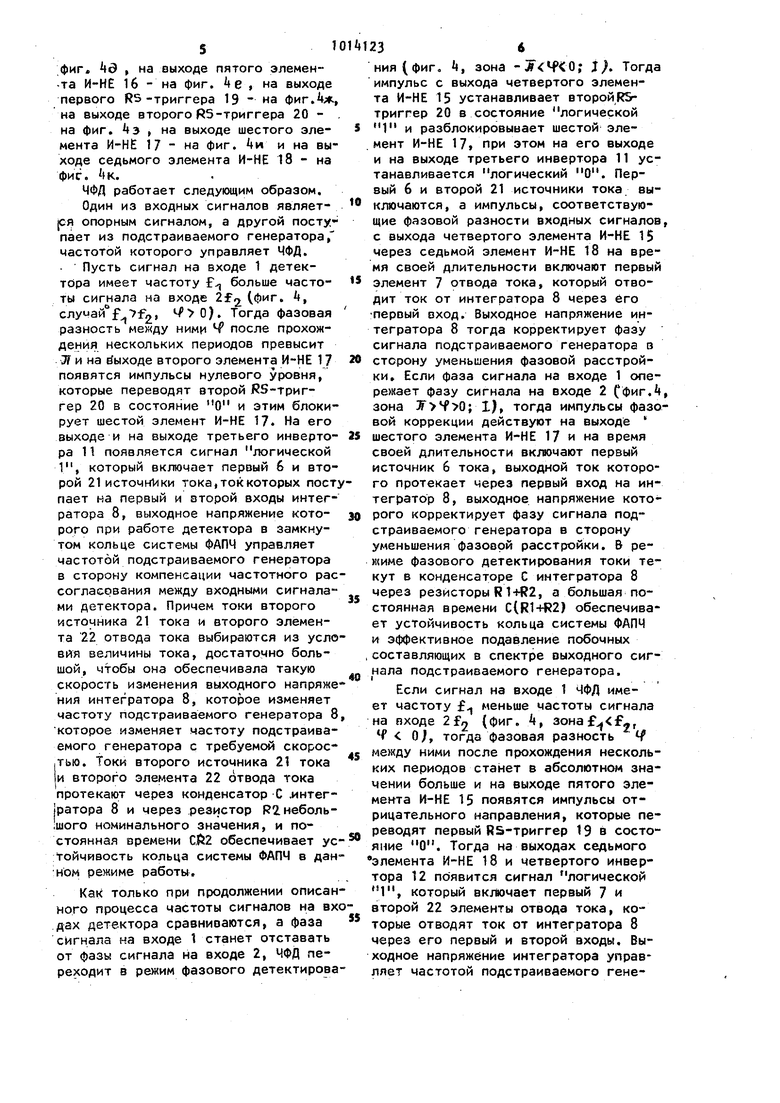

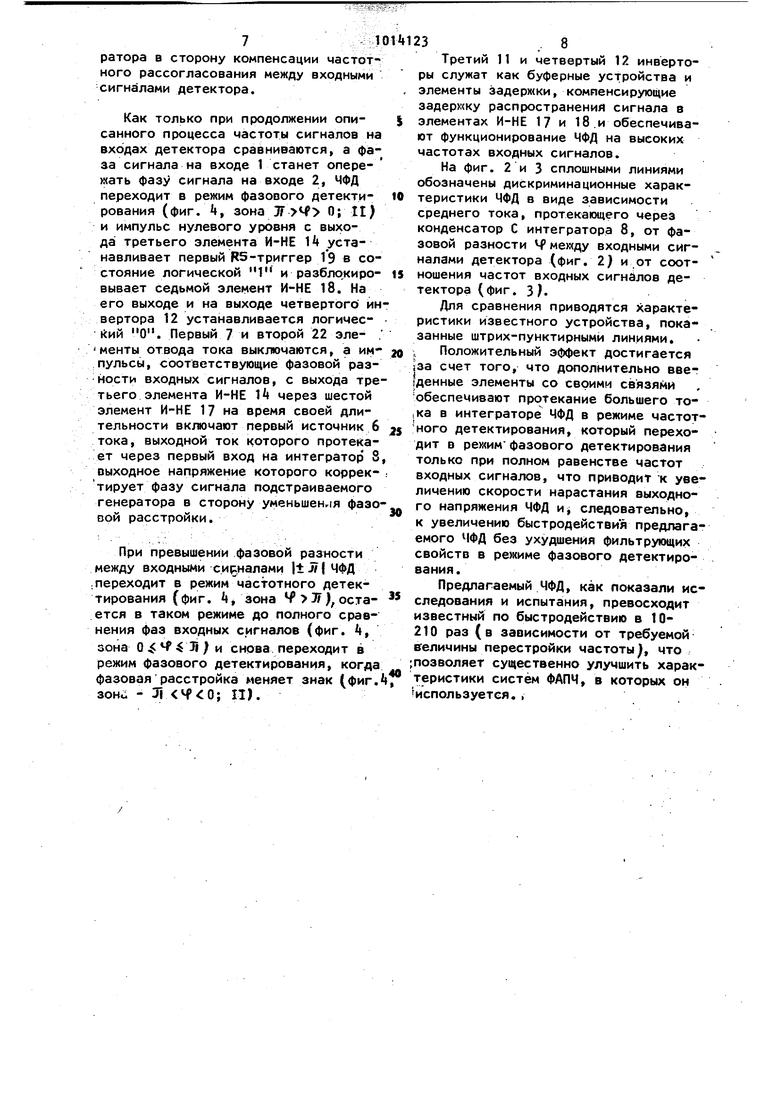

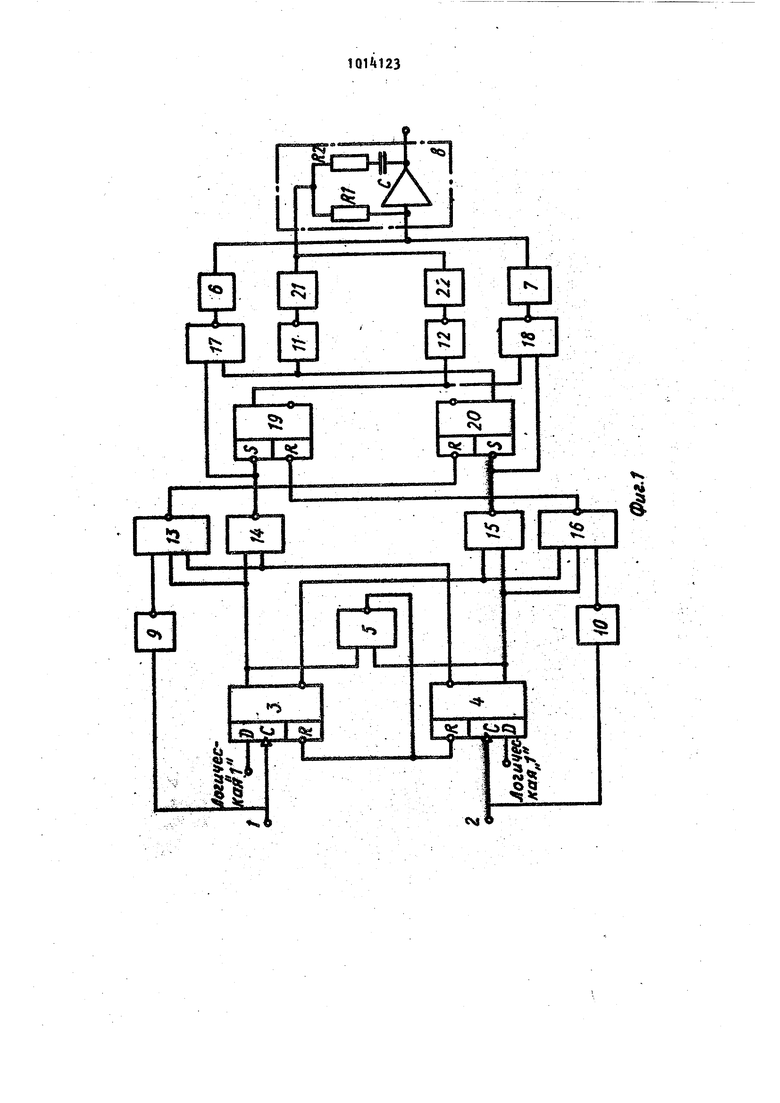

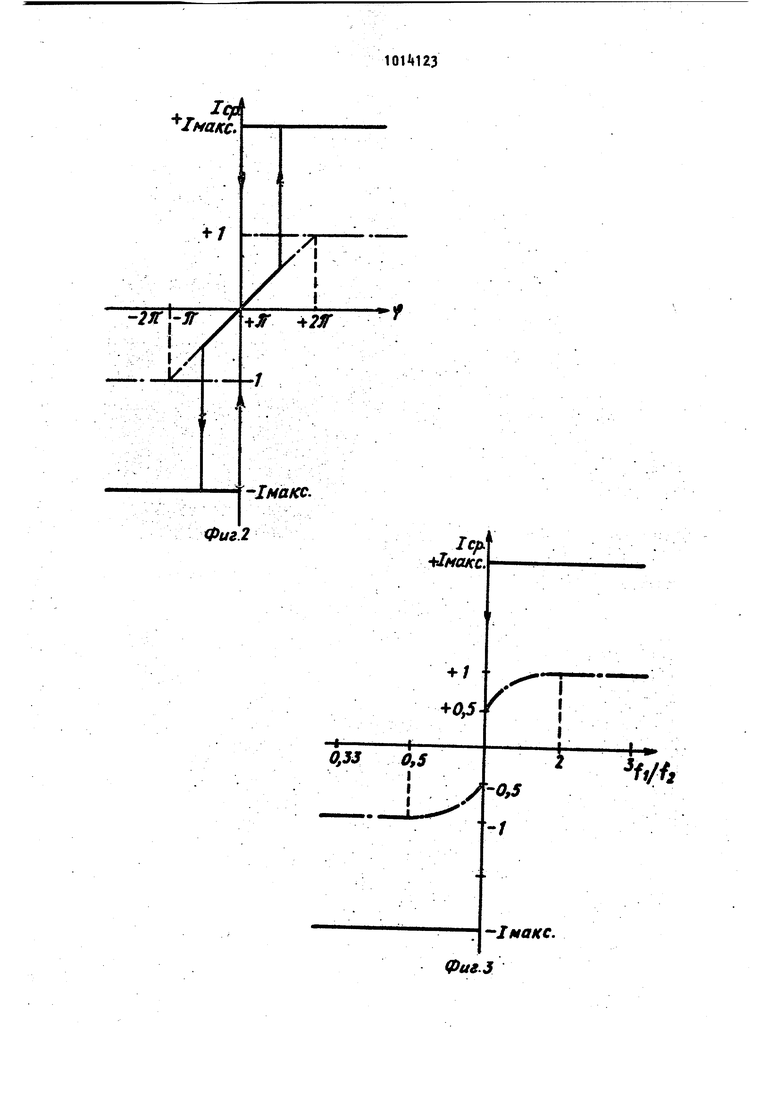

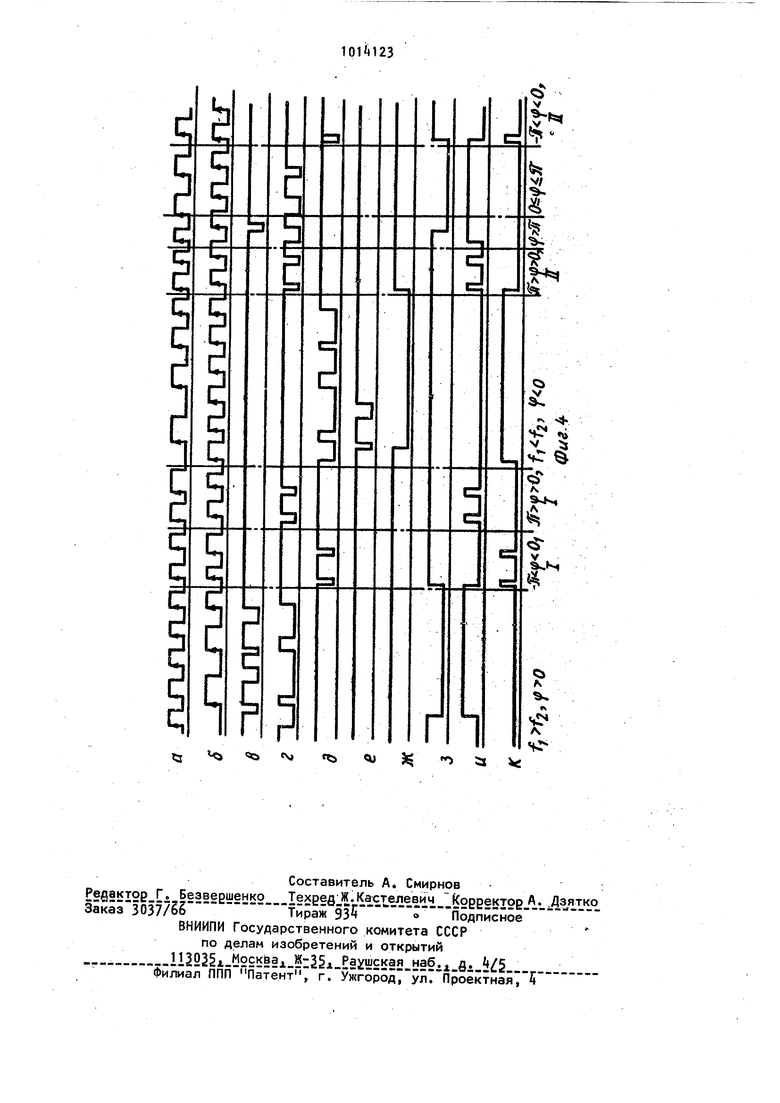

Изобретение относится к импульсной технике, а именно к устройствам для сравнения частоты и фазы импульсных сигналов,.и может найти применение в системах с автоматической подстройкой частоты и фазы, например в синтезаторах .частоты Известен частотно-фазовый детектор (ЧФД), содержащий блок сравне ия импульсов, состоящий из двухВтриггеров, двух RS-триггеров, элемента И-НЕ, двух элементов ИЛИ-НЕ и элемента ИЛИ, управляемых источника тока иэлемента отвода тока, фильтра с управляемой полосой пропускания 1 3Недостатками этого ЧФД являются возмо хность неопределенного состояния RS-триггеров, приводящая к сбоям в работе, ,и ограниченный диапазон установки уровня тока источника тока и элемента отвода тока, что ограничива,ет быстродействие ЧФД в смысле скорос ти вхождения в синхронизм при работе . ЧФД в кольце ФАПИ. Наиболее близким к изобретению по технической сущности является ЧФД, содержащий первый и второй входы детектора, первый, второй, третий и четвертыйО-триггеры, С-входами подключенные, соответственно, первый и третий - к первому входу детектора, второй и четвертой - к второму входу устройства. КD-входам первого и второго В-триггеров подключен источник логической единицы. Кроме того, детектор содержит элемент И-НЕ, первый и вУорой элементы ИЛИ-НЕ, источник тока элемент отвода тока и интегратор. Прямые выходы первого и второго D-триггеров подключены к1)-входам соответственно третьего и четвертого 1)-триггеров и входам элемента И-НЕ, выход которого подключен к R-входам первого и второго Ii-триггеров. Входы первого элемента ИЛИ-НЕ подключены к прямым выходам первого и третьего ДЗ-триггеров, а к его выходу подключен источник тока. Входы второго элемента ИЛИ-НЕ подключены к прямым выходам второго и четвертого)-триггеров а к его выходу подключен элемент отвода тока. Выходы источника тока и элемента отвода тока подключены к вхо ду интегратора, выход которого соединен с выходом устройства С 23. Недостатком известного ЧФД является малое быстродействие, обусловлен ное недостаточной средней скоростью нарастания выходного напряжения при отсутствии равенства фаз оходных сигналов детектора, в результате чего получается большое время вхождения в синхронизм колец ФАПЧ. Кроме того, при отношении входных частот 0,5 f-|/f2 2 Средний ток на входе интегратора ЧФД резко падает и скорость вхождения в синхронизм замедляется еще больше. Цель изобретения - увеличение быстродействия ЧФД в смысле ускорения вхождения в синхронизм системы ФАПЧ, использующей ЧФД. Цель достигается тем, что в ЧФД содержащий первый и второй)-триггеры, С-входы которых являются входами устройства,D-входы подключены к шине логической единицы, прямые выходы соединены с входами первого элемента И-НЕ, выход которого подключен к К-входамО-триггеров, первые источник тока и элемент отвода тока, выходы которых подк/почены к первому входу интегратора, выход которого является выходом устройства, введены первый, второй, третий и четвертый инверторы, второй, третий, четвертый, пятый, шестой и седьмой элементы И-НЕ, первый и второй RS-триггеры, вторые источник тока и элемент отвода тока, причем вход первого инвертора подключен к первому входу детектора, а выход подключен к первому входу второго элемента И-НЕ, второй вход которого соединен с первым входом третьего элемента И-НЕ и прямым выходом первого -триггера, а третий вход соединен с вторым входом третьего элемента И-НЕ и инверсным выходом второго -триггера, вход второго инвертора подключен к второму входу детектора, а выход - к первому входу пятого элемента И-НЕ, второй вход которого соединен с первым входом четвертого элемента И-НЕ и прямым выходом второго) -триггера, а третий вход соединен с вторым входом четвертого элемента И-НЕ и инверсным выходом перBoroD-триггера, S-вход первого Jits-триггера соединен с выходом третьего элемента И-НЕ и первым входом шестого элемента И-НЕ, а R-вход - с выходом пятого элемента И-НЕ, а выход подключен к входу четвертого инвертора и второму входу седьмого элемента И-НЕ, выход которого соединен с входом первого элемента отвода тока S -вход второго Ps-триггера соединен с выходом четвертого элемента И-НЕ и первым входом седьмого элемента И-НЕ,R-вход - с выходом второго элемента И-НЕ, а выход подключен к входу третьего инвертора и к вторЪму входу шестого элемента И-НЕ, выход которого соединен с входом первого источника тока, а вход вторых источника тока и элемента отвода тока подключены соответственно к выходам третье- ю и го и четвертого инверторов, а выходы подключены к второму входу интегратора. Благодаря указанным особенностям при наличии частотного рассогласования импульсных Сигналов на входах ЧФД средний ток на входе интегратора становится значительно большей величины чем при наличии только фазового рассогласования, что существенно увеличивает скорость вхождения в синхронизм системы ФАПЧ.« На фиг 1 приведена структурная схема ЧФД; на фиг. 2 - характеристика ЧФД в фазовой области; на фиг.3 то же, в частотной области; на фиг,,4 временные диаграммы, поясняющие работу ЧФД. ) . ЧФД содержит подключенные выходам к его первому 1 и второму 2 входам с ответственно первый 3 и второй Ц D-триггеры, KD-входам которых подключен: источник логической единицы, а к прямым выходам - первый элемент И-НЕ 5. выход которого соединен с R-входами первого 3 и второго if )-триггеров, первые источник 6 тока и элемент 7 отвода тока, выходы кото рых соединены между собой и подкшче ны к первому входу интегратора 8. Кроме того, детектор содержит первый 9 i второй 10, третий 11 и четвер тый 12инверторы,второй 13,третий 14, четвертый 15, пятый 16, шестой 17 ttседьмой 18 элементы , первый 19 и второй 20 RS-триггёры, вторые источник 21 тока и элемент 22 отвода тока, ;Вход первого инвертора 9 подключен к первому входу 1 детектора, а выход - к первому Входу второго эл мента И-НЕ 13, второй вход которого соединен с первым входом третьего элемента И-НЕ It и прямым выходом первогоD-триггера 3, а третий вход с вторым входом третьего элемента И-НЕ 1А и инверсным выходом второго D-триггера Ц. Вход второго инвертора to подключен к второму входу детектора 2, а выход - к первому входу 101 23.4 пятого элемента И-НЕ 1б, второй вход которого соединен с первым входом четвертого элемента И-НЕ 15 и прямым выходом BToporoD-триггера , а тре-. тий вход - с вторым входом четвертого элемента И-НЕ 15 и инверсным выг ходом первогоВ-триггера3.2-вход первого КЗ-триггера 19 соединен с выходом третьего элемента И-НЕ И первым входом шестого элемента И-НЕ 17, а R-вход - с выходом пятого элемента И-НЕ 1б.5-вход второго RS-триггера 20 соединен с выходом четвертого элемента И-НЕ 15 и первым входом седьмого элемента И-НЕ 18, а R-вход - С выходом второго элемента И-НЕ 13. Выход первогоРЭ-триггера 19 подключен к входу четвертого инвертора 12 и второму входу седьмого элемента И-НЕ 18, выход которого соединен с входом первого элемента отвода тока 7, а выход второго р5-триггера 20 подключен к входу третьего инвертора 11 и второму входу шестого элемента И-НЕ, выход которого соединен с входом первого источника 6 тока. Входы второго источника 21 тока и второго мента 22 отвода тока подключены соответственно к выходам третьего 11 и четвертого 12 инвертора, а выходы соединены между собой и подключены, к второму входу интегратора 8, выход которого является выходсж детек- тора. Первый 3 и второй «D-триггеры срабатывают от положительных фронтов сигнала. Логические элементы могут быть выполнены в любой сис:)теме логики, например ТТЛ. Первый 19 и второй 20 RS-триггерЫ переключаются низким уровнем сигнала. Интегратор 8 имеет первый и второй входы, причем постоянная времени интегрирования по второму входу значительно меньше, чем по первому. Первый 6 и вгорой 21 источники тока и первый 7 и вторс 22 элементы отвода тока могут быть выполнены в виде транзисторных ключей, подключающих через резисторы вход интегратора к источнику питания положительной или отрицательной полярности. Временная диаграмма сигнала на первом входе 1 показана на фиг. Ла на втором входе 2 - на фиг. 4 б, на выходе.второго элемента И-НЕ 13 - на фиг. Bf на выходе третьего элемента И-НЕ Н - на фиг. ь , на выходе четвертого элемента И-НЕ 15 на 1 фиг, д , на выходе пятого элемен-та И-НЁ 16 - на фиг. t е , на выходе первого RS-триггера 19 на фиг.Аж, на выходе второго R5-триггера 20 на фиг, 4э , на выходе шестого элемента И-НЕ 17 - на фиг. и и на выходе седьмого элемента И-НЕ 18 - на фиг. (К. . ЧФД работает следующим образом. Один из входных сигналов являет|ся опорным сигналом, а другой поступает из подстраиваемого генератора, частотой которого управляет ЧФД. Пусть сигнал на входе 1 детектора имеет частоту , больше частоты сигнала на входе 2f2 (фиг. Ц, слумай 2, ). Тогда фазовая разность между ними после прохождения нескольких периодов превысит JF и на ёыходе второго элемента И-НЕ 17 появятся импульсы нулевого уровня, которые переводят второй RS-триггер 20 в состояние О и этим блокирует шестой элемент И-НЕ 17. На его выходе и на выходе третьего инвертора И появляется сигнал логической 1, который включает первый 6 и второй 21 источкИки тока, ток которых пост пает на первый и аторой входы интегратора 8, выходное напряжение которого при работе детектора в замкнутом кольце системы ФАПЧ управляет частотой подстраиваемого генератора в сторону компенсации частотного рас согласования между входными сигналами детектора. Причем токи второго источника 21 тока и второго элемента 22 отвода тока выбираются из усло вия величины тока, достаточно большой, чтобы она обеспечивала такую скорость изменения выходного напряже ния интегратора 8, которое изменяет частоту подстраиваемого генератора В которое изменяет частоту подстраиваемого генератора с требуемой скорос,тью. toKH второго источника 21 тока |и второго элемента 22 отвода тока протекают через конденсатор С лнтег1ратора 8 и через резистор Р2неболь,шого номинального значения, и no,шиги мимимольниго значения, и постоянная времени СЙ2 обеспечивает ус тойчйвость кольца системы ФАПЧ в дан ном режиме работы. Как только при продолжении описан ного процесса частоты сигналов на вх дах детектора сравниваются, а фаза сигнала на входе 1 станет отставать от фазы сигнала на входе 2, ЧФД переходит в режим фазового детектирова 236 ния(фиг, , зона J). Тогда импульс с выхода четвертого элемента И-НЕ 15 устанавливает второйЯЭтриггер 20 в состояние логической 1 и разблокировывает шестой элемент И-НЕ 17, при этом на его выходе и на выходе третьего инвертора 11 устанавливается логический О. Первый 6 и второй 21 источники тока выключаются, а импульсы, соответствующие фазовой разности входных сигналов, с выхода четвертого элемента И-НЕ 1 $ через седьмой элемент И-НЕ 18 на время своей длительности вклочают первый элемент 7 отвода тока, который отводит ток от интегратора 8 через его первый вход. Выходное напряжение интегратора 8 тогда корректирует фазу сигнала подстраиваемого генератора в сторону уменьшения фазовой расстройки. Если фаза сигнала на входе 1 опережает фазу сигнала на входе 2 Сфиг., зона 1), тогда импульсы фазовой коррекции действуют на выходе шестого элемента И-НЕ 17 и на время своей длительности вклочают первый источник 6 тока, выходной ток которого протекает через первый вход на интегратор 8, выходное напряжение которого корректирует фазу сигнала подстраиваемого генератора в сторону уменьшения фазовой расстройки. В режиме фазового детектирования токи текут в конденсаторе С интегратора 8 через резисторы R1-bR2, а большая постоянная времени C(R1+R2) обеспечивает устойчивость кольца системы ФАПЧ и эффективное подавление побочных составляющих в спектре выходного сигнала подстраиваемого генератора. Если сигнал на входе 1 ЧФЛ имеет частоту меньше частоты сигнала на пходе 2 f j {фиг. А, , f 0, тогда фазовая разность между ними после прохождения нескольких периодов станет в абсолютном значении больше и на выходе пятого элемента И-НЕ 15 появятся импульсы отрицательного направления, которые переводят первый RS-триггер 19 в состо„.. „Q... тогда на выходах седьмого злемента И-НЕ 18 и четвертого инвер ора и появится сигнал логической 1, который вклочает первый 7 и второй 22 элементы отвода тока, которые отводят ток от интегратора В через его первый и второй входы. Выходное напряжение интегратора управляет частотой подстраиваемого генератора в сторону компенсации частотного рассогласования между входными сигналами детектора. Как только при продолжении описанного процесса частоты сигналов на вхЪдах детектора сравниваются, а фаза сигнала на входе 1 станет опереиать фазу сигнала на входе 2, ЧФД переходит в режим фазового детектирования (фиг/, зона 37 Ч 0; II) и импульс нулевого уровня с выхода третьего элемента И-НЕ 14 устанавливает первый R5-триггер 19 в состояние логической 1 и разбло,кировывает седьмой элемент И-НЕ 18. На его выходе и на выходе четвертого ин вертора 12 устанавливается логичесйий О. Первый 7 и второй 22 элементы отвода тока выключаются, а импульсы, соответствующие фазовой разности входных сигналов, с выхода тре тьего элемента И-НЕ It через шестой элемент И-НЕ 17 на время своей длительности вк/ж)чают первый источник 6 тока, выходной ток которого протекает через первый вход на интегратор 8 выходное напряжение которого корректирует фазу сигнала подстраиваемого генератора в сторону уменьшен.т фазо вой расстройки. При превышении фазовой разности между входными сигналами |±Л1 ЧФД ;переходит в режим частотного детектирования (фиг. А зона Ч Л ) остается в таком режиме до полного сравнения фаз входных сигналов (фиг. 4, зона О 4 М Л и снова переходит в режим фазового детектирования, когда фазоваярасстройка меняет знак (фиг. зоне. - 31 П). Третий П и четвертый 12 инверторы служат как буферные устройства и элементы задерх ки, компенсирующие задерхску распространения сигнала в элементах И-НЕ 17 и 18.и обеспечивают функционирование ЧФД на высоких частотах входных сигналов. На фиг. 2 и 3 сплошными линиями обозначены дискриминационные характеристики ЧФД в виде зависимости среднего тока, протекающего через конденсатор С интегратора 8, от фазовой разности ме)хду входными сигналами детектора (фиг. 2) и от соотношения частот входных сигналов детектора (фиг. 3 Л Для сравнения приводятся характеристики известного устройства, показанные штрих-пунктирными линиями. Положительный эффект достигается aa счет того, что дополнительно вве денные элементы со своими связями обеспечивают протекание большего то,ка в интеграторе ЧФД в режиме частотного детектирования, который переходит в режим фазового детектирования только при полном равенстве частот входных сигналов, что приводит к увеличению скорости нарастания выходного напряжения ЧФД и следовательно, к увеличению быстродействия предлагаемого ЧФД без ухудшения фильтрующих свойств в режиме фазового детектирования. Предлагаемый ЧФД, как показали исследования и испытания, превосходит известный по быстродействию в 10210 раз (в зависимости от требуемой ЕГеличины перестройки частоты), что позволяет существенно улучшить характеристики систем ФАПЧ, в которых он используется. ,

1макс

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый детектор | 1981 |

|

SU995302A1 |

| Цифровой синтезатор частот | 1985 |

|

SU1252940A1 |

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

| Частотно-фазовый детектор | 1985 |

|

SU1287251A1 |

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 1991 |

|

RU2012992C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2023 |

|

RU2812098C1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР С МИНИМАЛЬНОЙ ДЛИТЕЛЬНОСТЬЮ УПРАВЛЯЮЩИХ ИМПУЛЬСОВ | 2023 |

|

RU2814213C1 |

| Цифровой синтезатор частот | 1987 |

|

SU1510080A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Устройство для приема частотно-манипулированных сигналов | 1978 |

|

SU768000A1 |

ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР, содержащий первый и второйВ-триггеры, С-входы которых являются входами устройства, D -входы подключены к шине логической единицы, прямые выходы соединены с входами первого элемента И-НЕ, выход которого подключен к R - входам D-триггеров, первые источник тока и элемент отвода тока, выходы которых подключены к первому входу интегратора, выход которого является выходом устройства, о т л и ч а ю щ и и с я .тем, что, с целый увеличения быстродействия, в него введены первый, второй, третий и четвертый- инверторы, второй, третий; четвертый, пятый, шестой и седьмой элементы И-НЕ первый и второй Р5-т0иггеры, вторые источник тока и элемент отвода тока, причем вход первого И1 .вертора подключен К ;первому входу, устройства, а выход подключен к первому входу второго элемента И-НЕ, второй вход котороrq соединен с первым входом третьего элемента И-НЕ и прямым выходом nepBoroD-триггера, а третий вход соединен с вторым входом третьего элемента И-НЕ и инверсным выходом второго D-триггера, вход второго инвертора подключен к второму входу устройства, а выход - к первому входу пятого элемента И-НЕ, второй вход которого соединен с первым входом четвертого элемента И-НЕ и прямьм выходом второго)-триггера,а третий вход соединен с вторым входом четвертого элемента И-НЕ и инверсным выходом первогоВ-триггера, при этом .5-вход первого RS-триггера соединен. с выходом третьего элемента и первым входом шестого элемента И-НЕ, R -вход - с выходом пятого элемента И-НЕ, а выход подключен к входу четвертого инвертора и второму входу седьмого элемента И-НЕ, выход которого соединен с входом первого элемента отвода тока, 5-вход второго КЗ-триггера соединен с выходом четвертого элемента И-НЕ и первым вхо.дом седьмого элемента И-НЕ,R-вход с выходом второго элемента И-НЕ, а выход подключен к входу третьего инвертора и второму входу шестого элемента И-НЕ, выход которого со- . единен с входом первого источника тока, а входа вторых источника тока и элемента отвода тока подключен соответственно к выходам третьего и четвертого инверторов а выходы подключекм к второму входу интегратора,

т

Хнакс.

Фиг.2

0,53

/с/х

4-;

X

V

л//

У

0,5 -1

Хмакс.

Фиг.З

Г

Ч «30

«

:i

V

J

N

§V

V/

1

i

Ci

л л; V

чГ о

л.

.

s

о

л s

A

S

1

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США К 4027262, кя | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1983-04-23—Публикация

1981-12-23—Подача