I

Изобретение относится к электронной технике и предназначено для цепей с частотнофазовой синхронизацией.

Известен частотно-фазовый детектор, содержащий подключенный к источнику входного сигнала первый J-К-триггер и соединенные последовательно с ним первь1е элемент И-НЕ и генератор тока, подключенный к источнику опорного сигнала, второй J-К-триггер и соединенные последовательно с ним вторые элемент И-НЕ и генератор тока, запоминающий конденсатор, подключенный к выходам обоих генераторов тока и третий элемент И-НЕ, входы которого подключены к прямым выходам первого и второго 3 -К--три,ггеров соответственно, а выход соединен с вторыми входами первого и вторрго элементов И-НЕ и с R-входами обоих 3-К триггеров 1.

Однако точность и быстродействие в таком детекторе невелики.

Цель изобретения - повышение точности и быстродействия устройства.

Для этого в частотно-фазо1вый детектор, содержащий подключенный к источнику входного сигнала первый J-К-триггер и соединенные последовательно с ним первые элемент И-НЕ и генератор тока, подключенный к источнику опорного сигнала Второй J-К-триггер и соединенные последовательно с ним вторые элемент И-НЕ и генератор тока, запоминающий конденсатор, подключенный к выходам обоих генераторов тока и третий элемент И-НЕ, входы которого подключены к прямым выходам первоJ го и второго -К-триггеров соответственно, а выход соединен с вторьши входами перво-, го и второго элементов И-НЕ и с R-BXOдами обоих 3-К-триггеров, введены четвертый элемент И-НЕ, третий и четвертый генераторы тока и два D-триггера, С-входы которых через элементы НЕ подключены к источнику входного и опорного сигналов со- ответственно, D-входы подключены соответственно к выходам первого и второго 3-К-триггеров, входы третьего генератора тока и один из входов четвертого элемента И-НЕ подключены к прямому выходу первого D-триггера, вход четвертого генератора тока и второй вход четвертого элемента И-НЕ подключены к прямому выходу второго D-триггера, выход четвертого элемента И-НЕ соединен с R-входами D-триггеров, а выходы третьего и четвертого генераторов

тока подключены к запоминающему конденсатору, инверсный выход первого D-триггера подключен к его S-входу и к третьему входу второго элемента И-НЕ, инверсный выход второго D - триггера подключен к его S входу и к третьему входу первого элемента И-НЕ, вход J первого J-К триггера соединен с входом К второго J-Ктриггера, вход J второго J-К - триггера соединен-с входом К первого J-К - триггера, а инверсные выходы и другие J - входы этих триггеров соединены перекрестными связями.

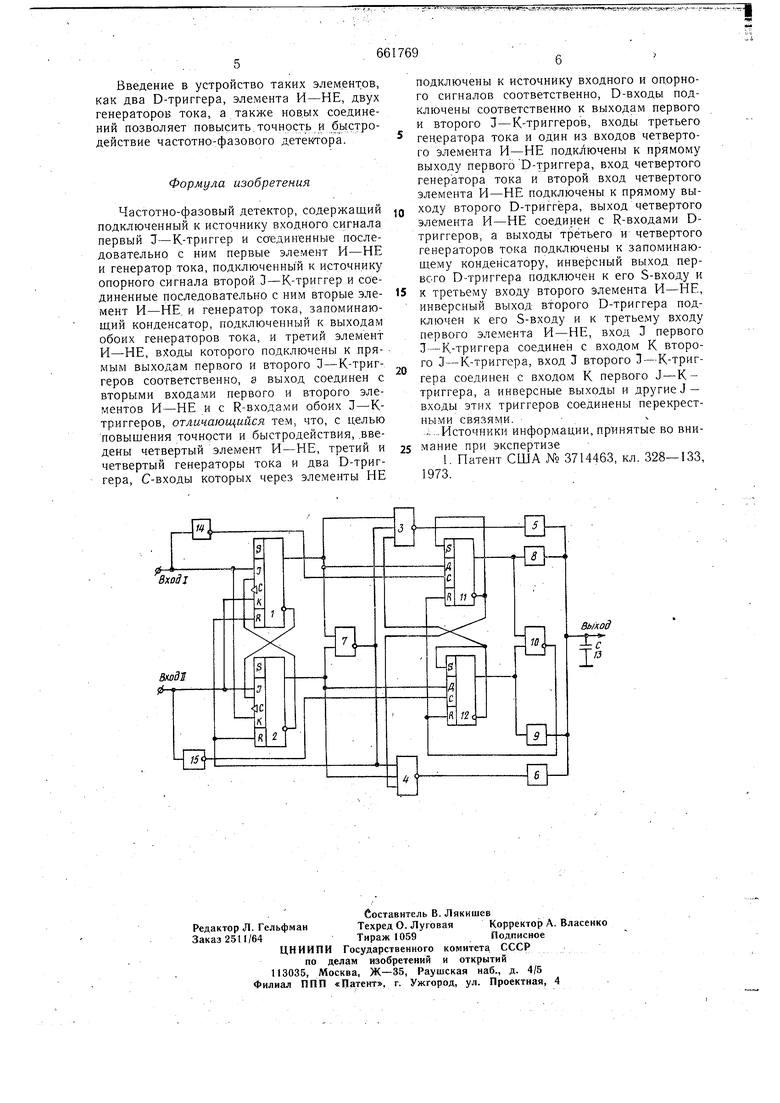

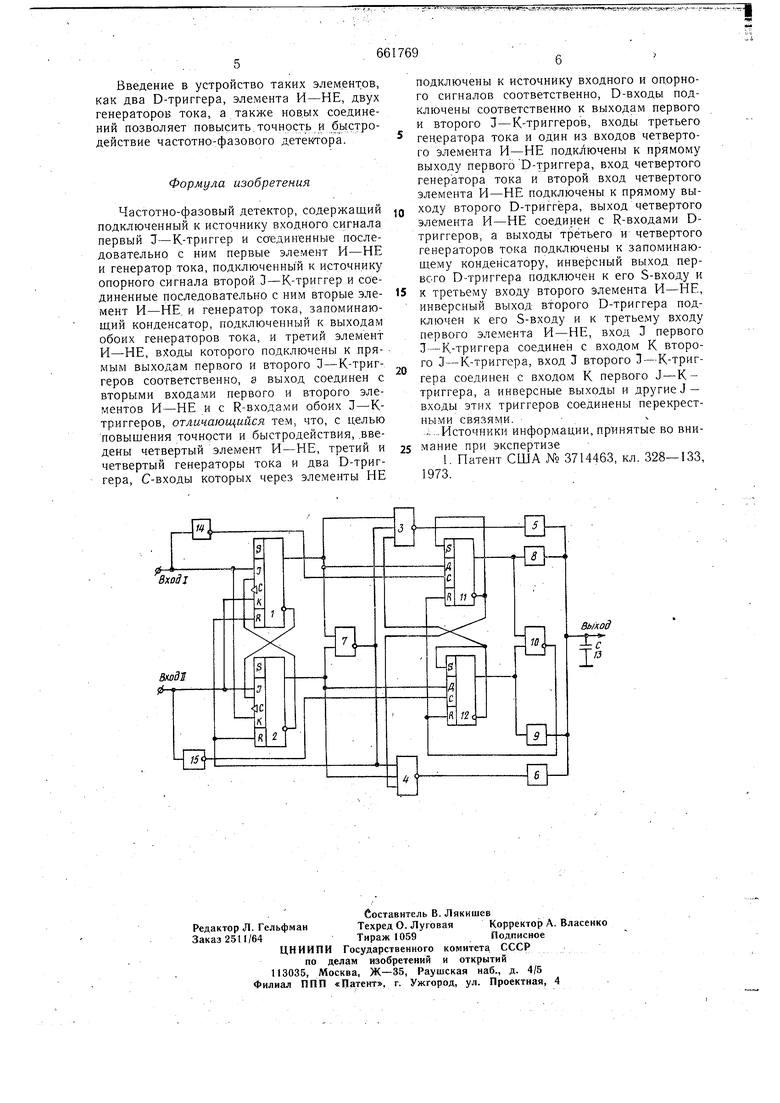

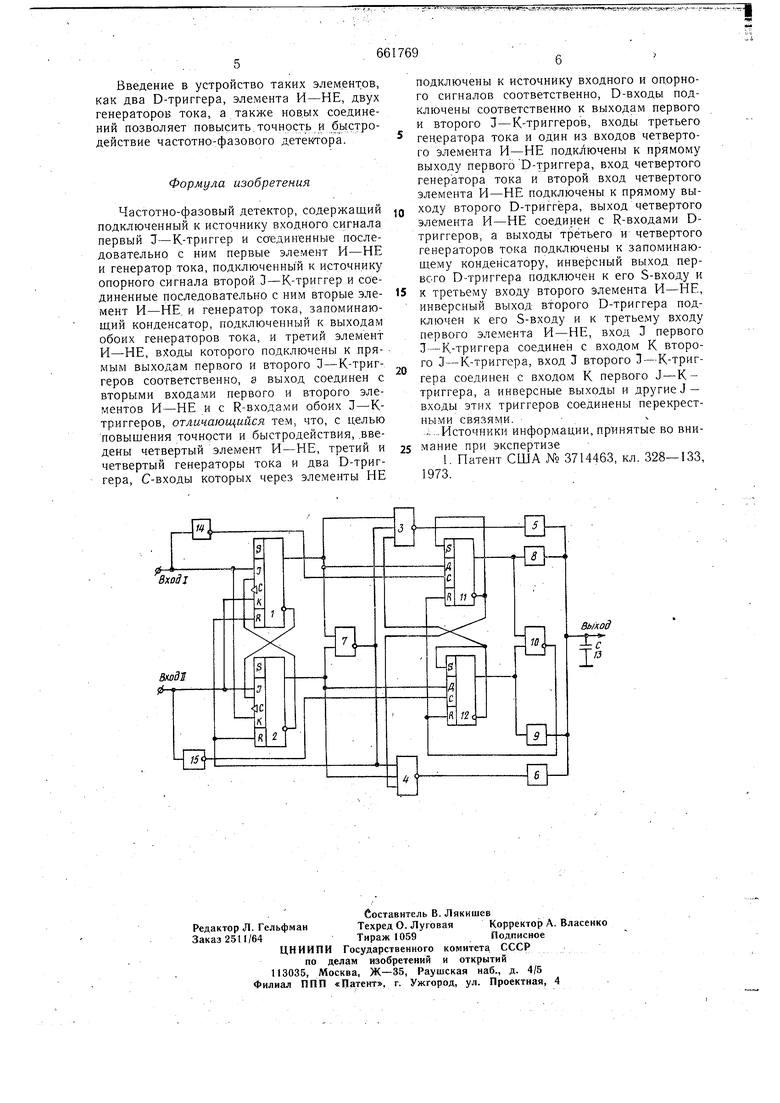

На чертеже .преДставлема структурная электрическая схема частотно-фазового детектора.

Частотно-фазовый детектор содержит первый и второй 3-К-триггеры 1, 2, первый и второй элементы И-НЕ 3, 4, первый и второй генераторы 5, 6 тока, третий элемёйт И-НЕ 7, третий и четвертый генераторы 8, 9 тока, четвертый элемент 10, первыи и второй, D-триггеры 11, 12, запоминающий конденсатор 13 и элементы НЕ 14, 15.

Устройство работает следующим образом.

Если сигналы, действующие по входам устройства, имеют разную частоту (режим рассогласования частот), то в этом случае по входу, частота н.а котором выше, пойдет

два импульса подряд. Первый из этих импульсов установит соответствующий J-Ктриггер, например 1, в состояние логической «1 и тем самым подготовит включение первого D-триггера 11 (т. к. по входу устанавливается состояние логической «1). Второй импульс переписывает состояние D-входа на выход D-триггера 11, при этом благодаря наличию соединения S входа с инверсным выходом D-триггер 11 самоблокируется в этом состоянии.

Инверсный выход D-триггера 11 (логический 0) обеспечивает блокировку элемента И-НЕ 4, а прямой выход (логическая «1) включает третий генератор 8 тока и еледовательно обеспечивает непрерывное и однонаправленное изменение напряжения на запомина.ющем конденсаторе 13. Это напряжение при работе устройства в замкнутом кольце системы фазовой автоподстрочки частоты (ФАПЧ) должно управлять частотой подстраиваемого генератора в сторону ктэмпенсйции частотного рассогласования по входам частотно-фазового детектора. Процесс компенсации будет продолжаться до момента появления двух импульсов подряд по другому входу частотно-фазового детектора (частотная перекомпенсация); так как при этом произойдет установление в состояние логической «1 D-триггера 12, то на входах элемента И-НЕ 10 будут две логические «I, он срабатывает и возвращает оба Dтриггера 11, 12 в исходное состояние. При этом генератор 8 тока выключается, элемент И-НЕ 4 разблокируется, и через вьгходные

схемы начинают выделяться импульсы, длительность которых соответствует фазовому сдвигу входных сигналов. При частотном рассогласовании другого знака устройство работает аналогично.

Если сигналы на входах устройства имеют одинаковые частоты, но между ними имеется определенней фазовый сдвиг (меняющийся по знаку и величине), то устройство производит определение знака и величины этого фазового рассогласования и в соответствии с этим меняет напряжение на запоминающем конденсаторе 13.

Пусть триггеры 1, 2 и 11, 12 находятся в соответствии логического «О. При этом входы J-К-триггеров 1, 2 разблокированы, и при поступлении отрицательного фронта одного из входных сигналов соответствующий триггер переходит в состояние «1. Так как при этом на второй вход другого триггера поступает «О, то при воздействии входного сигнала по второму входу происходит только сброс первого триггера (по входу К) в начальное состояние (логический «О), а второй триггер своего состояния не меняет. Тем самым на выходе первого триггера происходит выделение сигнала, длительность которого соответствует фазовому сдвигу входных сигналов, а по другому выходу детектора сигнала вообще не образуется. В зависимости от знака фазового рассогласования работает Л-К-триггер I или 2. Сигналы с инверсных выходов триггеров через разблокированные в этом режиме элементы 3 или 4 управляют генератора.ми тока 5, 6. Элемент И-НЕ 7 в цепи обратной связи работает и обеспечивает устойчивость только в случае одновременного поступления импульсов по выходам частотно-фазового детектора. D-TpHrfepbi 11, 12 в этом режиме работь своего состояния, не меняют. Это обусловлено тем, что установка J-К-триггера в состояние «1 по входу 3 происходит отрицательным фронтом входного импульса, а Перезапись состояния D-входа на выход D-триггера по входу С производится благодаря наличию элементов НЕ 14, 15 от отрицате тьного фронта входного сигнала и ввиду наличия задержки J-К-триггеров, в D-триггере производится перезапись предыдущего состояния J-К-триггера (то есть «О), и они все время остаются в состоянии «О. Третий и четвертый генераторы тока 8, 9, подключенные к прямым выходам D-триггеров 11, 12 при этом выключены, а элементы И-НЕ 3, 4, подключенные к инверсным выходам D-,TpHrrepoB II, 12, разблокиррвань. Таким образом, в режиме выделения фазового сдвига работает только один из J-К-триггеров 1 или 2 в. зависимости от знака фазового рассогласования.

Следует отметить, что по выходам D-триггеров 11 или 12 устройство может бытьисподьзрва но как компаратор частоты. Введение в устройство таких элементов, как два D-триггера, элемента И-НЕ, двух генераторов тока, а также новь1х соединений позволяет повысить точность и быстродействие частотно-фазового детектора. Формула изобретения Частотно-фазовый детектор, содержащий подключенный к источнику входного сигнала первый 3-К-триггер и соединенные последовательно с ним первые элемент И-НЕ и генератор тока, подключенный к источнику опорного сигнала второй 3-К-триггер и соединенные последовательно с ним вторые элемент И-НЕ. и генератор тока, запоминающий конденсатор, подключенный к выходам обоих генераторов тока, и третий элемент И-НЕ, входы которого подключены к прямым выходам первого и второго 3-К-триггеров соответственно, а выход соединен с вторыми входами первого и второго элементов И-НЕ и с R-входами обоих Л-Ктриггеров, отличающийся тем, что, с целью повыщения точности и быстродействия, .введены четвертый элемент И-НЕ, третий и четвертый генераторы тока и два D-триггера, С-входы которых через элементы НЕ

- подключены к источнику входного и оп.орного сигналов соответственно, D-входы подключены соответственно к выходам первого и второго 3--К-триггеров, входы третьего генератора тока и один из входов четвертого элемента И-НЕ подключены к прямому выходу первого D-триггера, вход четвертого генератора тока и второй вход четвертого элемента И-НЕ подключены к прямому выходу второго D-триггёра, выход четвертого элемента И-НЕ соединен с R-входами Dтриггеров, а выходы третьего и четвертого генераторов тока подключены к запоминающему конденсатору, инверсный выход первого D-триггера подключен к его S-входу и к третьему входу второго элемента И-НЕ, инверсный выход второго D-триггера подключен к его S-входу и к третьему входу первого элемента И-НЕ, вход 3 первого 3 --К-триггера соединен с входом К второго J-К-триггера, вход 3 второго 3-К-триггера соединен с входом К первого J-Ктриггера, а инверсные выходы и другие J - входы этих триггеров соединены перекрестными связями.- . -....Источники информации, принятые во внимание при экспертизе 1. Патент США № 3714463, кл. 328-133, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый детектор | 1981 |

|

SU1014123A1 |

| Импульсный частотно-фазовый детектор | 1982 |

|

SU1059662A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1328924A2 |

| Частотно-фазовый детектор | 1990 |

|

SU1775844A1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

| Частотно-фазовый детектор | 1986 |

|

SU1406717A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| Измерительное устройство к балансировочному станку | 1985 |

|

SU1259118A1 |

| Умножитель частоты следования импульсов | 1983 |

|

SU1119165A1 |

Авторы

Даты

1979-05-05—Публикация

1977-02-21—Подача