(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ХАРАКТЕРИСТИК ЛИНЕЙНЫХ УСИЛИТЕЛЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговая вычислительная система | 1987 |

|

SU1483468A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ НАГРЕВАТЕЛЯМИ АППАРАТУРЫ КОСМИЧЕСКОГО АППАРАТА | 2014 |

|

RU2571728C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЖИДКИХ СРЕД | 1992 |

|

RU2045055C1 |

| Ультразвуковой томограф | 1984 |

|

SU1261629A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭФФЕКТИВНОСТИ ЭНЕРГОИСПОЛЬЗОВАНИЯ В ПОТРЕБИТЕЛЬСКИХ ЭНЕРГЕТИЧЕСКИХ СИСТЕМАХ | 2011 |

|

RU2458445C1 |

| АНАЛИЗАТОР ДЛЯ КОНТРОЛЯ ХАРАКТЕРИСТИК ДИНАМИЧЕСКИХ СИСТЕМ | 1971 |

|

SU300875A1 |

| Устройство для ввода информации | 1983 |

|

SU1124274A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ВЗАИМНОЙ КОРРЕЛЯЦИИ МЕЖДУ ДВУМЯ СЛУЧАЙНЫМИ СИГНАЛАМИ В УСЛОВИЯХ ПОМЕХИ ЭФИРА | 2022 |

|

RU2797196C1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2399156C1 |

| Устройство для измерения температуры | 1988 |

|

SU1672237A1 |

Изобретение относится к технике измерений и может быть использовано для контроля коэффициента усиления, границ .линейного динамического усиления и т.д.линейных, усилителей в .процессе сборки, например усилителей датчиков систем автоматического управления.

. Известно устройство для измерения линейности амплитудных характеристик четырехполюсников , в toM числе в линейньГх усилителях, содержащее коммутатор, блок управления, преобразователь аналог-код, схему вычцтания, индикатор, причем выход коммутатора подключен к первому входу ключевого расширителя импульсов, соединенного с селективным вольтметром, а выход блока управления, состоящего из формирователя стробирующих импульсов,схемы переключения и схемы задержки, подсоединен к одному из входов коммутатора, при этом выход схемы задержки соединен с вторым входом ключевого расширителя импульсоь Cll.

Недостатком этого устройства является невозможность проведения допускового контроля в -динамическом диапазоне характеристики,а также

определения границ диапазона линейности коэффициента усиления.

Наиболее близким техническим решением к изобретению является устройство, содержащее генератор линей- . но-изменяющегося напряжения, который соединен с генератором синусоидального напряжения, коммутатор, блок сравнения, составленный из резисто10ров , операционный усилителей с параллельной отрицательной обратной связью, амплитудных детекторов, в измерительное плечо которого включен объект контроля, дифференциальный

15 нуль-орган, имеющий временный и амплитудный каналы, причем в образцовое -плечо цепи сравнения включен импульсный усилитель, подключенный к входу блока квантования по времени,

20 выход которого подключен к управляющему входу временного канала дифференциального нуль-органа, и входу сдвигателя, соединен с регулируемыми дискретными делителями, под25ключенными к cyMi.iaTOpy и блоку индикации 23 .

Недостатком известного устройства является ограничение функциональных возможностей из-за сложности

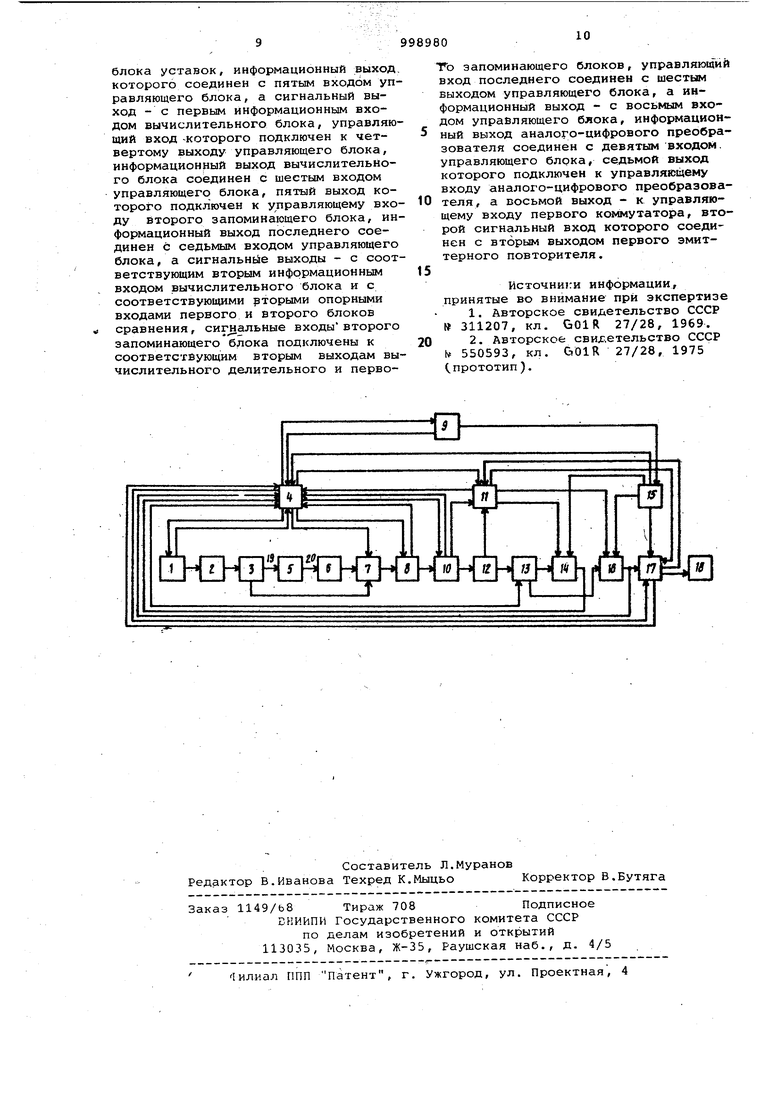

30 контроля границ диапазона линейноети коэффициента усиления по амплитуд и абсолютных измерений характеристи линейных усилителей. Целью изобретения является расшкрение функциональных возможностей за счет контроля границ динамического диапазона абсолютных измерений коэффициента, усиления. Цель достигается тем, что в устройство для контроля характеристик линейных усилителей, содержащее генератор линейно изменяющегося напряжения , первый выход которого соединён с управляющим входом генератора гармонического сигнала, кo Iмyтaтop, входные клеммы устройртва, блок срав нения и блок регистрации, введены второй коммутатор, второй блок сравнения, пульт управления, управляющий блок, аналого-цифровой преобразователь, два эмиттерных повторите ля, два запоминающих блока, делитель ный блок, блок уставок и вычислитель ный блок, при этом соответствующие выходы пульта правления соединены с управляющим входом блока уставок и с первым входом управляющего блока,а вход - с первым выходом управляющего блока, второй выход которого соединен с управляющим входом генератора линейно изменяющегося напряжения второй выход которого соединен с вторым входом управляющего блока, вы ход генератора гармонического сигнала через первый эмиттерный повторитель подключен к первой входной клем ме устройства, вторая входная клемма которого через последовательно соединенные второй эммиттерный повторитель, первый коммутатор, аналого цифровой преобразователь, первый запоминающий блок, делительный блок и второй коммутатор подключена к сигнальному входу первого блока сравнения, выход которого соединен с третьим входом управляющего блока, а первый опорный вход первого блока сравнения соединен, с одним из выхс1дов блока уставок, второй сигнальный выход второго коммутатора через последовательно соединенные второй блок сравнения и вычислительный блок подключен к входу блока регистрации , управляющий вход второго коммутатора соединен с третьим выходом управляющего блока, четвертый вход которого подключен к выходу йторого блока сравнения, первый опор ный вход последнего соединен с вторым выходом блока уставок, информационный выход которого соединен с пятым входом управляющего блока, а сигнальный выход - с первым информационным входом вычислительного блока, управляющий вход которого подключен к четвертому выходу управляющего блока, информационный выход вычислительного блока соединен с шестым входом управляющего блока, пятый выход которого подключен к управляющему входу второго запоминающего блока, информационный вход последнего соединен с седьмым входом управляющего блока, а сигнальные выходы - с соответствующим вторым информационным входом вычислительного блока и с соответствующими вторыми опорными входами первого и второго блоков сравнения, сигнальные входы второго запоминакицего блока подключены к соответствующим вторым выходам вычислительного, делительного и перэого запоминающего блоков , управляющий вход последнего соединен с шестьлм выходом управляющего блока, а информационный выход - с восьмым входом управлякадего блока, информационный вход аналого-цифрового преобразователя соединен с девятым входом управляющего блока, седьмой выход которого подключен к управляющему входу аналого-цифрового преобразователя, а восьмой выход - к управляющему входу первого коммутатора, второй сигнальный вход которого соединен с вторым выходом первого эмиттерного повторителя. На чертеже представлена структурная схема устройства. Устройство содержит генератЬр 1 линейно изменяющегося напряжения, генератор2 гармонического сигнала первый эмиттерный повторитель 3, управляющий блок 4, контролируемый объект 5, второй эмиттерный повторитель 6, первый коммутатор 7, аналого-цифровой преобразователь 8, пульт управления 9, первый и второй запоминающие блоки 10 и 11, делительный блок 12 второй коммутатор 13, первый блок сравнения 14, блок уставок 15, второй блок сравнения 16, вычислительный блок 17, блок регистрации 18 и входные клеммы 19 и 20. Устройство работает следующим образом. Испыауемый линейный усилитель 5 своими входом и выходом подключает к соответствующим входным клеммам устройства 19 и 20. С пульта управления 9 вводят в блок уставок 15 необходимое значения числовых коэффициентов.иа.и.ид., где ЛК - граничные значения выходного сигнала на линейном участке зависимости коэффициента усиления от входного напряжения, а именно предельно допустимая разность двух последовательных значений коэффициента усиления на начале линейного участка (ее значения зависят от точности измерений коэффициента усиления, скорости нарастания входного напряжения, быстродействия аналого-цифрового преобразователя), ЛК 2 - граничные значения выходного сигнала вне пределов линейного участ ка, а именно:предельно допустимая разность между текущим значением коэффициента усиления и его средним значением; 0 lU-i минимальное и максимальное значение входного напряжения на начальном участке диапазона, которому соответствует номинальный коэффициент, усиления,- U , U соответствующие напряжения на границах линейного участка диапазона, К, Kjt - нижний и верхний пределы допустимых значений коэффициента усиления на линейном участке Д1(1апаэона. С выхода пульта 9 на управлякиций блок 4 выделяется команда на проведение измерений. Управляющий блок 4 подключает через первый коммутатор 7 аналого-цифровой преобразователь 9 к первому эмиттерному повторителю 3 обнуляет ячейки запоминающих блоков 10 и 11, подключает через второй коммутатор 13 делительный блок 12 к первому блоку сравнения 14, после че го запускает генератор 1 линейно из меняющего напряжения. На выходе генератора 2 гармонических сигналов формируется синусоидальный сигнал с плавно нарастающей амплитудой, кото рый измеряется аналого-цифровым, преобразователен 8. После завершения замера и .аналого-цифровой преобразователь .выдает на управляющий блок 4 команду по которой управляющий блок 4 разрешает .записать измеренного значения U в первый запоминающий блок 10 и переключает первый коммутатор 7 для измерения U. После окончания замера U аналогоцифровой преобразователь о выдает команду на управляющий блок 4, по которой управляющий блок 4 разрешает повторную запись измеренного зна чения в первом запоминающем бло ке 10, запись значений во втором запоминающем блоке 11 и вычисление значения коэффициента усиления в начальной точке в де лительном блоке 12. После чего значение Kt поступает в память второго запоминающего блока 11 и на вход первого блока сравнения 14, где про исходит сравнение нулевым уров нем. После сравнения запоминается в ячейке второго запоминающего блока 11, соответствующей информаци от первого блока сравнения 14. Зате пульт выдает команду на проведение измерений второго значения коэффи ., ииен.та усиления. . со6тветствуюш« соответствуюше входному значению Ug . При этом уп равляющий блок 4 подключает вход аналого-цифрового преобразователя 8 к выходу первого эмиттерного повторителя 3. После замера U аналого-цифровой преобразовате,ль 8 выдает управляющему блоку 4 сигнал, получив который управляющий блок 4 пересылает измеренное значение Ugx первый запоминающий блок 10 и переключает первый коммутатор 7 для измерения . После окончания замера аналого-цифровой преобразователь 8 выдает сигнал управляющему блоку 4, получив который управляющий блок 4 пересылает измеренное значение первый запоминающий блок 10, из которого значения и и, пересылаются во второй запоминающий блок 11 в место и . и в делительный блок 12, который вычисляет к . Полученное значение К пересылается во второй запоминающий блок 11 вместо и на первый блок сравнения 14, где происходит сравнение с пересланным из второго запоминающего блока 11 значением . Если j АК, , что соответствует -начальному участку значений коэффициента усиления, цикл вычислений будет повторяться. При этом во втором запоминающем блоке 11 запоминаются последние значения Ugy и . При выполнении неравенства -К /$йК , что соответствует линейному участку коэффициента ус1 ления, происходит запоминание соответствующих значений иу; JVbV UebtvWM, а также выдается команда второму коммутатору 13 на подключение второго блока сравнения 15 и сигнал на управляк-ИлИй блок 4 о завер1лении начально.го этапа измерений (значение переносится в ячейку второго запоминающего блока 11, связанную с вторым блоком сравнения).После получения сигнала управляющий блок подключает аналого-цифровой преобразователь 8 для измерения ..После получения от аналого-цифрового . преобразователя 8 сигнала- об окон-, чании измерения значение U пересылается в первый запомниа|С1иий блок 10, а на первый коммутатор 7 выдается команда подключить аналогоцифровой преобразователь 8 для измерения . и После окончания замера i-ftbx аналого-цифровой пре.образсватель 8 выдает сигнал управляющему блоку 4 получив который управлшощий блок 4 .пересылает измеренное значение в первый запоминающий блок 10, из которого значение и пересьшаю.тся во СЫ f О лл | второй запоминающий блок 11 на место и. и и в делительный блок 12, который вычисляет . Звачение пересылается во второй запоминающий блок 11 и во второй блок сравнения ,16, где происходит сравнение с . При условии/K -Kt /7A 1((( (. Kj что соответствует участку линейности коэффициента усиления, управляющий блок .4 пересылает значения и в вычислительный блок 17 для опред: еле - среднего значения и ния К, а полученное среднее значе|ние К Р пересылает в ячейку второго запоминающего блока 11, связанную с вторым блоком сравнения 16. Затем управляющий блок 4 выдает команду на измерение , которое измеряется аналогично . После чего пр исходит сравнение, к с Кср . При условии, что / .2, управляющий блок 4 пересылает значе-. и к для нахождения ново го среднего значения, которое пересылают в ячейку второго запоминаю щего устройства 11 на место старого значения К с-р .. Вычисление текущего значения К выполняют по следующе формуле КСР -КСРУ,, где К5. старое значение средне го значения коэффициента усиления. соответствующее новое значение, п 1,2,... Аналогично вычисля ются величины, характеризующие неравномерность коэффициента усиления на линейном участке, а именно: сред )( .Т йТйУГ ТпГТ ние значения (ср . Ц-ор Эти значения пересылаются во второй запоминающий блок 11 на место старых значений 1 и i I . ср ср . мерение производится до тех по пока н.е будет заполняться условие (.р|7/дк , соответствующее пре дельно допустимому отклонению коэфф циента усиления от среднего значения, т.е. завалу коэффициента уси ления при больших значениях входног напряжения ( этом случае второй блок сравнения 16 выдает управляющему блоку 4 сигнал об оконча нии измерений коэффициента усиления Получив сигнал, управляющий блок 4 передает в вычислительный блок 17 полученные значения IU.HICP -ySxlIp I/ etrra Bxmim и производится выключение генератор линейного напряжения 1. В вычислительном блоке 17 производится оценка наличия КСР в пределах допуска, Uexwin и пределах допуска, т.е. оценивается выполнение неравенства K,i Кср К,;,, и и Jeчmi 2 После чего про&У fno изводится Bt.ma4a всей полученной информации на регистрирующий блок 18. На пульт управления 9 поступает сигнал об окончании измерений и проводится индикация измерений норма или не норма. Формула изобретения Устройство для контроля характеристик линейных усилителей, содержащее генератор линейно изменяющегося напряжения, первый выход которого соединен с управляющим.входом генератора гармонического сигнала, коммутатор,, входные клеммы устройства, блок сравнения, блок регистрации, отличающееся тем, что, с целью расширения функциональных возможностей за счет контроля границ динамического диапазона и абсолютных измерений коэффициента усиления, в него введены второй коммутатор, второй блок сравнения, пульт управления, управляющий блок, аналого-цифровой преобразователь, два эмиттерных повторителя, два запоминающих блока, делительный блок, блок уставок и вычислительный блок приэтом соответствующие выходы пульта управления соединены с управляющим входом блока уставок и с первым входом управляющего блока, а вход - с первым выходом управляющего блока, второй выход которого соединен с управляющим входом генератора линейно изменяющегося напряжения, второй выход которого соединен с вторым входом управляющего блока, выход генератора гармонического сигнала через первый эмиттерный пов-, торитель подключен к первой входной клемме устройства, вторая входная клемма которого через последовательно соединенные второй эмиттерный повторитель, первый коммутатор, аналого-цифровой преобразователь первый запоминающий блок, делительный блок и второй коммутатор подключена к сигнальному входу первого блока сравнения, выход которого соединен с третьим входом упргвляющего блока, а первый опорный вход первого блока сравнения соединен с одним из выходов блока уставок , второй сигнальный выход второго коммутатора через последовательно соединенные второй блок сравнения и вычислительный блок подключен к входу блока регистрации, управляющий вход второго коммутатора соединен с третьим выходом управляющего блока, четвертый вход которого подключен к выходу второго блока сравнения, первый опорный вход последнего соединен с вторым выходом

блока уставок, информационный выход, которого соединен с пятым входом управляющего блока, а сигнальный выход - с первым информационным входом вычислительного блока, управляющий вход -которого подключен к четвертому выходу управляющего блока, информационный выход вычислительного блока соединен с шестым входом управляющего блока, пятый выход которого подключен к управляющему входу Второго запоминающего блока, информационный выход последнего соединен с седьмым входом управляющего блока, а сигнальнйе выходы - с соответствующим вторым информационным входом вычислительного блока и с соответствующими рторыми опорными входами первого и второго блоков сравнения, сиг нальные входывторого запоминающего блока подключены к соответствующим вторым выходам вычислительного делительного и первоТо запоминающего блоков, управляющий вход последнего соединен с шестым выходом управляющего блока, а информационный выход - с восьмым входом управляющего блока, информационный выход аналого-цифрового преобразователя соединен с девятым входом. управляющего блока, седьмой выход которого подключен к управляющему входу аналого-цифрового преобразова0теля, а восьмой выход - к управляющему входу первого коммутатора, второй сигнальный вход которого соединен с вторым выходом первого эмиттерного повторителя.

5

Источники информации, принятые во внимание при экспертизе

0 1 550593, кл. CV01R 27/28, 1975 (.прототип).

Авторы

Даты

1983-02-23—Публикация

1981-10-27—Подача