Изобретение относится к измерению температуры термоэлектрическими методами.

Целью изобретения является повышение точности измерения.

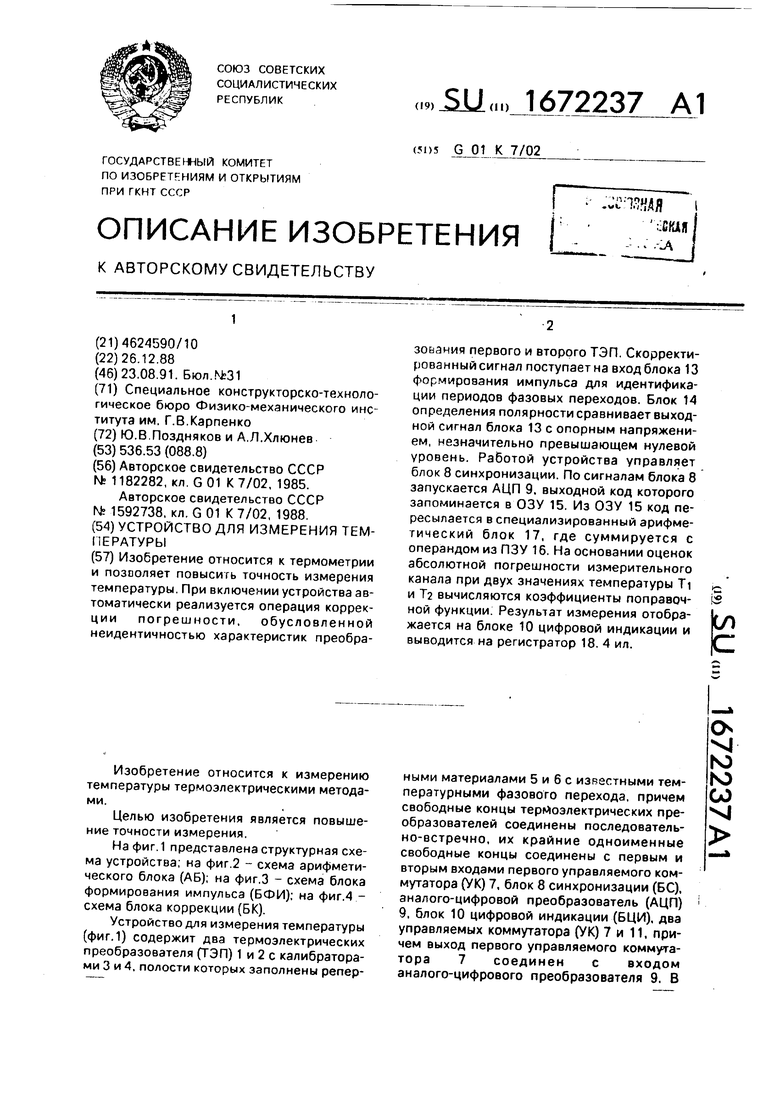

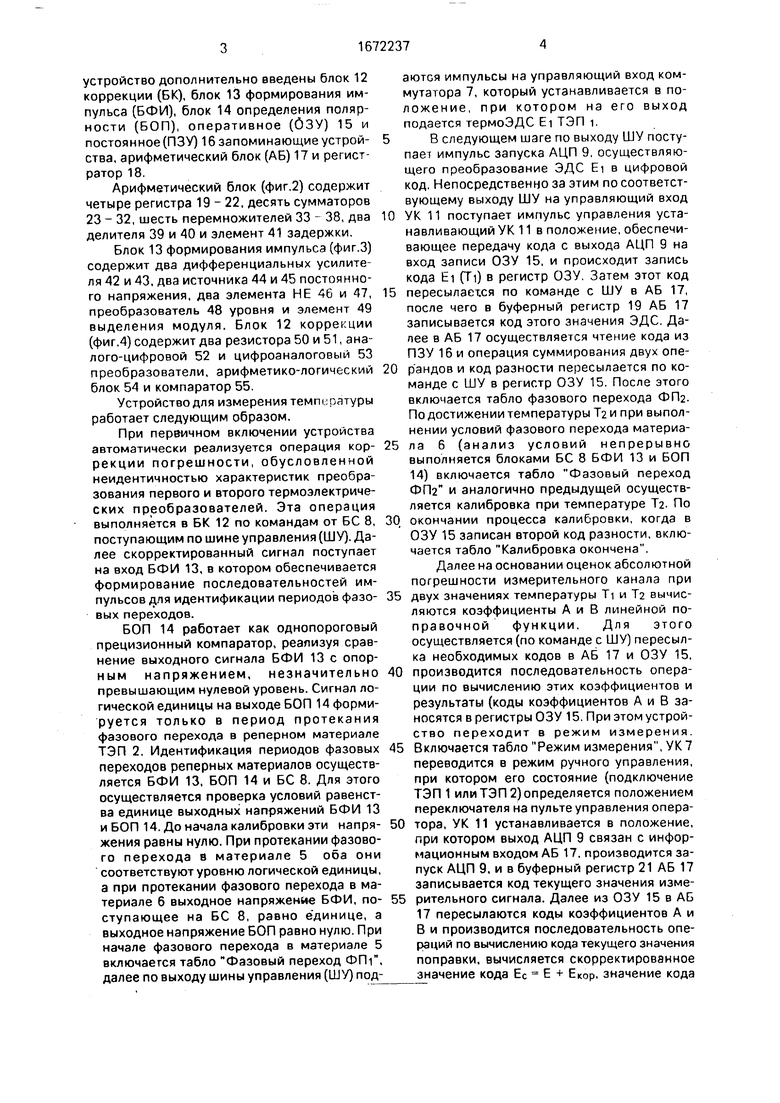

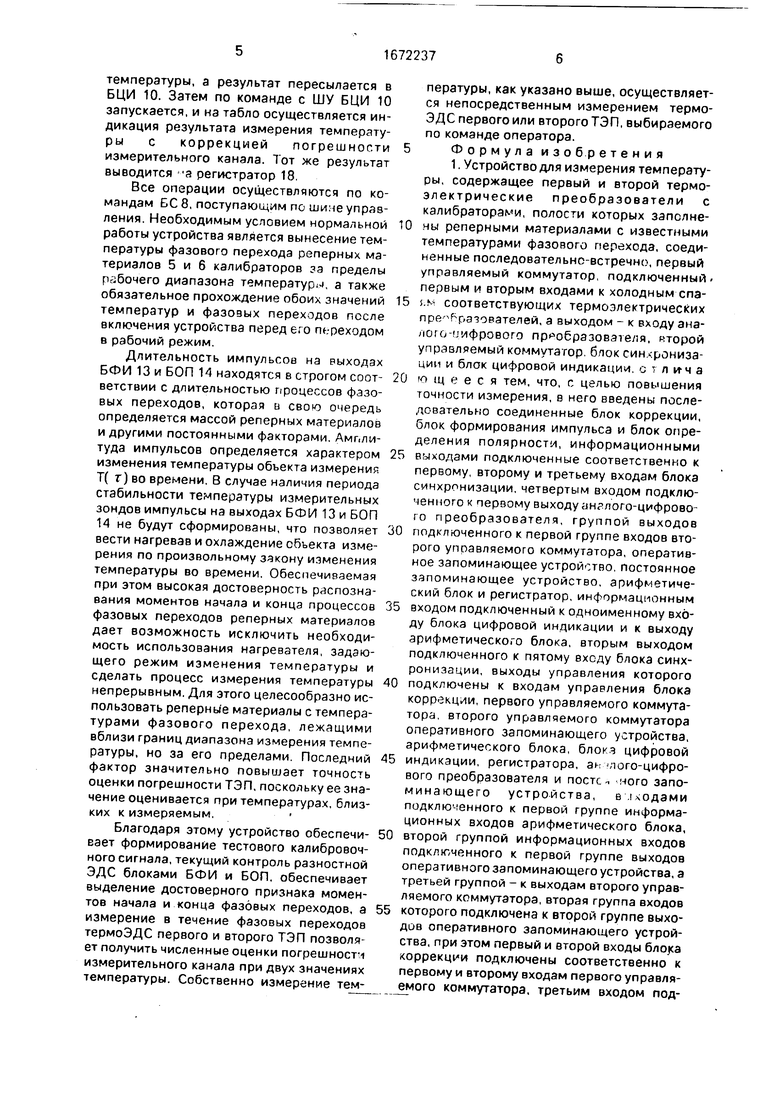

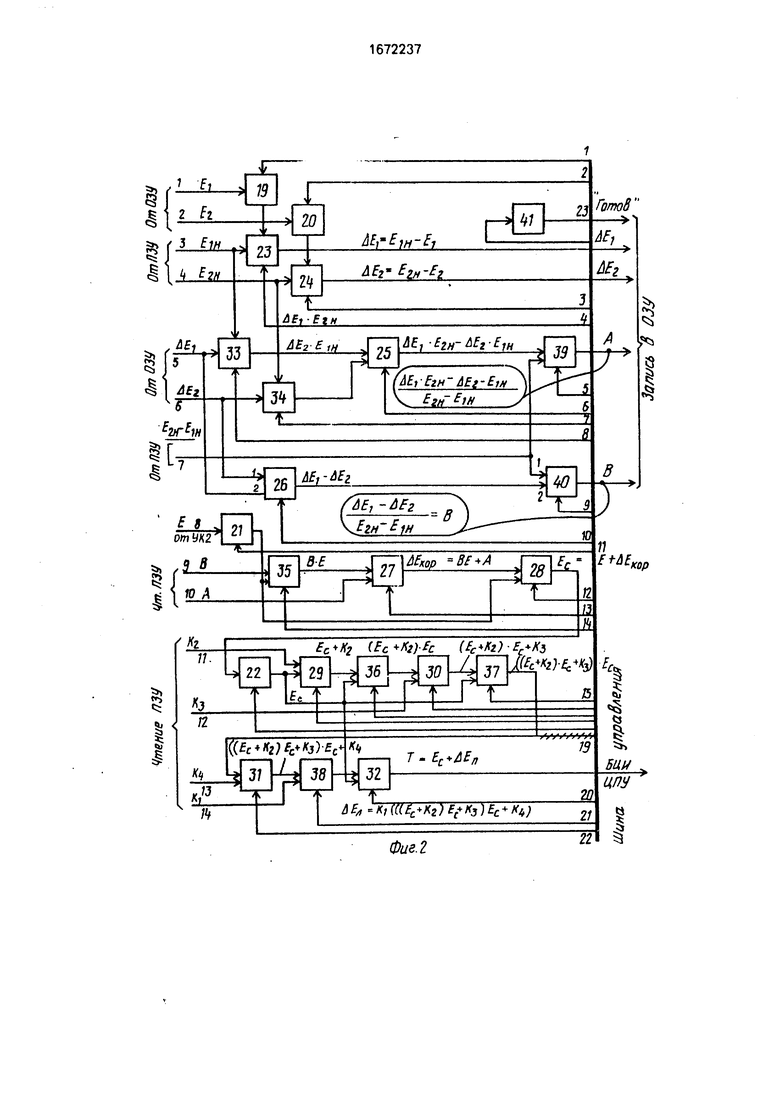

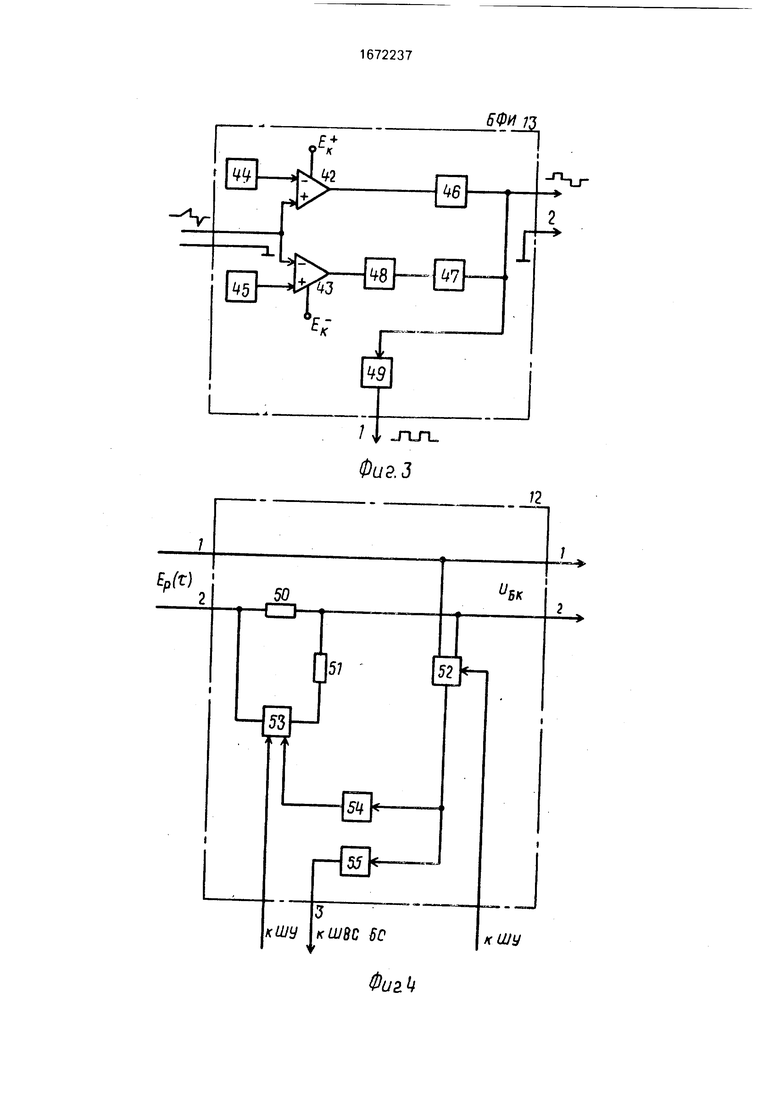

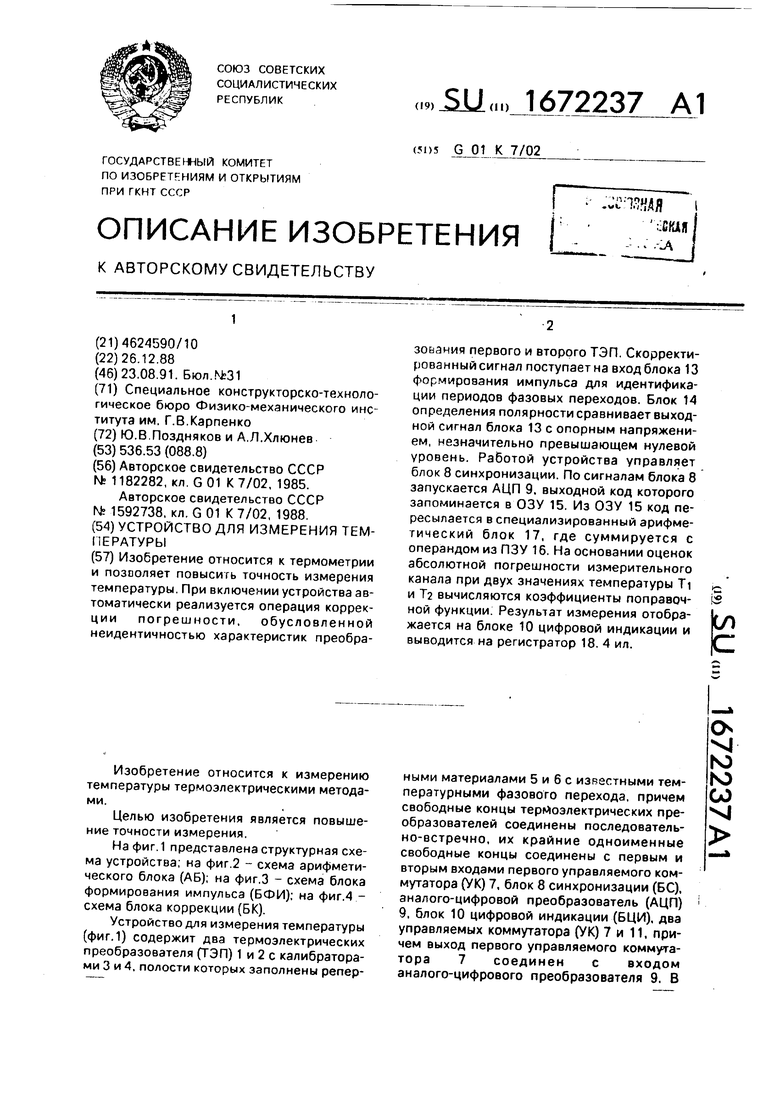

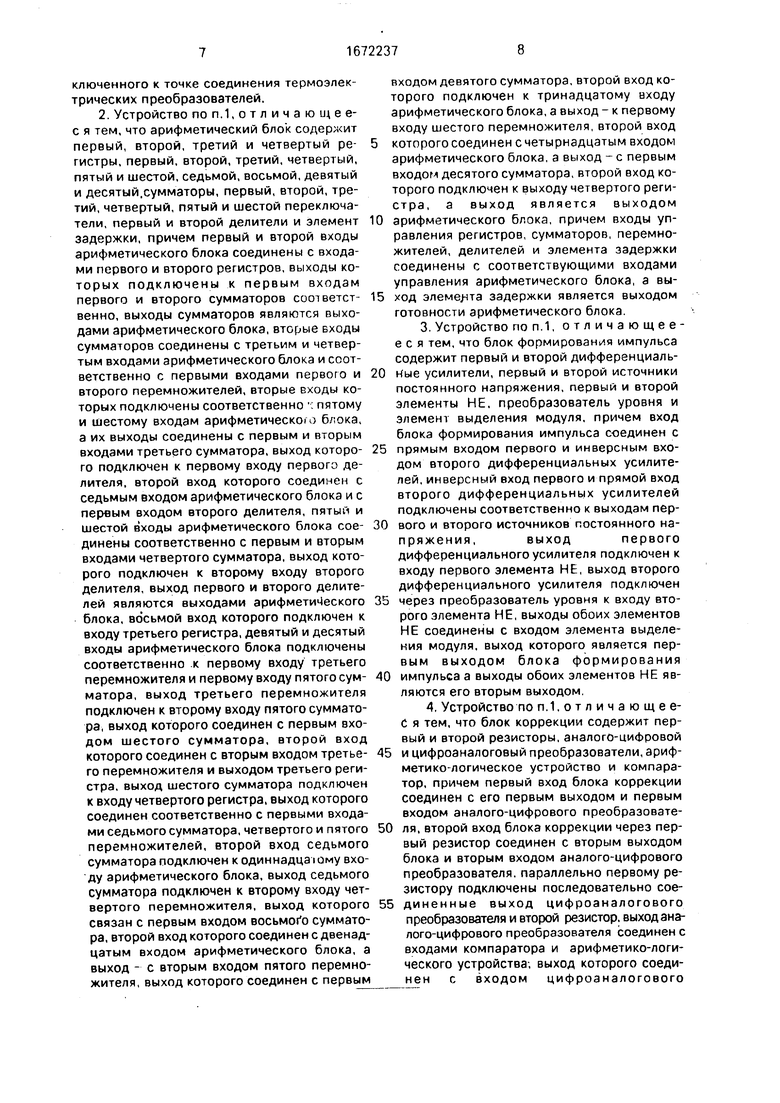

На фиг. 1 представлена структурная схема устройства; на фиг.2 - схема арифметического блока (АБ); на фиг.З - схема блока формирования импульса (БФИ); на фиг.4 - схема блока коррекции (БК).

Устройство для измерения температуры (фиг. 1) содержит два термоэлектрических преобразователя (ТЭП) 1 и 2 с калибраторами 3 и 4, полости которых заполнены реперными материалами 5 и б с известными температурными фазового перехода, причем свободные концы термоэлектрических преобразователей соединены последовательно-встречно, их крайние одноименные свободные концы соединены с первым и вторым входами первого управляемого коммутатора (УК) 7, блок 8 синхронизации (БС), аналого-цифровой преобразователь (АЦП) 9, блок 10 цифровой индикации (БЦИ). два управляемых коммутатора (УК) 7 и 11, причем выход первого управляемого коммутатора 7 соединен с входом аналого-цифрового преобразователя 9. В

О vj Ю Ю СО

VJ

устройство дополнительно введены блок 12 коррекции (БК), блок 13 формирования импульса (БФИ), блок 14 определения полярности (БОП), оперативное (ОЗУ) 15 и постоянное (ПЗУ) 16 запоминающие устройства, арифметический блок (АБ) 17 и регистратор 18.

Арифметический блок (фиг,2) содержит четыре регистра 19 - 22, десять сумматоров 23 - 32, шесть перемножителей 33 - 38, два делителя 39 и 40 и элемент 41 задержки.

Блок 13 формирования импульса (фиг.З) содержит два дифференциальных усилителя 42 и 43, два источника 44 и 45 постоянного напряжения, два элемента НЕ 46 и 47, преобразователь 48 уровня и элемент 49 выделения модуля. Блок 12 коррекции (фиг.4) содержит два резистора 50 и 51, аналого-цифровой 52 и цифроаналоговый 53 преобразователи, арифметико-логический блок 54 и компаратор 55.

Устройство для измерения температуры работает следующим образом.

При первичном включении устройства автоматически реализуется операция коррекции погрешности, обусловленной неидентичностью характеристик преобразования первого и второго термоэлектрических преобразователей. Эта операция выполняется в БК 12 по командам от БС 8, поступающим по шине управления (ШУ). Далее скорректированный сигнал поступает на вход БФИ 13, в котором обеспечивается формирование последовательностей импульсов для идентификации периодов фазовых переходов.

БОП 14 работает как однопороговый прецизионный компаратор, реализуя сравнение выходного сигнала БФИ 13 с опорным напряжением, незначительно превышающим нулевой уровень. Сигнал логической единицы на выходе БОП 14 формируется только в период протекания фазового перехода в реперном материале ТЭП 2. Идентификация периодов фазовых переходов реперных материалов осуществляется БФИ 13, БОП 14 и БС 8. Для этого осуществляется проверка условий равенства единице выходных напряжений БФИ 13 и БОП 14. До начала калибровки эти напряжения равны нулю. При протекании фазового перехода в материале 5 оба они соответствуют уровню логической единицы, а при протекании фазового перехода в материале б выходное напряжение БФИ, поступающее на БС 8, равно единице, а выходное напряжение БОП равно нулю. При начале фазового перехода в материале 5 включается табло Фазовый переход ФП1, далее по выходу шины управления (ШУ) подаются импульсы на управляющий вход коммутатора 7, который устанавливается в положение, при котором на его выход подается термоЭДС EI ТЭП 1.

В следующем шаге по выходу ШУ поступает импульс запуска АЦП 9, осуществляющего преобразование ЭДС EI в цифровой код. Непосредственно за этим по соответствующему выходу ШУ на управляющий вход

УК 11 поступает импульс управления устанавливающий УК 11 в положение, обеспечивающее передачу кода с выхода АЦП 9 на вход записи ОЗУ 15, и происходит запись кода Ei (Ti) в регистр ОЗУ. Затем этот код

пересылается по команде с ШУ в АБ 17, после чего в буферный регистр 19 АБ 17 записывается код этого значения ЭДС. Далее в АБ 17 осуществляется чтение кода из ПЗУ 16 и операция суммирования двух операндов и код разности пересылается по команде с ШУ в регистр ОЗУ 15. После этого включается табло фазового перехода ФПа. По достижении температуры Таи при выполнении условий фазового перехода материала 6 (анализ условий непрерывно выполняется блоками БС 8 БФИ 13 и БОП 14) включается табло Фазовый переход ФП2 и аналогично предыдущей осуществляется калибровка при температуре Т2. По

окончании процесса калибровки, когда в ОЗУ 15 записан второй код разности, включается табло Калибровка окончена.

Далее на основании оценок абсолютной погрешности измерительного канала при

двух значениях температуры TI и Т2 вычисляются коэффициенты А и В линейной поправочной функции. Для этого осуществляется (по команде с ШУ) пересылка необходимых кодов в АБ 17 и ОЗУ 15.

производится последовательность операции по вычислению этих коэффициентов и результаты (коды коэффициентов А и В заносятся в регистры ОЗУ 15. При этом устройство переходит в режим измерения.

5 Включается табло Режим измерения, УК7 переводится в режим ручного управления, при котором его состояние (подключение ТЭП 1 или ТЭП 2) определяется положением переключателя на пульте управления опера0 тора, УК 11 устанавливается в положение, при котором выход АЦП 9 связан с информационным входом АБ 17, производится запуск АЦП 9, и в буферный регистр 21 АБ 17 записывается код текущего значения изме5 рительного сигнала. Далее из ОЗУ 15 в АБ 17 пересылаются коды коэффициентов А и В и производится последовательность операций по вычислению кода текущего значения поправки, вычисляется скорректированное

значение кода Ес Е + ЕКОр, значение кода

температуры, а результат пересылается в БЦИ 10. Затем по команде с ШУ БЦИ 10 запускается, и на табло осуществляется индикация результата измерения температуры с коррекцией погрешности измерительного канала. Тот же результат выводится а регистратор 18.

Все операции осуществляются по командам БС 8, поступающим по шине управления. Необходимым условием нормальной работы устройства является вынесение температуры фазового перехода реперных материалов 5 и 6 калибраторов за пределы рабочего диапазона температуры, а также обязательное прохождение обоих значений температур и фазовых переходов после включения устройства перед его переходом в рабочий режим.

Длительность импульсов на выходах БФИ 13 и БОП 14 находятся в строгом соответствии с длительностью процессов фазовых переходов, которая в свою очередь определяется массой реперных материалов и другими постоянными факторами. Амплитуда импульсов определяется характером изменения температуры объекта измерения Т( г) во времени. В случае наличия периода стабильности температуры измерительных зондов импульсы на выходах БФИ 13 и БОП 14 не будут сформированы, что позволяет вести нагревав и охлаждение объекта измерения по произвольному закону изменения температуры во времени. Обеспечиваемая при этом высокая достоверность распознавания моментов начала и конца процессов фазовых переходов реперных материалов дает возможность исключить необходимость использования нагревателя, задающего режим изменения температуры и сделать процесс измерения температуры непрерывным. Для этого целесообразно использовать реперны е материалы с температурами фазового перехода, лежащими вблизи границ диапазона измерения температуры, но за его пределами. Последний фактор значительно повышает точность оценки погрешности ТЭП, поскольку ее значение оценивается при температурах, близких к измеряемым.

Благодаря этому устройство обеспечивает формирование тестового калибровочного сигнала, текущий контроль разностной ЭДС блоками БФИ и БОП, обеспечивает выделение достоверного признака моментов начала и конца фазовых переходов, а измерение в течение фазовых переходов термоЭДС первого и второго ТЭП позволяет получить численные оценки погрешносп измерительного канала при двух значениях температуры. Собственно измерение температуры, как указано выше, осуществляется непосредственным измерением термоЭДС первого или второго ТЭП, выбираемого по команде оператора. 5Формула изобретения

1. Устройство для измерения температуры, содержащее первый и второй термоэлектрические преобразователи с калибраторами, полости которых заполне0 ны реперными материалами с известными температурами фазового перехода, соединенные последовательно-встречно, первый управляемый коммутатор, подключенный- первым и вторым входами к холодным спа5 .м соответствующих термоэлектрических преобразователей, а выходом - к входу аналого-цифрового преобразователя, второй управляемый коммутатор, блок синхронизации и блок цифровой индикации, с л и-ч а

0 ю щ е е с я тем, что, с целью повышения точности измерения, в него введены последовательно соединенные блок коррекции, блок формирования импульса и блок определения полярности, информационными

5 выходами подключенные соответственно к первому, второму и третьему входам блока синхронизации, четвертым входом подключенного к первому выходу ан лого-цифрово- го преобразователя, группой выходов

0 подключенного к первой группе входов второго упоавляемого коммутатора, оперативное запоминающее устройство, постоянное запоминающее устройство, арифметический блок и регистратор, информационным

5 входом подключенный к одноименному входу блока цифровой индикации и к выходу арифметического блока, вторым выходом подключенного к пятому входу блока синхронизации, выходы управления которого

0 подключены к входам управления блока коррекции, первого управляемого коммутатора, второго управляемого коммутатора оперативного запоминающего устройства, арифметического блока, блока цифровой

5 индикации, регистратора, аи лого-цифро- вого преобразователя и посте., ного запоминающего устройства, выходами подключенного к первой группе информационных входов арифметического блока,

0 второй группой информационных входов подключенного к первой группе выходов оперативного запоминающего устройства, а третьей группой - к выходам второго управляемого коммутатора, вторая группа входов

5 которого подключена к второй группе выходов оперативного запоминающего устройства, при этом первый и второй входы блока коррекции подключены соответственно к первому и второму входам первого управляемого коммутатора, третьим входом подключенного к точке соединения термоэлектрических преобразователей.

2. Устройство по п. 1, отличаю щее- с я тем, что арифметический блок содержит первый, второй, третий и четвертый регистры, первый, второй, третий, четвертый, пятый и шестой, седьмой, восьмой, девятый и десятый.сумматоры, первый, второй, третий, четвертый, пятый и шестой переключатели, первый и второй делители и элемент задержки, причем первый и второй входы арифметического блока соединены с входами первого и второго регистров, выходы которых подключены к первым входам первого и второго сумматоров соответственно, выходы сумматоров являются выходами арифметического блока, вторые входы сумматоров соединены с третьим и четвертым входами арифметического блока и соответственно с первыми входами первого и второго перемножителей, вторые входы которых подключены соответственно . пятому и шестому входам арифметическою блока, а их выходы соединены с первым и вторым входами третьего сумматора, выход которого подключен к первому входу первого делителя, второй вход которого соединен с седьмым входом арифметического блока и с первым входом второго делителя, пятый и шестой входы арифметического блока соединены соответственно с первым и вторым входами четвертого сумматора, выход которого подключен к второму входу второго делителя, выход первого и второго делителей являются выходами арифметического блока, восьмой вход которого подключен к входу третьего регистра, девятый и десятый входы арифметического блока подключены соответственно к первому входу третьего перемножителя и первому входу пятого сумматора, выход третьего перемножителя подключен к второму входу пятого сумматора, выход которого соединен с первым входом шестого сумматора, второй вход которого соединен с вторым входом третьего перемножителя и выходом третьего регистра, выход шестого сумматора подключен к входу четвертого регистра, выход которого соединен соответственно с первыми входами седьмого сумматора, четвертого и пятого перемножителей, второй вход седьмого сумматора подключен к одиннадца юму входу арифметического блока, выход седьмого сумматора подключен к второму входу четвертого перемножителя, выход которого связан с первым входом восьмого сумматора, второй вход которого соединен с двенадцатым входом арифметического блока, а выход - с вторым входом пятого перемножителя, выход которого соединен с первым

входом девятого сумматора, второй вход которого подключен к тринадцатому входу арифметического блока, а выход - к первому входу шестого перемножителя, второй вход

которого соединен с четырнадцатым входом арифметического блока, а выход - с первым входом десятого сумматора, второй вход которого подключен к выходу четвертого регистра, а выход является выходом

0 арифметического блока, причем входы управления регистров, сумматоров, перемножителей, делителей и элемента задержки соединены с соответствующими входами управления арифметического блока, а вы5 ход элемента задержки является выходом готовности арифметического блока.

3.Устройство по п. 1, отличающее- е с я тем, что блок формирования импульса содержит первый и второй дифференциаль0 Ные усилители, первый и второй источники постоянного напряжения, первый и второй элементы НЕ, преобразователь уровня и элемент выделения модуля, причем вход блока формирования импульса соединен с

5 прямым входом первого и инверсным входом второго дифференциальных усилителей, инверсный вход первого и прямой вход второго дифференциальных усилителей подключены соответственно к выходам пер0 вого и второго источников постоянного на- пряжения,выходпервого

дифференциального усилителя подключен к входу первого элемента НЕ, выход второго дифференциального усилителя подключен

5 через преобразователь уровня к входу второго элемента НЕ, выходы обоих элементов НЕ соединены с входом элемента выделения модуля, выход которого является первым выходом блока формирования

0 импульса а выходы обоих элементов НЕ являются его вторым выходом.

4,Устройство поп.1,отличающее- С я тем, что блок коррекции содержит первый и второй резисторы, аналого-цифровой

5 и цифроаналоговый преобразователи, арифметико-логическое устройство и компаратор, причем первый вход блока коррекции соединен с его первым выходом и первым входом аналого-цифрового преобразовате0 ля, второй вход блока коррекции через первый резистор соединен с вторым выходом блока и вторым входом аналого-цифрового преобразователя, параллельно первому резистору подключены последовательно сое5 диненные выход цифроаналогового преобразователя и второй резистор, выход аналого-цифрового преобразователя соединен с входами компаратора и арифметико-логического устройства; выход которого соединен с входом цифроаналогового

преобразователя, выход компаратора является третьим выходом блока коррекции, а управляющие входы аналого-цифрового и

цифроаналогового преобразователей подключены к соответствующим входам управления блока коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения температуры | 1985 |

|

SU1390515A1 |

| Устройство для измерения температуры | 1984 |

|

SU1281921A1 |

| Устройство для измерения температуры | 1987 |

|

SU1578511A1 |

| Устройство для измерения температуры | 1986 |

|

SU1434279A1 |

| Способ определения температуры | 1989 |

|

SU1737281A1 |

| Устройство для контроля состояния объекта | 1983 |

|

SU1119055A1 |

| Устройство для измерения температуры | 1987 |

|

SU1506294A1 |

| Устройство для измерения температуры | 1989 |

|

SU1677535A1 |

| Устройство для измерения температуры | 1984 |

|

SU1236330A1 |

| Преобразователь фазового сдвига в цифровой код | 1982 |

|

SU1056073A1 |

Изобретение относится к термометрии и позволяет повысить точность измерения температуры. При включении устройства автоматически реализуется операция коррекции погрешности, обусловленной неидентичностью характеристик преобразования первого и второго ТЭП. Скорректированный сигнал поступает на вход блока 13 формирования импульса для идентификации периодов фазовых переходов. Блок 14 определения полярности сравнивает выходной сигнал блока 13 с опорным напряжением, незначительно превышающем нулевой уровень. Работой устройства управляет блок 8 синхронизации. По сигналам блока 8 запускается АЦП 9, выходной код которого запоминается в ОЗУ 15. Из ОЗУ 15 код пересылается в специализированный арифметический блок 17, где суммируется с операндом из ПЗУ 16. На основании оценок абсолютной погрешности измерительного канала при двух значениях температуры Т1 и Т2 вычисляются коэффициенты поправочной функции. Результат измерения отображается на блоке 10 цифровой индикации и выводится на регистратор 18. 4 ил.

7 5 J

Уеоп

Шина управления

f

щ

-V

Вр(т)

2

50 -O

57

-Ш

Wy

л-ШЙС 5Г

6ФИ 7J

47

/ 1 J-LTU

Фиг.З

i/

SK

52}fАГШУ

Фиг ft

| Авторское свидетельство СССР № 1182282,кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР М 1592738, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-08-23—Публикация

1988-12-26—Подача