(Б) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональное интегрирующее устройство | 1977 |

|

SU732903A1 |

| Генератор степенных функций | 1976 |

|

SU636631A1 |

| Функциональный частотный преобразователь | 1983 |

|

SU1120365A1 |

| Функциональный преобразователь | 1980 |

|

SU886012A1 |

| Устройство для воспроизведения функций | 1987 |

|

SU1411787A1 |

| Функциональный преобразователь | 1974 |

|

SU516051A1 |

| Широтно-импульсный развертывающий функциональный преобразователь | 1987 |

|

SU1474693A1 |

| Измерительный преобразователь напряжения в частоту следования импульсов | 1975 |

|

SU532174A2 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Интегрирующее устройство | 1983 |

|

SU1267439A1 |

1

Изобретение относится к информационно-измерительной технике и может быть использовано при построении аналоговых и аналого-цифровых вычислительных устройств.

Известен преобразователь напряжение-частота, содержавший сумматор входных переменных, соединенный последовательно с интегратором,и блок, формирующий импульсыt 1 .

Недостатком этого преобразователя является ограниченный класс воспроизводимых функций.

Наиболее близким к изобретению является функциональный частотный преобразователь, содержащий два интегратора, между входами и выходами каждого из которых включен ключ, выходы -интеграторов подключены к первым входам соответствующих кймпараторов, выходы компараторов через блок управления подключены к управляющим входам ключей, четыре сумматора, входы которых через соответствующие ключевые элементы сое-/: динены с источниками входного и опорного напряжений, выходы первого и второго сумматоров подключены соответственно к входам интеграторов, а вторые входы компараторов соединены cooтвeтcтвeн ю с выходами третьего и четвертого сумматоров J2j.

Недостатком этого преобразова,теля является недостаточно широкий класс воспроизводимых функциональных возможностей.

Цель изобретения - расширение класса решаемых задач.

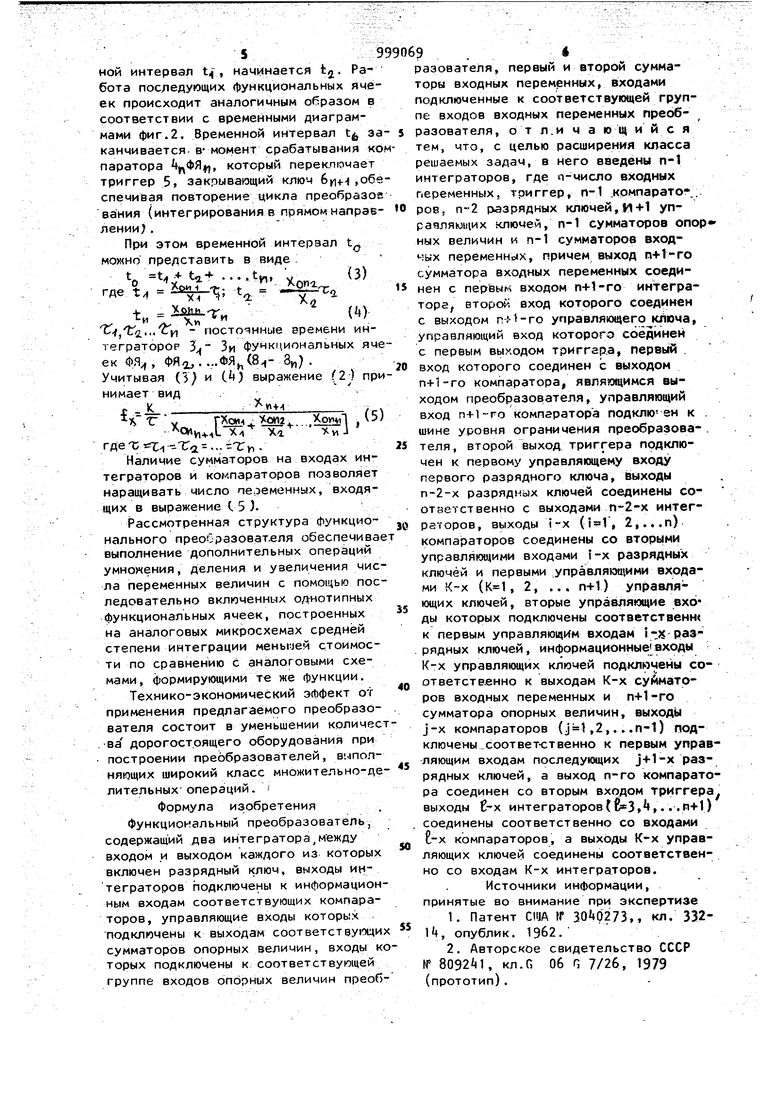

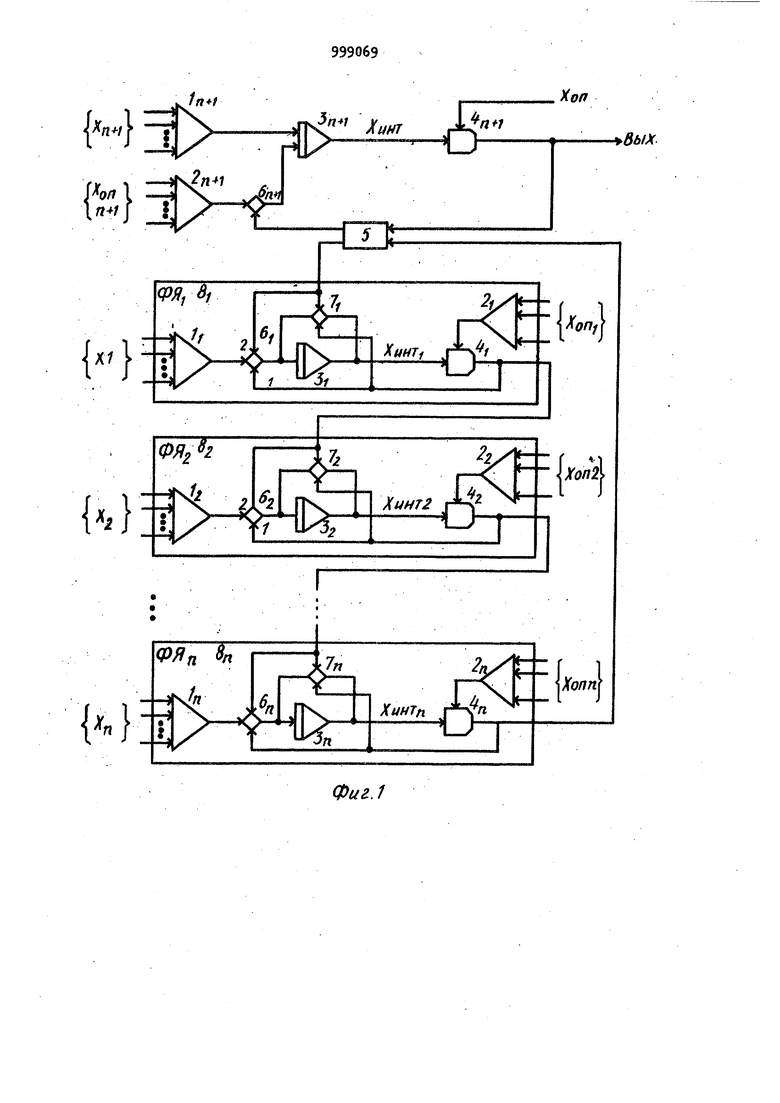

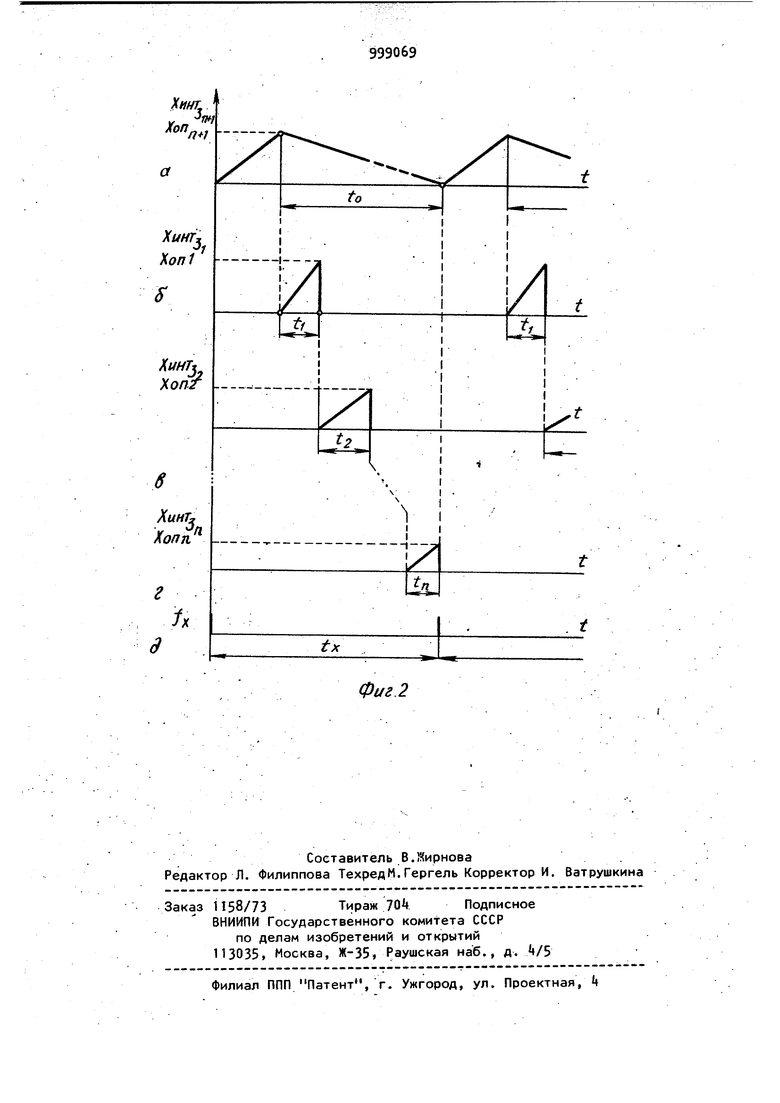

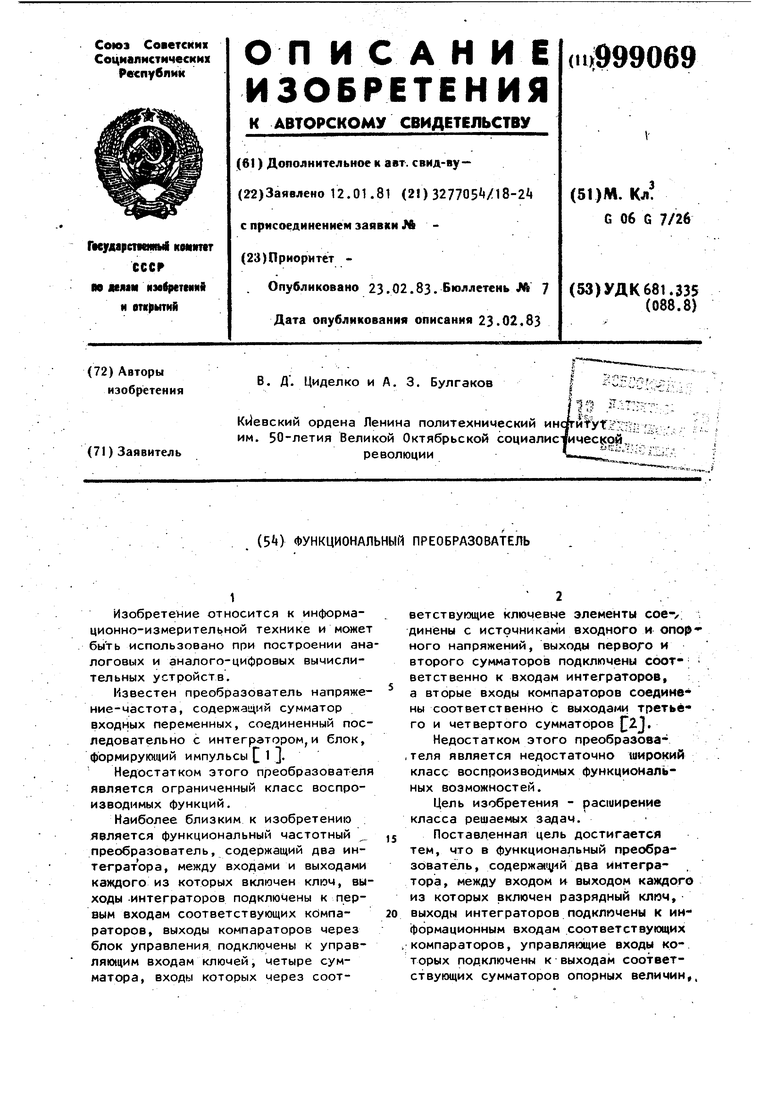

Поставленная цель достигается тем, что в функциональный преобразователь, содержа1Ц|1й два Интегратора, между входом и выходом каждого из которых включен разрядный ключ, выходы интеграторов подключены к информационным входам соответствующих компараторов, управляющие входы которых подключены к выходам соответствующих сумматоров опорных величин,. входы которых подключены к соответствующей группе входов опорных величин преобразователя, первый и вто рой сумматоры входных переменных, входами подключенные к соответствую щей группе входов входных переменны преобразователя, введены п-1 интеграторов, где п-число входных перемен ных, триггер, п-1 компараторов, п-2 разрядных ключей, управляющих ключей, п-1 сумматоров опорных вели чин и О-1 сумматоров входных переменных, причем выход п+1-го сумматора входных переменных соединен с первым входом П-f 1-го интегратора, второй вход которого соединен с выходом п+1-го управляющего ключа, управляющий вход которого соединен с первым выходом триггера, первый вхо которого соединен с выходом п+1-го компаратора, являющимся выходом пре/ образователя,управляющий вход п+1-г компаратора подключен к шине уровня ограничения лреобразователя, второй выход триггера подключен к первому управляющему входу первого разрядного ключа, выходы n-2-x разрядных ключей соединены соответственно с выходами n-2-x интеграторов, выходы i-x (i, 1,2„. .п) компараторов соединены со вторыми управляющими входами 1-х разрядных ключей и гтервыми управляющими входами К-х (,2,..п+1) управляющих ключей, вторые управляющие входы которых подключены соответственно к первым управляющим: вхо дам i-x разрядных ключей подключены соответственно к выходам К-х сум маторов входных переменных и п+1-го сумматора опорных величин, выходы J-X компараторов (,2,...п-1) под ключены соответственно к первым управляющим входам последующих j+1-x разрядных ключей, а выход п-го компаратора соединен со вторым входом триггера, выходы -х интеграторов (,t,.. .п+1) соединены соответственно со входами i-x компараторов, а выходы К-х управляю1чих ключей сое динены соответственно со входами КНа фиг. 1 представлена структур ная схема функционального преобразователя СФП); на фиг.2 - временные диаграммы его работы. Функциональный преобразователь ( фиг. 1 ) содержит,сумматоры Ц 1 входных переменных, сумматоры ..| опорных величин, интеграторы 3v|-3u+j «омпараторы -V-fb триггер 5, управляющие ключи о разрядные ключи ., функциональные ячейки П . Функциональный преобразователь работает следующим образом.(фиг.2. Если в исходный момент времени на первый вход интегратора Зц+ грез сумматор входных переменных .л подаются входные переменные Xy.j, то происходит их интегрирование в прямом направлении до уровня ограиичения XQ(1иг.2а компаратора ,.-f,который, срабатывая, переключает т(и1- гер 5. Сигналом первого выхода триггера 5 открывается управляющий ключ 6, сигналом второго выхода открывается ключ 6-1 и закрывается разрядный ключ 7. первой функциональной ячейки ФЯ . При этом, на второй вход интегратору 3)t через ключ бу, с выхода сумматора 2j подаются опорные еевеличины XOM, чем обуславливается интегрирование в обратном направлении в течение времени t, которое определяется последовательным интег рированием входных переменных Х, Х. . .Х, соответствующих функциональных ячеек ФЯ , ФЯ ФЯу,. В результате равенства зарядов накопительного элемента интегратора Зу, при прямом и обратном интегрировании, можно записать M + t OYlnfi-o где ty- период следования выходных имимпульсов. Откуда, выходная частота FV, ФП определяется выражением f ., - ; 2) tx ои, ., Временной интервал 1,,начинается в момент срабатывания ключей б. , 7 подключения входных переменных Х через сумматор Ц ко входу интегратора . На выходе интегратора 3 величина Ху,ц-г изменяется по линейному закону (фиг.26) до опорной переменной величины Х компаратора 4 , подаваемой с выхода сумматора 2, который закрывает ключ 6 и открывает ключ 7 ФЯ , а в ФЯ,-. закрывает ключ 7, открывает ключ $2.- - этот момент сбрасывается в исходное состояние интегратор , переключается в режим прямого интегрирования интегратор 3 ФЯ2(фиг.2в), заканчивается временной интервал Ц, начинается Работа последующих функциональных ямеек происходит аналогичным образом в соответствии с временными диаграммами фиг.2. Временной интервал t за канмивается- в момент срабатывания ко паратора , который перек.пюмает триггер 5 закрывающий ключ .обе спечивая повторение цикла преобразоа вания (интегрирования в прямом направ лении;, При этом временной интервал t можно представить в виде г.... U) а л-- .,.. Си - постоянные времени интеграторор 3 Зи функциональных яче ек ФЯ. ФЯа,....ФЯ( Учитывая (3} и (i) выражение (2) при нимает вид . - - (5) ЧТу rXoHi itoMi. XovHil . ЧТИ гдеСтт;.-:.Га ...гТк. Наличие сумматоров на входах интеграторов и компараторов позволяет наращивать число пе.оеменных, входящих в выражение (.5). Рассмотренная структура Функционального преобразователя обеспечивае выполнение дополнительных операций умножения, деления и увеличения числа переменных величин с помощью последовательно включенных однотипных функциональных ячеек, построенных на аналоговых микросхемах средней степени интеграции меньшей стоимости по сравнению с аналоговыми схемами, формирующими Т€ же функции. Технико-экономический эффект от применения предлагаемого преобразователя состоит в уменьшении количест ва дорогостоящего оборудования при построении преобразователей, выполняющих широкий класс множительно-де лительных операций. Формула изобретения Функциональный преобразователь, содержащий .два интегратор а, между входом и выходом каждого из которых включен разрядный ключ, выходы интеграторов подключены к информационным входам соответствующих компараторов, управляющие входы которых подключены к выходам соответст0у|х:1их сумматоров опорных величин, входы ко торых подключены к соответствующей группе входов опорных величин преобразоватеЛя, первый и второй сумматоры входных переменных, входами подключенные к соответствующей группе входов входных переменных преобразователя, от л,и ч а ю щ и и с я тем, что, с целью расширения класса решаемых задач, в него введены п-1 интеграторов, где п-число входных переменных, триггер, п-1 компарато-,.. ров5 п-2 разрядных ключей,И+1 управляющих ключей, п-1 сумматоров опор ных величин и п-1 сумматоров входных переменных, причем выход п+1-го сумматора входных переменных соединен с первым входом п+1-го интегратора, второй вход которого соединен с выходом ni-i-ro управляющего клоча, управляющий вход которого соединен с первым выходом тригггр.а, первы1й . вход которого соединен с выходом п+1-го компаратора, являющимся выходом преобразов1ателя, управляющий вход п+1-го компаратора подключен к . шине уровня ограничения преобразова- , теля, второй выход триггера подключен к первому управляющему входу первого разрядного ключа, выходы n-2-x разрядных ключей соединены соответственно с выходами n-2-x интеграторов, вь1хоАЫ |-х (i-l, 2,...п) компараторов соединены со вторыми управляюодими входами i-x разрядных ключей и первыми управляющими входами (, 2, ... п+1) управляющих ключей, вторые управляющие входы которых подключены соответственж к первым управляющим входам i JJразрядных ключей, информационныевходы К-х управляющих ключей подключены соответственно к выходам К-х суйматрров входных переменных и п+1-го сумматора опорных величин, выходы J-X компараторов ,2,...п-1) подключены соответ-ственно к первым управляющим входам последующих j+1-x разрядных ключей, а выход п-го компаратора соединен со вторым входом триггера, выходы бх интеграторов б З,,.. .п+1) соединены соответственно со входами L-X компараторов, а выходы К-х управляющих ключей соединены соответственно со входам К-х интеграторов. Источники информации, принятые во внимание при экспертизе 1.Патент США № ,, кл. 332Й, опублик. 19б2. 2,Авторское свидетельство СССР № 8092«1, кл.П 06 г, 7/26, 1979 (прототип).

Фиа.1

XHffL

XUHT,, 1 Xoni

s

KuHTr Xon.f

/

Кинц Xofin

-e

I

I -1tx

Фиг.2

Авторы

Даты

1983-02-23—Публикация

1981-01-12—Подача