(54) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь сигнала тензомоста в интервал времени | 1987 |

|

SU1580260A1 |

| Нелинейный преобразователь | 1988 |

|

SU1674172A1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| Регулятор электрической мощности переменного тока(его варианты) | 1981 |

|

SU983690A1 |

| Устройство для управления вентильным преобразователем со слежением | 1988 |

|

SU1607061A1 |

| Функциональный генератор | 1979 |

|

SU781839A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Измеритель среднеквадратического значения напряжения одиночного импульса случайной формы и длительности | 1987 |

|

SU1429054A1 |

| Устройство для контроля качества электрической изоляции | 1990 |

|

SU1749845A1 |

| Функциональное интегрирующее устройство | 1977 |

|

SU732903A1 |

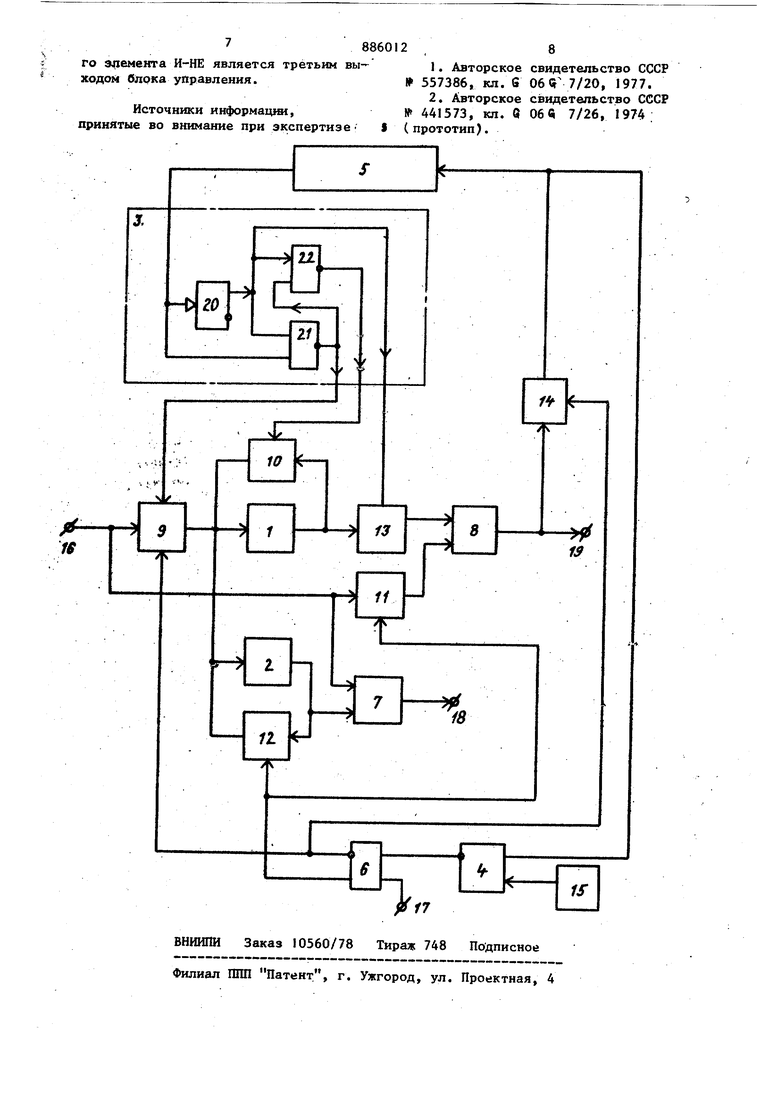

Изобретение относится к функциональным преобразователям электрических сигналов и может быть использовано в аналоговых вычислительных машинах. Известен преобразователь сигналов по степенно закону, содержащий блок управления генератор линейного напряжения, степенной преобразовател и усилительный блок ГП. Однако известное устройство преобразует сигнал только по степенному закону. Наиболее близким к предлагаемому является функциональный преобразователь, содержащий ключи, интеграторы, компаратор, блок управления и источник опорного напряжения 1.21, Указанное устройство позволяет по лучить только временный интервал, пропорциональный степенному полиному от входного напряжения. Цель изобретения - расширение кла са воспроизводим1 1х функций. Поставленная цель достигается тем, что в функциональный преобразователь, содержащий соединенные последовательно первый ключ и первый интегратор, второй интегратор, компаратор, вход которого подключен к выходу источника опорного напряжения, блок управления, второй ключ, первый и второй разрядные ключи, подключенные соответственно между входом и выходом первого и второго интеграторов, BXOjVd первого и второго ключей присоединены ко входу функционального преобразователя, первый выход блока управления соединен с управляющим входом первого ключа, второй выход блока управления подключен к управляющему входу первого разрядного ключа, введены преобразователь напряжения в дпительность импульса, блок памяти, триггер, сумматор и первый и второй дополнительные ключи, причем выход компаратора соединен со входом триггера, инверсный выход триггера подключен к дополнительному управляющему входу первого ключа и к управл ющему входу второго дополнительного ключа, прямой выход триггера присоединен к управляющим входам,второго ключа и второго разрядного ключа, вы ход первого интегратора через первый дополнительньй ключ присоединен к первому входу блока памяти, ко второму входу которого подключен выход второго ключа, выход блока памяти че рез второй дополнительный ключ присоединен ко входу преобразователя на пряжения в длительность импульса и ко второму входу компаратора, выход преобразователя напряжения в длитель ность импульса соединен со входом блока управления, третий выход которого подключен к уугравляющему входу первого дополнительного ключа, первы вход сумматора присоединен ко входу функционального преобразователя, выход второго интегратора подключен ко второму входу сумматора, выход котор го и выход блока памяти являются соответственно первым и вторым выходами функционального преобразователя, второй вход триггера подключен.ко входу запуска функционального преобр зователя, входы первого и второго интеграторов соединены. Кроме того, блок управления содержит счетный триггер и первый и второй элементы И-НЕ, вход счетного триггера подключен ко входу блока управления и первому входу первого элемента И-НЕ, второй вход которого соединен с первым входом второго эле мента И-НЕ,второй вход которого присоединен к выходу первого элемента И-НЕ, являющемуся первым выходом (5ло ка управления, выход второго элемента И-НЕ является вторым выходом блок управления, первый вход второго элемента И-НЕ является третьим выходом блока управления. На чертеже представлена функциональная схема предлагаемого преобразователя. Функциональный преобразователь содержит первый и второй и11теграторы 1 и 2, блок 3 управления, компаратор 4, преобразователь 5 напряжения в длительность импульса, триггер 6, сумматор 7, блок 8 памяти, первый клю 9, первый разрядный ключ 10, второй кл|8ч 11, второй разрядный клю 12, первый и второй дополнительные ключи 13 и 14, источник 15 опорного напряжения, вход 16, вход 17 запуска, первый и второй выходы 18 и 19 функционального преобразователя, счетный триггер 20, первый и второй элементы И-НЕ 21 и 22. Функциональный преобразователь работает следующим образом. До подачи импульса на вход 17 запуска компаратор 4 устанавливает триггер 6 в состояние, при котором высокий потенциал на его инверсном выходе размыкает ключи 9 и 14, а низкий потенциал прямого выхода замыкает ключи П и 12, Сигнал со входа 16 через ключ I1 запоминается в блоке 8 памяти и одновременно подается на сумматор 7. В момент прихода импульса на вход 17 триггер 6 переключается, размыкаются ключи 1I и 12, замыкается ключ 14, ас дополнительного управляицего входа ключа 9 снижается размыкающий сигнал. Запомненное входное напряжение в блоке 8 памяти через замкнутый ключ 14 подается на вход блока 5, на выходе которого формируются прямоугольные импульсы с длительностью, пропорциональной величине входного напряжения. Эти.импульсы поступают в блок 3 управления на вход счетного триггера 20. Счетный триггер 20 перебрасывается отрицательным фронтом каждого импульса и в момент, когда на его прямом выходе устанавливается единичное состояние, замыкается ключ 10 и первый интегратор обнуляется. При этом на первом и втором выходах 18 и 19 устанавливаются напряжения, соответствующие величине входного бигнала. В момент размыкания ключа 10 замыкается ключ 9 и происходит интегрирование входного напряжения первым и BTopbiM интеграторами i и 2. В момент размыкания ключа 9 на выходах первого и второго интеграторов 1 и 2 устанавливаются напряжения, пропорциональные отноше1шю квадрата входного напряжения к постоянной времени интегрирования соответствующего интегратора. Одновременно замыкается ключ 13, и выходное напряжение первого интегратора 1 запоминается в блоке 8 памяти, а на выходе сумматора 7 устанавливается напряжение, равное сумме входного напряжения rt выходного напряжения второго интегратора 2. Блок 5 формирует импульсы, первый из которых отрицательным фронтом 58 замыкает ключ IО и обнуляет первый интегратор 1, а второй размыкает ключ 10 и замыкает ключ 9, благодаря чему происходит интегрирование входного напряжения в течение сформированных импульсов. Отрицательный фронт третьего импульса размыкает ключ 9 и заьыкает ключ 13. Выходное напряжение блока 8 памяти вновь подается на вход блока 5, и цикл работы повторяется. При повторении t аналогичных циклов на первом и втором выходах 18 и 19 устанавливаются напряжениягде Ujx - напряжение на входе л - масштабный коэффициент преобразователя 5 напряжения в длительность импульса}T/|HTjj - постоянные времени интегрирования соответственно первого и второго интегра торов 1 и 2. Когда напряжение на выходе блока 8 памяти достигает значения, равного напряжению источника 15 опорного напряжения, срабатывает компаратор 4 и триггер 6 перебрасывается в нулевое состояние, в результате чего функцио нальный преобразователь устанавливае ся в исходное состояние. Предлагаемый функциональный преоб разователь позволяет решать более ши рокий класс задач по сравнению с известным. Формула изобретения 1. Функциональный преобразователь содержащий соединенные последовательности первый ключ и первый интегратор второй интегратор, компаратор, первый вход которого подключен к выходу источника опорного напряжения, блок управления второй ключ, первый и второй разрядные ключи, подключенные соответственно между входом и выходом первого и второго интеграторов, входы первого и второго ключей подсоединены ко входу функционального преобразователя, первый выход блока управления , . 4. соединен с управляющим входом первого ключа, второй выход блока управления подключен к управляющему входу первого разрядного ключа, отличающийс я тем, что, с целью расширения класса воспроизводимых функций, в него введены преобразователь напряжения в длительность импульса, блок памяти, триггер, сумматор и первый и второй дополнительные ключи, причем выход компаратора соединен со входом триггера, инверсный выход триггера подключен к дополнительному управляющему входу первого ключа и к управляющему входу второго дополнительного ключа, прямой выход триггера присоединен к управляющим входам второго ключа и второго разрядного ключа, выход первого интегратора через первый дополнительный ключ присоединен к первому входу блока памяти, ко второму входу которого подключен выход второго ключа, выход блока памяти через второй дополнительный ключ подсоединен ко входу преобразователя напряжения в длительность импульса и ко второму входу компаратора, выход преобразователя напряжения в длительность импульса соединен со входом блока управления, третий выход которого подключен к управляющему входу первого дополнительного ключа, первый вход сумматора подсоединен ко входу функционального преобразователя, выход второго интегратора подключен ко второму входу сумматора, выход которого и выход блока памяти являются соответственно первым и вторым выходами функционального преобразователя, второй вход триггера подключен ко входу запуска функционального преобразователя, входы первого и второго интеграторов соединены. 2. Преобразователь по п.1, о т личающийся тем, что блок управления содержит счетный триггер и первый и второй элементы И-НЕ, вход счетного триггера подключен ко входу блока управления и первому входу первого элемента И-НЕ, второй вход которого соединен с первым входом второго элемента И-НЕ, второй вход которого присоединеи к выходу первого элемента И-НЕ, являющемуся первым выходом блока управле{шя, выход второго элемента И-НЕ является вторым выходом блока управления, первый вход второго ацемента И-НЕ является третьим выходом блока управления.

Источники информащш, принятые во внимание при экспертизе

свидетельство СССР 06 Q 7/20, 1977.

свидетельство СССР 06Q 7/26, 1974.

Авторы

Даты

1981-11-30—Публикация

1980-02-12—Подача