генератора функции или генератора сигналов. Цель изобретения - повышение точности за счет формирования функций времени с переменным шагом интерполирования. Устройство содержит коммутатор каналов 1, цифроана- логовый преобразователь 2 и п каналов, канодый из которых состоит из сумматоров 3, 12, 13, 14, 20, ключей 4, 5, 6, 7, 8, 9 и 19, аналоговых запоминающих устройств 10 и 11, цифровых управляемых сопротивлений 15 и 16, интеграторов 17 и 18, блока управления 21„ Каждый канал содер 1

Изобретение относится к вычислительной технике и может быть использовано для воспроизведения функций при выводе информации на электроН- но-лучевые трубки, графопостроители и исполнительные механизмы н управляющих вычислительных машинах, а также в качестве программируемого генератора функций или генератора сигналов.

Цель изобретения - расши эение функциональных возможностей за счет формирования функций времени с переменным шагом интерполирования.

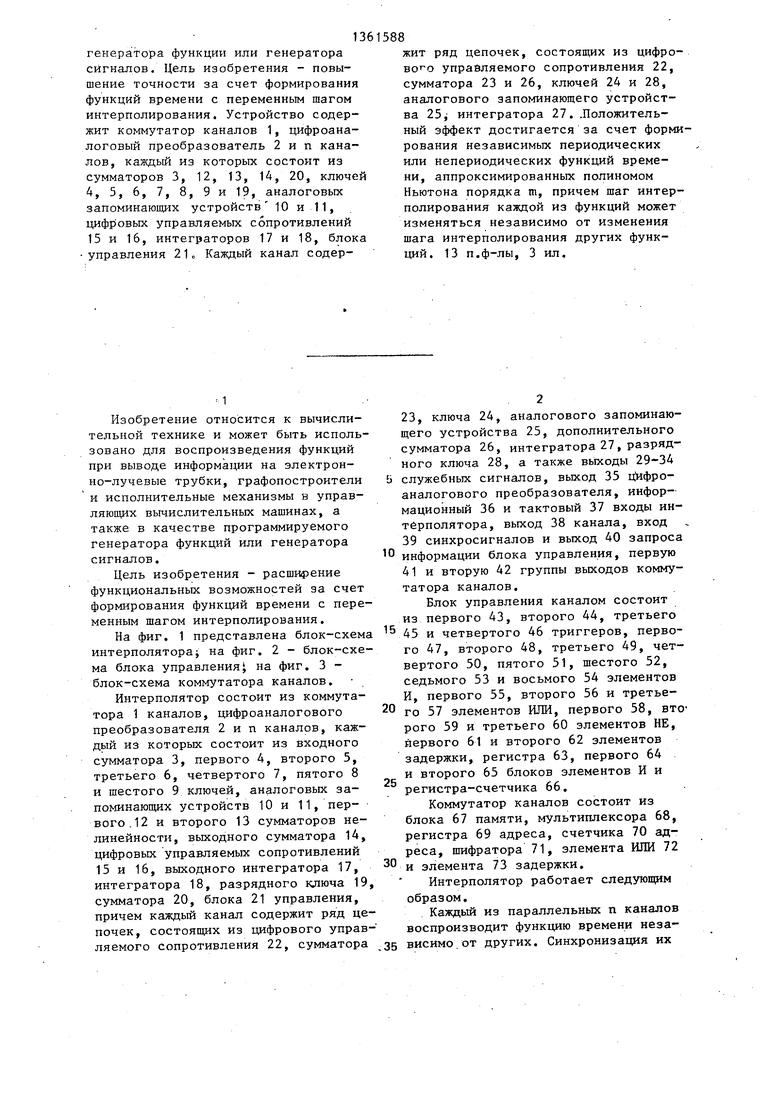

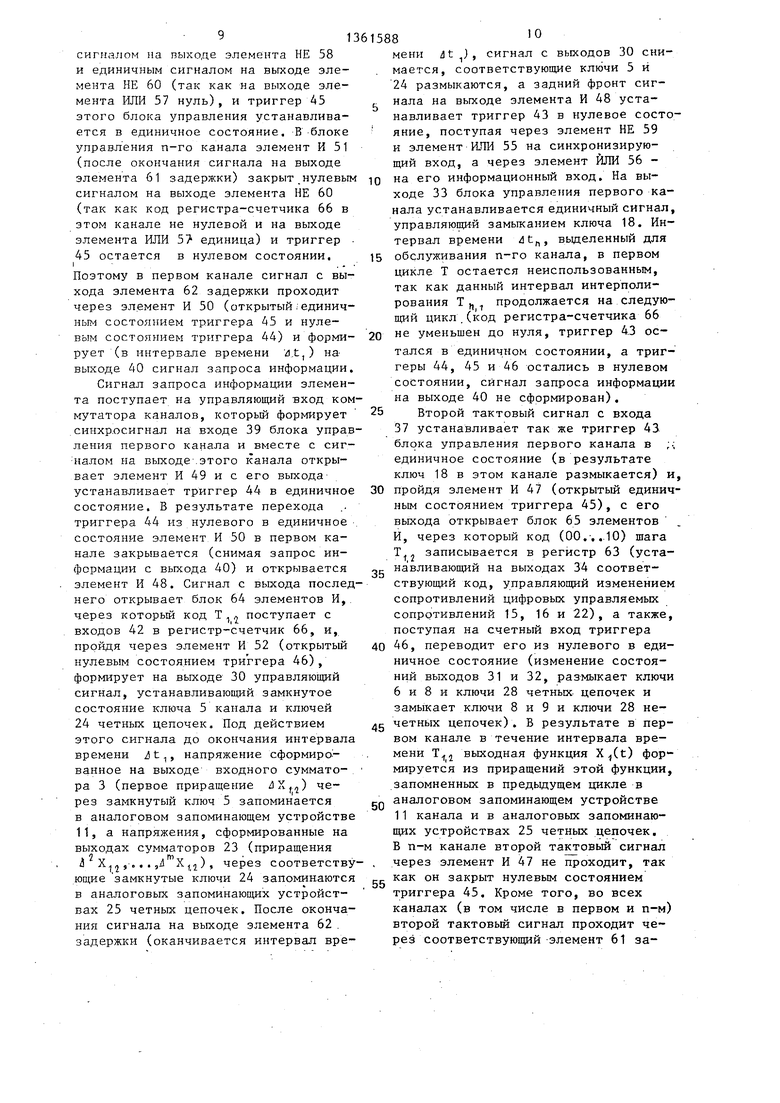

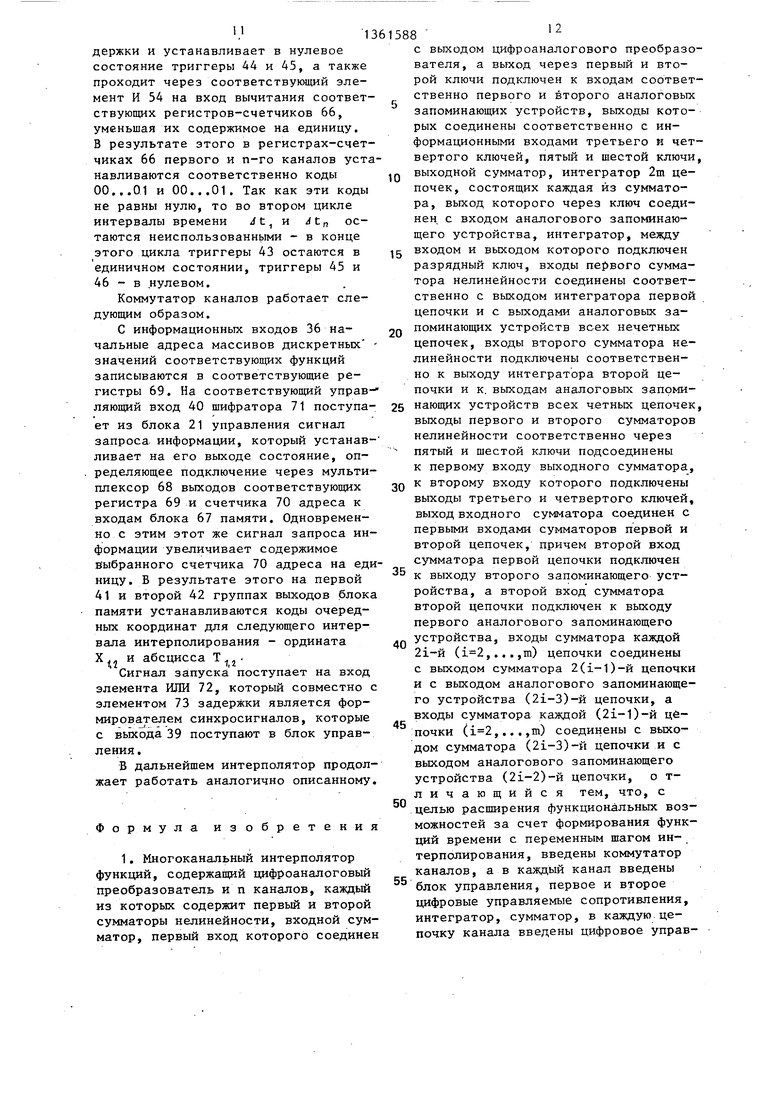

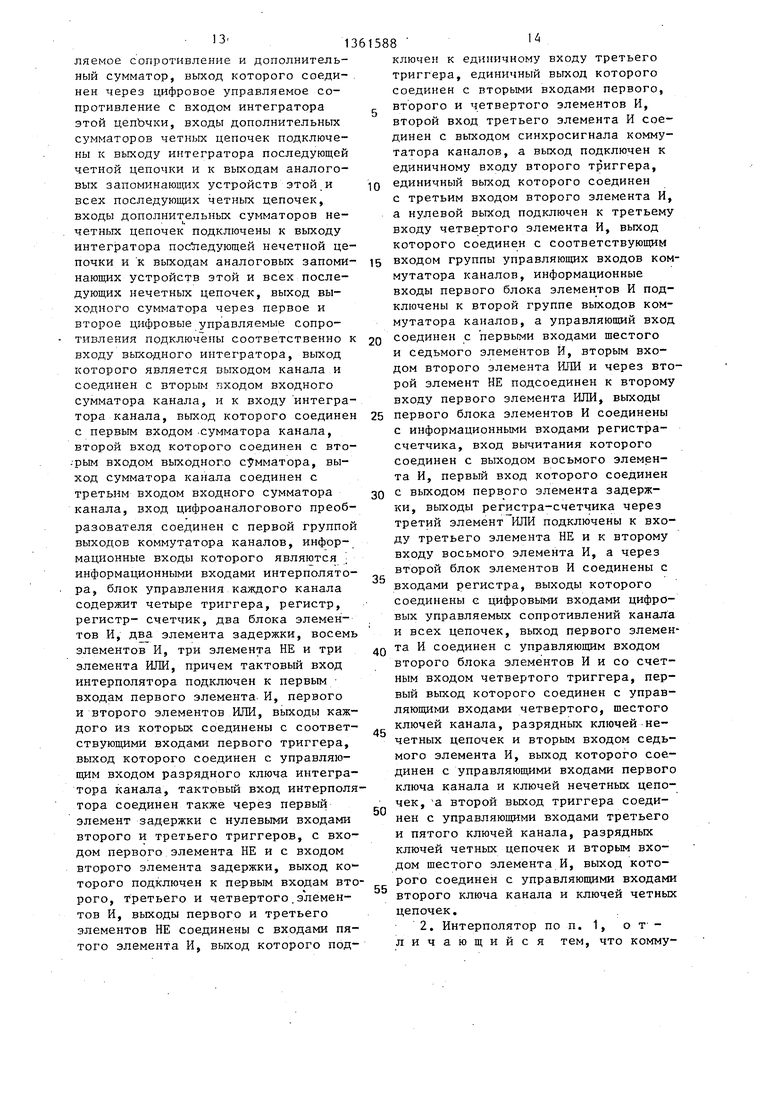

На фиг. 1 представлена блок-схема интерполятораi на фиг. 2 - блок-схема блока управления на фиг. 3 - блок-схема коммутатора каналов.

Интерполятор состоит из коммутатора 1 каналов, цифроаналогового преобразователя 2 и п каналов, каждый из которых состоит из входного сумматора 3, первого 4, второго 5, третьего 6, четвертого 7, пятого 8 и шестого 9 ключей, аналоговых запоминающих устройств 10 и 11, первого, 12 и второго 13 сумматоров нелинейности, выходного сумматора 14, цифровых управляемых сопротивлений 15 и 16, вькодного интегратора 17, интегратора 18, разрядного ключа 19, сумматора 20, блока 21 управления, причем каждый канал содержит ряд цепочек, состоящих из цифрового управляемого сопротивления 22, сумматора

жит ряд цепочек, состоящих из цифро- управляемого сопротивления 22, сумматора 23 и 26, ключей 24 и 28, аналогового запоминающего устройства 25j интегратора 27. .Положительный эффект достигается за счет формирования независимых периодических или непериодических функций времени, аппроксимированных полиномом Ньютона порядка т, причем шаг интерполирования каждой из функций может изменяться независимо от изменения шага интерполирования других функций. 13 п.ф-лы, 3 ил.

23, ключа 24, аналогового запоминающего устройства 25, дополнительного сумматора 26, интегратора 27, разрядного ключа 28, а также вь1ходы 29-34 5 служебных сигналов, выход 35 ц ифро- аналогового преобразователя, информационный 36 и тактовый 37 входы интерполятора, выход 38 канала, вход 39 синхросигналов и выход 40 запроса

информации блока управления, первую 41 и вторую 42 группы выходов коммутатора каналов.

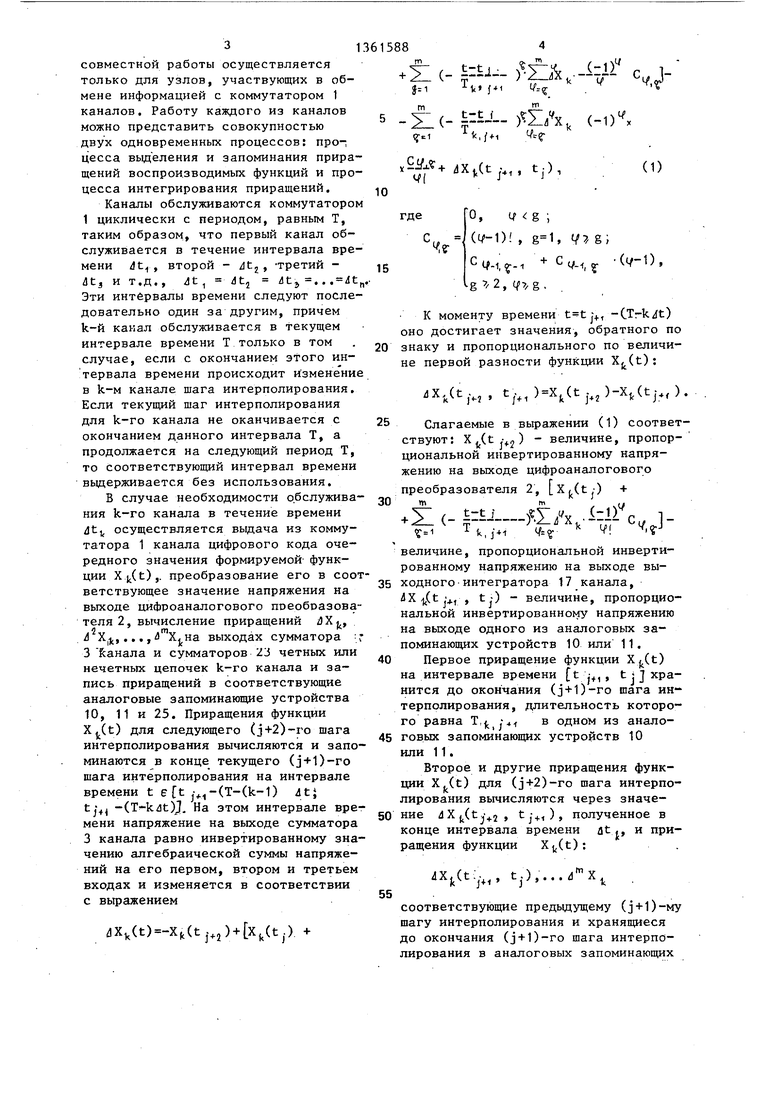

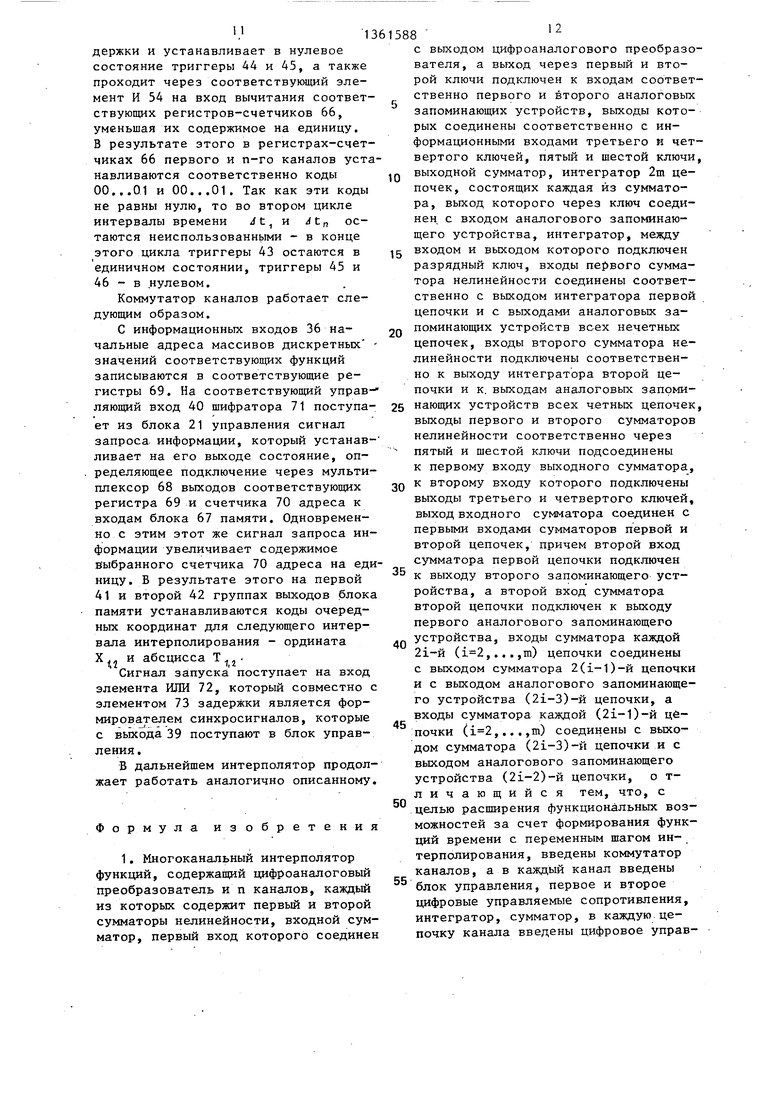

Блок управления каналом состоит из первого 43, второго 44, третьего

45 и четвертого 46 триггеров. Первого 47, второго 48, третьего 49, четвертого 50, пятого 51, шестого 52, седьмого 53 и восьмого 54 элементов И, первого 55, второго 56 и третье0 го 57 элементов ИЛИ, первого 58, второго 59 и третьего 60 элементов НЕ, первого 61 и второго 62 элементов задержки, регистра 63, первого 64 и второго 65 блоков элементов И и регистра-счетчика 66,

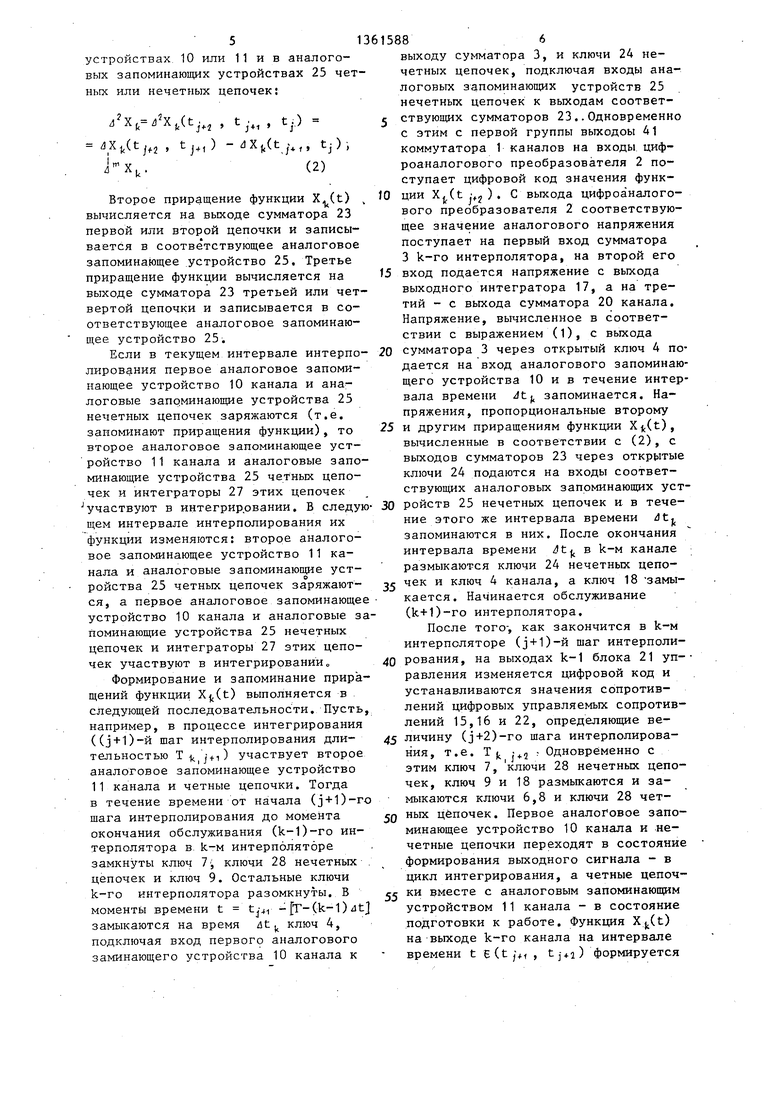

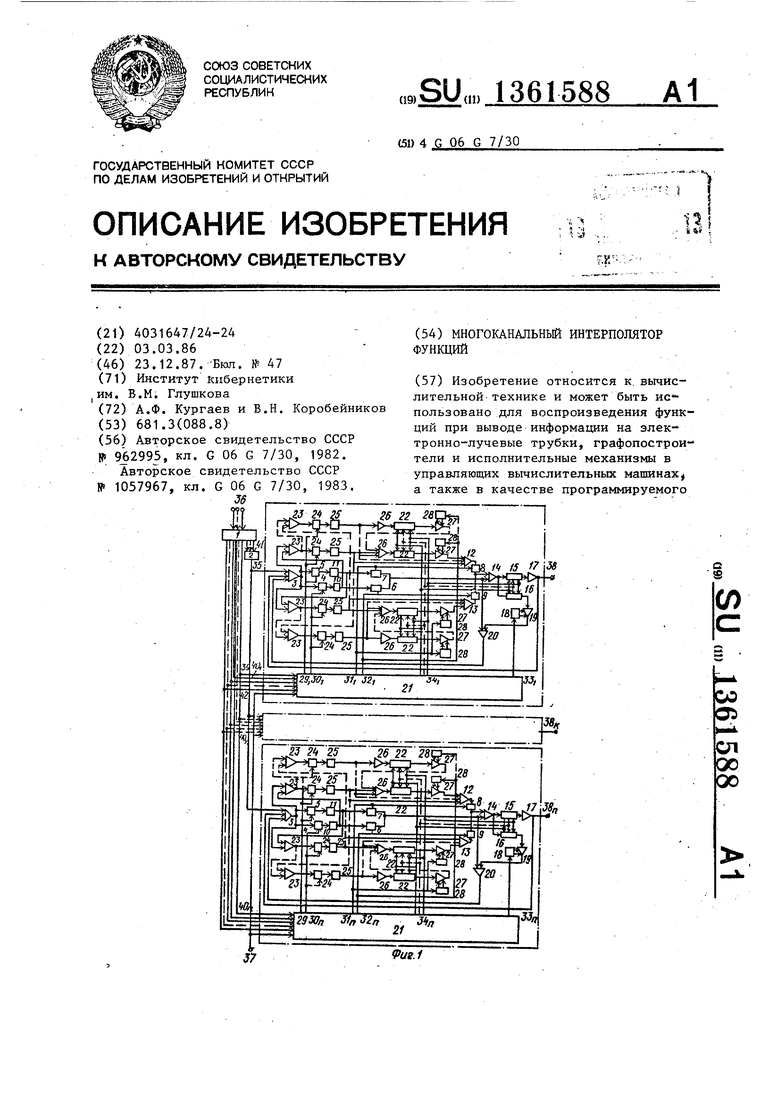

Коммутатор каналов состоит из блока 67 памяти, мультиплексора 68, регистра 69 адреса, счетчика 70 адреса, шифратора 71, элемента ИЛИ 72

и элемента 73 задержки.

Интерполятор работает следующим образом.

Каждый из параллельных п каналов воспроизводит функцию времени неза5 висимо.от других. Синхронизация их

5

совместной работы осуществляется только для узлов, участвующих в обмене информацией с коммутатором 1 каналов. Работу каждого из каналов можно представить совокупностью двух одновременных процессов: про-; цесса вьщ еления и запоминания приращений воспроизводимых функций и процесса интегрирования приращений.

Каналы обслуживаются коммутатором 1 циклически с периодом, равным Т, таким образом, что первый канал обслуживается в течение интервала времени /tt , второй - Jtj, -третий - dtj и т.д., It, tj /Itj .. . ilt Эти интервалы времени следуют последовательно один за другим, причем k-й какал обслуживается в текущем интервале времени Т только в том случае, если с окончанием этого ин- тервала времени происходит изменение в k-M канале шага интерполирования. Если текущий шаг интерполирования для k-ro канала не оканчивается с окончанием данного интервала Т, а продолжается на следующий период Т, то Соответствующий интервал времени выдерживается без использования.

В случае необходимости обслуживания k-ro канала в течение времени ut осуществляется выдача из коммутатора 1 канала цифрового кода очередного значения формируемой функции Xi,(t),. преобразование его в соответствующее значение напряжения на выходе цифроаналогового поеобоазова- теля2, вычисление приращений dXj, Х|,..,, , на выходах сумматора 3 Канала и сумматоров 23 четных или нечетных цепочек k-го канала и запись приращений в соответствующие аналоговые запоминающие устройства 10, 11 и 25. Приращения функции X(t) для следующего (j+2)-ro щага интерполирования вычисляются и запоминаются в конце текущего (j+1)-ro шага интерполирования на интервале времени t е t jV,-(T-(k-1) 4tJ tj -()J, Ha этом интервале времени напряжение на выходе сумматора 3 канала равно инверт ированному значению алгебраической суммы напряжений на его первом, втором и третьем входах и изменяется в соответствии с вьфажением

dX(t)-Xfc(t,j) + x(t.) +

.у- ( t:tj ).f: -iilf с 1tr т,,.,, t-,- Ч

Jrl J-H Чm

5 (. |ZtJ.. ),. у --1 Н, Ц

,с. +

{

,,, t.),

(1)

где

Ч

О, М g , (M -l) , , (/7, g; Ci.i;., + C(,, (/-1), g /2, (, g. ,

К моменту времени , -CTrkJt) OHO достигает значения, обратного по знаку и пропорционального по величине первой разности функции X,(t):

X.(t.,, , t.,,)X(tj,)-X,(tj., ).

Слагаемые в выражении (1) соответствуют: X (t , ) величине, пропорциональной инвертированному напряжению на выходе цифроаналогового

преобразователя 2, x/(t.) +

к J

mm (j

.-(.15l/x,.. т t,j4i t/ Ч fJ

величине, пропорциональной инвертированному напряжению на выходе выходного интегратора 17 канала,

4X(t jj., , t-) - величине, пропорциональной инвертированному напряжению на выходе одного из аналоговых запоминающих устройств 10 или 11.

Первое приращение функции ) на интервале времени t ;, , t J хранится до окончания (j+1)-ro шага интерполирования, длительность которого равна Т, ,-4 в одном из аналоговых запоминающих устройств 10 или 11.

Второе и другие приращения функции X.(t) для (j+2)-ro шага интерполирования вычисляются через значение 4X((ty.j , tj+, ), полученное в конце интервала времени at,, и приращения функции Xi(t):

55

4x(t;.,, t.),....

соответствующие предыдущему (j+1)-My щагу интерполирования и хранящиеся до окончания (j+1)-ro шага интерполирования в аналоговых запоминающих

5

устройствах, 10 или 11 и в аналоговых запоминающих устройствах 25 четных или нечетных цепочек;

,(t.,

Ч

- J4,

x(t,j , tj,,) - ,,, tj),

,.(2)

Второе приращение функции X(t) , вычисляется на выходе сумматора 23 первой или второй цепочки и записывается в соответствующее аналоговое запоминакзщее устройство 25, Третье приращение функции вычисляется на выходе сумматора 23 третьей или четвертой цепочки и записывается в соответствующее аналоговое запоминаю- Dtee устройство 25.

Если в текущем интервале интерпоирования первое аналоговое запоминающее устройство 10 канала и анаоговые запоминающие устройства 25 нечетных цепочек заряжаются (т.е. запоминают приращения функции), то второе аналоговое запоминающее устройство 11 канала и аналоговые запоминающие устройства 25 четных цепочек и интеграторы 27 этих цепочек частвуют в интегриррвании. В следуюем интервале интерполирования их ункции изменяются: второе аналоговое запоминающее устройство 11 канала и аналоговые запоминающие устройства 25 четных цепочек заряжаются, а первое аналоговое запоминающее стройство 10 канала и аналоговые запоминающие устройства 25 нечетных цепочек и интеграторы 27 этих цепочек участвуют в интегрировании

Формирование и запоминание приращений функции ) выполняется в следующей последовательности. Пусть, например, в процессе интегрирования ((j+l)-u шаг интерполирования длительностью ) участвует второе аналоговое запоминающее устройство 11 канала и четные цепочки. Тогда в течение времени от начала (з 1)го шага интерполирования до момента окончания обслуживания (k-l)-ro интерполятора в k-M интерполяторе замкнуты ключ 7-, ключи 28 нечетных . цепочек и ключ 9. Остальные ключи k-ro интерполятора разомкнуты. В моменты времени t ty (k-1)dtj замыкаются на время лt , ключ 4, подключая вход первого аналогового заминающего устройства 10 канала к

615886

выходу сумматора 3, и ключи 24 нечетных цепочек, подключая входы аналоговых запоминающих устройств 25 нечетных цепочек к выходам соответ5 ствующих сумматоров 23..Одновременно с этим с первой группы выходоы 41 коммутатора 1 каналов на входы циф- роаналогового преобразователя 2 поступает цифровой код значения функtO ции Xj(t jVj ) . С выхода цифроаналого- вого преобразователя 2 соответствующее значение аналогового напряжения поступает на первый вход сумматора 3 k-ro интерполятора, на второй его

15 вход подается напряжение с выхода выходного интегратора 17, а на третий - с выхода сумматора 20 канала. Напряжение, вычисленное в соответствии с выражением (1), с выхода

20 сумматора 3 через открытый ключ 4 подается на вход аналогового запоминающего устройства 10 и в течение интер0

5

0

вала времени t запоминается. Напряжения, пропорциональные второму

5 и другим приращениям функции Xj((t), вычисленные в соответствии с (2), с выходов сумматоров 23 через открытые ключи 24 подаются на входы соответствующих аналоговых запоминающих устройств 25 нечетных цепочек и в течение этого же интервала времени Jtj запоминаются в них. После окончания интервала времени Jt в k-м канале размыкаются ключи 24 нечетных цепочек и ключ 4 канала, а ключ 18 замыкается. Начинается обслуживание (k+1)-ro интерполятора.

После ТОГО, как закончится в k-м интерполяторе (з+1)-й щаг интерполирования, на выходах k-1 блока 21 уп- равления изменяется цифровой код и устанавливаются значения сопротивлений цифровых управляемых сопротивлений 15,16 и 22, определяющие ве5 личину (j+2)-ro шага интерполирования, т.е. Т 1 -2 Одновременно с этим ключ 7, ключи 28 нечетных цепочек, ключ 9 и 18 размыкаются и замыкаются ключи 6,8 и ключи 28 четных цепочек. Первое аналоговое запоминающее устройство 10 канала и нечетные цепочки переходят в состояние формирования выходного сигнала - в цикл интегрирования, а четные цепочки вместе с аналоговым запоминающим устройством 11 канала - в состояние подготовки к работе. Функция ) на выходе k-ro канала на интервале времени t E(t j, , tj + i) формируется

0

5

в соответствии с интерполяционным полиномом Ньютона порядка т:

) ,,)

( ..)«i/x,.,,. I-T Т.ц, j.a (/.5 -

Блок управления 21 работает следующим образом.

В блоке длительность задержки элемента 61 задержки составляет небольшую долю от длительности &t и одинакова для всех блоков управления. Длительность задержки элемента 62 задержки различна для разных блоков 21 управления и такова, что ,обес печивает формирование на ее выходе сигнала, сдвинутого относительно тактового сигнала на входе 37 для блока управления первого канала на величину t, для блока второго канала - на величину 2 ut, для блока k-ro канала - на величину k /it, для блока п-го канала - на величину . В начальном состоянии в блоке управления первого канала регистр- счетчик 66 содержит код первого шага интерполирования (00...01), триггер 43 в нулевом состоянии (на выходе 33 единичный сигнал-ключ 18 замкнут) триггер 4 в единичном состоянии (на выходе 31 нулевой сигнал, а на выходе 32 единичный сигнал - ключи 6 и 8 и разрядные ключи 28 четных цепочек разомкнуты, а ключи 7 и 9 и разрядные ключи 28 третьей и других нечетных цепочек замкнуты), триггеры 44 и 45 находятся в единичном состоянии, в блоке управления п-го канала регистр-счетчик 66 содержит код первого шага интерполирования Т f, , (00... 11), триггер 43 в нулевом состоянии (на выходе 33 единичный сигнал - ключ 18 замкнут) триггер 46 в единичном состоянии (на в)1ходе 31 нулевой сигнал, а на вьпсоде 32 единичньй сигнал - ключи 6 и 8, разрядные ключи 28 четньк цепочек разомкнуты, а ключи 7 и 9 и разрядные ключи 28 третьей и других нечетных цепочек замкнуты), триггеры 44 и 45 находятся в единичном состоянии. Пусть, кроме того, на выходе 38 первого канала достигнуто напряжение X , а в аналоговых за- поминаювщх устройствах 10 канала и 25 п-ервой и других нечетных цепочек запомнены приращения 4 X , , й х,,..., ,, функции X(t) для

первого интервала интерполирования Т , на выходе 38 п-го канала достигнуто напряжение ,а в аналого- вых запоминающих устройствах 10 канала и 25 первого и других нечетных цепочек запомнены приращения , ,;, .. ., функции X(t) для первого интервала интерполирова10 ния Т .

.....-..,

Первый тактовый сигнал первого и п-каналов с входов 37, поступая через элементы ИЛИ 55 и 56 одновременно на информационный и синхронизи15 рующий входы триггеров 43, устанавливает их в единичное состояние - нулевые выходы 33 этих триггеров управляют размыканием ключей 18 всех каналов. Этот же тактовый сигнал,

20 пройдя элементы И 47, открывает узлы элементов И 65, через которые коды Т. и 1 . из регистров счетчиков 66

f П| 7

записываются в регистры 63, на выходах 34 блоков 21 соответствующих ка налов устанавливаются коды, определяющие значения сопротивленш цифровых управляемых сопротивлений 15, 16 и 22. Кроме того, первый тактовый сигнал с выходов элементов И 47, по- 30 ступая на счетный вход триггеров 46,

устанавливает их в нулевое состоя- . ние - управляющий сигнал снимается с выходом 32 и устанавливается на вы- ходах 31. В результате этого замыка35 ются ключи 6 и 8 и разрядные ключи 28 четных цепочек, а ключи 7 и 9 и разрядные ключи 28 нечетных цепочек размыкаются - в формировании выходных сигналов на шаге Т для первого

40 канала и шаге Т„ для п -го канала участвуют первые аналоговые запоминающие устройства 10 и первая и другие нечетные цепочки, а аналоговые запоминающие устройства 11 и четные

45 цепочки переключены в режим подготовки к работе.

Этот же тактовый сигнал, пройдя элемент 61 задержки, устанавливает в нуль триггеры 44 и 45, а также,

50 пройдя элементы И 54, вычитает из счетчиков 66 по единице, в результате в регистре-счетчике 66 блока уп-, равления первого канала устанавлива- ется код 00...00, а в регистре-счет55 чике 66 блока управления п-го канала - код 00... 10. После окончания сигнала на выходе элемента 61 задержки элемент И 51 блока управления первого канала открывается единичным

сигналом на выходе элемента НЕ 58 и единичным сигналом на выходе элемента НЕ 60 (так как на вЕяходе элемента ИЛИ 57 нуль), и триггер А5 этого блока управления устанавливается в единичное состояние. В блоке управления п-го канала элемент И 51 (после окончания сигнала на выходе элемента 61 задержки) закрыт нулевым сигналом на выходе элемента НЕ 60 (так как код регистра-счетчика 66 в этом канале не нулевой и на выходе элемента ИЛИ 5 единица) и триггер 45 остается в нулевом состоянии,

Поэтому в первом канале сигнал с выхода элемента 62 задержки проходит через элемент И 50 (открытый . единичным состоянием триггера 45 и нулевым состоянием триггера 44) и формирует (в интервале времени /),t, ) на выходе 40 сигнал запроса информации. Сигнал запроса информации элемента поступает на управляющий вход коммутатора каналов, который формирует .синхросигнал на; входе 39 блока управления первого канала и вместе с сиг- налом на выходе .этого канала открывает элемент И 49 и с его выхода- устанавливает триггер 44 в единичное состояние. В результате перехода триггера 44 из нулевого в единичное состояние элемент И 50 в первом канале закрывается (снимая запрос информации с выхода 40) и открывается элемент И 48. Сигнал с выхода последнего открывает блок 64 элементов И,. через который код Т поступает с входов 42 в регистр-счетчик 66, и, пройдя через элемент И 52 (открытый нулевым состоянием триггера 46), формирует на выходе 30 управляющий сигнал, устанавливающий замкнутое состояние ключа 5 канала и ключей 24 четных цепочек. Под действием этого сигнала до окончания интервала времени t, напряжение сформиро- - ванное на выходе входного суммато- . ра 3 (первое приращение Х,.) через замкнутый ключ 5 запоминается в аналоговом запоминающем устройстве 11, а напряжения, сформированные на выходах сумматоров 23 (приращения Х J ,,, . ,), через соответствующие замкнутые ключи 24 запоминаются в аналоговых запоминающих устройствах 25 четных цепочек. После окончания сигнала на выходе элемента 62 . задержки (оканчивается интервал вре

61588 О

мени dt ), сигнал с выходов 30 снимается, соответствующие ключи 5 и 24 размыкаются, а задний фронт сигнала на выходе элемента И 48 устанавливает триггер 43 в нулевое состо- яние, поступая через элемент НЕ 59 и элемент ИЛИ 55 на синхронизирующий вход, а через элемент ИЛИ 56 - ТО на его информационный вход. На выходе 33 блока управления первого канала устанавливается единичный сигнал, управляющие замыканием ключа 18. Интервал времени t, выделенный для

15 обслуживания п-го канала, в первом цикле Т остается неиспользованным, так как данный интервал интерполирования Т продолжается на следующий цикл . (код регистра-счетчика 66

20 не уменьшен до нуля, триггер 4.3 остался в единичном состоянии, а триггеры 44, 45 и 46 остались в нулевом состоянии, сигнал запроса информации на выходе 40 не сформирован),

25 Второй тактовый сигнал с входа 37 устанавливает так же триггер 43 блока управления первого канала в ;; единичное состояние (в результате ключ 18 в этом канале размыкается) и,

30 пройдя элемент И 47 (открытый единичным состоянием триггера 45), с его выхода открывает блок 65 элементов И, через который код (00.-, ,.10) шага

1,2

записывается в регистр 63 (уста- на1вливающий на выходах 34 соответствующий код, управляющий изменением сопротивлений цифровых управляемых сопротивлений 15, 16 и 22), а также, поступая на счетный вход триггера 46, переводит его из нулевого в единичное состояние (изменение состояний выходов 31 и 32, размыкает ключи 6 и 8 и ключи 28 четных цепочек и замыкает ключи 8 и 9 и ключи 28 не- четных цепочек), В результате в первом канале в течение интервала времени выходная функция X/t) формируется из приращений этой функции, запомненных в предыдущем цикле в аналоговом запоминающем устройстве 11 канала и в аналоговых запоминающих устройствах 25 четных цепочек. В п-м канале второй тактовый сигнал через элемент И 4 не проходит, так как он закрыт нулевым состоянием триггера 45. Кроме того, во всех каналах (в том числе в первом и п-м) второй тактовый сигнал проходит через соответствующий элемент 61 за

1. 13

держки и устанавливает в нулевое состояние триггеры 44 и 45, а также проходит через соответствующий элемент И 54 на вход вычитания соответствующих регистров-счетчиков 66, уменьшая их содержимое на единицу. В результате этого в регистрах-счетчиках 66 первого и п-го каналов устанавливаются соответственно коды 00...01 и 00...01, Так как эти коды не равны нулю, то во втором цикле интервалы времени Jt, и tn остаются неиспользованными - в конце этого цикла триггеры 43 остаются в единичном состоянии, триггеры 45 и 46 - в нулевом.

Коммутатор каналов работает следующим образом.

С информационных входов 36 начальные адреса массивов дискретных - значений соответствующих функций записываются в соответствующие регистры 69. На соответствующий управ- ляющий вход 40 шифратора 71 поступает из блока 21 управления сигнал запроса информации, который устанавливает на его выходе состояние, определяющее подключение через мультиплексор 68 выходов соответствующих регистра 69 и счетчика 70 адреса к входам блока 67 памяти. Одновременно с этим этот же сигнал запроса информации увеличивает содержимое выбранного счетчика 70 адреса на единицу. Б результате этого на первой 41 и второй 42 группах выходов блока памяти устанавливаются коды очередных координат для следующего интервала интерполирования - ордината X j и абсцисса Т.

Сигнал 3a. поступает на вход элемента ИЛИ 72, который совместно с элементом 73 задержки является формирователем синхросигналов, которые с выхода 39 поступают в блок управления .

В дальнейшем интерполятор продолжает работать аналогично описанному.

Формула изобретения

1. Многоканальный интерполятор функций, содержащий цифроанапоговый преобразователь и п каналов, каждый из которых содержит первый и второй сумматоры нелинейности, входной сумматор, первый вход которого соединен

8

с выходом цифроаналогового преобразователя, а выход через первый и второй ключи подключен к входам соответственно первого и второго аналоговых

запоминающих устройств, выходы которых соединены соответственно с информационными входами третьего и четвертого ключей, пятый и шестой ключи,

выходной сумматор, интегратор 2т цепочек, состоящих каждая из сумматора, выход которого через ключ соединен с входом аналогового запоминающего устройства, интегратор, между

входом и выходом которого подключен разрядный ключ, входы первого сумматора нелинейности соединены соответственно с выходом интегратора первой цепочки и с выходами аналоговых запоминающих устройств всех нечетных цепочек, входы второго сумматора нелинейности подключены соответственно к выходу интегратора второй цепочки и к. выходам аналоговых запоминающих устройств всех четных цепочек, выходы первого и второго сумматоров нелинейности соответственно через пятый и шестой ключи подсоединены к первому входу выходного сумматора,

к второму входу которого подключены выходы третьего и четвертого ключей, выход входного сумматора соединен с первыми входами сумматоров первой и второй цепочек, причем второй вход сумматора первой цепочки подключен к выходу второго запоминающего устройства, а второй вход сумматора второй цепочки подключен к выходу первого аналогового запоминающего устройства, входы сумматора каждой 21-й (,...,т) цепочки соединены с выходом сумматора 2(1-1)-и цепочки и с выходом аналогового запоминающего устройства (21-3)-и цепочки, а входы сумматора каждой (21-1)-и цепочки (,...,т) соединены с выходом сумматора (21-3)-и цепочки и с выходом аналогового запоминающего устройства (21-2)-й цепочки, о т- личающийся тем, что, с

целью расширения функциональных возможностей за счет формирования функций времени с переменным шагом ин- терполирования, введены коммутатор каналов, а в каждый канал введены блок управления, первое и второе цифровые управляемые сопротивления, интегратор, сумматор, в каждую цепочку канала введены цифровое управляемое сопротивление и дополнительный сумматор, выход которого соединен через цифровое управляемое сопротивление с входом интегратора этой цепЬчки, входы дополнительных сумматоров четных депочек подключены к выходу интегратора последующей четной цепочки и к выходам аналоговых запоминаюпщх устройств этой и всех последующих четных цепочек, входы дополнит ельных сумматоров нечетных цепочек подключены к выходу интегратора последующей нечетной цепочки и к выходам аналоговых запоминающих устройств этой и всех последующих нечетных цепочек, выход выходного сумматора через первое и второе цифровые управляемые сопротивления подключены соответственно к входу выходного интегратора, выход которого является выходом канала и соединен с вторым входом входного сумматора канала, и к входу интегратора канала, выход которого соединен с первым входом -сумматора канала, второй вход которого соединен с вто- -рым входом выходного сумматора, выход сумматора канала соединен с третьим входом входного сумматора канала, вход цифроаналогового преобразователя соединен с первой группой выходов коммутатора каналов, информационные входы которого являются информационными входами интерполятора, блок управления каждого канала содержит четыре триггера, регистр, регистр- счетчик, два блока элементов И, два элемента задержки, восемь элементов И, три элемента НЕ и три элемента ИЛИ, причем тактовый вход интерполятора подключен к первым входам первого элемента. И, первого и второго элементов ИЛИ, выходы каждого из которых соединены с соответствующими входами первого триггера, выход которого соединен с управляющим входом разрядного ключа интегратора канала, тактовый вход интерполятора соединен также через первый элемент задержки с нулевыми входами второго и третьего триггеров, с входом первого элемента НЕ и с входом второго элемента задержки, выход ко - торого подключен к первым входам второго, третьего и четвертого.элементов И, выходы первого и третьего элементов НЕ соединены с входами пятого элемента И, выход которого под-

5

0

ключей к единичному входу третьего триггера, единичный выход которого соединен с вторыми входами первого, второго и четвертого элементов И, второй вход третьего элемента И соединен с выходом синхросигнала коммутатора каналов, а выход подключен к единичному входу второго триггера, единичный выход которого соединен с третьим входом второго элемента И, а нулевой выход подключен к третьему входу четвертого элемента И, выход которого соединен с соответствующим входом группы управляющих входов коммутатора каналов, информационные входы первого блока элементов И подключены к второй группе выходов коммутатора каналов, а управляющий вход соединен с первыми входами шестого и седьмого элементов И, вторым входом второго элемента ИЛИ и через второй элемент НЕ подсоединен к второму входу первого элемента ИЛИ, выходы 5 первого блока элементов И соединены с информационными входами регистра- счетчика, вход вычитания которого соединен с выходом восьмого элемента И, первый вход которого соединен с выходом первого элемента задержки, выходы регистра-счетчика через третий элемент ИЛИ подключены к входу третьего элемента НЕ и к второму входу восьмого элемента И, а через второй блок элементов И соединены с входами регистра, выходы которого соединены с цифровыми входами цифровых управляемых сопротивлений канала и всех цепочек, выход первого элемента И соединен с управляющим входом второго блока элементов И и со счетным входом четвертого триггера, первый выход которого соединен с управляющими входами четвертого, шестого

0

5

0

ключей канала, разрядных ключей нечетных цепочек и вторым входом седьмого элемента И, выход которого соеинен с управляющими входами первого ключа канала и ключей нечетных цепочек, а второй выход триггера соединен с управляющими входами третьего и пятого ключей канала, разрядных ключей четных цепочек и вторым входом шестого элемента И, выход которого соединен с управляющими входами второго ключа канала и ключей четных цепочек.

2. Интерполятор по п. 1, отличающийся тем, что комму15136

татор каналов содержит блок памяти, мультиплексор, шифратор, элемент ИЛИ, элемент задержки, счетчики адреса, регистры адреса, входы которых являются информационными входами коммутатора каналов, а выходы вместе с выходами счетчиков адреса соединены с информационными входами мультиплексора, управляющий вход которого подсоединен к выходу шифратора, входы которого являе ся управляющими

1588 6

входами коммутатора каналов и соединены с входами счетчиков адреса и входами элемента ИЛИ, выход которого через элемент задержки соединен с выходом синхросигналов коммутатора каналов, выходы мультиплексора подключены к адресным входам блока памяти, первая и вторая группы вы10 ходов которого являются п ервой и второй группами выходов коммутатора каналов.

Фиг г

J6 0

Фиг.

yw w- 7

04(9/

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1986 |

|

SU1345217A1 |

| Линейный интерполятор | 1982 |

|

SU1042038A1 |

| Интерполятор | 1978 |

|

SU765821A1 |

| Генератор функций | 1980 |

|

SU962995A1 |

| Линейный интерполятор | 1980 |

|

SU883925A1 |

| Интерполятор | 1981 |

|

SU1061157A2 |

| Устройство для многоканального интерполирования функций | 1986 |

|

SU1377878A1 |

| Интерполятор | 1981 |

|

SU991445A1 |

| Интерполятор | 1973 |

|

SU480094A1 |

| Линейный интерполятор | 1978 |

|

SU698012A1 |

Изобретение относится к. вычислительной технике и может быть использовано для воспроизведения функций при выводе информации на электронно-лучевые трубки, графопостроители и исполнительные механизмы в управляющих вычислительных машинахj а также в качестве программируемого п W со Oi сл 00 00 Pue.l

Редактор ИоНиколайчук

Составитель Г.Осипов Техред А.Кравчук

Заказ 6293/50

Тираж 671 . Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор О.Кравцова

| Генератор функций | 1980 |

|

SU962995A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Интерполятор | 1981 |

|

SU1057967A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| да | |||

Авторы

Даты

1987-12-23—Публикация

1986-03-03—Подача