Изобретение относится к автоматике, а именно к аналого-цифровым интегрирующим устройствам, обеспечивающим гальваническое разделение входного и выходного аналоговых сиг налов.

Целью изобретения является повышение точности интегрирования и упрощение устройства.

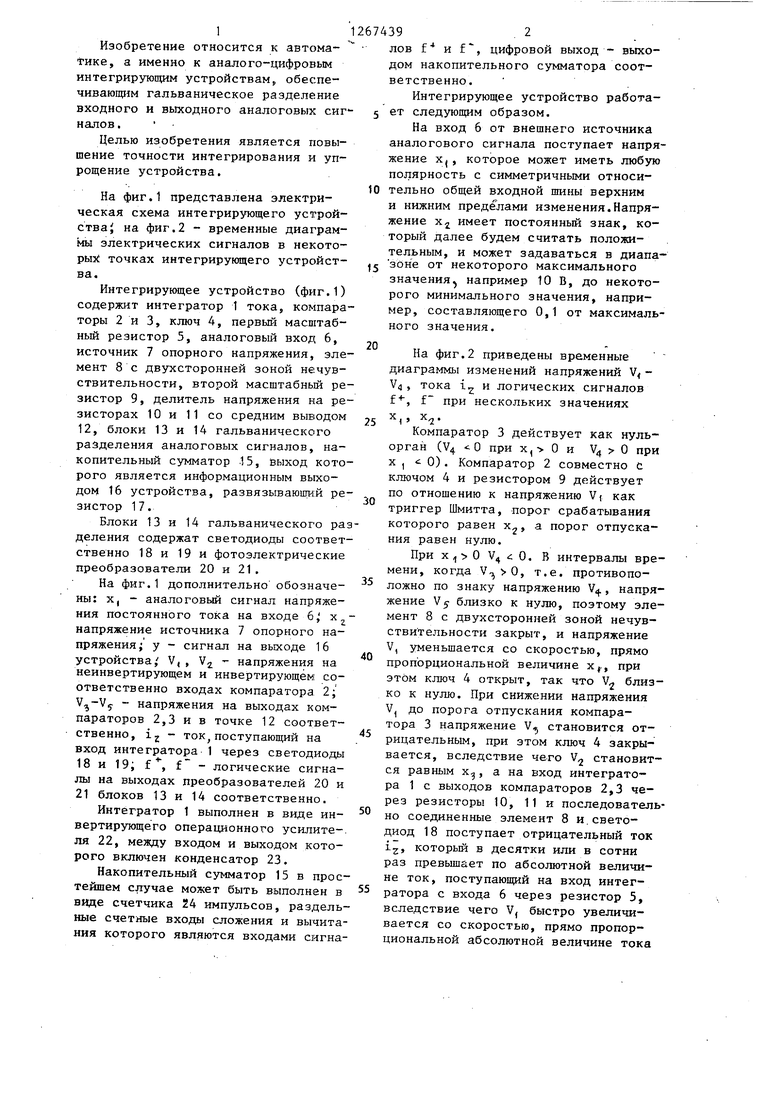

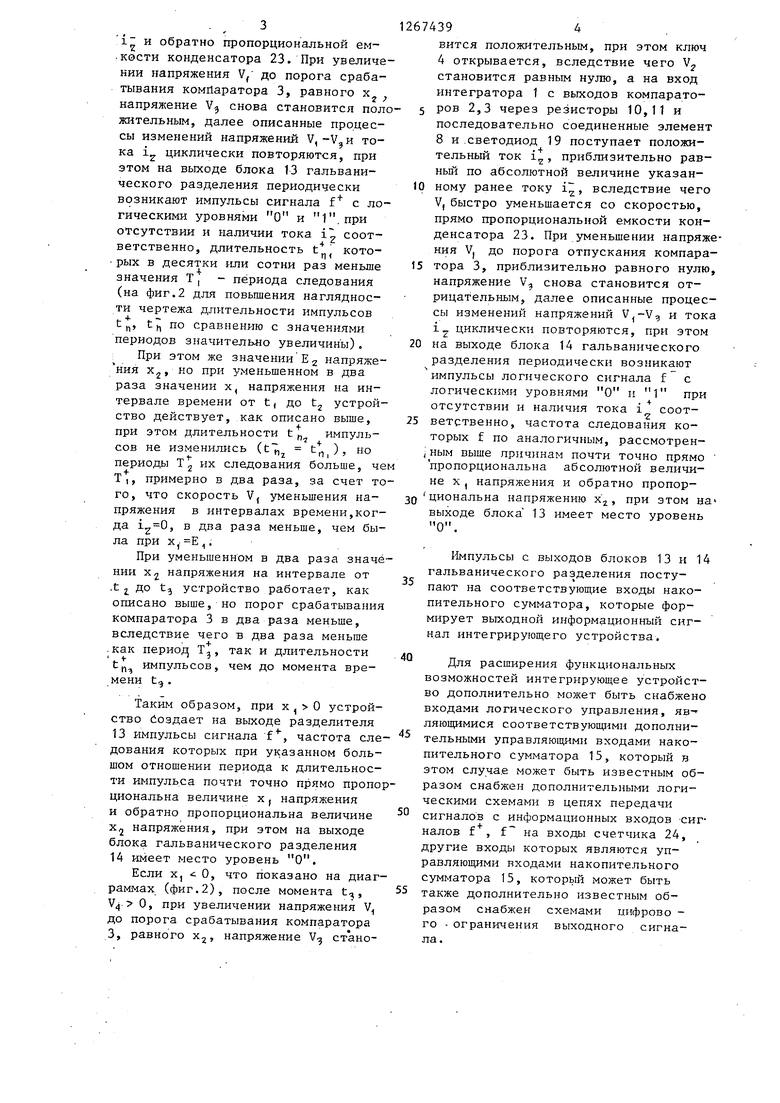

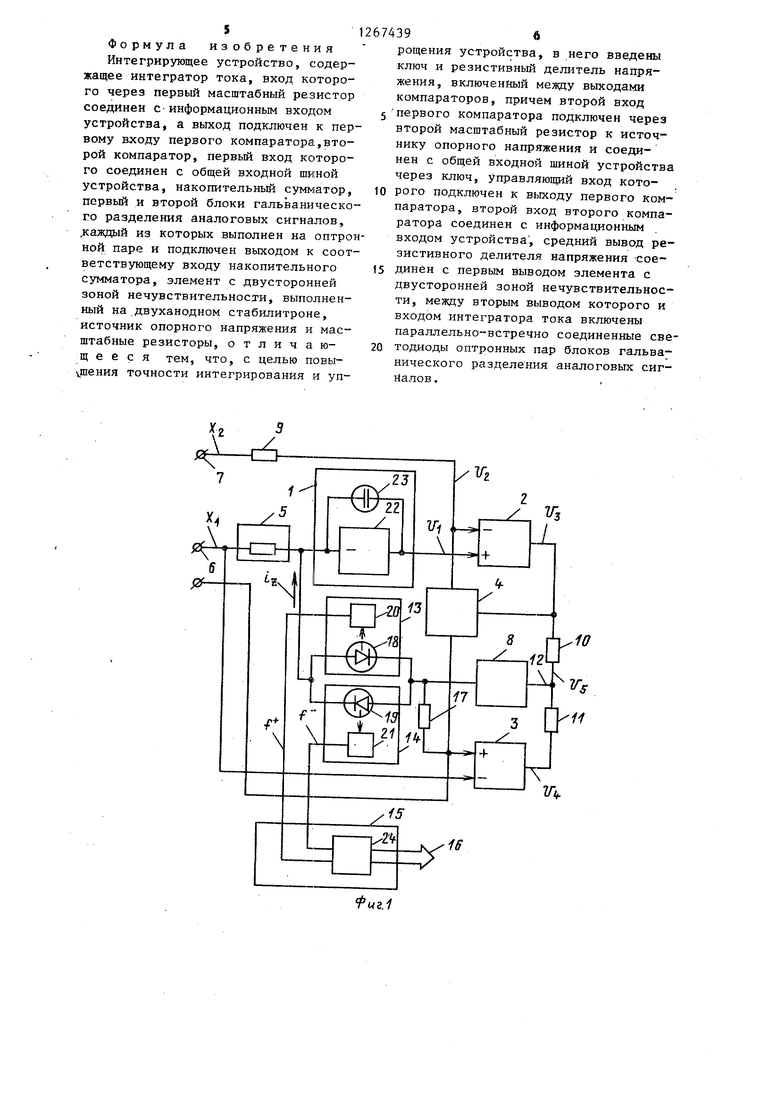

На фиг.1 представлена электрическая схема интегрирующего устройства j на фиг.2 - временные диаграммы электрических сигналов в некоторых точках интегрирующего устройства.

Интегрирующее устройство (фиг.1) содержит интегратор 1 тока, компараторы 2 и 3, ключ 4, первый маспгтабный резистор 5, аналоговый вход 6, источник 7 опорного напряжения, элемент 8с двухсторонней зоной нечувствительности, второй масштабный резистор 9, делитель напряжения на резисторах 10 и 11 со средним выводом 12, блоки 13 и 14 гальванического разделения аналоговых сигналов, накопительный сумматор .15, выход которого является информационным выходом 16 устройства, развязываюш:н;й резистор 17.

Блоки 13 и 14 гальванического раделения содержат светодиоды соответственно 18 и 19 и фотоэлектрические преобразователи 20 и 21.

На фиг.1 дополнительно обозначены: X, - аналоговый сигнал напряжения постоянного тока на входе 6, х напряжение источника 7 опорного напряжения; у - сигнал на выходе 16 устройства, V, , Vj - напряжения на неинвертирующем и инвертирующем соответственно входах компаратора 2; - напряжения на выходах компараторов 2,3 и в точке 12 соответственно, ij токJпоступающий на вход интегратора 1 через светодиоды 18 и 19; f , f - логические сигналы на выходах преобразователей 20 и 21 блоков 13 и 14 соответственно.

Интегратор 1 выполнен в виде инвертирующего операционного усилителя 22, между входом и выходом которого включен конденсатор 23.

Накопительный сумматор 15 в простейшем случае может быть выполнен в виде счетчика 24 импульсов, раздельные счетные входы сложения и вычитания которого являются входами сигналов f и f, цифровой выход - выходом накопительного сумматора соответственно.

Интегрирующее устройство работа-

ет следующим образом.

На вход 6 от внешнего источника аналогового сигнала поступает напряжение Х(, которое может иметь любую полярность с симметричными относительно общей входной шины верхним и нижним пределами изменения.Напряжение Xj имеет постоянный знак, который далее будем считать положительным, и может задаваться в диапазоне от некоторого максимального значения например 10 В, до некоторого минимального значения, например, составляющего 0,1 от максимального значения.

На фиг.2 приведены временные диаграммы изменений напряжений , тока г и логических сигналов , f при нескольких значениях

1 1

Компаратор 3 действует как нульорган (V4 0 при х, О и V О при X , 0). Компаратор 2 совместно с ключом 4 и резистором 9 действует по отношению к напряжению V( как триггер Шмитта, порог срабатывания которого равен х, а порог отпускания равен нулю.

При х О V 0. В интервалы времени, когда V- О, т.е. противоположно по знаку напряжению V, напряжение Vj близко к нулю, поэтому элемент 8 с двухсторонней зоной нечувствительности закрыт, и напряжение V, уменьшается со скоростью, прямо пропорциональной величине Xj., при этом ключ 4 открыт, так что V близко к нулю. При снижении напряжения V до порога отпускания компаратора 3 напряжение V,) становится отрицательным, при этом ключ 4 закрывается, вследствие чего V становится равным х, а на вход интегратора 1 с выходов компараторов 2,3 через резисторы 10, 11 и последователно соединенные элемент 8 и.светодиод 18 поступает отрицательный ток i, который в десятки или в сотни раз превышает по абсолютной величине ток, поступающий на вход интегратора с входа 6 через резистор 5, вследствие чего V, быстро увеличивается со скоростью, прямо пропорциональной абсолютной величине тока i и обратно пропорциональной ем.К0СТИ конденсатора 23. При увеличе нии напряжения V, до порога срабатывания комйаратора 3, равного х напряжение V снова становится пол жительным, далее описанные процессы изменений напряжений V,-V,и тока i циклически повторяются, при этом на выходе блока 13 гальванического разделения периодически возникают импульсы сигнала f с ло гическими уровнями О и Г.при отсутствии и наличии тока i ветственно, длительность t ши сотни раз меньше рых в десятки значения Т , - периода следования (на фиг.2 для повышения наглядности чертежа длительности импульсов t, t по сравнению с значениями периодов значительно увеличины). При этом же значении Е2 напряже ния Х-, но при уменьшенном в два раза значении х, напряжения на интервале времени от t, до tj устрой ство действует, как описано выше. этом длительности t импуль(t ц, - , ) изменились , „., периоды Т 2 их следования больше, ч Т,, примерно в два раза, за счет т го, что скорость V, уменьшения напряжения в интервалах времени,когда , в два раза меньше, чем была при X,. Е,. При уменьшенном в два раза значе НИИ Х2 напряжения на интервале от .t до t устройство работает, как описано выше, но порог срабатывания компаратора 3 в раза меньше, вследствие чего в два раза меньше .как перио 5 Т, так и длительности tjj.j импульсов, чем до момента времени tci. Таким образом, при х , О устройство Создает на выходе разделителя 13импульсы сигнала , частота сле дования которых при указанном большом отношении периода к длительности импульса почти точно прямо пропо циональна величине х , напряжения и обратно пропорциональна величине х напряжения, при этом на выходе блока гальванического разделения 14имеет место уровень О, Если X, О, что показано на диаг раммах (фиг.2), после момента t, V О, при увеличении напряжения V, до порога срабатывания компаратора 3, равного Xj, напряжение V стано394вится положительным, при этом ключ 4 открывается, вследствие чего V становится равным нулю, а на вход интегратора 1 с выходов компараторов 2,3 через резисторы 10,11 и последовательно соединенные элемент 8 и .светодиод 19 поступает положительный ток i, приблизительно равньш по абсолютной величине указанному ранее току i, вследствие чего V, быстро уменьшается со скоростью, прямо пропорциональной емкости конденсатора 23. При уменьшении напряжения V| до порога отпускания компаратора 3, приблизительно равного нулю. напряжение V снова становится отрицательным, далее описанные процессы изменений напряжений и тока i циклически повторяются, при этом на выходе блока 14 гальвагпгческого разделения периодически возникают импульсы логического сигнала f с логическими уровнями О и 1 при отсутствии и наличия тока i соответственно, частота следования которых f по аналогичным, рассмотренным выше причинам почти точно прямо пропорциональна абсолютной величине X , напряжения и обратно пропор4 ° - напряжению Xj, , при этом на13 имеет место уровень выходе блока О. Импульсы с выходов блоков 13 и 14 гальванического разделения поступают на соответствующие входы накопительного сумматора, которые формирует выходной информационный сигнал интегрирующего устройства. Для расширения функциональных возможностей интегрирующее устройство дополнительно может быть снабжено входами логического управления, HB- ляющимися соотБетствуюш 1ми дополнительными управляющими входами накопительного сумматора 15, который в этом случае может быть известным образом снабжен дополнительными логическими схемами в цепях передачи сигналов с информационных входов -сигналов f, f на входы счетчика 24, другие входы которых являются управляющими входами накопительного сумматора 15, который может быть также дополнительно известным образом снабжен схемами цифрово - го ограничения выходного сигнала.

Формула изобретения Интегрирующее устройство, содержащее интегратор тока, вход которого через первьй масштабный резистор соединен синформационным входом устройства, а выход подключен к первому входу первого компаратора,второй компаратор, первьй вход которого соединен с общей входной шиной устройства, накопительньй сумматор, первый и второй блоки гальванического разделения аналоговых сигналов, .каждый из которых выполнен на оптроной паре и подключен выходом к соответствующему входу накопительного сумматора, элемент с двусторонней зоной нечувствительности, выполненный на.двуханодном стабилитроне, источник опорного напряжения и масштабные резисторы, отличающееся тем, что, с целью повыvшeния точности интегрирования и упощения устройства, в него введены ключ и резистивный делитель напряжения, включенный между выходами компараторов, причем второй вход первого компаратора подключен через второй масштабный резистор к источнику опорного напряжения и соединен с общей входной шиной устройства через ключ, управляющий вход которого подключен к выходу первого компаратора, второй вход второго компаратора соединен с информационным . входом устройства, средний вывод резистивного делителя напряжения -соединен с первым выводом элемента с двусторонней зоной нечувствительности, между вторым выводом которого и входом интегратора тока включены параллельно-встречно соединенные светодиоды оптронных пар блоков гальванического разделения аналоговых сигНалов .

П

3 T7 T-g

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| Измерительный преобразователь активной мощности | 1989 |

|

SU1659890A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

| МНОГОЗОННЫЙ РАЗВЕРТЫВАЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ПЕРЕДАЧИ ЛОГИЧЕСКИХ ДАННЫХ ПО ОДНОПРОВОДНОЙ ЛИНИИ СВЯЗИ | 2001 |

|

RU2206922C2 |

| Преобразователь напряжения в частоту | 1982 |

|

SU1115222A2 |

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| Аналого-цифровой интегратор | 1980 |

|

SU866563A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1985 |

|

SU1242801A1 |

| Интегратор | 1982 |

|

SU1062726A1 |

Изобретение относится к области вычислительной техники. Целью изобретения является повышение точности интегрирования и упрощение. Входной сигнал интегрируется интегратором тока и сравнивается на первом компараторе с двумя уровнями опорных напряжений,при этом один из компараторов действует как нуль-орган, а другой компаратор совместно с ключом и резистором действует как триггер Шмитта. Интегрирующее устройство содержит также элемент с двухсторонней зоной нечувствительности, делитель напряжения на резисторах, блоки гальванического разделения и накопительный сумматор. Частота следования импульсов на выходе разделителей прямо пропорциональна аналоговому сигналу на входе устроргства и обратно пропорциональна напряжению источника опорного напряжения. Импульсы К) с выходов блоков гальванического а разделения поступают на соответст-вующие входы накопительного суммато s ра, который формирует выходной сиг нал интегрирующего устройства. 2 йл. GO СО

| Пневматический прибор для заправки нити в челнок | 1924 |

|

SU670A1 |

| Техническое описание и инструкция по эксплуатации, 1981 | |||

| Блоки динамических преобразователей БДП-П, БДП-Ш, блоки прецизионного интегрирования БПИ-П, БПИ-Ш, Б11И-21 | |||

| Техническое описание и инструкция по эксплуатации ОЯа | |||

| Пневматический прибор для заправки нити в челнок | 1924 |

|

SU670A1 |

| Ивано-Франковский приборостроительный завод, 1976 | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Схема электрическая принципиальная гЕЗ | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| Московский завод тепловой автоматики, 1982. | |||

Авторы

Даты

1986-10-30—Публикация

1983-10-18—Подача