Изобретение относится к преобразовательной технике и предназначено для управления компенсаторами реактивной мощности различных типов.

Известны компенсаторы реактивной мощности, подавляющие реактивные мощности сдвига и искажения и состоящие из резонансных последовательных фильтров и индуктивного регулируемого источника реактивной мощности [1] . Для управления такими компенсаторами используются устройства фазового управления.

Такие компенсаторы не подавляют неканонические гармоники сети.

Ближайшим по технической сущности к предлагаемому является устройство для управления компенсатором реактивной мощности, построенном на базе автономного инвертора, генерирующего в сеть ампердобавку, дополняющую ток системы до эталонной синусоидальной формы [2] . Основную часть устройства составляет вычислитель активной мощности, состоящий из двух датчиков (тока и напряжения), умножителя и интегратора.

Недостатком прототипа является низкая точность, связанная с дрейфом аналоговых умножителей, а при цифровой реализации - с большими затратами времени на умножение и снижением числа замеров на периоде сети.

Целью изобретения является повышение точности.

Цель достигается тем, что цифровое устройство для управления компенсатором реактивной мощности, содержащее два датчика, умножитель и интегратор, снабжено двумя датчиками знака, полусумматором, компаратором и двумя конъюнкторами, оба датчика выполнены в виде датчиков модулей, интегратор - в виде реверсивного счетчика, а умножитель состоит из преобразователя напряжения в частоту, связанного через первый управляемый делитель частоты и непосредственно с блоком запрета, к выходу которого подключен второй управляемый делитель частоты, аналого-цифрового преобразователя, подключенного к преобразователю кодов, к выходам которого подключены управляющие входы обоих управляемых делителей частоты, причем к выходу первого датчика подключен вход преобразователя напряжения в частоту, а второй датчик связан с аналого-цифровым преобразователем, датчики знака связаны с полусумматором, прямой выход которого связан с первым входом первого конъюнктора, а инверсный выход - с первым входом второго конъюнктора, вторые входы обоих конъюнкторов подключены к выходу второго управляемого делителя частоты, выход первого конъюнктора связан с вычитающим входом реверсивного счетчика, а выход второго конъюнктора - с суммирующим входом реверсивного счетчика, установочный вход которого подключен к компаратору, при этом коды на выходе преобразователя имеют вид Кд2 - целая часть a/X, где Х - код на выходе преобразователя кодов, K =

=  , округленное до ближайшего целого, константа a>Хмакс.

, округленное до ближайшего целого, константа a>Хмакс.

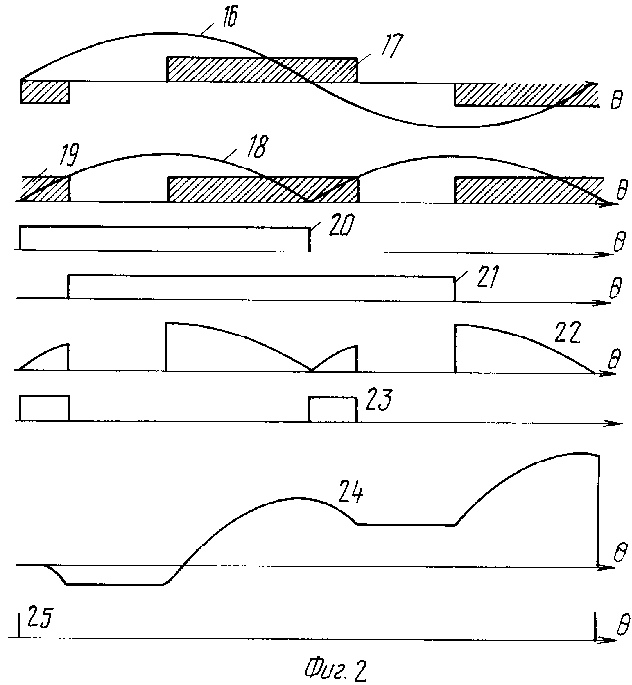

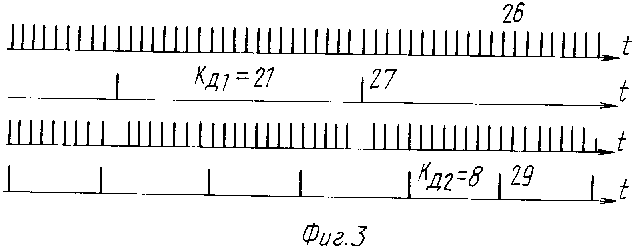

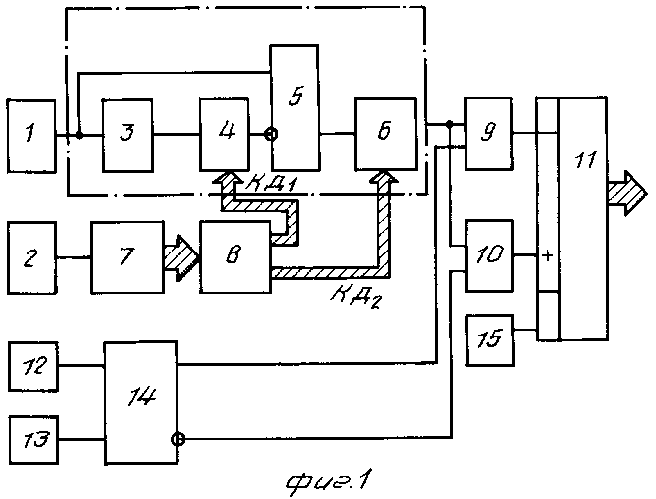

На фиг. 1 представлена структурная схема устройства; на фиг. 2 и 3 - временные диаграммы.

К выходу первого датчика 1 подключен преобразователь 3 напряжения в частоту, связанный с первым управляемым делителем частоты 4 и узлом запрета 5, к выходу которого подключен второй управляемый делитель частоты 6.

К второму датчику 2 через аналого-цифровой преобразователь 7 подключен преобразователь 8 кодов. Второй управляемый делитель частоты 6 подключен к конъюнкторам 9 и 10, выходы которых связаны с вычитающим и суммирующим входами реверсивного счетчика 11. Датчики 12 и 13 знака подключены к полусумматору 14, прямой и инверсный выходы которого связаны с входами конъюнкторов 9 и 10. К установочному входу реверсивного счетчика 11 подключен компаратор 15, связанный с питающей сетью.

На фиг. 2 приведены временные диаграммы: 16 - напряжение сети; 17 - ток сети; 18 - зависимость частоты на выходе преобразователя 3 напряжения в частоту; 19 - сигнал на выходе второго датчика 2; 20 - сигнал на выходе датчика 12 знака (знак напряжения); 21 - сигнал на выходе датчика 13 знака (знак тока); 22 - зависимость частоты на выходе второго управляемого делителя частоты 6; 23 - сигнал на выходе полусумматора 14; 24 - сигнал, записанный в реверсивном счетчике 11; 25 - сигнал на установочном входе реверсивного счетчика 11.

На фиг. 3 приведены временные диаграммы: 26 - импульсы на выходе преобразователя 3 напряжения в частоту; 27 - импульсы на выходе первого управляемого делителя частоты 4; 28 - импульсы на выходе узла запрета 5; 29 - импульсы на выходе второго управляемого делителя частоты 6.

Принцип действия устройства заключается в следующем. Первый датчик 1 фиксирует сигнал 18, пропорциональный модулю напряжения сети 16. Преобразователь 3 напряжения в частоту формирует на выходе импульсы 26 высокой частоты, частота которых пропорциональна мгновенному значению напряжения, эта же диаграмма 18 представляет зависимость частоты. Сигнал 19 на выходе второго датчика 2 пропорционален модулю тока сети 17. Этот сигнал преобразуется в цифровую форму Х.

На выходе второго управляемого делителя частоты 6 частота импульсов 29 пропорциональна произведению мгновенных значений датчиков 1 и 2, т. е. мгновенной мощности. Зависимость частоты приведена на диаграмме 22.

Число импульсов, поступающих на вход реверсивного счетчика 11 за единицу времени, пропорционально модулю мгновенной мощности. Знак мгновенной мощности фиксирует полусумматор 14 (диаграмма 23). В зависимости от знака работает либо суммирующий, либо вычитающий вход реверсивного счетчика 11, который выполняет функцию интегратора. К концу периода сети код в счетчике 11 пропорционален активной мощности.

Рассмотрим подробнее работу делителей частоты. Второй делитель частоты 6 делит частоту импульсов 26 в целое число раз Кд2. Если же коэффициент a/X нецелый, то первый управляемый делитель частоты из Кд1импульсов 26 выделяет один (диаграмма 27) и сигналом 27 блокирует прохождение импульсов через узел запрета 5. Результирующий коэффициент деления получает дробную часть, так как средняя частота импульсов на входе второго управляемого делителя частоты 6 несколько снижается.

Устройство может измерять также реактивную мощность, если на входе одного из датчиков включить дифференцирующее звено. При микропроцессорной реализации устройства широко используются БИС, что обеспечивает компактную реализацию устройства. Применение устройства позволяет снизить установленную мощность компенсаторов реактивной мощности и улучшить компенсацию в динамических режимах.

(56) Горбачев Г. Н. Промышленная электроника. - М. : Энергоатомиздат, 1988, гл. 8.

Супронович Г. Улучшение коэффициента мощности преобразовательных установок. - М. : Энергоатомиздат, 1985, с. 128-130.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления компенсатором реактивной мощности | 1991 |

|

SU1802390A1 |

| Способ формирования эталонного сигнала для управления компенсатором мощности искажения | 1991 |

|

SU1838867A3 |

| Источник квазисинусоидального напряжения | 1991 |

|

SU1800561A1 |

| Генератор опорного кода для микропроцессорной системы управления вентильного преобразователя | 1990 |

|

SU1758792A1 |

| Генератор опорного кода вентильного преобразователя | 1989 |

|

SU1674330A1 |

| Генератор опорного кода вентильного преобразователя | 1990 |

|

SU1818666A1 |

| Преобразователь угловых перемещений в код | 1982 |

|

SU1035627A1 |

| Цифровой измеритель симметричных составляющих трехфазной сети | 1982 |

|

SU1056081A1 |

| Преобразователь угловых перемещений в код | 1978 |

|

SU926703A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

Сущность изобретения: схема управления регулируемого источника реактивного тока выполнена в виде цифрового устройства. Оно включает в себя два датчика знака, умножитель, полусумматор, компаратор и два конъюктора. Оба датчика выполнены в виде датчиков модулей, интегратор - в виде реверсивного счетчика. Умножитель состоит из преобразователя напряжения в частоту, связанного через управляемый делитель частоты и непосредственно с блоком запрета, к выходу которого подключен второй управляемый делитель частоты, аналого-цифрового преобразователя, подключенного к преобразователю кодов, к выходам которого подключены входы обоих управляемых делителей частоты. Использование такой схемы позволяет повысить точность ее измерения в статических и динамических режимах, тем самым улучшив степень ее компенсации. 3 ил.

ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ КОМПЕНСАТОРОМ РЕАКТИВНОЙ МОЩНОСТИ, содержащее два датчика, умножитель и интегратор, отличающееся тем, что, с целью повышения точности, оно снабжено двумя датчиками знака, полусумматором, компаратором и двумя конъюнкторами, оба датчика выполнены в виде датчиков модулей, интегратор выполнен в виде реверсивного счетчика, а умножитель состоит из преобразователя напряжения в частоту, связанного через первый управляемый делитель частоты и непосредственно с блоком запрета, к выходу которого подключен второй управляемый делитель частоты, аналого-цифрового преобразователя, подключенного к преобразователю кодов, к выходам которого подключены управляющие входы обоих управляемых делителей частоты, причем к выходу первого датчика подключен вход преобразователя напряжения в частоту, а второй датчик связан с аналого-цифровым преобразователем, датчики знака связаны с полусумматором, прямой выход которого связан с первым входом первого конъюнктора, а инверсный выход - с первым входом второго конъюнктора, вторые входы обоих конъюнкторов подключены к выходу второго управляемого делителя частоты, выход первого конъюнктора связан с вычитающим входом реверсивного счетчика, а выход второго конъюнктора - с суммирующим входом реверсивного счетчика, установочный вход которого подключен к компаратору, при этом коды на выходе преобразователя кодов имеют вид Kδ2 - целая часть a/X, где X - код на выходе преобразователя кодов, Kδ2= (a/X): (a/X-Kδ2), округленное до ближайшего целого, константа a > Xмакс.

Авторы

Даты

1994-01-15—Публикация

1991-06-13—Подача