фиг 1

Ъ

00

XI

чэ

ю

Устройство относится к области преобразовательной техники и предназначено для использования в микропроцессорных системах управления фазового управления вентильных преобразователей, ведомых сетью.

Известны аппаратные формирователи цифрового опорного кода (сигнала развертки) для систем управления вертикального типа, стабилизированные по отношению к изменениям частоты сети.

Однако в таких устройствах для достижения точной стабилизации необходима высокая рабочая частота. Достаточно сложна аппаратурная реализация.

Ближайшим по технической сущности к заявляемому устройству является генератор опорного кода, содержащий источник тактовых импульсов, каскадный делитель частоты, вычислительный узел (микропроцессор), счетчик опорного кода и ряд логических узлов, вводимых для стабилизации опорного кода при изменении частоты сети, Устройство весьма просто и обеспечивает высокую точность формирования опорного кода при невысокой рабочей частоте.

Недостатком устройства является невысокая надежность его работы, обусловленная тем, что опорный код вводится в микропроцессор без остановки счетчика. В связи с этим велика возможность ложного считывания опорного кода.

Цель изобретения - повышение надежности.

Поставленная цель достигается тем, что генератор опорного кода для микропроцессорной системы управления вентильного преобразователя, содержащий компаратор сети, соединенный с установочным входом счетчика, генератор импульсов, первый и второй коньюнкторы, снабжен третьим конъюнктором, узлом задержки, интегратором, дополнительным компаратором и источником постоянного напряжения, причем генератор импульсов подключен к первому входу первого конъюнктора, выход которого через интегратор и первый вход дополнительного компаратора подключен к первому входу второго конъюнктора, выход которого через узел задержки подключен к первому входу третьего коньюнктора, выход которого подключен к счетному входу счетчика, выходы которого являются выходами генератора опорного кода, выход первого конъюнктора подключен к второму инверсному входу второго конъюнктора и второму входу третьего конъюнктора, а источник постоянного напряжения подключен к второму входу дополнительного компаратора, второй

инверсный вход первого конъюнктора и вход разрешения ввода информации со счетчика предназначены для подключения к адресной магистрали микропроцессорной

системы управления вентильного преобразователя.

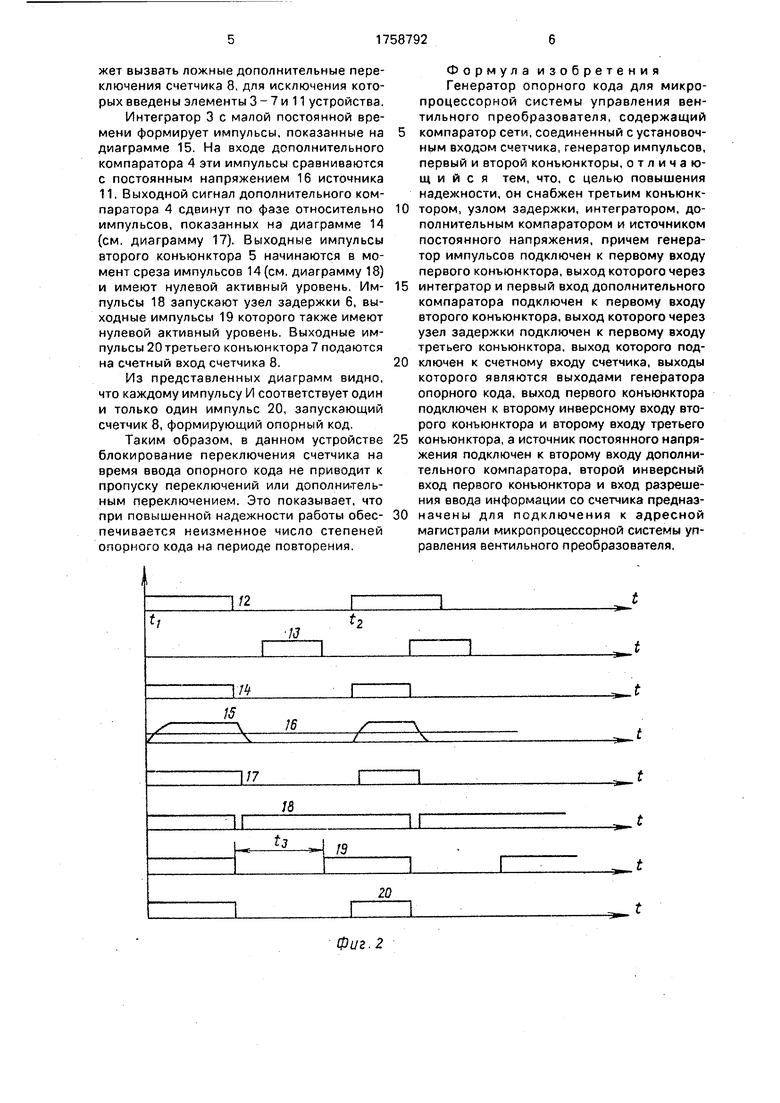

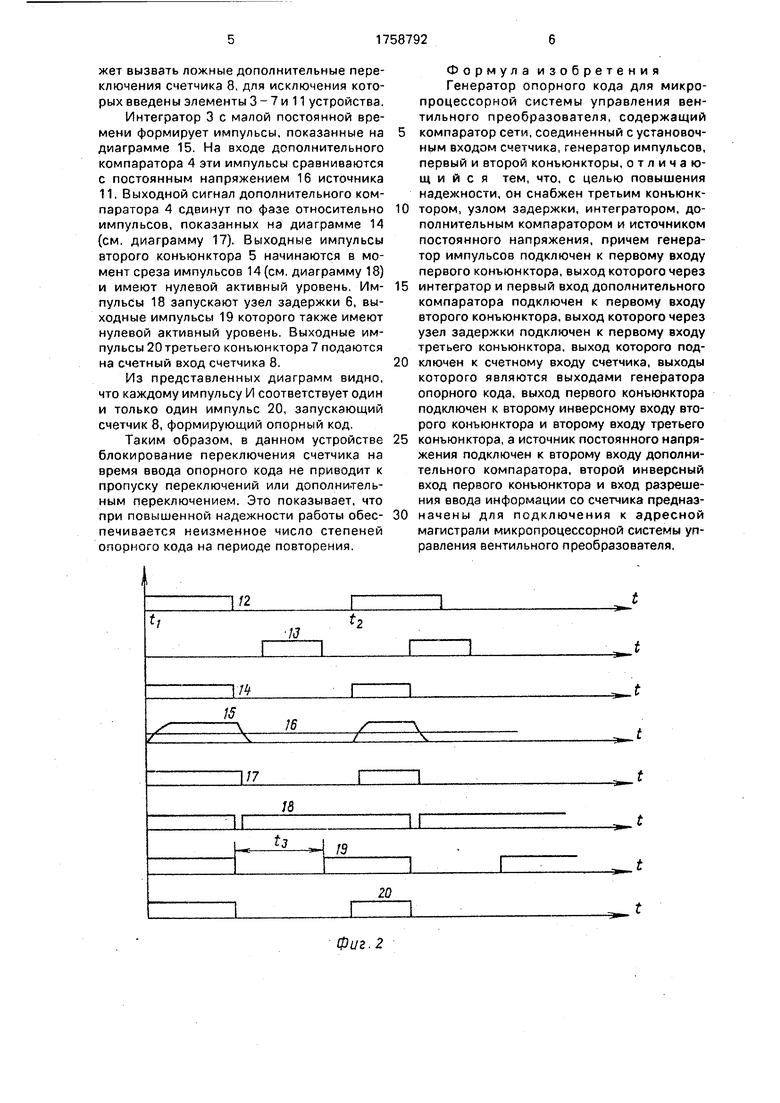

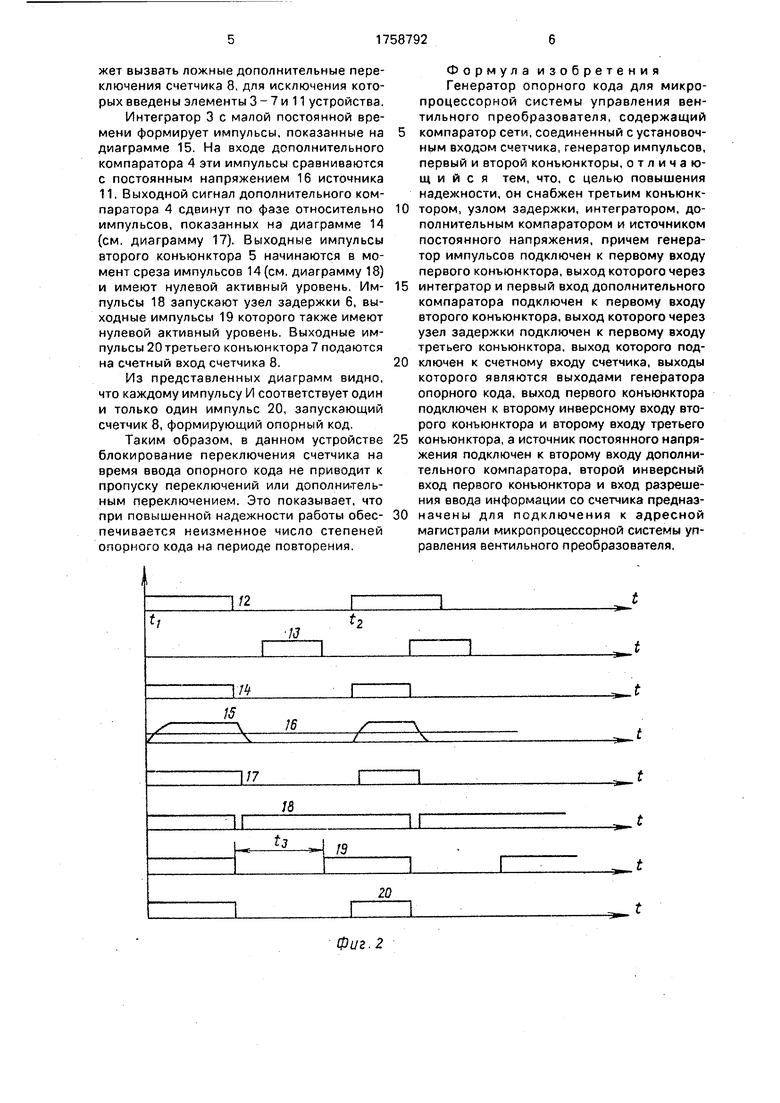

На фиг. 1 приведена структурная схема устройства, где генератор импульсов 1 через первый конъюнктор 2, интегратор 3, до0 полнительный компаратор 4, второй мультиплексор 5, узел задержки 6, и третий конъюнктор 7 связан со счетным входом счетчика 8, выходы которого связаны с входами микропроцессора 9, адресная магист5 раль которого связана со счетчиком 8 и инверсным входом первого конъюнктора 2. выход которого связан с вторым инверсным входом второго конъюнктора 5 и вторым входом третьего конъюнктора 7, компара0 тор сети 10 подключен к установочному входу счетчика 8, а источник постоянного напряжения 11 - к второму входу дополнительного компаратора 4; на фиг. 2 и 3 - временные диаграммы работы, причем ди5 аграммы фиг. 3 являются продолжением диаграмм фиг. 2, где 12 - импульс И на выходе генератора импульсов 1,13- сигнал на инверсном входе первого конъюнктора 2, 14 - сигнал на выходе первого конъюнктора 2,15

0 - сигнал на выходе интегратора 3, 16 - сигнал источника постоянного напряжения 11, 17-сигнал на выходе дополнительного компаратора 4, 18 - сигнал на выходе второго конъюнктора 5, 19 - сигнал на выходе узла

5 задержки 6, 20 - сигнал на счетном входе счетчика 8.

Принцип действия устройства заключается в следующем.

В момент естествен ной коммутации по

0 сигналу компаратора сети 10 счетчих 8 устанавливается в исходное положение и далее переключается с частотой, задаваемой генератором 1. Микропроцессор 9 на один машинный такт ранее процедуры ввода

5 опорного кода со счетчика 8 формирует на адресной магистрали сигнал 13, который поддерживается до конца ввода. Для исключения ошибок при вводе в устройстве блокируется переключение счетчика 8 на время

0 существования импульса 13, что представлено на временных диаграммах сигнала на выходе-первого конъюнктора 2 (диаграмма 14). Устройство функционирует при условии, что длительность импульсов И

5 на выходе генератора импульсов 1 (диаграмма 12) больше, чем длительность импульсов, показанных на диаграмме 13. Это обеспечивается выбором схемного решения генератора импульсов 1. Однако блокировка переключения счетчика на время ввода может вызвать ложные дополнительные переключения счетчика 8, для исключения которых введены элементы 3 - 7 и 11 устройства.

Интегратор 3 с малой постоянной времени формирует импульсы, показанные на диаграмме 15. На входе дополнительного компаратора 4 эти импульсы сравниваются с постоянным напряжением 16 источника 11. Выходной сигнал дополнительного компаратора 4 сдвинут по фазе относительно импульсов, показанных на диаграмме 14 (см. диаграмму 17). Выходные импульсы второго коньюнктора 5 начинаются в момент среза импульсов 14 (см. диаграмму 18) и имеют нулевой активный уровень. Им- пульсы 18 запускают узел задержки 6, выходные импульсы 19 которого также имеют нулевой активный уровень. Выходные импульсы 20третьего коньюнктора 7 подаются на счетный вход счетчика 8.

Из представленных диаграмм видно, что каждому импульсу И соответствует один и только один импульс 20, запускающий счетчик 8, формирующий опорный код.

Таким образом, в данном устройстве блокирование переключения счетчика на время ввода опорного кода не приводит к пропуску переключений или дополнительным переключением. Это показывает, что при повышенной надежности работы обес- печивается неизменное число степеней опорного кода на периоде повторения.

Формула изобретения Генератор опорного кода для микропроцессорной системы управления вентильного преобразователя, содержащий компаратор сети, соединенный с установочным входом счетчика, генератор импульсов, первый и второй конъюнкторы, отличающийся тем, что, с целью повышения надежности, он снабжен третьим конъюнк- тором, узлом задержки, интегратором, дополнительным компаратором и источником постоянного напряжения, причем генератор импульсов подключен к первому входу первого конъюнктора, выход которого через интегратор и первый вход дополнительного компаратора подключен к первому входу второго конъюнктора, выход которого через узел задержки подключен к первому входу третьего коньюнктора, выход которого подключен к счетному входу счетчика, выходы которого являются выходами генератора опорного кода, выход первого коньюнктора подключен к второму инверсному входу второго конъюнктора и второму входу третьего конъюнктора, а источник постоянного напряжения подключен к второму входу дополнительного компаратора, второй инверсный вход первого конъюнктора и вход разрешения ввода информации со счетчика предназ- начены для подключения к адресной магистрали микропроцессорной системы управления вентильного преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор опорного кода вентильного преобразователя | 1989 |

|

SU1674330A1 |

| Устройство для управления регулируемым мостовым инвертором напряжения | 1984 |

|

SU1239809A1 |

| Генератор опорного кода вентильного преобразователя | 1990 |

|

SU1818666A1 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2474864C1 |

| Одноканальное устройство для фазового управления статическим преобразователем | 1977 |

|

SU736344A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU414734A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ КОМПЕНСАТОРОМ РЕАКТИВНОЙ МОЩНОСТИ | 1991 |

|

RU2006128C1 |

| Стабилизатор переменного напряжения | 1986 |

|

SU1427350A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ МОЩНОСТИ | 2013 |

|

RU2533746C2 |

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1993 |

|

RU2056693C1 |

Сущность изобретения: устройство содержит компаратор 10 сети, счетчик 8, генератор 1 импульсов, конъюнкторы 2, 5, 7, микропроцессор 9, узел 6 задержки, интегратор 3, дополнительный компаратор 4 и источник ПРОСТОЯННОГО напряжения. 3 ил.

12

;

/J

15

/

16

Ж

J8

t3

/5

Фиг. 2

-

t-t

-

-

t

${U.3

| Чаплыгин Е.Е | |||

| Стабилизация управления вентильными преобразователями при изменениях частоты сети | |||

| - Электротехника, 1989, tvfe 12, с | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Генератор опорного кода вентильного преобразователя | 1989 |

|

SU1674330A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1992-08-30—Публикация

1990-06-11—Подача