1

(21)4689635/07

(22) 10.05.89

(46)30.08.91. Бюл. №32

(71)Московский энергетический институт

(72) Е.Е.Чаплыгин

(53)621.316.727(088.8)

(56)Горбачев Г.Н. Промышленная электроника. Учебник для ВУЗов, М. Энергоато- миздат. 1988, с 293-295

(54) ГЕНЕРАТОР ОПОРНОГО КОДА ВЕНТИЛЬНОГО ПРЕОБРАЗОВАТЕЛЯ

(57)Устройство относится к области преобразовательной техники и предназначено для использования в микропроцессорных устройствах фазового управления ведомыми сетью вентильными преобразователями.

Целью изобретения является стабилизация опорного кода при изменениях частоты сети Источник 1 тактовых импульсов через оба делителя 2 и 3 частоты связан с входами первого коньюнктора 4, выход которого через счетный триггер 5 связан со счетным входом счетчика 6, компаратор 7 напряжения сети связан с первым входом второго коныонктора 8, установочным входом дополнительного счетчика 9 и тактовым входом вычислительного узла 10, выход которого связан с управляющим входом управляемого делителя 2 частоты, а вход - с выходом дополнительного счетчика 9, счетный вход которого связан с выходом второго конъюнктора 8, второй вход которого подключен к выходу первого коньюнктора 4 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор опорного кода для микропроцессорной системы управления вентильного преобразователя | 1990 |

|

SU1758792A1 |

| Генератор опорного кода вентильного преобразователя | 1990 |

|

SU1818666A1 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2474864C1 |

| Устройство для управления регулируемым мостовым инвертором напряжения | 1984 |

|

SU1239809A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ-КОД СО СТУПЕНЧАТЫМ ПИЛООБРАЗНЫМ НАПРЯЖЕНИЕМ | 2018 |

|

RU2692426C1 |

| Стабилизатор переменного напряжения | 1986 |

|

SU1427350A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU414734A1 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1994 |

|

RU2072550C1 |

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1993 |

|

RU2056693C1 |

| Устройство для обнаружения боксования колесной пары локомотива | 1990 |

|

SU1749071A1 |

Устройство относится к области преобразовательной техники и предназначено для использования в микропроцессорных устройствах фазового управления ведомыми сетью вентильными преобразователями. Целью изобретения является стабилизация опорного кода при изменениях частоты сети. Источник 1 тактовых импульсов через оба делителя 2 и 3 частоты связан с входами первого конъюнктора 4, выход которого через счетный триггер 5 связан со счетным входом счетчика 6, компаратор 7 напряжения сети связан с первым входом второго конъюнктора 8, установочным входом дополнительного счетчика 9 и тактовым входом вычислительного узла 10, выход которого связан с управляющим входом управляемого делителя 2 частоты, а вход - с выходом дополнительного счетчика 9, счетный вход которого связан с выходом второго конъюнктора 8, второй вход которого подключен к выходу первого конъюнктора 4. 2 ил.

Изобретение относится к области преобразовательной техники и предназначено для использования в микропроцессорных устройствах управления ведомыми сетью вентильными преобразователями.

Целью изобретения является стабилизация опорного кода при изменении частоты сети.

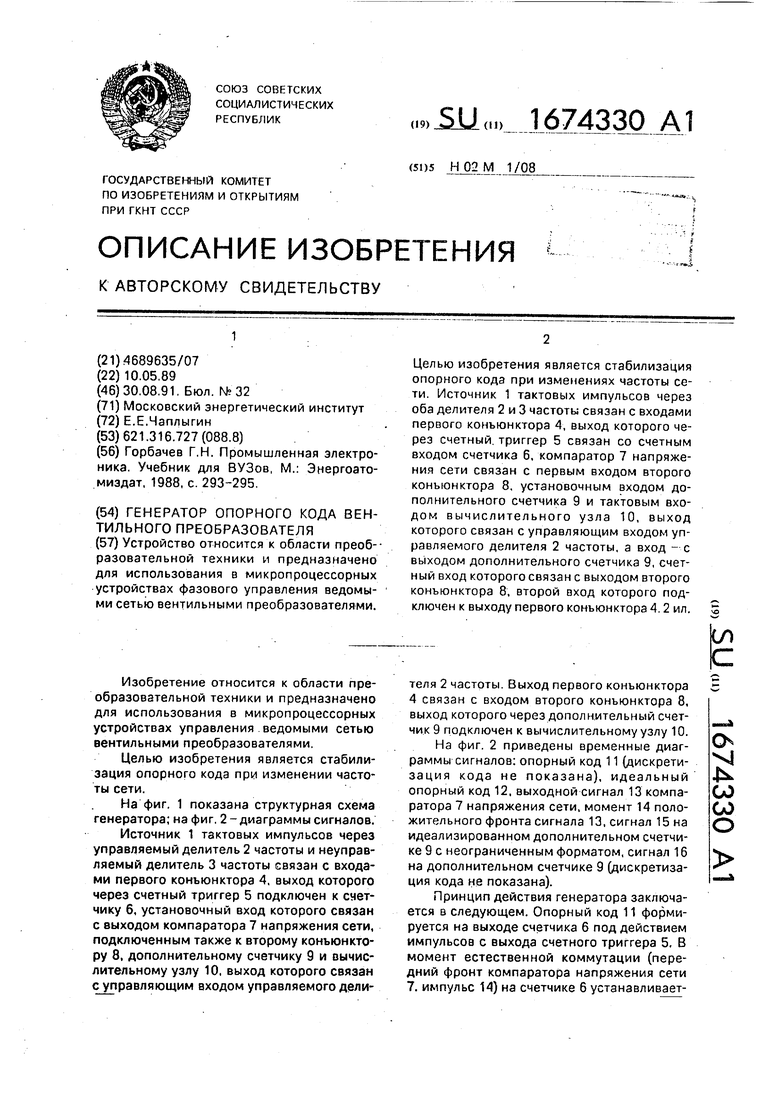

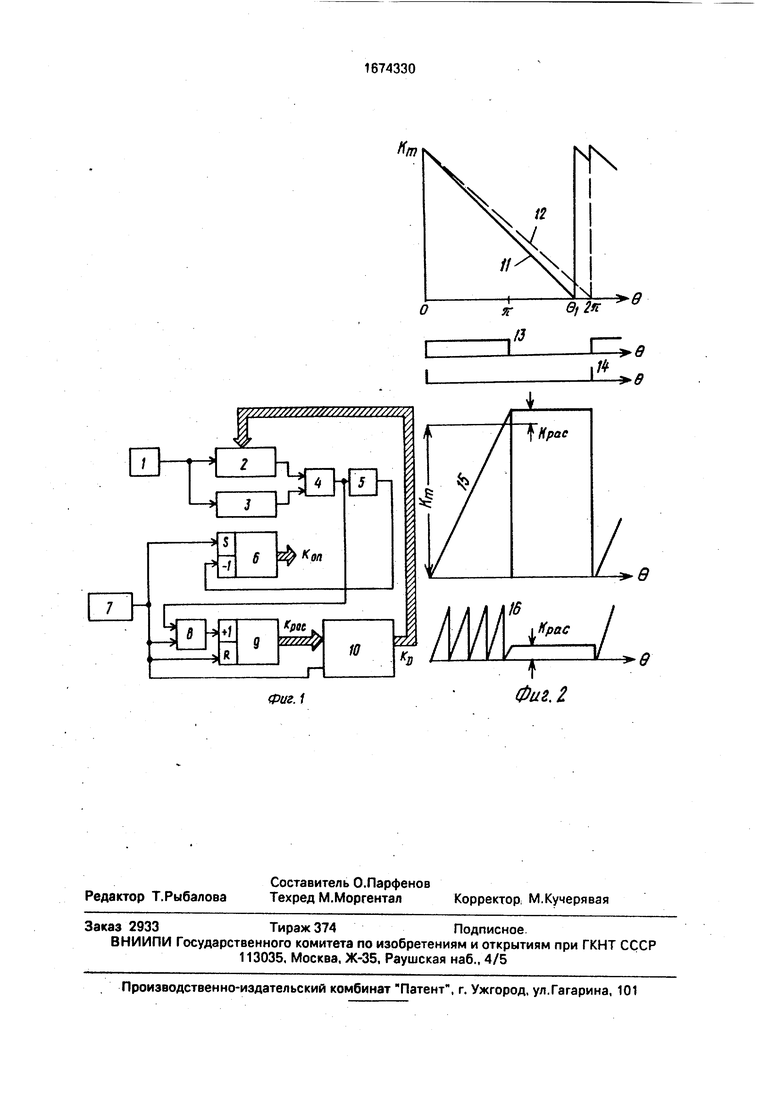

На фиг. 1 показана структурная схема генератора; на фиг. 2 - диаграммы сигналов.

Источник 1 тактовых импульсов через управляемый делитель 2 частоты и неуправляемый делитель 3 частоты связан с входами первого коньюнктора 4, выход которого через счетный триггер 5 подключен к счетчику 6, установочный вход которого связан с выходом компаратора 7 напряжения сети, подключенным также к второму конъюнкто- ру 8, дополнительному счетчику 9 и оычис- лительному узлу 10, выход которого связан с управляющим входом управляемого делисо

С

теля 2 частоты. Выход первого коньюнктора 4 связан с входом второго коньюнктора 8, выход которого через дополнительный счетчик 9 подключен к вычислительному узлу 10.

На фиг. 2 приведены временные диаграммы сигналов: опорный код 11 (дискретизация кода не показана), идеальный опорный код 12, выходной сигнал 13 компаратора 7 напряжения сети, момент 14 положительного фронта сигнала 13, сигнал 15 на идеализированном дополнительном счетчике 9 с неограниченным форматом, сигнал 16 на дополнительном счетчике 9 (дискретизация кода не показана).

Принцип действия генератора заключается в следующем. Опорный код 11 формируется на выходе счетчика 6 под действием импульсов с выхода счетного триггера 5. В момент естественной коммутации (передний фронт компаратора напряжения сети 7. импульс 14) на счетчике 6 устанавливаетО

VI

v Сл)

со о

ся максимальный код Кт. Если частота импульсов на выходе счетного триггера 5 выше требуемой, то опорный код 11 достигает нуля раньше момента следующей естественной коммутации (момент 01 ), при отсутствии погрешности в формировании опорного кода он должен был бы соответствовать кривой 12, т.е. частота на выходе счетного триггера 5 должна быть ниже.

Поскольку в микропроцессорных системах выход счетчика 6 доступен только программно, фиксация рассогласования опорного кода 11 в конце периода неприменима, это потребовало бы прерывания работы системы фазового управления. Поэтому для фиксации рассогласования служит дополнительный счетчик 9, частота переключений которого вдвое меньше, чем у счетчика 6. При отсутствии рассогласования в счетчике 9 с неограниченным числом разрядов за половину периода был бы записан код Кт. В рассматриваемом режиме код 15 больше на величину рассогласования Крае. При ограничении, наложенном на изменения частоты сети, ограничен формат рассогласования Крас, поэтому разрядность дополнительного счетчика 9 может быть ограничена (сигнал 16 на его выходе не содержит старших разрядов). Благодаря второму коныонктору 8 накопление сигнала в дополнительном счетчике происходит в течение первой половины периода, в различие частот, заполняющих счетчики 6 и 9, в два раза за счет работы счетноготриггера 5 приводит к тому, что с выхода дополнительного счетчика на второй половине периода можно снять сигнал Крас. (16 на фиг. 2). Отрицательные значения представлены в дополнительном коде, обычном для представления отрицательных чисел в ЭВМ, старший разряд - знаковый: при О частота на входе счетчика 6 больше требуемой, при 1 - меньше требуемой,

Вторая половина периода - это интервал работы вычислительного узла, в результате его работы Ко, управляющий работой делителя 2 частоты, увеличивается таким образом, что недостаток или избыток импульсов, заполняющих счетчик 6 на предыдущем периоде, устраняется. В качестве вычислительного узла используется микро- ЭВМ, в режиме разделения времени (после выработки управляющего импульса) эту функцию выполняет микро-ЭВМ фазового управления системы. Для ускорения расчета может использоваться табулирование решение с записью в ПЗУ.

Источник 1 тактовых импульсов имеет ограниченную сверху частоту, поэтому деление его частоты в целое число раз не позволяет регулировать число импульсов на входе

счетчика 6 с требуемой точностью. Примененный принцип: неуправляемый делитель 3 частоты формирует минимально необходимую последовательность импульсов, а управляемый вычислительным узлом 10

делитель 2 частоты добавляет в нее дополнительные импульсы. Суммирование импульсов осуществляет первый коньюнктор 4. Сигнал управления на выходе узла 10 увеличивает или уменьшает число дополнительных импульсов, полностью компенсируя ошибку формирования опорного сигнала на предыдущем периоде. Неравномерность следования импульсов на выходе коньюнктора 4 при малом интервале квантования угла управления не оказывает заметного влияния на точность формирования опорного кода.

Формула изобреиния Генератор опорного кода вентильного

преобразователя, содержащий источник тактовых импульсов и счетчик, вход установки числа Кт которого связан с компаратором напряжения сети, первый коньюнктор и счетный триггер, отличающийся тем,

что, с целью стабилизации опорного кода при изменении частоты сети, введены неуправляемый делитель частоты в D раз, управ- ляемый делитель частоты в Ко раз, дополнительный счетчик, второй конъюнктор и вычислительный узел, причем источник тактовых импульсов через делители частоты связан с входами первого коньюнктора, выход которого через счетный триггер связан со счетным входом счетчика и непосредственно с вторым входом второго конъ- юнктора, компаратор напряжения сети связан с первым входом второго коньюнктора, установочным входом дополнительного счетчика и тактовым входом вычислительного узла, выход которого связан с управляющим входом управляемого делителя частоты, а вход - с выходом дополнительного счетчика, счетный вход которого подключен к выходу второго конъюнктора, а

вычислительный узел выполнен вычисляющим в п такте код

Ко

55

v L Кр. п -1 v

, п - . п - 1 1J7-К- К-рас .

где Крас - код на выходе дополнительного счетчика,

Авторы

Даты

1991-08-30—Публикация

1989-05-10—Подача