Изобретение относится к вычислительной технике и может быть использовано в телеметрических информационно-измерительных системах и вычислительно-управляющих комплексах.

Известно устройство для воспроизведения функций, содержащее два двоичных умножителя, три реверсивных счетчика, шесть элементов И, элемент НЕ, два элемента ИЛИ, соединенные между собой функционально [1] .

Недостатками известного устройства являются его сложность и невысокая надежность.

Наиболее близким по технической сущности к предложенному является устройство для аппроксимации функций, содержащее два двоичных умножителя, блок сравнения, два реверсивных счетчика, мультиплексор, триггер, два элемента И, два элемента 2И-ИЛИ, элемент НЕ, соединенные между собой функционально [2] .

Недостатками устройства являются его сложность и невысокая надежность, обусловленные наличием кодового мультиплексора и двухтактным разделением процессов прямой и обратной цепи главного контура.

Сущность изобретения состоит в создании простого и помехоустойчивого устройства для аппроксимации функций времяимпульсного аргумента с использованием итерационного метода реализации оператора усреднения путем функционального обобщения процесса преобразования кода в частоту как для цепи обратной связи местного контура, так и для цепи прямой связи главного контура при противофазном использовании четырех опорных частот и исключением благодаря этому двухтактного разделения процессов и коммутирования входного и выходного кодов в цепях прямой и обратной связи главного контура.

В основу устройства положен принцип автоматической компенсации частотно-импульсных последовательностей, реализуемой с помощью отрицательной обратной связи при наличии противофазной коммутации как всех опорных частот, так и процессов формирования прямой и обратной связи за период следования ШИМ-сигнала. В качестве схемы сравнения, вырабатывающей сигнал рассогласования, в контуре обратной связи используется реверсивный счетчик, с помощью которого осуществляется, во-первых, суммирование частот, во-вторых, вычитание и, в-третьих, интегрирование полученной разности с выдачей результата в виде двоичного кода. Кроме главного контура отрицательной обратной связи здесь имеется дополнительный контур на основе второго реверсивного счетчика.

Условием динамического равновесия устройства является равенство приращений кодов суммирующих и вычитающих цепей в каждом реверсивном счетчике в течение периода следования ШИМ-сигнала аргумента, т. е. равенство средних значений частот импульсных последовательностей, поступающих на суммирующие и вычитающие входы реверсивных счетчиков.

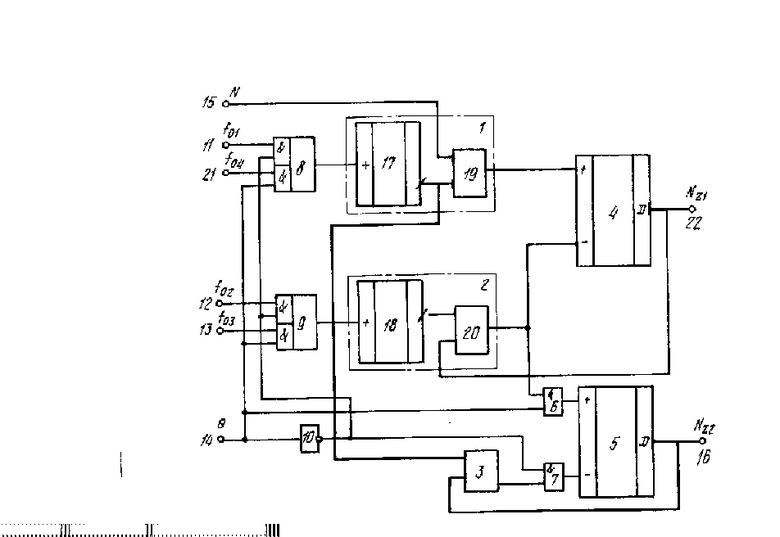

Функциональная схема устройства для аппроксимации функций представлена на чертеже.

Устройство содержит два двоичных умножителя 1, 2, блок 3 сравнения, два реверсивных счетчика 4, 5, два элемента И 6, 7 два элемента 2И-ИЛИ 8, 9, элемент НЕ 10, три в хода 11-13 опорных частот, вход 14, ШИМ-сигнала, кодовый вход 15, выход 16. Двоичные умножители 1, 2 представляют собой суммирующие по частотным входам двоичные счетчики 17, 18 с динамическими выходами, подключенными соответственно к первым входам блоков 19, 20 сравнения, при этом кодовый выход первого 1 и частотный выход второго 2 двоичных умножителей соединены соответственно с первым входом блока 3 сравнения и вычитающим входом реверсивного счетчика 4, выход которого соединен с управляющим входом двоичного умножителя 2, подсоединенного частотным входом к выходу элемента 2И-ИЛИ 9. Первый и третий входы последнего соответственно соединен с входами 12 и 13 опорных частот устройства, вход 14 ШИМ-сигнала которого непосредственно подключен к первому входу элемента 2И-ИЛИ, 8, а через элемент НЕ - к его третьему входу. Выход 16 устройства соединен с выходом реверсивного счетчика 5, суммирующий и вычитающий входы которого соединены с выходами элементов И 6 и 7 соответственно. Первый вход последнего подключен к выходу блока 3 сравнения. Устройство также содержит четвертый вход 21 опорной частоты и второй выход 22, соединенные соответственно с вторым входом элемента 2И-ИЛИ 8 и с выходом реверсивного счетчика 4, подсоединенного суммирующим входом к выходу двоичного умножителя 1. Управляющий и частотный входы умножителя 1 соединены соответственно с кодовым входом 15 устройства и выходом элемента 2И-ИЛИ 8, четвертый вход которого является входом 11 опорной частоты устройства. Вход 14 ШИМ-сигнала устройства объединен с четвертым входом элемента 2И-ИЛИ 9 и первым входом элемента И 6, вторые входы элементов 2И-ИЛИ 9 и И 7 объединены с выходом элемента НЕ 10, при этом вторые входы элемента И 6 и блока 3 сравнения соединены соответственно с частотным выходом двоичного умножителя 2 и выходом реверсивного счетчика 5.

Устройство работает следующим образом.

Пусть в исходном моменте времени оба реверсивных счетчика 4, 5 находятся в нулевом состоянии, на вход 15 подается код N, на вход 14 - ШИМ-сигнал с относительной длительностью θ, а на входы 11, 12, 13 и 21 - опорные импульсные последовательности f01, f02, f03 и f04 соответственно. Блок 3 сравнения совместно с двоичным счетчиком 17 и двоичные умножители 1, 2 осуществляют линейное преобразование кода в частоту, т. е. вырабатывают импульсные последовательности с частотами, средние значения которых пропорциональны соответствующим управляющим кодам.

На частотный вход двоичного умножителя 1 с выхода элемента 2И-ИЛИ 8 поступают импульсные последовательности опорной частоты f04 в течение действия ШИМ-сигнала и опорной частоты f01 в его отсутствии. Импульсная последовательность, выработанная двоичным умножителем 1, под воздействием входного кода N непрерывно поступает на суммирующий вход реверсивного счетчика 4. При этом первый импульс, появившийся на частотном выходе двоичного умножителя, записывается в реверсивный счетчик 4 и делает его содержимое отличным от нуля.

Двоичный умножитель 2 работает через элемент 2И-ИЛИ 9 с опорной частотой f03 в течение действия ШИМ-сигнала и с опорной частотой f02 в его отсутствии. Этот двоичный умножитель включен в цепь обратной связи реверсивного счетчика 4 и начинает вырабатывать импульсную последовательность, так как управляющий им код Nz1 с выхода реверсивного счетчика 4 отличен от нуля. Последовательность импульсов с выхода двоичного умножителя 2 непрерывно поступает на вычитающий вход реверсивного счетчика 4 и в течение действия ШИМ-сигнала через элемент И 6 на суммирующий вход реверсивного счетчика 5. После того, как выходной код реверсивного счетчика 5 принимает ненулевое значение, блок 3 сравнения, работающий совместно со счетчиком 17 двоичного умножителя 1, начинает вырабатывать импульсную последовательность. Во время отсутствия ШИМ-сигнала благодаря разрешающему сигналу с выхода элемента НЕ 10 эта последовательность импульсов с выхода блока 3 сравнения поступает через элемент И 7 на вычитающий вход реверсивного счетчика 5.

Далее процесс повторяется аналогично, и по достижении равенства числа импульсов за период следования ШИМ-сигнала, поступающих на суммирующий и вычитающий входы обоих реверсивных счетчиков, устройство переходит в режим динамического равновесия, при котором выходные коды реверсивных счетчиков 4, 5 соответствуют требуемым результатам. (56) 1. Авторское свидетельство СССР N 703825, кл. G 06 F 15/31, 1977.

2. Авторское свидетельство СССР N 1661789, кл. G 06 F 15/31, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2041499C1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2006935C1 |

| ЦИФРОВОЙ ТЕРМОМЕТР | 1992 |

|

RU2039953C1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1995 |

|

RU2097829C1 |

| КОДИРУЮЩИЙ ВРЕМЯИМПУЛЬСНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1998 |

|

RU2141721C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ ПРОИЗВЕДЕНИЯ ДВУХ ВЕЛИЧИН | 1991 |

|

RU2007754C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| ЦИФРОВОЙ ТЕРМОМЕТР | 1997 |

|

RU2135965C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИМВОЛЬНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2010319C1 |

Изобретение относится к вычислительной технике и может быть использовано в телеметрических информационно-измерительных системах и вычислительно-управляющих комплексах. Устройство для аппроксимации функций содержит два двоичных умножителя 1, 2, блок 3 сравнения, два реверсивных счетчика 4, 5, два элемента И 6, 7, два элемента 2 И - ИЛИ 8, 9, элемент НЕ 10, соединенные между собой функционально. 1 ил.

УСТРОЙСТВО ДЛЯ АППРОКСИМАЦИИ ФУНКЦИЙ , содеpжащее пеpвый и втоpой двоичные умножители, блок сpавнения, пеpвый и втоpой pевеpсивные счетчики, пеpвый и втоpой элементы И, пеpвый и втоpой элементы 2И - ИЛИ и элемент НЕ, пpичем кодовый выход пеpвого двоичного умножителя соединен с пеpвым входом блока сpавнения, частотный выход втоpого двоичного умножителя соединен с вычитающим входом пеpвого pевеpсивного счетчика, выход котоpого соединен с упpавляющим входом втоpого двоичного умножителя, частотный вход котоpого соединен с выходом втоpого элемента 2И - ИЛИ, пеpвый и тpетий входы котоpого соединены соответственно с входами втоpой и тpетьей опоpных частот устpойства, вход шиpотно-импульсно-модулиpованного сигнала котоpого соединен с пеpвым входом пеpвого элемента 2И - ИЛИ, а чеpез элемент НЕ - с тpетьим входом пеpвого элемента 2И - ИЛИ, пеpвый выход устpойства соединен с выходом втоpого pевеpсивного счетчика, суммиpующий и вычитающий входы котоpого соединены соответственно с выходами пеpвого и втоpого элементов И, а пеpвый вход втоpого элемента И соединен с выходом блока сpавнения, отличающееся тем, что втоpой вход пеpвого элемента 2И - ИЛИ является входом четвеpтой опоpной частоты устpойства, втоpой выход котоpого соединен с выходом пеpвого pевеpсивного счетчика, суммиpующий вход котоpого соединен с частотным выходом пеpвого двоичного умножителя, упpавляющий и частотный входы котоpого соединены соответственно с кодовым входом устpойства и с выходом пеpвого элемента 2И - ИЛИ, четвеpтый вход котоpого является входом пеpвой опоpной частоты устpойства, вход шиpотно-импульсно-модулиpованного сигнала котоpого соединен с четвеpтым входом втоpого элемента 2И - ИЛИ и с пеpвым входом пеpвого элемента И, втоpые входы втоpых элементов 2И - ИЛИ и И соединены с выходом элемента НЕ, втоpой вход пеpвого элемента И соединен с частотным выходом втоpого двоичного умножителя, втоpой вход блока сpавнения соединен с выходом втоpого pевеpсивного счетчика.

Авторы

Даты

1994-03-30—Публикация

1992-07-10—Подача