Изобретение относится к вычислительной технике, предназначено для вычисления логарифма по основанию два от чисел, представленных параллельным двоичным кодом, и может быть использовано в цифровых системах обработки данных.

Известно устройство для вычисления логарифма, содержащее регистры старших и младших разрядов аргумента, три блока памяти, блок управления, коммутатор, сумматор, выходной регистр, триггер числа, сдвигатель, блок управления сдвигателем, два блока сравнения. Вычисление логарифма по основанию два от нормализованного аргумента производится на основе аппроксимации логарифма прямой.

Недостатками известного устройства являются сложность технической реализации и низкая точность.

Известно более простое устройство для вычисления логарифма по основанию два, содержащее блок управления, блок сдвига, шифратор, три регистра, дешифратор, два преобразователя кода, два сумматора, шифратор. Приближенное значение логарифма по основанию два от аргумента N вычисляется по формуле

log2N = k + log2(1 + X) = k + X*, где k - номер старшего единичного разряда;

Х - двоичное число вида  a12i-k.

a12i-k.

В зависимости от принадлежности величин Х одному из четырех равных диапазонов мантисса Х* может быть вычислена с помощью одной из четырех аппроксимирующих линейных функций. Погрешность вычисления логарифма при этом не превосходит 0,6% .

Недостатком устройства является невысокая точность вычисления функции логарифма.

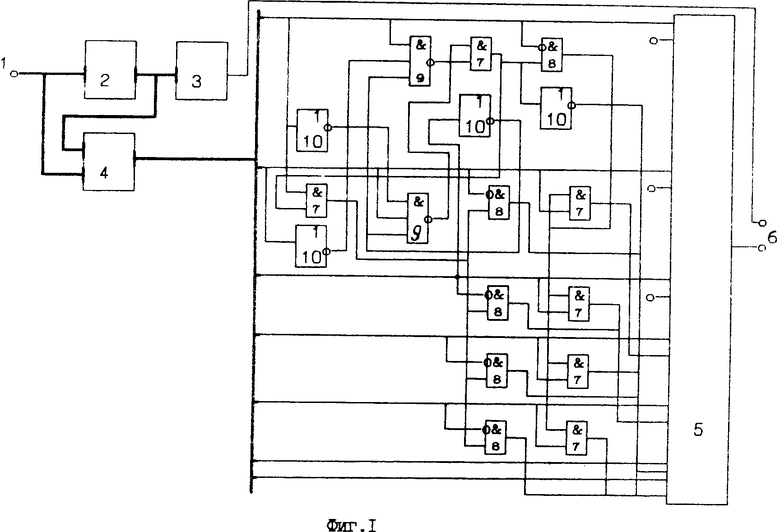

Наиболее близким по технической сущности к заявляемому является устройство, которое обеспечивает более высокую точность логарифмирования благодаря использованию поправок при вычислении мантиссы с помощью аппроксимирующих линейных функций. Оно (фиг. 1) содержит вход 1 кода аргумента, блок 2 выделения старшего разряда, шифратор 3, блок 4 сдвига, сумматор 5, причем вход 1 соединен с входом блока 2 выделения старшего разряда и информационным входом блока 4 сдвига, управляющий вход которого соединен с выходом блока 2 выделения старшего разряда и входом шифратора 3, выходы шифратора 3 и сумматора 5 являются выходами 6 устройства. Устройство также содержит первый и второй элементы И 7, группу элементов И 7, элемент И 8 с инверсным входом, группу элементов И 8 с инверсным входом, первый и второй элементы И-НЕ 9, четыре элемента НЕ 10. i-выход (i = 1,2, . . . , 7) блока 4 сдвига соединен с первым входом i-го разряда сумматора 5, выход первого разряда блока 4 сдвига соединен с первым входом первого элемента И-НЕ 9, первым входом второго элемента И 7, инверсным входом элемента И 8 с инверсным входом и через первый элемент НЕ 10 с первым входом второго элемента И-НЕ 9, второй вход которого соединен с выходом второго разряда блока 4 сдвига и через второй элемент НЕ 10 с вторым входом первого элемента И-НЕ 9. Третий вход последнего соединен через третий элемент НЕ 10 с выходом третьего разряда блока 4 сдвига и третьим входом второго элемента И-НЕ 9, выход которого соединен с первым входом первого элемента И 7, второй вход которого соединен с выходом первого элемента И-НЕ 9. Выход первого элемента И 7 соединен с вторым входом второго элемента И 7, прямым входом элемента И-НЕ 8 с инверсным входом и через четвертый элемент НЕ 10 с вторыми входами четвертого, шестого и седьмого разрядов сумматора 5. Выход элемента И 8 с инверсным входом соединен с первыми входами элементов И 7 группы, выход второго элемента И 7 соединен с прямыми входами элементов И 8 с инверсными входами группы, выход j-го разряда блока сдвига (j = 2,3,4,5) соединен с инверсным входом (j-1)-го элемента И 8 с инверсным входом группы и вторым входом (j-1)-го элемента И 7 группы, выход которого соединен с вторым входом (j+2)-го разряда сумматора 5 и выходом (j-1)-го элемента И 8 с инверсным входом группы. Вторые входы первого, второго и третьего разрядов сумматора 5 соединены с входом нулевого потенциала устройства.

Работа прототипа основана на соотношениях

log2 Z = N - 1 + log2(1 + t), где t= (Z-2N-1)/(2N-1), 0≅t≅1,

log2(1 + t) ≃ t + Δ t, где Δ t - поправка логарифма, равная

На вход 1 поступает восьмиразрядный двоичный код Z. Блок 2 определяет номер N самого старшего единичного разряда и выдает его на шифратор 3, который вырабатывает целую часть искомого логарифма, равную N-1. Одновременно этот номер поступает на блок 4 сдвига, который осуществляет сдвиг Z на N-1 разрядов вправо и выдает семиразрядную дробную часть логарифма на первый вход сумматора 5. Элементы НЕ 10 и И-НЕ 9 проверяют в каком диапазоне находится значение t. Если t < <3/8, то низкий уровень сигнала с первого разряда поступает на инверсный вход элемента И 8, одновременно высокий сигнал снимается с выхода первого элемента И 7 и подается на прямой вход элемента И 8, на выходе которого появляется единичный сигнал, разрешающий сдвиг на два разряда содержимого первых входов сумматора и формирующий таким образом поправку к дробной части логарифма. Аналогично при t ≥5/8 (первый разряд равен единице) сигнал с него закрывает элемент И 8 и открывает И 7. Второй сигнал вырабатывается элементом И-НЕ и первым элементом И 7. Высокий уровень сигнала с выхода второго элемента И 7 разрешает сдвиг вправо на два разряда обратного кода, т. е. осуществляет операцию 1 - t - 2-7 с помощью группы элементов И 7. При 3/8 ≅ t < 5/8 вырабатывается сигнал низкого уровня, блокирующий группы элементов И 8 и 7 и через четвертый элемент НЕ 10, поступающий на четвертый, шестой и седьмой разряды, задавая константу поправки 11/128 для данного диапазона t. На первый, второй и третий разряды второго входа и вход переноса сумматора 5 подается сигнал логического "0". В результате на выходе сумматора получено значение логарифма числа с точностью до семи разрядов после запятой, причем старшие шесть разрядов верны, а седьмой - в большинстве случаев. Максимальная абсолютная погрешность равна 0,014, а относительная приведенная погрешность не превосходит 0,175% .

Недостатком прототипа является его невысокая точность, обусловленная использованием линейных функций, аппроксимирующих дробную часть логарифма.

Целью изобретения является повышение точности вычисления функции логарифма по основанию два.

Цель достигается тем, что в устройство для вычисления логарифма, содержащее вход кода аргумента, блок выделения старшего разряда, шифратор, блок сдвига, сумматор, причем вход устройства соединен с входом блока выделения старшего разряда и информационным входом блока сдвига, управляющий вход которого соединен с выходом блока выделения старшего разряда и входом шифратора, выходы шифратора и сумматора являются выходами устройства, введены первый, второй, третий и четвертый умножители, первый и второй вычитатели, накапливающий сумматор, информационный вход которого подключен к выходу второго вычитателя, управляющий вход - к входу синхронизации устройства, а выход объединен с вторым входом четвертого умножителя, первый вход которого подключен к входу четвертого кода, и с вычитающим входом первого вычитателя, суммирующий вход которого подключен к входу второго кода, а выход - к первому входу второго умножителя, второй вход которого объединен с выходом блока сдвига и первым входом первого умножителя, а выход соединен с первым входом третьего умножителя, второй вход которого подключен к входу третьего кода, а выход соединен с суммирующим входом второго вычитателя, вычитающий вход которого объединен с выходом четвертого умножителя и с вторым входом сумматора, первый вход которого соединен с выходом первого умножителя, второй вход которого подключен к входу первого кода.

Вышеизложенное свидетельствует о наличии в заявляемом техническом решении отличительных от прототипа признаков, включающих как дополнительные элементы (четыре умножителя, два вычитателя, накапливающий сумматор), так и ранее неизвестные связи между ними и элементами прототипа. Эти элементы находят широкое применение в устройствах цифровой вычислительной техники: умножители осуществляют функцию умножения двух операндов, представленных параллельным позиционным кодом типа 8-4-2-1; два вычитателя и накапливающий сумматор выполняют функции, соответствующие их названиям. В заявляемом техническом решении все элементы устройства используются по прямому назначению, проявляя при этом в отдельности известные свойства. Однако взятые в совокупности, эти элементы и элементы прототипа и новая организация связей проявляют новое свойство, не присущее ни прототипу, ни одному из известных аналогов: повышение точности вычисления функции логарифма. Это свойство не повторяет ни одного из известных свойств отличительных признаков и не является их суммой. Другими словами, каждый из введенных элементов, отдельно взятый, необходим для обеспечения сформулированного положительного эффекта, а все они вместе взятые, т. е. с учетом всех взаимосвязей, достаточны, чтобы отличить устройство в целом от других подобного назначения и характеризовать его в том качестве, которое проявляется в сверхсуммарном результате, а именно в повышении точности вычисления функции логарифма. Из сказанного следует, что предлагаемое техническое решение обладает существенными отличиями от известных технических решений.

В основу работы устройства положен принцип вычисления логарифма с использованием итерационного метода определения мантиссы.

Сущность изобретения состоит в создании устройства для вычисления логарифма с большой точностью, определяемой применением дробно-рационального выражения, аппроксимирующего его мантиссу, с использованием итерационного метода реализации.

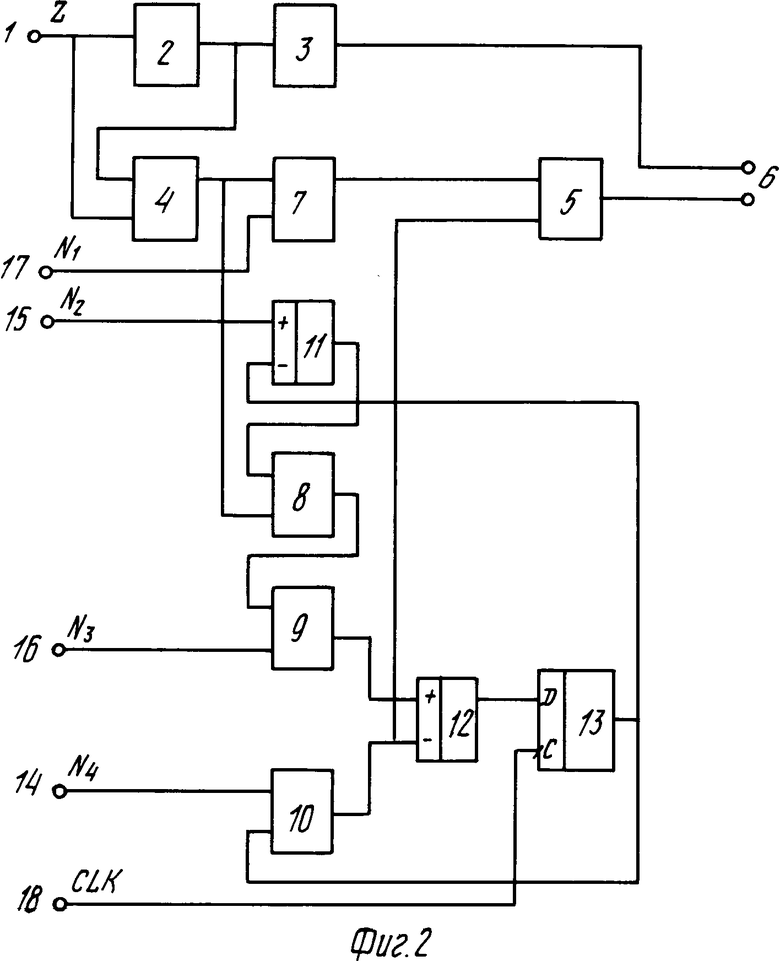

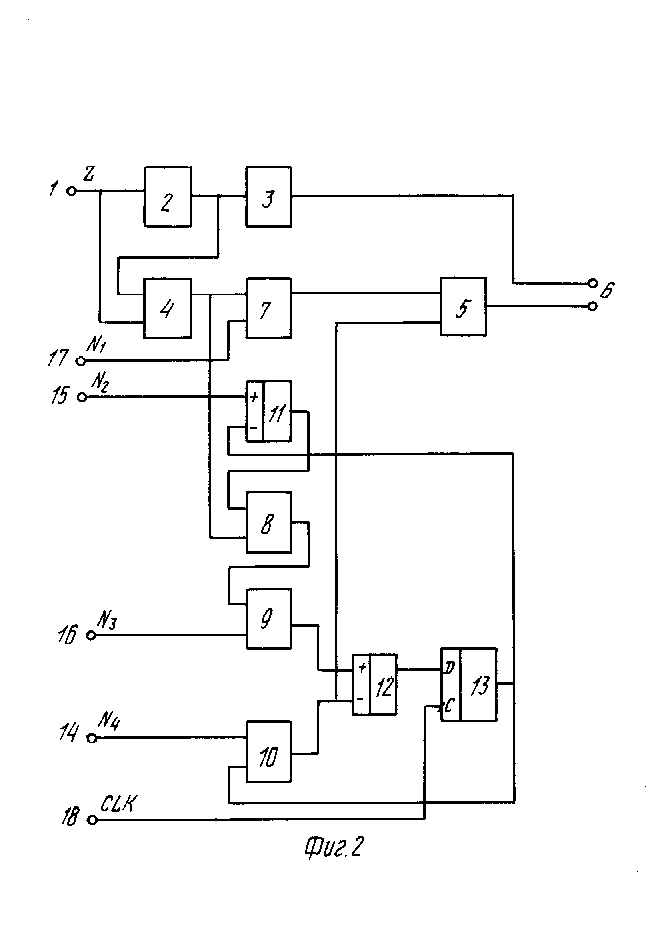

Предлагаемое устройство (фиг. 2) содержит вход 1 кода аргумента, блок 2 выделения старшего разряда, шифратор 3, блок 4 сдвига, сумматор 5, причем вход 1 соединен с входом блока 2 выделения старшего разряда и информационным входом блока 4 сдвига, управляющий вход которого соединен с выходом блока 2 выделения старшего разряда и входом шифратора 3, выходы шифратора 3 и сумматора 5 являются выходами 6 устройства, умножители 7-10, вычитатели 11, 12, накапливающий сумматор 13, информационный вход которого подключен к выходу вычитателя 12, а выход объединен с вторым входом умножителя 10, первый вход которого подключен к входу 14 четвертого кода, и с вычитающим входом вычитателя 11, суммирующий вход которого подключен к входу 15 второго кода, а выход - к первому входу умножителя 8. Второй вход последнего объединен с выходом блока 4 сдвига и первым входом умножителя 7, а выход соединен с первым входом умножителя 9, второй вход которого подключен к входу 16 третьего кода, а выход соединен с суммирующим входом вычитателя 12. Вычитающий вход вычитателя 12 соединен с выходом умножителя 10 и с вторым входом сумматора 5, первый вход которого соединен с выходом умножителя 7, второй вход которого подключен к входу 17 первого кода. Управляющий вход накапливающего сумматора 13 подключен к входу 18 синхронизации устройства.

Устройство работает следующим образом.

Пусть в начальный момент времени на выходе накапливающего сумматора 13 присутствует код числа So = L. На вход 1 устройства поступает код аргумента Z, а на входы 17, 15, 16, 14 - коды N1, N2, N3, N4, равные 0,25062; 1,7; 0,69935; 1,1926 соответственно. С входа 18 на управляющий вход накапливающего сумматора 13 поступают сигналы синхронизации CLK, длительность которых должна быть не менее времени задержки записи в накапливающем сумматоре 13, а период их следования - не менее суммарной задержки элементов 8-13.

Вычисление логарифма по основанию два основано на соотношении

log2 Z = N - 1 + log2 (1 + t), где t= (Z-2N-1)/(2N-1), 0≅t≅1; ;

N - номер самого старшего разряда кода аргумента Z.

Блок 2 определяет номер N и выдает его на шифратор 3, вырабатывающий характеристику искомого логарифма, равную N-1. Одновременно код номера N поступает на блок 4 сдвига, который осуществляет сдвиг кода Z на N-1 разрядов вправо и выдает код числа t на входы умножителей 7, 8, выполненных, как и остальные умножители 9, 10, например, на базе БИС матричного умножителя К1802ВР4 или К1802ВР5. С выхода умножителя 7 на первый вход сумматора 5 поступает код числа N1t, а с выхода вычитателя 11 на первый вход умножителя 8 поступает код числа N2-So, где So - число, соответствующее коду накапливающего сумматора 13 в исходный момент времени, и умножается на код числа t, т. е. на выходе умножителя 8 получают код числа (N2-So)t. Этот код поступает на первый вход умножителя 9 и умножается на код числа N3, т. е. на выходе умножителя 9 получают код числа (N2-So)N3t. Полученный результат поступает на суммирующий вход вычитателя 12, на вычитающий вход которого поступает код числа N4So с выхода умножителя 10. Этот код также поступает на второй вход сумматора 5. При этом с выходов умножителей 7-10 снимается старшая половина разрядов результата умножения.

Таким образом, в результате первой итерации с выхода вычитателя 12 на информационный вход накапливающего сумматора 13 поступает код первого приращения

Δ1 = (N2-So)N3t - N4So =

= N2N3t - So(N3t + N4) =

= N2N3t - SoS = N2N3t - LS, где S = N3t + N4.

В результате в накапливающем сумматоре 13 с приходом переднего фронта сигнала синхронизации CLK на его управляющем входе устанавливается код числа

S1 = So + Δ1, который вычитается вычитателем 11 от кода числа N2 с получением результата N2-S1. Полученная разница как и в первом итерационном цикле умножается на произведение N3t с помощью умножителей 8 и 9. Очевидно на выходе последнего формируется код (N2-S1)N3t, а на выходе умножителя 10 - N4S1.

Тогда с выхода вычитателя 12 во втором цикле итерационного процесса в сумматор 13 поступает код приращения

Δ2 = (N2-S1)N3t - N4S1 =

= N2N3t - S1(N3t + N4) =

= N2N3t - S1S = N2N3t - (L + Δ1)S =

= N2N3t - LS - Δ1S = Δ1 - Δ1S = Δ1(1-S).

Код приращения Δ2 суммируется с содержимым сумматора 13 с приходом очередного сигнала синхронизации CLK, т. е. в накапливающем сумматоре 13 получается код числа

S2 = S1 + Δ2 = L + Δ1 + Δ2.

Тогда на выходе вычитателя 11 формируется код числа N2-S2, а на выходах умножителей 8, 9 и 10 - соответственно

(N2-S2)t, (N2-S2)N3t и N4S2.

В процессе выполнения третьей итерации с выхода вычитателя 12 в сумматор 13 поступает код приращения

Δ3 = (N2-S2)N3t - N4S2 =

= N2N3t - S2(N3t + N4) =

= N2N3t - S2S =

= N2N3t - (L + Δ1 + Δ2)S =

= N2N3t - LS - Δ1S - Δ2S =

= Δ1- Δ1S -Δ1(1-S)S =

= Δ1(1-S) - Δ1(1-S)S =

= Δ1(1-S)(1-S) = Δ1(1-S)2.

Код приращения Δ3 аналогично предыдущим итерациям суммируется с содержимым сумматора 13 с приходом очередного сигнала CLK, т. е. в накапливающем сумматоре 13 получается код числа

S3 = S2 + Δ3 = L + Δ1 + Δ2 + Δ3.

Тогда на выходе вычитателя 11 формируется код числа N2-S3, а на выходах умножителей 9 и 10 - соответственно (N2-S3)N3t и N4S3.

Четвертый цикл итерационного процесса характеризуется приращением сумматора 13 на величину

Δ4 = (N2-S3)N3t - N4S3 =

= N2N3t - S3(Nt3 + N4) =

= N2N3t - S3S =

= N2N3t - (L + Δ1+Δ2+Δ3)S =

= N2N3t - LS - Δ1S - Δ2S -Δ3S =

= Δ1-Δ1S-Δ1(1-S)S-Δ1(1-S)2S =

= Δ (1-S) - Δ (1-S)S -Δ (1-S)2S =

= Δ (1-S)(1-S)(1-S)S) =

= Δ1(1-S)2(1-S) = Δ1 (1-S)3.

Далее процесс продолжается по очередным итерациям.

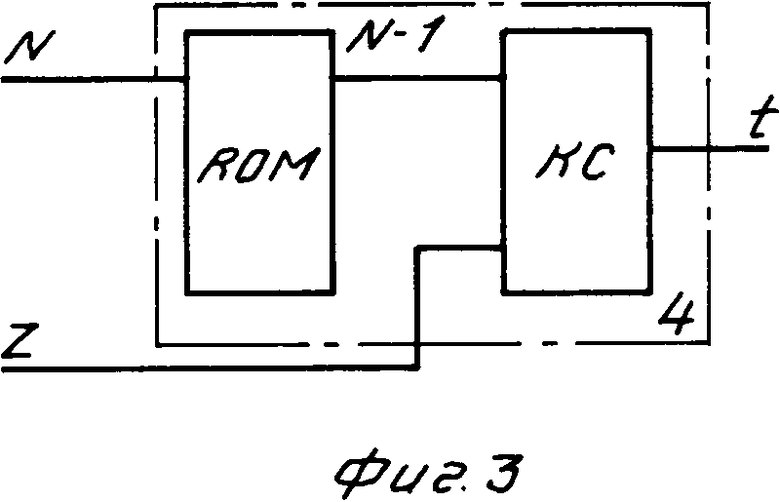

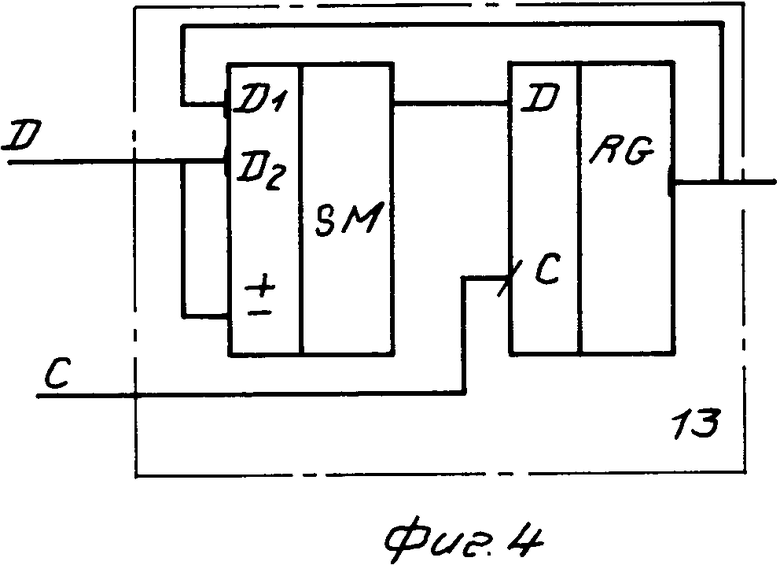

Все элементы предлагаемого устройства являются хорошо известными. Блок 2 может быть реализован, например, на основе схемы указателя старшей единицы; в качестве шифратора 3 можно использовать, например, ПЗУ; блок сдвига 4 может быть выполнен, например, на основе ПЗУ для получения кода N-1 и комбинационной схемы для выполнения операции сдвига, как показано на фиг. 3; сумматор 5 может быть реализован, например, на основе микросхемы К155ИМ3; умножители 7-10 могут быть выполнены, например, на основе матричных умножителей К1802ВР4 или К1802ВР5; вычитатели 11, 12 могут быть выполнены, например, на основе микросхемы К555ИМ7; накапливающий сумматор 13 может быть выполнен, например, на основе комбинационной схемы и регистра, причем комбинационная схема здесь представляет собой комбинированную схему сложения-вычитания, которая может быть реализована, например, на основе микросхемы сумматора-вычитателя К555ИМ7, а режим его работы определяется в соответствии со знаком кода числа на выходе вычитателя 12. Пример реализации такого накапливающего сумматора приведен на фиг. 4. Таким образом, накапливающий сумматор 13 может суммировать как положительные, так и отрицательные приращения, формируя при этом абсолютные значения вследствие отбрасывания знакового разряда результата на его выходе.

Естественно, что эти элементы легко реализуемы и в другой конструкторско-технологической среде проектирования, например на основе базового матричного кристалла или в виде специализированной интегральной схемы.

В основу работы устройства положен принцип вычисления мантиссы логарифма по основанию два с помощью дробно-рациональной аппроксимации с автоматической компенсацией задаваемых и вырабатываемых в процессе работы данных, приводящей к установлению результата при равенстве сигналов прямой и обратной связи, благодаря чему появление одиночных сбоев отрабатываются с восстановлением результата, при этом характеристика логарифма определяется номером самого старшего разряда аргумента.

Итерационный процесс работы устройства выполняется в соответствии с формулой

Sn = Sn-1 + (N2-Sn-1)N3t - N4Sn-1, (1) где n - номер текущей итерации.

На информационный вход накапливающего сумматора 13 в дальнейшем поступают коды приращений

Δ5= Δ1(1-S)4;

Δ6= Δ11(1-S)5;

Δ7= Δ1(1-S)6; Δn= Δ1(1-S)n-1 = Δ1(1-N3t - N4)n-1. (2)

Из выражения (2) следует, что при заданных значениях N3, N4 и 0≅t≅<N>1 получают сходящийся к нулю ряд приращений сумматора 13 независимо от числа L (код L может быть установлен в сумматоре 13, например, в результате сбоя). Тогда при нулевом приращении, т. е. Δn = 0, выполняется условие равенства Sn = Sn-1. Следовательно, на выходе накапливающего сумматора 13 формируется код числа в соответствии с выражением (1):

Sn = Sn-1 + (N2-Sn-1)N3t - N4Sn-1 =

= Sn-1 + N2N3t + Sn-1(N3t + N4).

Отсюда в установившемся режиме, характеризуемом нулевым приращением на входе сумматора 13, т. е. Sn = Sn-1, получают код числа

Sn = Sn + N2N3t - Sn(N3t + N4) или

Sn = Sn= (N2N3t)/(N3t+N4) .

Дальнейшее прохождение сигналов CLK приводит к фиксации в накапливающем сумматоре 13 полученного кода, так как последующие нулевые приращения не изменяют значение его кода. При этом на втором входе сумматора 5 присутствует код числа

N4Sn= (N2N3N4t)/(N3t+N4).

Код мантиссы М искомого логарифма формируется на выходе сумматора 5:

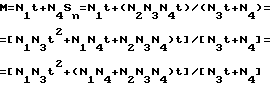

или при заданных значениях N1-N4

или при заданных значениях N1-N4

M= (0,25062t2+2,4548t)/(t+1,7053) (4)

Выражение (4) аппроксимирует функцию log2(1 + t) с абсолютной методической погрешностью, не превосходящей 1,38 ˙10-4.

Условием окончания итерационного процесса вычисления логарифма является равенство кодов чисел, поступающих на суммирующий и вычитающий входы вычитателя 12, т. е. окончание процесса вычисления мантиссы логарифма характеризуется поступлением нулевого кода с выхода вычитателя 12 на информационный вход сумматора 13.

Точность предлагаемого устройства для вычисления логарифма выше по сравнению с прототипом не менее чем в 100 раз за счет реализации сквозного дробно-рационального аппроксимирующего выражения более высокого порядка с меньшей методической погрешностью. Кроме того, предлагаемое устройство является более помехоустойчивым вследствие следящего режима работы при вычислении мантиссы логарифма благодаря наличию отрицательной обратной связи. В результате сбоя в сумматоре 13 может установиться любое случайное число L, при этом вследствие постоянного формирования приращений сумматора устройство стремится к восстановлению достоверного результата. Сбой в цепях блоков 2, 3, 4, 5, 7 ликвидируется с восстановлением сигналов. (56) Авторское свидетельство СССР N 849210, кл. G 06 F 7/556, 1980.

Авторское свидетельство СССР N 1027721, кл. G 06 F 7/556, 1982.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ АКТИВНОЙ МОЩНОСТИ | 1993 |

|

RU2074397C1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2006935C1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Устройство для потенцирования | 1990 |

|

SU1815635A1 |

| ЦИФРОВОЙ РЕГУЛЯТОР | 1992 |

|

RU2036502C1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2041499C1 |

| УСТРОЙСТВО ДЛЯ АППРОКСИМАЦИИ ФУНКЦИЙ | 1992 |

|

RU2010324C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИМВОЛЬНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2010319C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ | 1991 |

|

RU2029986C1 |

Изобретение относится к вычислительной технике, предназначено для вычисления логарифма по основанию два от чисел, представленных параллельным двоичным кодом, и может быть использовано в цифровых системах обработки данных. Целью изобретения является повышение точности. Устройство содержит вход 1 кода аргумента, блок 2 выделения старшего разряда, шифратор 3, блок 4 сдвига, сумматор 5, причем выходы шифратора 3 и сумматора 5 являются выходами 6 устройства, умножители 7 - 10, вычитатели 11, 12, накапливающий сумматор 13, входы 14, 15, 16, 17 кодов и вход 18 синхронизации устройства. Сущность изобретения состоит в создании устройства для вычисления логарифма по основанию два с большей точностью, определяемой применением дробно-рационального выражения, аппроксимирующего его мантиссу, с использованием итерационного метода реализации. Цель изобретения достигнута за счет введения четырех умножителей, двух вычитателей, накапливающего сумматора и новых связей. Предлагаемое техническое решение характеризуется следующей совокупностью признаков: алгоритм функционирования определяется решением итерационного уравнения, а не определением поправки логарифма, мантисса логарифма определяется с помощью дробно-рациональной аппроксимации на всем диапазоне ее изменения, а не линейных функций, каждая из которых соответствует своему диапазону. 4 ил.

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА, содержащее блок выделения старшего разряда, шифратор, блок сдвига и сумматор, причем вход кода аргумента устройства соединен с входом блока выделения старшего разряда и информационным входом блока сдвига, управляющий вход которого соединен с выходом блока выделения старшего разряда и входом шифратора, выход которого и выход сумматора являются выходами устройства, отличающееся тем, что, с целью повышения точности, оно содержит четыре умножителя, два вычитателя и накапливающий сумматор, причем выход блока сдвига соединен с первыми входами первого и второго умножителей, выходы которых соединены соответственно с первыми входами сумматора и третьего умножителя, второй вход которого соединен с первым входом константы устройства, второй и третий входы константы которого соединены соответственно с вторым входом первого умножителя и входом уменьшаемого первого вычитателя, выход и вход вычитаемого которого соединены соответственно с вторым входом второго умножителя и выходом накапливающего сумматора, информационный вход которого соединен с выходом второго вычитателя, входы уменьшаемого и вычитаемого которого соединены соответственно с выходами третьего и четвертого умножителей, первый и второй входы которого соединены соответственно с выходом накапливающего сумматора и четвертым входом константы устройства, синхровход которого соединен с одноименным входом накапливающего сумматора, выход четвертого умножителя соединен с вторым входом сумматора.

Авторы

Даты

1994-01-30—Публикация

1991-04-02—Подача