Изобретение относится к вычислительной технике и может быть использовано для контроля обмена информацией между источником информации и устройствами обработки.

Известно устройство для контроля [1], содержащее элементы ИЛИ, элементы задержки, элементы И, триггеры блокировки и управления, регистры, элементы памяти, счетчик импульсов.

Данное устройство осуществляет контроль времени выработки кодов управляющих сигналов устройством управления (управляющим автоматом - УА) и времени поступления сигналов ответных реакций объекта управления (операционного автомата - ОА). Контроль в этом устройстве производится непосредственно в процессе работы контролируемых устройств. При этом объект управления и устройство управления контролируются как по временному, так и по информационному параметрам.

Недостатком устройства [1] является низкая достоверность контроля, обусловленная тем, что при контроле объекта управления контролю подлежат лишь заранее известные логические условия (ЛУ), принимающие в зависимости от выработанного кода управляющих сигналов (КУС) фиксированные значения.

Наиболее близким по сущности и технической реализации к заявляемому устройству является устройство для контроля [2], выбранное в качестве прототипа и содержащее триггер управления, триггер блокировки, счетчик, первый и второй элементы задержки, первый и второй элементы И, первый, второй и третий регистры, первый, второй и третий блоки памяти, первую и вторую группы соответственно из m + n и m элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (n - число разрядов счетчика, m - разрядность вектора логических условий), первую и вторую группы соответственно из m + n и m элементов И, причем выход переполнения счетчика является выходом сигнала превышения заданного интервала времени контроля устройства, выход первого элемента И является выходом ошибки устройства, вход синхроимпульсов устройства соединен с первым входом второго элемента И, вход запуска устройства соединен с первым входом первого элемента ИЛИ, вход сброса устройства соединен с первым входом второго элемента ИЛИ, группа входов кода управляющих сигналов соединена с второй группой входов первого элемента ИЛИ и с группой информационных входов первого регистра, группа входов вектора логических условий устройства соединена с группой информационных входов второго регистра и с третьей группой входов первого элемента И ЛИ, выход которого соединен с вторым входом второго элемента ИЛИ, и через первый и второй элементы задержки соединен с R-входом триггера блокировки, S-вход которого соединен с выходом второго элемента ИЛИ, инверсный выход триггера блокировки соединен с вторым входом второго элемента И, выход первого элемента задержки соединен с первым входом первого элемента И и с первым входом третьего элемента ИЛИ, выход второго элемента И соединен со счетным входом счетчика, вход установки в "0" которого соединен с выходом третьего элемента ИЛИ, второй вход которого соединен с входом сброса устройства, прямой выход триггера управления соединен с входом синхронизации второго регистра и со старшим разрядом адресных входов первого и второго блоков памяти, у которых младшие разряды адресных входов объединены и соединены с группой разрядных выходов первого регистра и с группой адресных входов третьего блока памяти, информационные выходы первого блока памяти соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, информационные выходы второго блока памяти соединены с первыми входами элементов И первой группы, вторые входы которых соединены с соответствующими выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выходы элементов И первой группы соединены с соответствующими входами четвертого элемента ИЛИ, вход ввода устройства соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с входом сброса устройства, выход пятого элемента ИЛИ соединен с S-входом триггера управления, R-вход которого соединен с входом разрешения устройства, инверсный выход триггера управления соединен с входом синхронизации первого регистра и третьего регистра, информационные входы которого соединены с соответствующими выходами второго регистра, R-входы первого, второго и третьего регистров соединены с входом сброса устройства, разрядные выходы третьего регистра соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вторые входы которых соединены с вторыми входами первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы и с группой выходов второго регистра, информационные выходы третьего блока памяти соединены с первыми входами элементов И второй группы, вторые входы которых соединены с соответствующими выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, выходы элементов И второй группы соединены с соответствующими входами четвертого элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, выходы разрядов счетчика соединены с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы с (m + 1)-го элемента по (m + n)-й.

В отличие от устройства [1] прототип позволяет контролировать не только заранее известные инварианты логических условий, вырабатываемых объектом управления, но и инварианты, определяемые в ходе контроля. То есть прототип контролирует те ЛУ, которые не меняются под воздействием данного КУС, но априори нельзя указать соответствующие им фиксированные значения (0 или 1).

К свойствам, характеризующим прототип, относится прежде всего низкая достоверность контроля, так как он не позволяет выявлять ошибки типа зацикливания в случае, если граф-схема алгоритма (ГСА) контролируемого устройства управления содержит "ждущие" вершины или циклы и заранее известно время нахождения УА в состоянии цикла.

Другим свойством прототипа является невозможность выявления ошибочного перехода УА в недопустимое состояние, которое достижимо при наборе значений ЛУ, выработанном непосредственно перед переходом, например, невозможно выявить пропуск КУС, расположенного в линейной части алгоритма. Кроме того, прототип может быть использован лишь для контроля устройств, описываемых автоматной моделью без заключительного состояния, то есть функционирующих циклически, что сужает область применения прототипа.

Цель изобретения - создание устройства, позволяющего с высокой достоверностью контролировать последовательность допустимых переходов состояний, задаваемых ГСА управляющего устройства, времена поступления КУС, ЛУ и время функционирования циклов и "ждущих" вершин на ГСА.

Сущность технического решения заключается в том, что в заявляемое устройство для контроля, содержащее два триггера, два элемента И, четыре элемента ИЛИ, три регистра и первый счетчик, прямой выход первого триггера соединен с первой группой адресных входов блока памяти, информационный вход устройства соединен с первым информационным входом первого регистра, первый выход которого соединен с информационным входом второго регистра, вход обнуления которого соединен с входом "Сброс" устройства и входом обнуления третьего регистра, вход синхроимпульсов устройства соединен с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, выход переполнения первого счетчика является выходом сигнала превышения заданного интервала времени контроля устройства, введены второй счетчик, формирователь импульсов, два элемента И-НЕ, причем вход "Ввод" устройства соединен с первым входом второго элемента И и инверсным входом обнуления первого триггера, прямой выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с синхровходом второго регистра, выход которого соединен с второй группой адресных входов блока памяти, инверсный выход первого триггера соединен с первым входом второго элемента ИЛИ, выход которого соединен с синхровходом третьего регистра, выход которого соединен с третьей группой адресных входов блока памяти, первый и второй выходы блока памяти соединены с первыми входами соответственно третьего и четвертого элементов ИЛИ, вход "Вывод" устройства соединен с вторым входом второго элемента И и инверсным входом установки в единицу первого триггера, вход синхроимпульсов устройства соединен также с тактовым входом формирователя импульсов, первый выход которого соединен с вторыми входами первого, второго, третьего и четвертого элементов ИЛИ, второй выход формирователя импульсов соединен с первым входом первого элемента И-НЕ и с входом установки в единицу второго триггера, второй информационный вход первого регистра соединен с выходами разрядов второго счетчика, первый выход первого регистра соединен также с информационным входом третьего регистра и с четвертой группой адресных входов блока памяти, второй выход первого регистра соединен с пятой группой адресных входов блока памяти, вход "Сброс" устройства также соединен с вторым входом первого элемента И-НЕ и с первым входом второго элемента И-НЕ, параллельный выход разрядов первого счетчика соединен с шестой группой адресных входов блока памяти, прямой выход второго триггера соединен с вторым входом первого элемента И и с входом разрешения формирователя импульсов, выход второго элемента И соединен с входом обнуления второго триггера и с синхровходом первого регистра, выход первого элемента И соединен также со счетным входом второго счетчика, выход первого элемента И-НЕ соединен с входом обнуления первого счетчика, выход третьего элемента ИЛИ является выходом ошибки устройства, выход четвертого элемента ИЛИ соединен с вторым входом второго элемента И-НЕ, выход которого соединен с входом обнуления второго счетчика.

Техническим результатом является высокая достоверность контроля, достигаемая за счет контроля последовательности допустимых переходов состояний управляющего устройства и контроля временных параметров алгоритма функционирования ОУ и УА, в частности контроля времени функционирования циклов и "ждущих" вершин на ГСА. Кроме того, в качестве контролируемых устройств могут быть автоматы, функционирующие циклически или с заключительным состоянием, а также сложные устройства, например, ЭВМ, управляющая дискретным технологическим процессом.

Повышение достоверности контроля достигается за счет использования более полного по сравнению с прототипом набора контролируемых инвариантов, в качестве которых выступают заданные интервалы времени для выполнения операций, заданные для каждого КУС ожидаемые значения ЛУ, а также набора кодов состояний, которые могут предшествовать данному состоянию, отождествляемому с выработанным КУС.

С допустимыми наборами значений контролируемых информационных и временных параметров сопоставляются наборы значений разрядов соответствующих групп адресных входов блока памяти. Для контроля последовательности допустимых переходов состояний, отождествляемых с КУС, используется второй регистр, в котором хранится предыдущий КУС, а текущий КУС заносится в первый регистр.

Выход второго регистра соединен с второй группой адресных входов блока памяти. Первый выход первого регистра соединен также с информационным входом третьего регистра и с четвертой группой адресных входов блока памяти. Эти признаки обеспечивают контроль допустимых сочетаний значений, поступающих в первый и второй регистры и определяющих адреса ячеек блока памяти, так как при прошивке памяти в эти ячейки заносится признак правильной работы, а в ячейки, адресуемые недопустимыми сочетаниями значений, заносится признак ошибки.

Для обеспечения контроля времени функционирования циклов и "ждущих" вершин (второй временной параметр) заданный для цикла (или "ожидания") интервал времени представляется в виде допустимого набора значений разрядов второго счетчика, определяющих адреса ячеек блока памяти, в которые при прошивке заносится признак правильности работы. Так как второй информационный вход первого регистра соединен с параллельным выходом разрядов второго счетчика и второй выход первого регистра соединен с пятой группой адресных входов блока памяти, а первый и второй выходы блока памяти соединены с первыми входами соответственно третьего и четвертого элементов ИЛИ и выход третьего элемента ИЛИ является выходом ошибки устройства, то существует наличие причинно-следственной связи между указанными существенными признаками и техническим результатом - высокой достоверностью контроля.

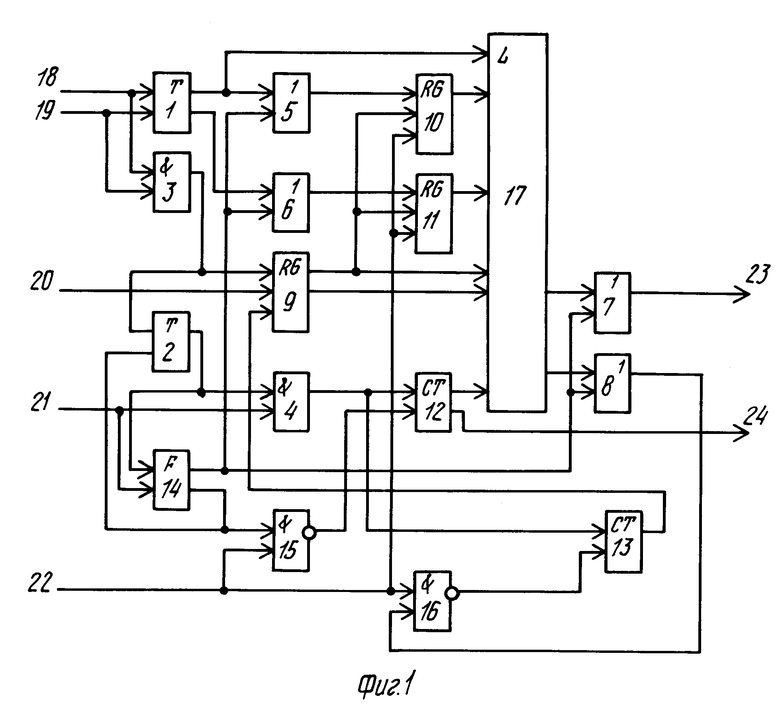

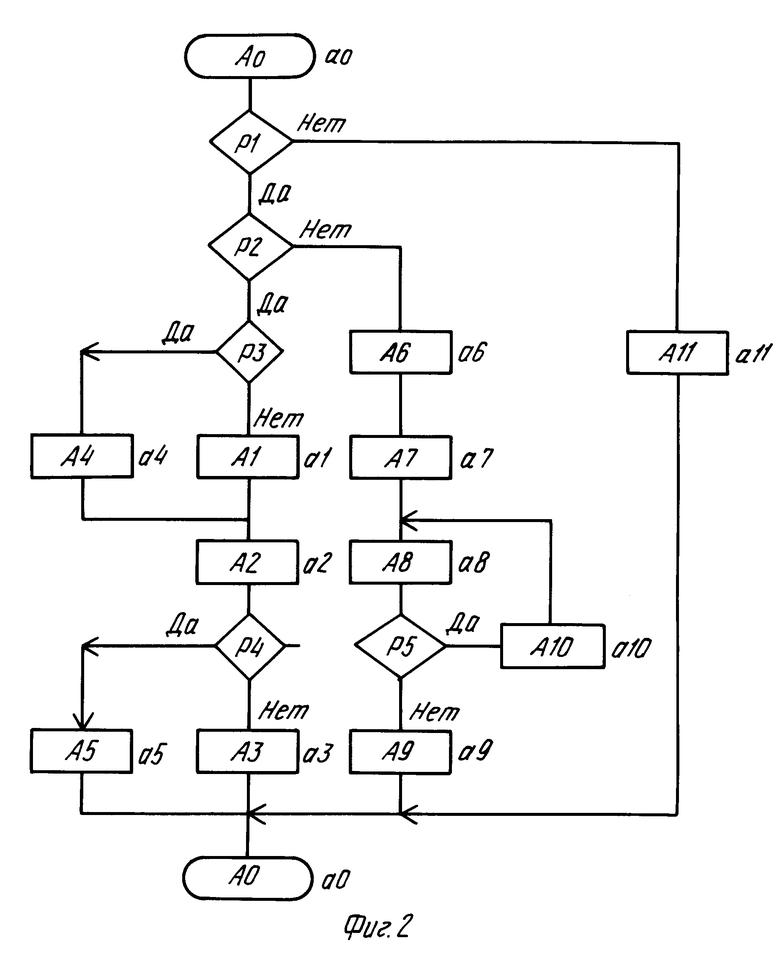

На фиг.1 представлена схема предлагаемого устройства; на фиг.2,3 - алгоритмы работы устройства.

Устройство для контроля (фиг.1) содержит первый и второй триггеры 1 и 2, первый и второй элементы И 3 и 4, первый, второй, третий и четвертый элементы ИЛИ 5,6,7 и 8, первый, второй и третий регистры 9, 10 и 11, первый и второй счетчики 12 и 13, формирователь 14 импульсов, первый и второй элементы И-НЕ 15 и 16, блок 17 памяти, вход "Ввод" 18 устройства, вход "Вывод" 19 устройства, информационный вход 20 устройства, вход 21 синхроимпульсов устройства, вход "Сброс" 22 устройства, выход 23 ошибки устройства и выход 24 сигнала превышения заданного интервала времени контроля устройства.

Устройство работает следующим образом.

В исходном состоянии кратковременным сигналом сброса с входа "Сброс" 22 устройства регистры 10 и 11 устанавливаются в нулевое состояние. Этим же сигналом через первый элемент И-НЕ 15 первый счетчик 12 устанавливается в нулевое состояние и через второй элемент И-НЕ 16 второй счетчик 13 устанавливается в нулевое состояние.

Единичное состояние с выхода второго триггера 2 поступает на первый вход второго элемента И 4 и первый вход формирователя 14 импульса, запрещая тем самым работу формирователя 14 импульсов. Состояние логической единицы на первом входе элемента И 4 разрешает поступление синхроимпульсов через этот элемент с входа 21 устройства на счетный вход первого счетчика 12.

При поступлении на УУ по входу "Ввод" 18 устройства сигнала низкого уровня "Ввод" выполняются следующие действия.

Сигнал "Ввод" поступает на инверсный вход обнуления первого триггера 1 и устанавливает на его прямом выходе состояние логического нуля, а на инверсном выходе - состояние логической единицы. Сигнал низкого уровня с прямого выхода триггера 1 поступает на первый вход первого элемента ИЛИ 5, разрешая прохождение через него сигнала низкого уровня с первого выхода формирователя 14 импульсов, и на первый адресный вход блока 17 памяти. Сигнал высокого уровня с инверсного выхода триггера 1 поступает на первый вход второго элемента ИЛИ 6, запрещая прохождение через него сигнала низкого уровня с первого выхода формирователя 14 импульсов.

Сигнал "Ввод" поступает через первый элемент И 3 на тактовый вход первого регистра 9, осуществляя запись в него информации с информационного входа 20 и с выхода счетчика 13. Одновременно этим сигналом второй триггер 2 устанавливается в нулевое состояние.

Сигнал логического нуля на выходе триггера 2 поступает: на первый вход второго элемента И 4, запрещая прохождение синхроимпульсов через этот элемент с входа 21 устройства на счетный вход первого счетчика 12; на первый вход формирователя 14 импульсов, разрешая тем самым его работу.

С первого выхода (ЛУ) и с второго выхода (информация со счетчика 13) регистра 9 информация поступает на соответствующие адресные входы блока 17. Кроме того, информация с первого выхода регистра 9 поступает на информационные входы регистров 10 и 11. Информация на первом и втором выходах регистра 9, состояние на прямом выходе триггера 1 и информация на выходе первого счетчика 12 контролируется блоком 17 памяти на соответствие ГСА УУ по методике, описанной выше, в зависимости от предыдущих значений КУС и ЛУ, поступающих с выходов регистров 10 и 11. В случае несоответствия информации заданной на первом выходе блока 17 памяти устанавливается сигнал "Ошибка" (состояние логического нуля), поступающий на первый вход третьего элемента ИЛИ 7. Тем самым разрешается прохождение через этот элемент сигнала с первого выхода формирователя 14 импульсов на выход 23 ошибки устройства.

В противном случае на первом выходе блока 17 памяти устанавливается единичное состояние, запрещая прохождение сигнала с первого выхода формирователя 14 импульсов на выход 23 ошибки устройства.

Через время, необходимое для срабатывания комбинационной схемы, на первом выходе формирователя 14 импульсов вырабатывается сигнал низкого уровня. При появлении этого сигнала выполняются следующие действия: на выходе третьего элемента ИЛИ 7 и выходе 23 "Ошибка" появляется сигнал ошибки низкого уровня, если на первом выходе блока 17 памяти было установлено состояние логического нуля; на выходе четвертого элемента ИЛИ 8 появляется сигнал сброса низкого уровня, если на втором выходе блока 17 памяти было установлено состояние логического нуля, которым через второй элемент И-НЕ 16 осуществляется сброс второго счетчика 13; фронтом этого сигнала (переход из нуля в единицу) происходит запись информации из первого регистра 9 во второй регистр 10, так как на прямом выходе первого триггера 1 и первом входе первого элемента ИЛИ 5 установлено состояние логического нуля.

После завершения сигнала на первом выходе формирователя 14 импульсов, на втором его выходе вырабатывается сигнал низкого уровня. При появлении этого сигнала выполняются следующие действия: через первый элемент И-НЕ 15 осуществляется сброс первого счетчика 12; фронтом этого сигнала (переход из нуля в единицу) происходит запись логической единицы во второй триггер 2.

Состояние логической единицы на выходе второго триггера 2 разрешает поступление синхроимпульсов с входа 21 устройства через второй элемент И 4 на счетный вход первого счетчика 12 и запрещает работу формирователя 14 импульсов. Тем самым устройство готово для контроля следующих значений, поступающих из УУ.

При поступлении из УУ по входу 19 устройства сигнала низкого уровня "Вывод" выполняются следующие действия.

Сигнал "Вывод" поступает на инверсный вход установки единицы первого триггера 1 и устанавливает на его прямом выходе состояние логической единицы, а на инверсном выходе - состояние логического нуля. Сигнал высокого уровня с прямого выхода триггера 1 поступает на первый вход первого элемента ИЛИ 5, запрещая прохождение через него сигнала низкого уровня с первого выхода формирователя 14 импульсов, и на первый адресный вход блока 17 памяти.

Сигнал низкого уровня с инверсного выхода триггера 1 поступает на первый вход второго элемента ИЛИ 6, разрешая прохождение через него сигнала низкого уровня с первого выхода формирователя 14 импульсов.

Сигнал "Вывод" поступает через первый элемент И 3 на тактовый вход первого регистра 9, осуществляя запись в него информации с информационного входа 20 и с выхода счетчика 13. Одновременно этим сигналом второй триггер 2 устанавливается в нулевое состояние.

Сигнал логического нуля на выходе триггера 2 поступает: на первый вход второго элемента И 4, запрещая прохождение синхроимпульсов через этот элемент с входа 21 устройства на счетный вход первого счетчика 12; на первый вход формирователя 14 импульсов, разрешая тем самым его работу.

С первого выхода (КУС) и с второго выхода (информация со счетчика 13) регистра 9 информация поступает на соответствующие адресные входы блока 17 памяти. Кроме того, информация с первого выхода регистра 9 поступает на информационные входы регистров 10 и 11. Информация на первом и втором выходах регистра 9, состояние на прямом выходе триггера 1 и информация на выходе первого счетчика 12 контролируются блоком 17 памяти на соответствие ГСА УУ по методике, описанной выше, в зависимости от предыдущих значений КУС и ЛУ, поступающих с выходов регистров 10 и 11. В случае несоответствия информации, заданной на первом выходе блока 17 памяти, устанавливается сигнал "Ошибка" (состояние логического нуля), поступающий на первый вход третьего элемента ИЛИ 7. Тем самым разрешается прохождение через этот элемент сигнала с первого выхода формирователя 14 импульсов на выход 23 ошибки устройства. В противном случае на первом выходе блока 17 памяти устанавливается единичное состояние, запрещая прохождение сигнала с первого выхода формирователя 14 импульсов на выход 23 ошибки устройства.

Через время, необходимое для срабатывания блока памяти, на первом выходе формирователя 14 импульсов вырабатывается сигнал низкого уровня. При появлении этого сигнала выполняются следующие действия: на выходе третьего элемента ИЛИ 7 и выходе 23 "Ошибка" появляется сигнал ошибки низкого уровня, если на первом выходе комбинационной схемы блока 17 было установлено состояние логического нуля; на выходе четвертого элемента ИЛИ 8 появляется сигнал сброса низкого уровня, если на втором выходе блока 17 памяти было установлено состояние логического нуля, которым через второй элемент И-НЕ 16 осуществляется сброс второго счетчика 13; фронтом этого сигнала (переход из нуля в единицу) происходит запись информации из первого регистра 9 во второй регистр 10, так как на прямом выходе первого триггера 1 и первом входе первого элемента ИЛИ 5 установлено состояние логического нуля.

После завершения сигнала на первом выходе формирователя 14 импульсов на втором его выходе вырабатывается сигнал низкого уровня. При появлении этого сигнала выполняются следующие действия:

через первый элемент И-НЕ 15 осуществляется сброс первого счетчика 12; фронтом этого сигнала (переход из нуля в единицу) происходит запись логической единицы во второй триггер 2.

Состояние логической единицы на выходе второго триггера 2 разрешает поступление синхроимпульсов с входа 21 устройства через второй элемент И 4 на счетный вход первого счетчика 12 и запрещает работу формирователя 14 импульсов. Тем самым устройство готово для контроля следующих значений, поступающих из УУ.

Обмен информацией между УУ и ОУ при их реализации на устройствах, описываемых автоматной моделью без заключительного состояния, может быть представлен следующим образом.

В начале работы УУ вырабатывает сигнал запуска, который поступает в ОУ, ОУ через некоторое время, отводимое на выполнение операций, связанных с обработкой поступившего на него сигнала, формирует сигнал ответной реакции (вектор логических условий), поступающий на УУ, УУ, реализуя алгоритм управления с учетом поступившего на него сигнала от ОУ, через заданное время вырабатывает код управляющих сигналов, поступивших на ОУ. Последний через заданное для данного КУС время выполнения операций формирует новый вектор ЛУ, который поступает в УУ. Сигналы КУС сопровождаются стробирующим сигналом "Вывод", сигналы ЛУ - стробирующим сигналом "Ввод". Обмен сигналами продолжается до поступления сигнала сброса. Проверяя с помощью устройства для контроля наличие на каждый КУС УУ ответной реакции ОУ и наличие на этот сигнал нового КУС и осуществляя при этом анализ как временного, так и информационного параметров этих сигналов, можно осуществить контроль функционирования УУ и ОУ.

В случае использования в качестве УУ микроЭВМ, обмен информацией между УУ и ОУ можно представить следующим образом. МикроЭВМ осуществляет выдачу КУС на ОУ, стробируя его сигналом "Вывод", получающимся в результате выработки соответствующего адреса и сигнала вывода, взятого непосредственно с процессорного модуля, после этого микроЭВМ может переключаться на выполнение другой задачи. После того, как ОУ выполнит команду, оно выдает запрос на обслуживание. Через некоторое время микроЭВМ осуществляет ввод с ОУ ЛУ, характеризующих результат выполнения операции, стробируя его сигналом "Ввод", получающимся в результате выработки соответствующего адреса и сигнала чтения. Затем микроЭВМ вырабатывает новый КУС и выдает его на ОУ.

При контроле УУ по информационному параметру осуществляется проверка на совпадение компонент вектора ЛУ, под воздействием которого выработался данный КУС с логическими условиями, которые являются постоянными и однозначно определенными для всех векторов ЛУ, под воздействием которых мог выработаться в УУ данный КУС. Например, УУ может перейти в состояние а1 (фиг.2) и выработать КУС А1. В зависимости от предыстории работы цифрового устройства под действием только векторов ЛУ: 10100, 11100, 10101. Для этих векторов первый, третий и четвертый (считая слева) всегда постоянны и равны соответственно 1,1,0. Второй и пятый разряды в составе различных векторов ЛУ принимают различные значения. Контролю подлежат заранее известные для данного КУС значения ЛУ. При этом в соответствующей строке в табл.5 в колонке, где указаны ожидаемые значения логических условий, записывается код "1 * 10 *". Знак "*" означает значение 0 или 1.

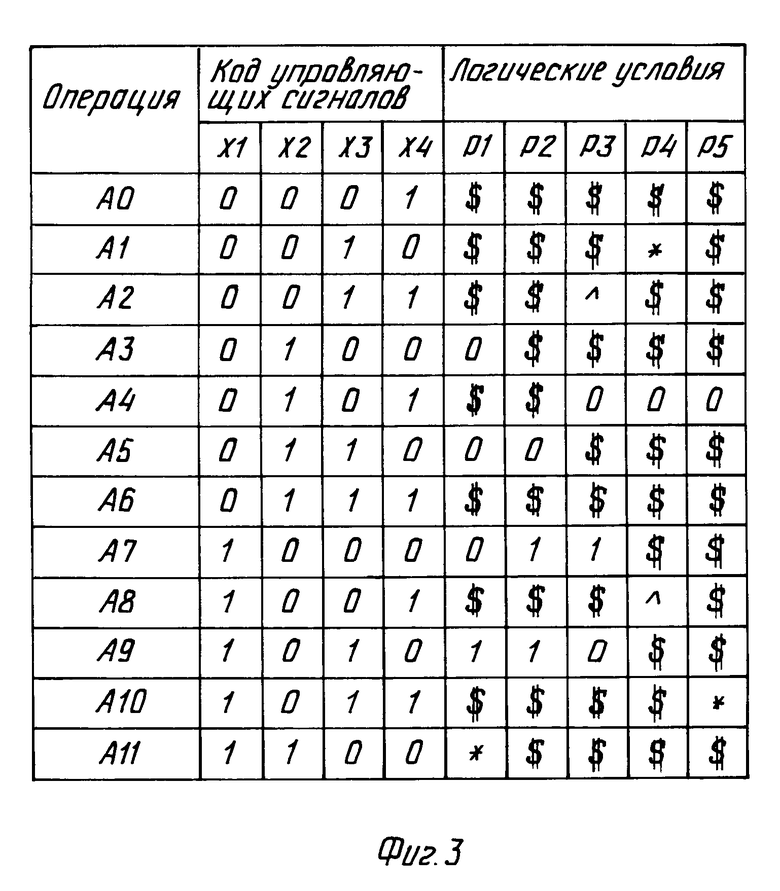

Контроль ОУ по информационному параметру осуществляется подобным образом. Контролю подлежат постоянные и заранее определенные логические условия для всех векторов ЛУ, которые могут быть сформированы ОУ как реакция на один и тот же КУС. Различие в этих векторах ЛУ обусловлено предысторией работы цифрового устройства. Кроме того, при контроле ОУ по информационному параметру дополнительно контролируются те логические условия, составляющие вектор ЛУ для данного КУС, которые также инвариантны к этому КУС (т.е. данный КУС не вызывает их изменения), однако в различных векторах ЛУ они могут принимать (в зависимости от предыстории) различные значения. Например, если известно по табл.4, что среди пяти логических условий Р1,...,Р5 КУС А1 вызывает изменение лишь первого, второго и пятого, то контролируя инвариантные относительно КУС А1 логические условия Р3, Р4 до поступления этого КУС на ОУ и после реакции на него, можно осуществить дополнительный контроль функционирования ОУ. Если КУС вызывает установку логического условия в конкретное состояние, то в соответствующей позиции указывается это значение (1 или 0), если логическое значение сохраняется, то указывается "$", если инвертируется, то указывается "0".

Также при контроле УУ по информационному параметру осуществляется проверка принадлежности КУС предыдущего состояния к группе КУС, которые могут ему предшествовать.

Контроль по первому временному параметру производится следующим образом. На формирование УУ КУС, равно как и формирование ОУ ЛУ, отводится определенный временной диапазон, при этом контролю подлежат лишь те разряды кода, снимаемого со счетчика 12, которые определены. Например, если возможное время формирования ОУ ЛУ для данного КУС составляет 12-15 Мкс, то при длительности синхроимпульсов, поступающих на вход 21 устройства и счетный вход первого счетчика 12, равной 1 Мкс, на выходе счетчика 12 должен быть сформирован при нормальном функционировании ОУ любой из кодов 12, 13, 14, 15. В двоичном представлении: 1100, 1101, 1110, 1111. В этом случае определены лишь два старших разряда и в соответствующей строке табл.2 в колонке, где указан первый временной параметр, записывается "11**".

В устройстве производится дополнительный временной контроль циклов и "ждущих" вершин на ГСА контролируемого устройства (второй временной параметр). Контроль по второму временному параметру производится следующим образом. На нахождение УУ в каком-либо цикле или в "ждущей" вершине алгоритма отводится определенный временной диапазон. При этом контролю подлежат лишь те разряды кода, снимаемого с второго выхода первого регистра 9, которые определены. Например, если верхняя граница этого времени для указанных участков алгоритма известна и составляет, например, 7 Мс, то в случае "зацикливания" УУ на выходе счетчика 13 появится код, превышающий 7, который записывается на второй выход первого регистра 9. В этом случае в соответствующей строке табл.5 в колонке, где указан второй временной параметр, записывается значение, не большее 7 (например, в двоичном представлении - 0***).

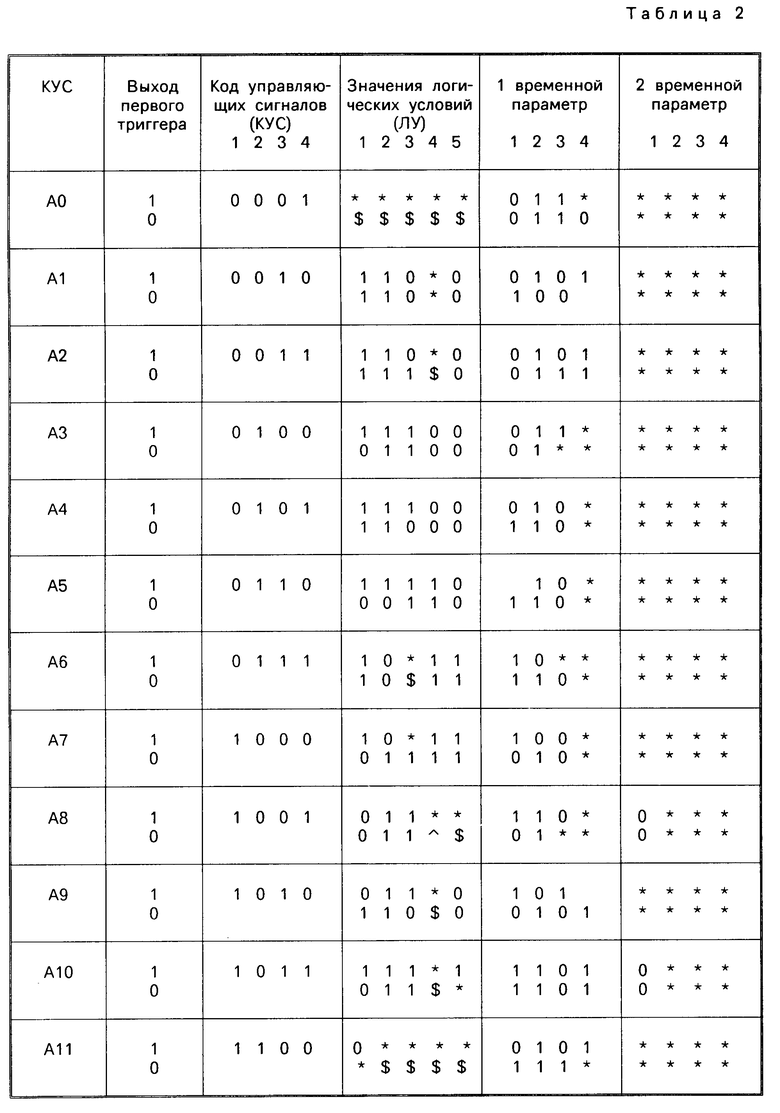

В качестве примера рассмотрим реализацию блока 17 памяти на ПЗУ для алгоритма, представленного на фиг.2. Таблица для программирования ПЗУ формируется следующим образом. Сначала составляется таблица ожидаемых значений КУС, ЛУ и временных параметров (табл.2).

Для нахождения неизменяемых значений векторов логических условий, соответствующих кодам управляющих сигналов, используют следующую методику. Находят объединенные отмечающие множества M(i)-множества значений векторов логических условий, которые могут появляться на входе УУ в результате выполнения операций ОУ под действием i-го кода управляющих сигналов. Находят отмечающие множества K(i)-множества значений логических условий, под воздействием одного из которых УУ перешел в i-состояние.

В исходном состоянии УУ формирует КУС АО, находится в состоянии аО (фиг. 2). ОУ вырабатывает вектор логических условий Р(ИСХ) = (00011). Таким образом первоначальное отмечающее множество для УУ - М(0,0) = Р(ИСХ) = (00011), а начальное значение вектора логических условий, под воздействием которого вырабатывается следующий КУС, будет К(0,0) = (00011). УУ в состоянии аО вырабатывает КУС АО и в ОУ выполняется операция АО, которая не изменяет логических условий (фиг.3), поэтому отмечающее множество не расширяется: М(1,0) = (00011). По алгоритму фиг.2 УУ может перейти только в состоянии а11, вырабатывая КУС А11 (так как Р1 = 0) и, следовательно К(0,11) = (00011). После выполнения операции А11 логическое условие Р1 может принимать любое значение: "0" или "1". Поэтому отмечающее множество М(1,0) расширяется: М(2,0) = (00011, 10011). В случае значений вектора логических условий Р = (00011) УУ вырабатывает КУС А11 и расширения, отмечающего множество К(0,11), не произойдет. В случае значений вектора логических условий Р = (00011) УУ вырабатывает КУС А6. Следовательно К(0,6) = (10011). Операция А6 не меняет логических условий.

Поэтому М(0,6) = (10011). Далее в соответствии с алгоритмом управления УУ вырабатывает КУС А7. Таким образом К(0,7) = (10011). Операция А7 изменит логические условия Р1, Р2, Р3 (табл.5) и, соответственно, М(0,7) = (01111), УУ, после получения этого вектора логических условий вырабатывается КУС А8 и К(0,8) = (01111).

Рассматривая далее работу УУ по алгоритму, представленному на фиг.2, получают объединенные отмечающие множества: МО, М1,...,М11 и КО, К1,...К11. Для более компактного представления значения вектора логических условий, задают объединенные отмечающие множества в восьмеричной системе счисления.

МО = 03, 07, 14, 23, 27, 30, 32, 34 КО = 03, 07, 14, 23, 27, 30, 32, 34

М1 = 30, 32 К1 = 30, 32

М2 = 34, 36 К2 = 30, 32

М3 = 14 К3 = 34

М4 = 30 К4 = 34

М5 = 06 К5 = 36

М6 = 23, 27 К6 = 23, 27

М7 = 17 К7 = 23, 27

М8 = 14, 15, 16, 17 К8 = 14, 15, 16, 17

М10 = 14, 15, 16, 17 К10 = 15, 17

М11 = 03, 07, 14, 23, 27, 34 К11 = 03, 07, 14

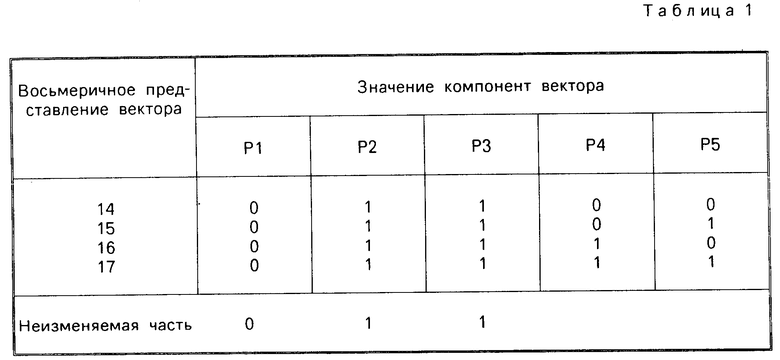

После получения объединенных множеств МО, М1,...М11 и КО, К1,...К11 нетрудно определить для каждого отмечающего множества постоянные значения логических условий (неизменяющиеся компоненты векторов). В качестве примера рассмотрим множество М8 = (14, 15, 16, 17). Смысл этого объединенного отмечающего множества в том, что УУ, выработавший КУС А8, может получить в ответ лишь следующие векторы логических условий, приведенные в табл.1.

Отсюда видно, что только условия Р1, Р2, Р3 являются не изменяющимися и заранее известными для данного КУС, а Р4, Р5 могут принимать значения "0" или "1". Аналогичным образом для каждого объединенного отмечающего множества можно получить неизменяющиеся значения логических условий.

Используя полученные значения, а также учитывая времена формирования управляющих сигналов в управляющем устройстве и времена выполнения операций операционным устройством, несложно построить табл.2. Здесь "1" в колонке значения управляющего триггера указывает, что в данный момент анализируется информация, определяемая по отмечающему множеству M(i), о постоянных значениях векторов логических условий, которые могут появиться на входе УУ после выполнения операций ОУ. "0" в колонке значений управляющего триггера указывает, что в данный момент анализируется информация, определяемая по отмечающему множеству K(i), о постоянных значениях векторов логических условий, которые могут поступить на вход управляющего устройства для выработки им следующего КУС.

Кроме того, в табл.2 некоторые разряды в строках, где в колонке "выход первого триггера" стоит значение "1", обозначены "$" и "^", где "$" - это значение логического условия, на которое управляющий автомат при выполнении i-го КУС не оказывает никакого воздействия и оно сохраняет прежнее значение; "^" - означает, что управляющее устройство оказывает на это логическое условие инвертирующее воздействие.

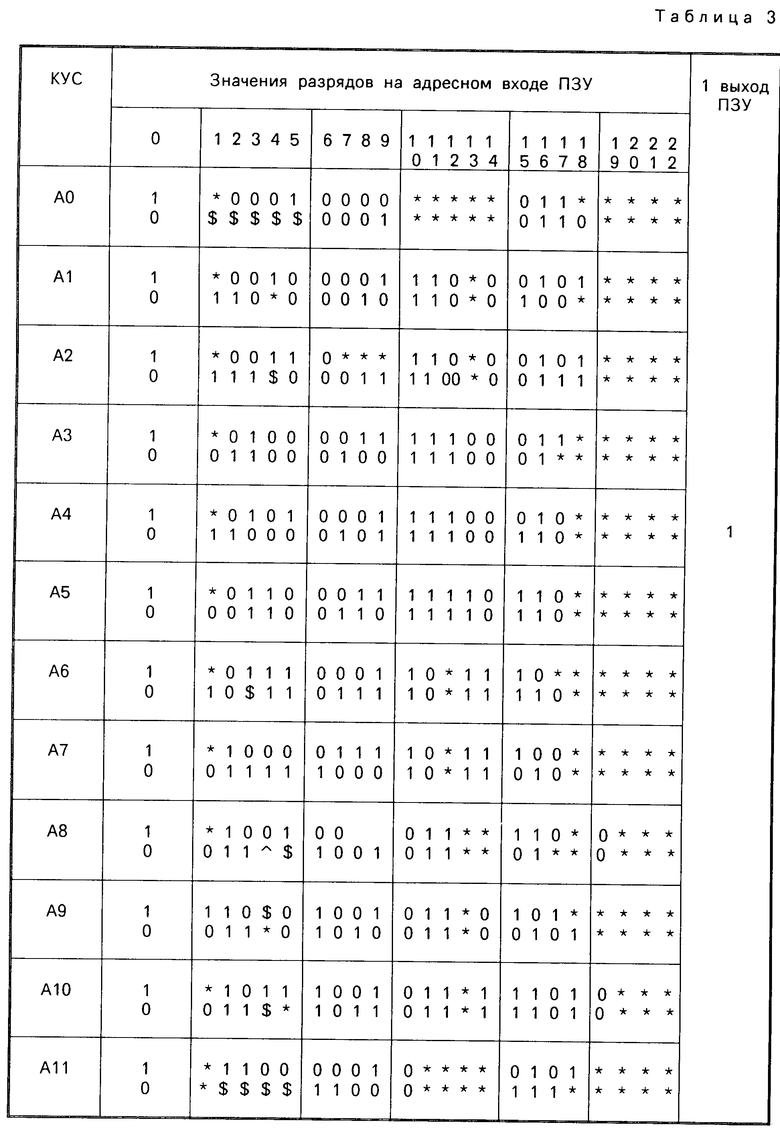

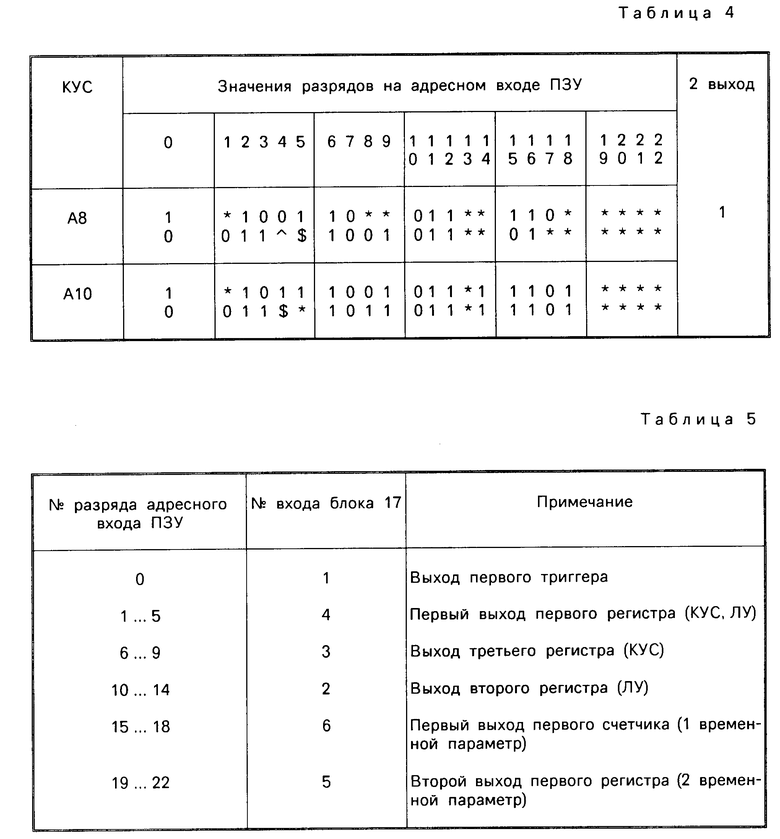

Затем по полученной таким образом табл.2 составляются табл.3,4 для программирования ПЗУ. При этом принято следующее соответствие между разрядами адресного входа ПЗУ и входами блока 17 (табл.5).

Первый и второй выходы ПЗУ являются соответственно первым и вторым выходами блока 17.

Если в позиции таблиц стоит знак "^", то ожидаемое значение разряда должно быть инверсным по отношению к его предыдущему значению. Если в позиции таблиц стоит знак "$", то ожидаемое значение разряда не изменяется по отношению к его предыдущему значению. Разряды, в позиции которых указан знак "*", могут принимать любые значения ("0" или "1").

В табл. 3 в колонке "1 выход ПЗУ" указано значение "1" для адресов в случае правильной работы УУ и ОУ. Остальные адреса соответствуют случаю возникновения ошибки при обмене между УУ и ОУ. Значения по этим адресам ПЗУ должны быть равны 0.

В предлагаемом устройстве производится дополнительный контроль управляющего устройства путем контроля времени его нахождения в каком-либо цикле (например, "ждущая вершина"). Так, для алгоритма фиг.2 имеется цикл А8-Р5-А10-А8 при Р5 = 1. В случае, если время нахождения в этом цикле известно и не может быть больше 7, то в табл.2 для КУС А8 и А10 в колонке "2 временной параметр" указывается значение "0***". В остальных случаях это значение не определено. Поэтому указываются значение "***".

В табл.4 в колонке "2 выход ПЗУ" указано значение "1" для адресов, соответствующих циклу А8-Р5-А10-А8. Значения по остальным адресам ПЗУ должны быть равны "0". Значение "1" на втором выходе ПЗУ запрещает сброс второго счетчика 13. Это позволяет измерять время цикла.

В случае, если происходит "зацикливание" при обмене между УУ и ОУ (цикл А8-Р5-А10-А8) и время нахождения в этом цикле становится больше заданного, то на первом выходе ПЗУ появляется значение, равное "0". Это приводит к возникновению сигнала ошибки на выходе 23 устройства. В прототипе ошибка подобного типа осталась бы не замеченной.

Таким образом, благодаря введению в устройство для контроля новых элементов и новых связей между элементами произошло повышение достоверности контроля за счет возможности временного контроля циклов на ГСА контролируемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СИТУАЦИОННОГО КОНТРОЛЯ И УПРАВЛЕНИЯ | 1992 |

|

RU2041494C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИМВОЛЬНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2010319C1 |

| КОРРЕЛЯЦИОННАЯ ИЗМЕРИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2007753C1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| ЦИФРОВОЙ ТЕРМОМЕТР | 1992 |

|

RU2039953C1 |

| ЦИФРОВОЙ РЕГУЛЯТОР | 1992 |

|

RU2036502C1 |

| ПЕРЕДАТЧИК УСТРОЙСТВА ДЛЯ ТЕЛЕИЗМЕРЕНИЙ | 1993 |

|

RU2057369C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ АКТИВНОЙ МОЩНОСТИ | 1993 |

|

RU2074397C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля обмена информацией между источником и устройством обработки информации. Целью является повышение достоверности контроля. Сущность заключается в сравнении ожидаемой, заранее определенной информации, которая должна вырабатываться при работе контролируемых устройств, с теми значениями, которые вырабатываются непосредственно в ходе работы. Несовпадение ожидаемых и выработанных значений является признаком ошибки. Цель достигается использованием двух триггеров,двух элементов И, четырех элементов ИЛИ, трех регистров, двух счетчиков, формирователя импульсов, двух элементов И - НЕ и блока памяти. Устройство позволяет расширить класс обнаруживаемых ошибок, возникающих при обмене информацией между источником и устройством обработки информации, за счет временного контроля циклов и "ждущих" вершин на граф-схеме алгоритма информации и сокращения времени на выявление ошибок при обмене. 3 ил., 5 табл.

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ, содержащее блок памяти, два триггера, два элемента И, четыре элемента ИЛИ, три регистра и первый счетчик, причем прямой выход первого триггера соединен с первой группой адресных входов блока памяти, информационный вход устройства соединен с первым информационным входом первого регистра, первый выход которого соединен с информационным входом второго регистра, вход обнуления которого соединен с входом "Сброс" устройства и входом обнуления третьего регистра, вход синхроимпульсов устройства соединен с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, выход переполнения первого счетчика является выходом сигнала превышения заданного интервала времени контроля устройства, отличающееся тем, что устройство дополнительно содержит второй счетчик, формирователь импульсов, два элемента И - НЕ, причем вход "Ввод" устройства соединен с первым входом второго элемента И и инверсным входом обнуления первого триггера, прямой выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с синхровходом второго регистра, выход которого соединен с второй группой адресных входов блока памяти, инверсный выход первого триггера соединен с первым входом третьего регистра, выход которого соединен с третьей группой адресных входов блока памяти, первый и второй выходы блока памяти соединены с первыми входами соответственно третьего и четвертого элементов ИЛИ, вход "Вывод" устройства соединен с вторым входом второго элемента И и инверсным входом установки в "1" первого триггера, вход синхроимпульсов устройства соединен с тактовым входом формирователя импульсов, первый выход которого соединен с вторыми входами первого, второго, третьего и четвертого элементов ИЛИ, второй выход формирователя импульсов соединен с первым входом первого элемента И - НЕ и с входом установки в "1" второго триггера, второй информационный вход первого регистра соединен с выходами разрядов второго счетчика, первый выход первого регистра соединен с информационным входом третьего регистра и с четвертой группой адресных входов блока памяти, второй выход первого регистра соединен с пятой группой адресных входов блока памяти, вход "Сброс" устройства соединен с вторым входом первого элемента И - НЕ и первым входом второго элемента И - НЕ, выходы разрядов первого счетчика соединены с шестой группой адресных входов блока памяти, прямой выход второго триггера соединен с вторым входом первого элемента И и входом разрешения формирователя импульсов, выход второго элемента И соединен с входом обнуления второго триггера и синхровходом первого регистра, выход первого элемента И соединен со счетным входом второго счетчика, выход первого элемента И - НЕ соединен с входом обнуления первого счетчика, выход третьего элемента ИЛИ является выходом ошибки устройства, выход четвертого элемента ИЛИ соединен со вторым входом второго элемента И - НЕ, выход которого соединен с входом обнуления второго счетчика.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля | 1986 |

|

SU1396145A2 |

Авторы

Даты

1995-02-27—Публикация

1991-08-06—Подача