Изобретение относится к электросвязи и вычислительной технике и может быть использовано для повышения помехоустойчивости в системах передачи и обработки цифровой информации, в частности в цифровой видео- или звукозаписи.

Известно устройство для декодирования кода Рида-Соломона, декодирующее блоки вычисления и циклического преобразования синдромов, содержащее буферный накопитель, сумматоры, преобразователи кода, дешифраторы, счетчики и ключи (1).

Недостаток аналога заключается в том, что в его схеме производится исправление двух стираний.

Наиболее близким к предлагаемому устройству является декодирующее устройство, которое содержит буферный накопитель на 64 байта, блок вычисления синдромов Si, блок запоминания значения синдрома So, блок индикации однократной ошибки, блок вычисления локатора ошибки, блок формирования маски, а также блоки ключей и сумматоров; причем первые входы буферного накопителя и блока вычисления синдромов объединены и являются соответствующими входами устройства (Вх. инф. ), тактовый вход устройства (ТИ) подключен ко вторым входам буферного накопителя и блока вычисления синдромов, а также параллельно к первым входам блока формирования маски и блока вычисления локатора ошибки, второй вход которого соединен с первым выходом блока индикации однократной ошибки, второй выход которого соединен со вторым входом блока формирования маски, третий вход которого соединен со входом синхронизации устройства и параллельно с третьим входом блока вычисления синдромов и пятым входом блока индикации однократной ошибки, первый, второй, третий и четвертый входы которого подключены к одноименным выходам блока вычисления синдромов; информационным выходом устройства является выход блока сумматора, первый вход которого подключен к выходу буферного накопителя, а второй вход подключен к выходу блока ключей, первый вход которого соединен с выходом блока вычисления локатора ошибки, второй вход блока ключей соединен с третьим входом упомянутого выше блока и параллельно с выходом блока запоминания значения синдрома So, вход которого подключен к первому выходу блока вычисления синдромов; третий вход блока ключей соединен с первым выходом блока индикации однократной ошибки; четвертый вход блока индикации однократной ошибки подключен ко второму выходу блока вычисления синдромов; выход блока формирования маски является контрольным выходом устройства.

Декодирующее устройство (прототип) работает следующим образом.

По поступающей на вход последовательности определяются синдромы So, S1, S2, S3. Если в блоке будет один ошибочный байт, то синдромы будут иметь следующий вид:

So = Y1

S1 = Y1 ˙ X1

S2 = Y1˙ X12 (1)

S3 = Y1˙ X13 где Y1 - значение ошибки;

Х1 - адрес ошибочного символа;

Из этой системы уравнений следуют уравнения для условия наличия однократной ошибки:

So ˙ S2 = S12

So ˙ S3 = S1˙ S2 (2)

S22 = S1˙ S3

Исправление ошибки происходит при последовательном считывании блока с буферного накопителя в тот момент, когда преобразованный синдром S1 совпадает с So, т. е. при выполнении равенства S1 α -i = = So. Если в результате обработки блока окажется, что хотя бы один из синдромов будет отличен от нуля и будет не выполнено хотя бы одно из уравнений наличия однократной ошибки (2), то это означает, что в блоке имеется два или более ошибочных байта. В этом случае весь блок маскируется. Если же все синдромы равны нулю, т. е. So = S1 = S2= = S3 = 0, то это означает, что ошибок нет и весь блок подается на выход без изменения.

Недостаток прототипа заключается в том, что схема декодирующего устройства имеет большое потребление электроэнергии и малую надежность. Этот недостаток вытекает из необходимости проверки всех трех уравнений системы (2) и поэтому схема блока индикаторов ошибки достаточно громоздкая и сложная (т. е. включает в себя большое число микросхем, что увеличивает потребление электроэнергии и снижает надежность работы устройства).

Целью изобретения является упрощение устройства и повышение его надежности за счет значительного уменьшения числа микросхем в блоке индикации однократной ошибки и уменьшение потребления электроэнергии схемой декодирующего устройства.

При таком построении структурной схемы заявляемого устройства появляется возможность использовать для индикации однократной ошибки только одно проверочное уравнение из системы (2), а именно

S1 ˙ S3 = S1 ˙ S2, (3) что позволяет существенно упростить схему блока индикации однократной ошибки декодирующего устройства. Однако при этом появляется вероятность ложного исправления как бы однократного ошибочного байта при поражении в блоке 4 или более байт. С целью проверки вероятности появления такой ситуации (см. Разработка и исследование кодека корректирующего кода Рида-Соломона для высокоскоростного видеотракта студийного цифрового видеомагнитофона.

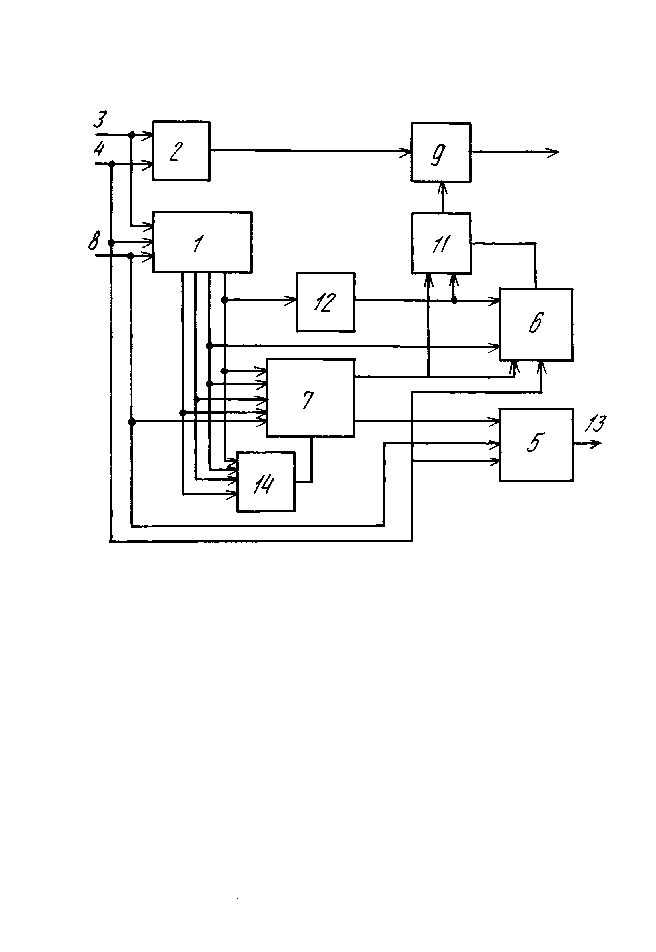

Структурная схема предлагаемого декодирующего устройства представлена на чертеже.

Она содержит блок вычисления синдромов 1, буферный накопитель 2, и информационный вход устройства 3, тактовый вход устройства 4, блок формирования маски 5, блок вычисления локатора ошибки 6, блок индикации однократной ошибки 7, вход синхронизации устройства 8, блок сумматора 9, информационный выход 10 устройства, блок ключей 11, блок памяти значения синдрома 12, контрольный выход устройства 13 и дешифратор ненулевого значения всех синдромов 14.

Схема устройства работает следующим образом.

По мере поступления на вход 3 информационных и проверочных байт они записываются в буферный накопитель 2 и одновременно в блоке 1 производится вычисление синдромов (So, S1, S2, S3). Если все синдромы нулевые, то исправление ошибок или маскирование блока не производится и он без изменений выдается на выход устройства. Если все синдромы ненулевые, но уравнение So ˙ S3 = S1 ˙ S2 не выполняется, то это означает, что в блоке ошибки кратности 2 или более (t≥ 2), и тогда в этом случае по сигналу со второго выхода блока 7 (индикации однократной ошибки) происходит маскирование ошибочного блока сигналом с выхода 13 устройства. При этом введенный в схему дешифратор 14 позволяет проверять не три уравнения (2), а только одно (3), которое может выполняться только тогда, когда все синдромы отличны от нуля. Если все синдромы отличны от нуля, то начинается процесс исправления ошибочного байта в соответствии с алгоритмом. При этом происходит преобразование синдрома S1 до тех пор, пока T = S1˙α191 не станет равным So (T = So), что и указывает адрес ошибочного байта, на который по сигналу от блока вычисления локатора ошибки 6 накладывается синдром через блок ключей 11 на блоке сумматоров 9 и на выход 10 поступает исправленный байт.

Дешифратор 14 реализован на микросхеме К155ЛЕ5.

Введение дополнительно дешифратора 14 позволяет отказаться от проверки уравнений So˙ S2 = S12 и S1˙ S3 = S22 и таким образом исключить из схемы устройства 4 микросхемы К155ИМ3, 4 - К556РТ5 и 4 - К531СП1, которые потребляли 1,7 А.

Уменьшение на 12 числа микросхем в схеме декодирующего устройства повышает надежность его в работе. (56) Авторское свидетельство СССР N 1332539, кл. H 03 M 13/00, 1987.

Разработка и исследование кодека корректирующего кода Рида-Соломона для высокоскоростного видеотракта студийного цифрового видеомагнитофона. Заключительный отчет по теме 052-89-09, гос. рег. N 018900 38301, ЛЭИС, 1990, с. 32.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ КОДА РИДА - СОЛОМОНА | 1991 |

|

RU2007040C1 |

| Устройство для декодирования кода Рида-Соломона | 1990 |

|

SU1718385A2 |

| Декодер линейного кода | 1986 |

|

SU1432786A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Система для передачи и приема цифровой информации | 1989 |

|

SU1637025A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО АМПЛИТУДНО-МОДУЛИРОВАННЫХ СИГНАЛОВ С КОМПЕНСАЦИЕЙ ГАРМОНИЧЕСКИХ ПОМЕХ | 1993 |

|

RU2079971C1 |

| ВОЛОКОННО-ОПТИЧЕСКИЙ ИНДИКАТОР ВНЕШНЕГО ВОЗДЕЙСТВИЯ | 1992 |

|

RU2036419C1 |

Изобретение относится к электросвязи и вычислительной технике и может быть использовано для повышения помехоустойчивости в системах передачи и обработки цифровой информации, в частности в цифровой звукозаписи. Целью изобретения является упрощение устройства и повышение его надежности. Указанная цель достигается введением дешифратора 14, который позволил использовать в блоке индикации однократной ошибки 7 для определения наличия ошибки только одно уравнение, в устройство, содержащее блок вычисления синдрома 1, буферный накопитель 2, блок 6 вычисления локатора ошибки, блок 5 формирования маски, блок 7 индикации ошибки, блок 12 памяти значения синдрома, блок 11 ключей, блок 9 сумматоров. 1 ил.

УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ КОДА РИДА - СОЛОМОНА, содержащее буферный накопитель, первый вход которого объединен с первым входом блока вычисления синдромов и является информационным входом устройства, вторые входы буферного накопителя и блока вычисления синдромов объединены с первыми входами блока вычисления локатора ошибки и блока формирования маски и являются тактовым входом устройства, третий вход блока вычисления синдромов объединен с вторым входом блока формирования маски и первым входом блока индикации ошибки и является синхронизирующим входом устройства, выход буферного накопителя соединен с первым входом блока сумматоров, выход которого является информационным выходом устройства, первый выход блока вычисления синдромов соединен с вторым входом блока индикации ошибки и входом блока памяти значения синдрома, выход которого соединен с первым входом блока ключей и вторым входом блока вычисления локатора ошибки, выход которого соединен с вторым входом блока ключей, выход которого соединен с вторым входом блока сумматоров, второй выход блока вычисления синдромов соединен с третьими входами блока вычисления локатора ошибки и блока индикации ошибки, первый выход которого соединен с третьим входом блока ключей и четвертым входом блока вычисления локатора ошибки, третий и четвертый выходы блока вычисления синдрома соединены соответственно с четвертым и пятым входами блока индикации ошибки, второй выход которого соединен с третьим входом блока формирования маски, выход которого является контрольным выходом устройства, отличающееся тем, что, с целью упрощения устройства и повышения его надежности, в устройство введен дешифратор, первый-четвертый входы которого подключены к одноименным выходам блока вычисления синдромов, выход соединен с шестым входом блока индикации ошибки.

Авторы

Даты

1994-01-30—Публикация

1991-07-03—Подача