(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2006 |

|

RU2314639C1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для мажоритарного декодирования имитостойких циклических кодов при трехкратном повторении комбинации | 1990 |

|

SU1709538A1 |

| Декодер кода БЧХ | 1987 |

|

SU1457166A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2010 |

|

RU2441318C1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

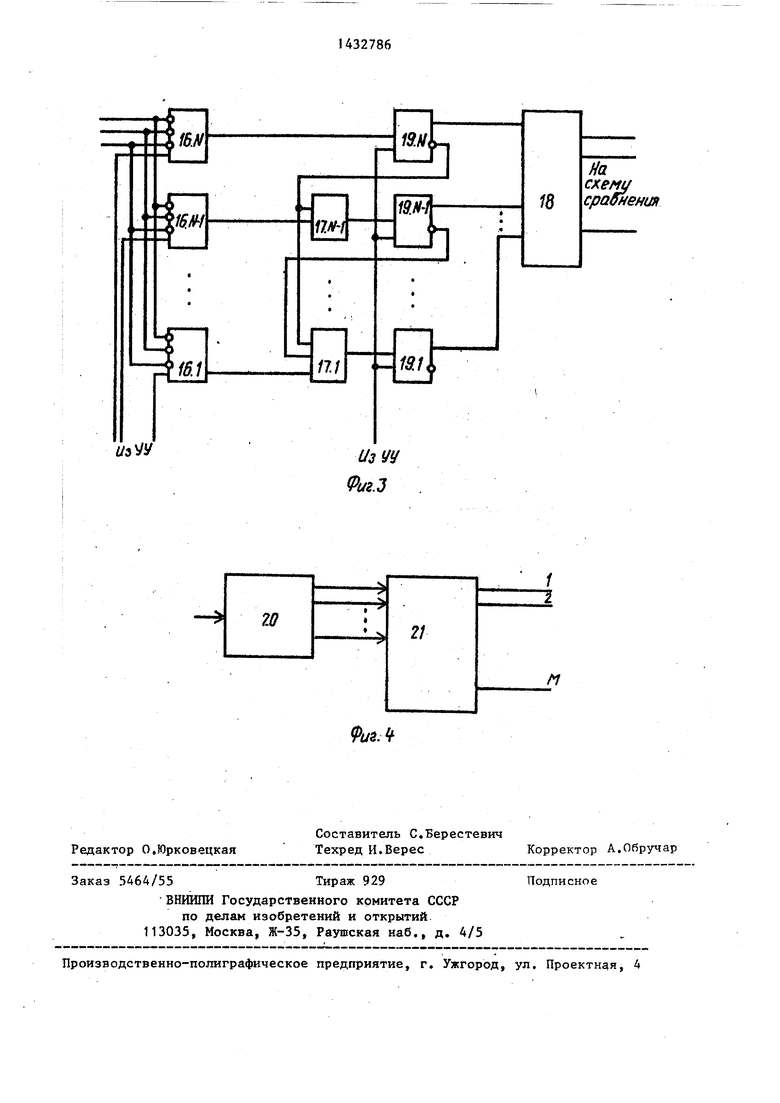

Изобретение относится к радиоэлектронике и может быть использовано в цифровом радиовещании. Цель изобретения - ловышение помехоустойчивости путем обнаружения ошибок кратности t + 1 и выше. Декодер линейного кода содержит буферньтй регистр 1, сумматор 2 по модулю два, вычислитель 3 синдромов, арифметический блок 4, блок 5 памяти многочлена, блок 6 управления, блок 7 маскировки, счетчик 8 ошибок, блок 9 вычисления степени многочлена, схему 10 сравнения. 3 з.п. ф-лы, 4 ил. с «

Фиг. 1

Изобретение Относится к радиоэлектронике и может быть использова- I но в цифровом-радиовещании. Целью изобретения является ппвы- шение помехоустойчивости путем обнаружения ошибок кратности t+1 и выше.

На фиг,1 приведена структурная схема предлагаемого декодера; на фиг, 2 - 4 - схемы возможт11х реализаций блока маскировки, блока вычисления степени многочлена И блока управ- :ления соответственно, : Декодер линейного кода (фиг,1) содержит буферный регистр 1, сумматор 2 по модулю два, вычислитель 3 синдромов, арифметический блок 4, блок 5 памяти многочлена, блок 6 управления блок 7 маскировки, счетчик 8 оотибок, ;блок 9 вычисления степени многочле- на и блок 10 сравнения.

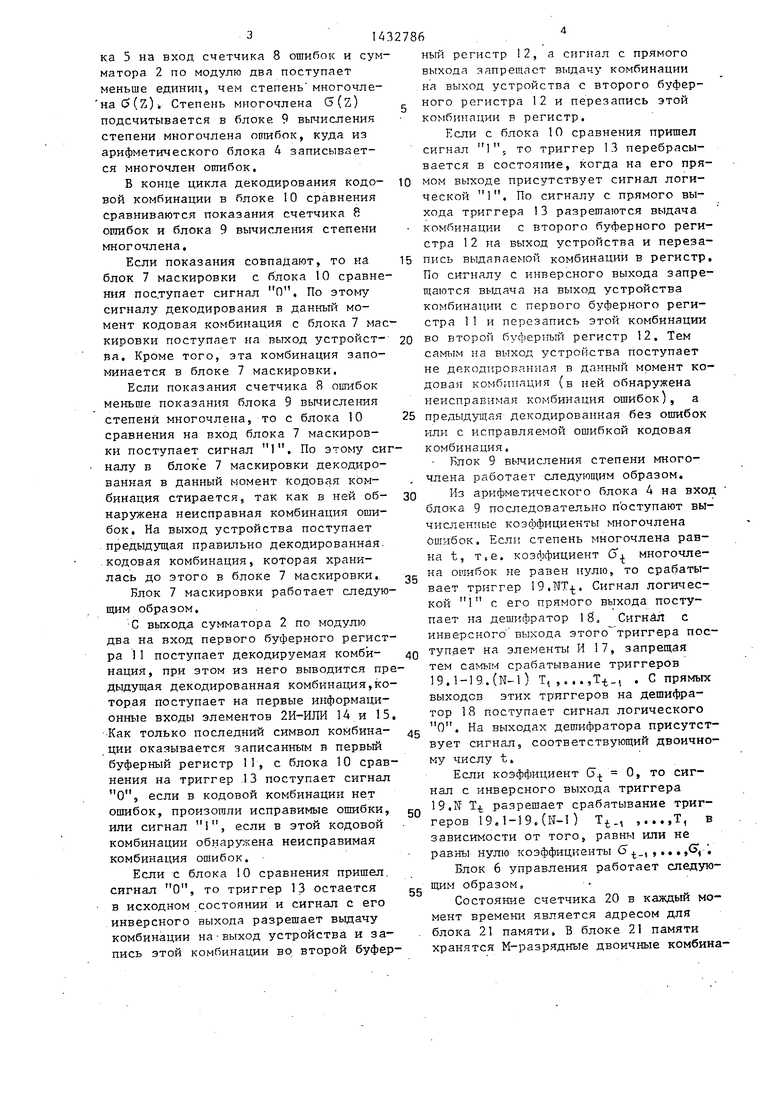

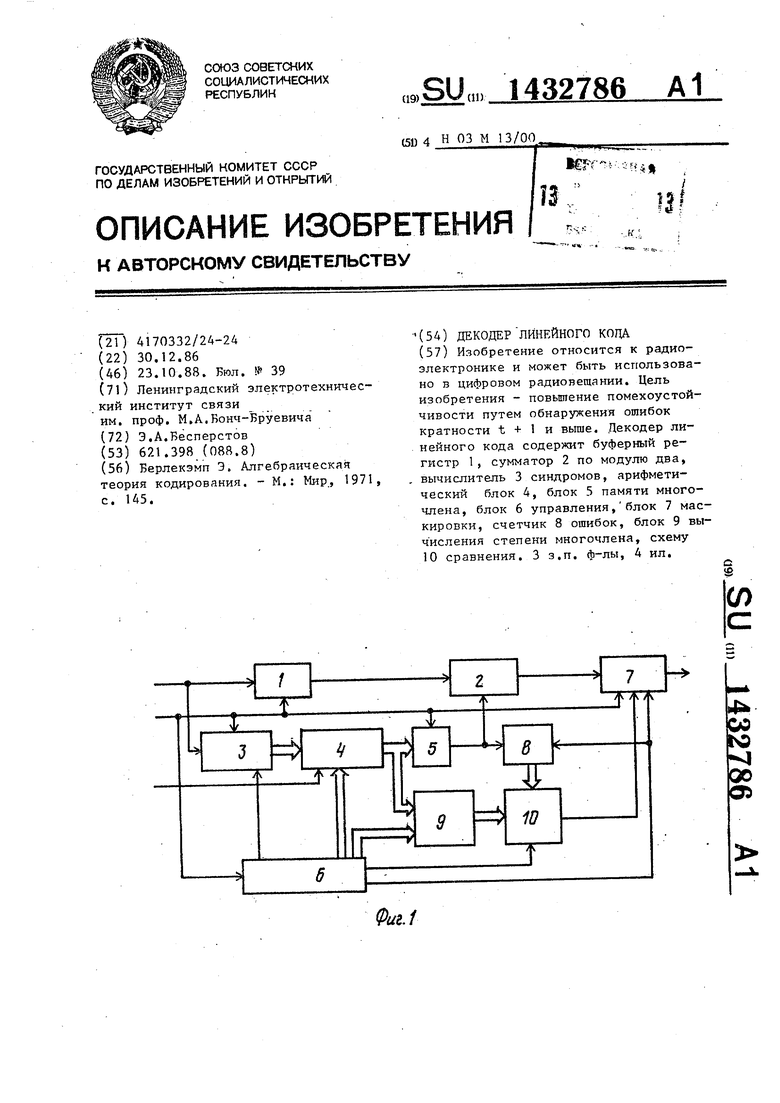

Блок 7 маскировки (фиг.2) содержит буферные регистры И и 12, триггер 13 и элементы 2И-ИЛИ 14 и 15.

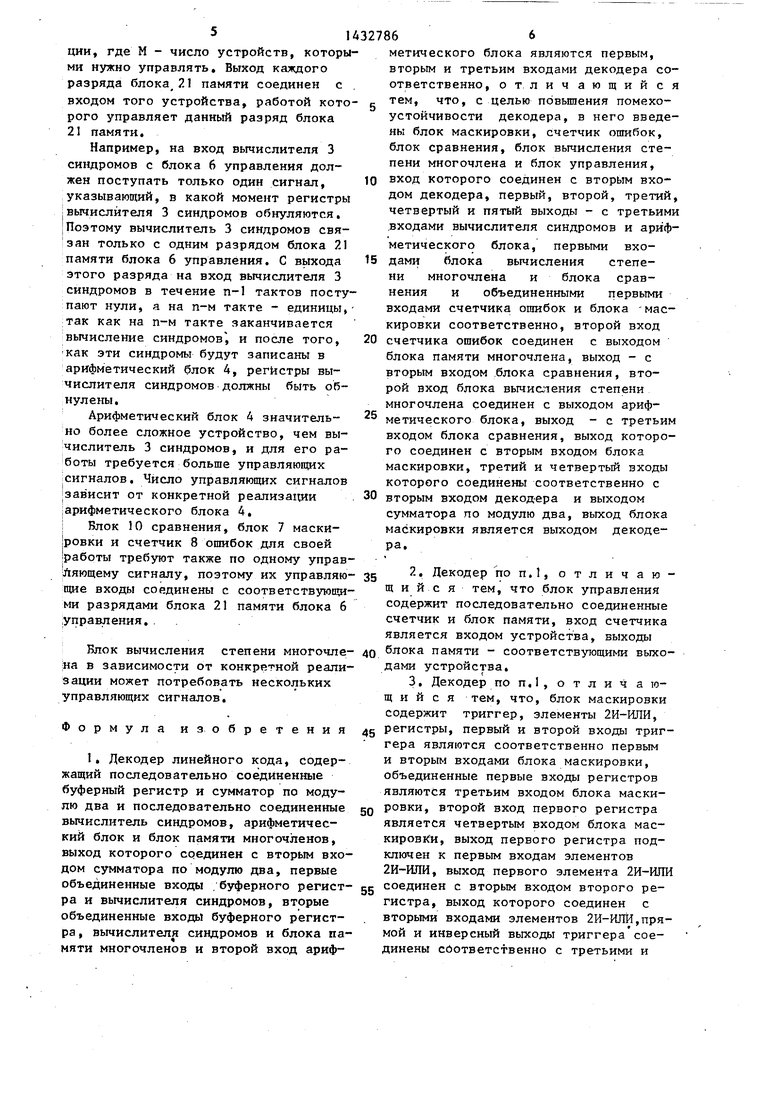

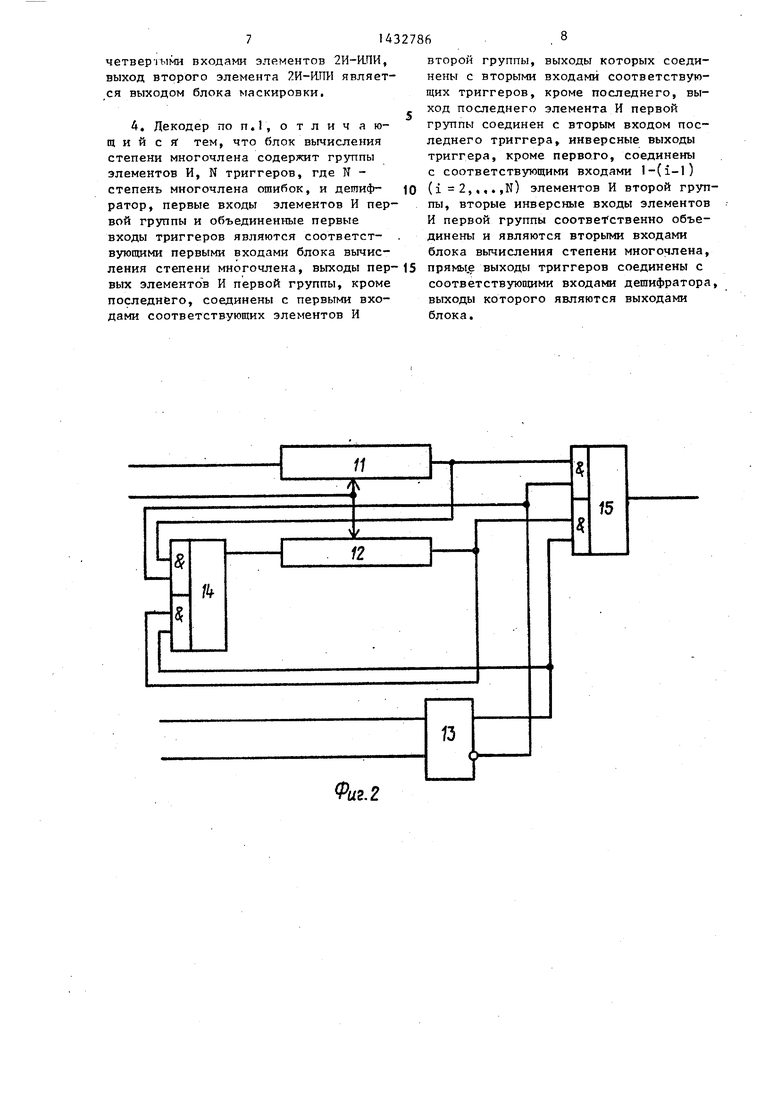

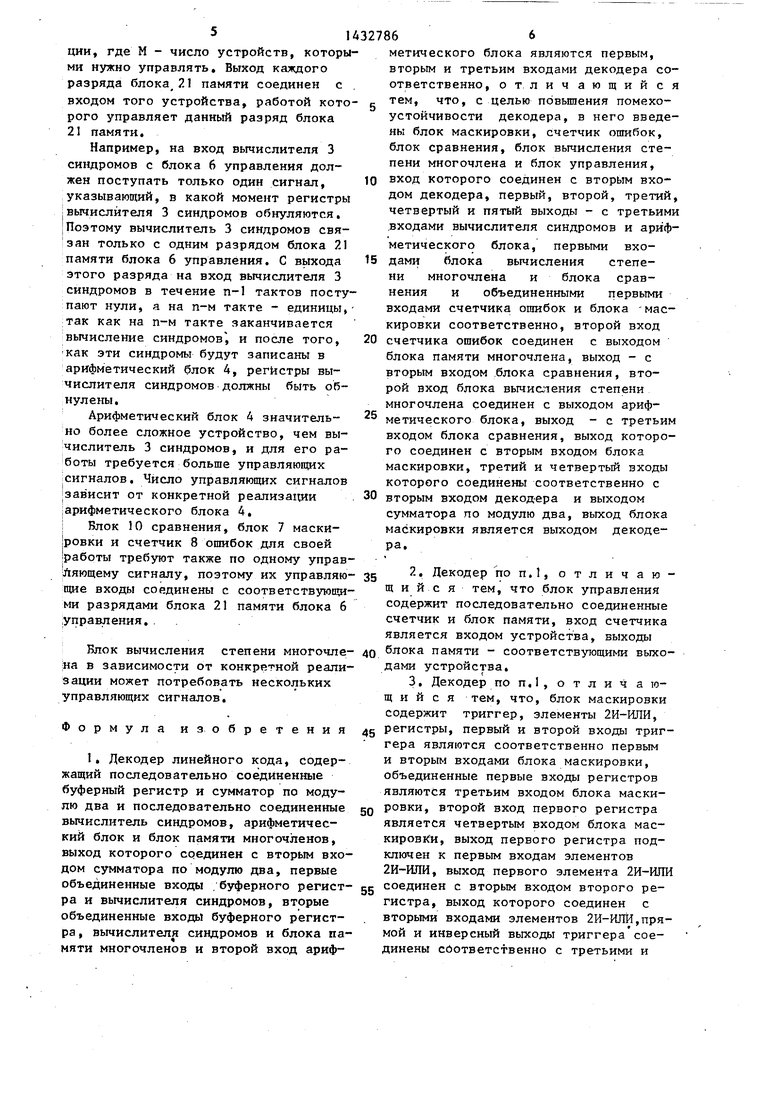

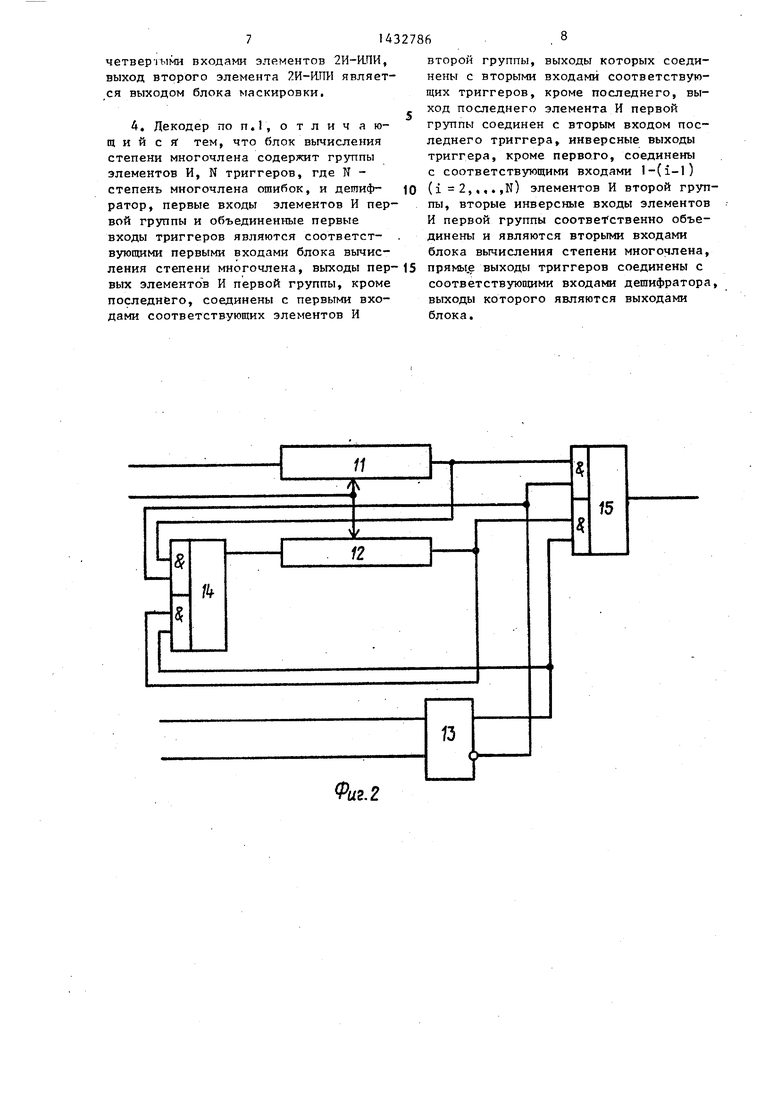

Блок 9 вычисления степени много- члена (фиг.З) содержит элементы И :16.1-16,Ни 17.1-17.(N-1), дешифра- Игор 18 и триггеры 19.1-I9.N. Блок 6 управления (фиг«4) содержит iсчетчик 20 и блок 21 памяти. : Декодер линейного кода работает следующим образом.

I Принимаемая п-разрядная комбинация I поступает в накопитель и одновремен- jно в вычислитель синдромов, где вы- числяют синдромы принимаемой комбинации. Как- только принимаемая комбина- :ция оказывается полностью записанной :в буферном регистре 1, в вычислите- ле 3 синдромов оканчивается вычисле- ние синдромов .и вычисленные синдромы переписываются по сигналу с блока 6 управления в ари(1метический блок 4, где по ним вычисляется многочлен огаи 6oKG(Z), степень которого равна t или в зависимости от кратности ошибок. Коэффициенты многочлена G (%) принадлежат полю GF(2)5 где п . Всего может быть 2 различных многочленов G (Z). С другой стороны, всего может быть различных синдромов и, следовательно, 2 различных смежных классов,Пр этом mt п - К,

Каждому смежному классу можно пос тавить в однозначное соответствие один многочлен. Многочлены 0(Z),соответствующие исправляемым данным-кодом ошибкам, называются допустимыми.

остальные - недопустимыми. Все многочлены первой степени соответствуют однократной ошибке и, следовательно, являются допустнмьпда. Но не все многочлены (3i (Z) степени 2 и вьппе являются допустимыми многочленами, так как Cj, i , где i i t, a C - равно числу i-кратных ошибок.

Если в принятой комбинации имеется ошибочных сигналов, то степень .многочлена S (%) равна i. Многочлен G (, в данном случае имеет i различных корней, принадлежащих полю ОРС). Если в принятой комбинации имеется i t ошибочных символов, то степень многочлена (5 (z) меньше или равна t. Число корней многочлена всегда равно степени тчногочлена. Но в данном случае не все корни многочлена (5 (ч принадлежат полю (ТГ(2), некоторые или все корни многочлена принадлежат к некоторому расширению поля GF().

Из арифметического блока 4 многочлен ошибок 3(z) переписывается в блок 5 памяти, где в него поочередно подставляются элементы поля, при этом из буферного регистра 1 считывается декодируемая комбинация. Каждому считываемо1«1у из накопителя символу соответствует подставляемый, в многочлен ошибок элемент поля GF(2) Если при подстановке очередного элемента поля .многочлен ошибок обраша- ется в ноль, то выводимый в данный момент из буферного регистра 1 символ опп бочен, С блока 5 на вход сумматора 2 по модулю два поступает единица, которая в cyNJMaTOpe 2 по модулю два складьЬается с символом, поступающим с буферного регистра I. Тем самым данньп символ кодовой комбинации инвертируется, т.е. происходит исправление ошибки. Число единиц Tje. число исправляемых ошибок в кодовой комбинации, поступающих с блок 5 за время декодирования одной кодовой комбинации, подсчитывается в счетчике 8 ошибок.

Предположим, что в блок 5 записан недопустимый многочлен, В этом случае может оказаться, что ни один из элементов поля GF(2) не является корнем данного многочлена, или корней, принадлежащих полю GF( 2),{меньше степени многочлена ошибок, В этом случае оказывается, что с выхода блока 5 на вход счетчика 8 ошибок и сумматора 2 по модулю два поступает меньше единиц, чем степень многочле- Ha6(Z)i Степень многочлена C5(z) подсчитывается в блоке 9 вычисления степени многочлена опшбок, куда из арифметического блока 4 записывается многочлен ошибок.

В конце цикла декодирования кодовой комбинации в блоке 10 сравнения сравниваются показания счетчика 8 ошибок и блока 9 вычисления степени многочлена.

Если показания совпадают, то на блок 7 маскировки с блока 10 сравнения пос.тупает сигнал О, По этому сигналу декодирования в данный момент кодовая комбинация с блока 7 маскировки поступает на выход устройства. Кроме того, эта комбинация запоминается в блоке 7 маскировки.

Если показания счетчика 8 ошибок меньше показания блока 9 вычислеютя степени многочлена, то с блока 10 сравнения на вход блока 7 маскировки поступает сигнал 1, По этому сигналу в блоке 7 маскировки декодированная в данный момент кодовая комбинация стирается, так как в ней обнаружена неисправная комбинация ошибок. На выход устройства поступает

.предыдущая правильно декодированная.

.кодовая комбинация, которая хранилась до этого в блоке 7 маскировки.

Блок 7 маскировки работает следующим образом,

С выхода сумматора 2 по модулю два на вход первого буферного регистра 11 поступает декодируемая комбинация, при этом из него выводится предыдущая декодированная комбинация,которая поступает на первые информационные входы элементов 2И-ИЛИ 14 и 15, Как только последний символ конбина, ции оказывается записанным в первый буферный регистр П, с блока 10 сравнения на триггер 13 поступает сигнал о, если в кодовой комбинация нет

20 во второй буфер1ПзШ регистр 12. Тем самым на выход устройства поступает не декодт фованная в данный момент кодовая комбинация (в ней обнаружена неисправимая комбинация ошибок), а

25 предыдущая декодированная без ошибок или с исправляемой ошибкой кодовая комбинация.

Блок 9 вычисления степени многочлена работает следующим образом.

Из арифметического блока 4 на вход блока 9 последовательно п оступают вычисленные коэффициенты ffloгoчлeнa ошибок. Если степень многочлена рая30

35

40

45

на t, т,е, коэффициент G многочлена О1чибок не равен нулю, то срабатывает триггер 19,NT. Сигнал логической 1 с его прямого выхода поступает на дешифратор Ig, Сигнйл с инверсного выхода этого триггера поступает на элементы И 17, запрещая тем срабатывание триггеров I9,l-19..(N-l) Ti,.,.,Tt, , С прямых выходов этих триггеров на дешифратор 18 поступает сигнал логического О, На выходах дешифратора присутствует сигнал, соответствующий двоичному числу t.

Если коэффициент С . О, то сигнал с инверсного выхода триггера

ошибок, произошли исправимые ошибки, разрешает срабатывание тригили сигнал 1, если в этой кодовой комбинации обнаруясена неисправимая комбинация ошибок.

Если с блока 10 сравнения пришел. Сигнал О, то триггер 13 остается в исходном состоянии и сигнал с его инверсного выхода разрешает выдачу комбинации навыход устройства и запись этой комбинации во второй буфер-

55

геров 19,1-}9.(N-I) Т., ,,..,TI зависимости от того, равны или не равны нулю коэффициенты G ,,,,, ,6,,

Блок 6 управления работает следующим образом.

Состояние счетчика 20 в каждый момент времеш является адресом для блока 21 памяти, В блоке 21 памяти хранятся М-разрядные двоичные комбина

ный регистр 12, а сигнал с прямого выхода запрещает выдачу комбинации на выход устройства с второго буферного регистра 12 и перезапись этой комбинации в регистр.

Если с блока 10 сравнения пришел сигнал I, то триггер 13 перебрасывается в cocTOHirae, когда на его прямом выходе присутствует сигнал логической 1. По сигналу с прямого выхода триггера 13 разрешаются выдача комбинации с второго буферного регистра 12 ка выход устройства и перезапись выдаваемой комбинации в регистр, По сигналу с инверсного выхода запрещаются вьщача на выход устройства комбинации с первого буферного регистра 1 и перезапись этой комбинации

во второй буфер1ПзШ регистр 12. Тем самым на выход устройства поступает не декодт фованная в данный момент кодовая комбинация (в ней обнаружена неисправимая комбинация ошибок), а

предыдущая декодированная без ошибок или с исправляемой ошибкой кодовая комбинация.

Блок 9 вычисления степени многочлена работает следующим образом.

Из арифметического блока 4 на вход блока 9 последовательно п оступают вычисленные коэффициенты ffloгoчлeнa ошибок. Если степень многочлена рая

на t, т,е, коэффициент G многочлена О1чибок не равен нулю, то срабатывает триггер 19,NT. Сигнал логической 1 с его прямого выхода поступает на дешифратор Ig, Сигнйл с инверсного выхода этого триггера поступает на элементы И 17, запрещая тем срабатывание триггеров I9,l-19..(N-l) Ti,.,.,Tt, , С прямых выходов этих триггеров на дешифратор 18 поступает сигнал логического О, На выходах дешифратора присутствует сигнал, соответствующий двоичному числу t.

Если коэффициент С . О, то сигнал с инверсного выхода триггера

разрешает срабатывание триг

геров 19,1-}9.(N-I) Т., ,,..,TI зависимости от того, равны или не равны нулю коэффициенты G ,,,,, ,6,,

Блок 6 управления работает следующим образом.

Состояние счетчика 20 в каждый момент времеш является адресом для блока 21 памяти, В блоке 21 памяти хранятся М-разрядные двоичные комбина10

15

ции, где М - число устройств, которыми нужно управлять. Выход каждого разряда блока. 1 памяти соединен с , входом того устройства, работой кото- g рого управляет данный разряд блока 21 памяти.

Например, на вход вычислителя 3 синдромов с блока 6 управления должен поступать только один сигнал, указывающий, в какой момент регистры I вычислителя 3 синдромов обнуляются. I Поэтому вычислитель 3 синдромов свя- :зан только с одним разрядом блока 21 памяти блока 6 управления. С выхода этого разряда на вход вычислителя 3 синдромов в течение п-1 тактов посту пают нули, а на п-м такте - единицы, так как на п-м такте заканчивается вычисление синдромов, и после того, как эти синдромы будут записаны в арифметический блок 4, регистры вычислителя синдромов должны быть обнулены.

Арифметический блок 4 значительно более сложное устройство, чем вычислитель 3 синдромов, и для его работы требуется больше управляющих сигналов. Число управляющих сигналов зависит от конкретной реализации ;арифметического блока 4, I Блок 10 сравнения, блок 7 маски- |ровки и счетчик 8 ошибок для своей |работы требуют также по одному управляющему сигналу, поэтому их управляю- 35 щие входы соединены с соответствзпощи- ми разрядами блока 21 памяти блока 6 управления,. .

метического блока являются первым, вторым и третьим входами декодера соответственно, отличающийся тем, что, с целью повышения помехоустойчивости декодера, в него введены блок маскировки, счетчик ошибок, блок сравнения, блок вычисления степени многочлена и блок управления, вход которого соединен с вторЬтм входом декодера, первый, второй, третий, четвертый и пятый выходы - с третьими .входами вычислителя синдромов и арифметического блока, первыми вхо- дам11 блока вычисления степени многочлена и блока сравнения и объединенными первыми входами счетчика ошибок и блока - маскировки соответственно, второй вход счетчика ошибок соединен с выходом блока памяти многочлена, выход - с вторым входом .блока сравнения, второй вход блока вычисления степени многочлена соединен с выходом ариф- метического блока, выход - с третьим входом блока сравнения, выход которого соединен с вторым входом блока маскировки, третий и четвертый входы которого соединены соответственно с вторым входом декодера и выходом сумматора по модулю два, выход блока маскировки является выходом декодера.

20

30

Блок вычисления

;на в зависимости от конкретной реализации может потребовать нескольких управляющих сигналов.

Формула изобретения

степени многочле- 40 блока памяти - соответствующими выходами устройства.

д регистры, первый и второй входы триггера являются соответственно первым и вторым входами блока маскировки, объединенные первые входы регистров являются третьим входом блока маскировки, второй вход первого регистра является четвертым входом блока маскировки, выход первого регистра подключен к первым входам элементов 2И-ИЛИ, выход первого элемента 2И-ИПИ

50

дом сумматора по модулю два, первые объединенные входы /буферного регист- gg соединен с вторым входом второго ре- ра и вычислителя синдромов, вторые гистра, выход которого соединен с объединенные входь буферного регист- . вторыми входами элементов 2И-ИЛИ,пря- ра, вычислителя синдромов и блока па- мой и инверсный выходы триггера сое- мяти многочленов и второй вход ариф- динены соответственно с третьими и

метического блока являются первым, вторым и третьим входами декодера соответственно, отличающийся тем, что, с целью повышения помехоустойчивости декодера, в него введены блок маскировки, счетчик ошибок, блок сравнения, блок вычисления степени многочлена и блок управления, вход которого соединен с вторЬтм входом декодера, первый, второй, третий, четвертый и пятый выходы - с третьими .входами вычислителя синдромов и арифметического блока, первыми вхо- дам11 блока вычисления степени многочлена и блока сравнения и объединенными первыми входами счетчика ошибок и блока - маскировки соответственно, второй вход счетчика ошибок соединен с выходом блока памяти многочлена, выход - с вторым входом .блока сравнения, второй вход блока вычисления степени многочлена соединен с выходом ариф- метического блока, выход - с третьим входом блока сравнения, выход которого соединен с вторым входом блока маскировки, третий и четвертый входы которого соединены соответственно с вторым входом декодера и выходом сумматора по модулю два, выход блока маскировки является выходом декодера.

71432786

четвертыми входами элементов 2И-И.ПИ, выход второго элемента 2И-ИПИ является выходом блока маскировки.

л п

§

иг,2

8

второй группы, выходы которых соединены с вторыми входами соответствующих триггеров, кроме последнего, выход последнего элемента И первой группы соединен с вторым входом последнего триггера, инверсные выходы триггера, кроме первого, соединены с соответствующими входами l-(i-l) (,,,.,N) элементов И второй группы, вторые инверсные входы элементов И первой группы соответственно объединены и являются вторыми входами блока вычисления степени многочлена, прямы.е выходы триггеров соединены с соответствующими входами дешифратора выходы которого являются выходами блока.

Л

«

15

/7/

f/зУУ

Y/j i/y fPue-J

18

Ha

схема

сравнения

,-/5f/

уз.

| Берлекэмп Э | |||

| Алгебраическая теория кодирования | |||

| - М.: Мир, 1971, с | |||

| Заслонка для русской печи | 1919 |

|

SU145A1 |

Авторы

Даты

1988-10-23—Публикация

1986-12-30—Подача