Изобретение относится к вычислительной технике, а именно к устройствам управления памятью ЭВМ, и может найти применение при организации и построении памяти вычислительной системы.

Известно устройство управления буферной памятью, содержащее буферную память, в которой отдельными массивами хранится информация, совпадающая с содержимым оперативного ЗУ, таблицу, в которой хранится информация об адресах массивов в памяти биты действительности данных, показывающие совпадает ли содержимое отдельных массивов, адреса которых заданы, с содержимым ЗУ, биты обращений, показывающие реализовались ли ранее обращения к определенным массивам, блок обновления битов обращения к определенным массивам, блок обновления битов обращения, блок индексации состояний [1] .

Недостатком устройства являются его малые функциональные возможности.

Наиболее близким по технической сущности к предлагаемому является устройство управления буферной памятью данных и буферной памятью команд, содержащее порт данных, порт буфера команд, блок управления памятью сегментов, порт буфера данных, блок управления буферной памятью данных, блок управления памятью страниц, блок центрального управления, блок управления буферной памятью команд, выходы признаков готовности которого и выходы признаков готовности порта буфера команд и блока управления памятью сегментов соединены через первую шину признаков готовности с первым входом признаков готовности блока центрального управления, первый управляющий вход-выход которого соединен двунаправленой внутренней шиной управляющих признаков с управляющим входом-выходом порта данных, управляющий выход соединен шиной управляющих сигналов с управляющим входом блока управления памятью сегментов, управляющим входом блока управления буферной памятью команд, первым управляющим входом порта буфера команд, управляющим входом порта данных, управляющим входом порта буфера данных, управляющим входом блока управления буферной памятью данных, управляющим входом блока управления памятью страниц, второй вход признаков готовности через вторую шину признаков готовности соединен с выходом признаков готовности блока управления памятью страниц, выходом признаков готовности блока управления буферной памятью данных и выходом признаков готовности порта буфера данных, причем адресно-числовой вход-выход порта данных через двунаправленную внутреннюю шину данных соединен с адресно-числовым входом-выходом порта буфера данных, адресно-числовым входом-выходом блока управления буферной памятью данных, адресно-числовым входом-выходом блока управления памятью страниц, адресно-числовым входом-выходом блока управления памятью сегментов, второй управляющий вход-выход блока центрального управления подключен к двунаправленной шине управления, числовой выход - к шине команд, адресный вход-выход порта буфера команд подключен к первой адресной шине, второй управляющий вход - к управляющей шине, адресный выход- к третьей адресной шине, адресно-числовой вход-выход порта данных подключен к двунаправленной адресно-числовой шине, числовой вход-выход - к двунаправленной шине тегов, адресный выход порта буфера данных подключен к второй адресной шине [2] .

Однако в известном устройстве управления буферной памятью данных и буферной памятью команд отсутствует аппаратный контроль хранения информации в накопителях в процессе функционирования адресных тегов. Отсутствует выделение физических страниц размером меньше, чем размер математической страницы. Из-за физического размера буфера команд и буфера данных отсутствует возможность задания их переменного размера.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения аппаратного контроля хранения информации в памяти в процессе функционирования.

Сущность изобретения заключается в том, что в предлагаемом устройстве, ориентированном на работу с независимыми шинами команд и данных, реализован подход, учитывающий различия в работе с командами и данными. Для команд характерна линейность при исполнении с вероятностью повторения исполнения как в пределах одного программного сегмента (циклы), так и возврата к выполнению команд ранее выполнявшихся сегментов (вложенность программы). Это учитывается за счет размещения команд сегмента в буфере команд по значению их индекса относительно начала сегмента и за счет жесткого распределения всей буферной памяти между различными сегментами.

Для данных учитывается, что реальные вопросы физической памяти для размещения таблиц страниц и собственно данных могут изменяться в значительных пределах.

Введенные аппаратные средства (регистры маски размеров таблиц и сумматор для формирования физического адреса данных) позволяют выделять физическую память в соответствии с реальными запросами, экономно расходуя оперативную память.

Предлагаемое устройство реализовано на внутренней локальной шине, которая является разделяемым ресурсом, т. е. только единственный блок может использовать шину в каждый момент времени. Так как имеется ряд потенциальных активных абонентов, подсоединенных к шине, каждый из которых может пытаться получить доступ к шине независимо, то необходимым элементом является блок арбитража.

Сравнение заявляемого технического решения с прототипом позволило установить соответствие его критерию "новизна". При изучении других известных технических решений в данной области техники признаки, отличающие изобретение от прототипа, не были выявлены и потому они обеспечивают заявляемому техническому решению соответствию критерию "существенные отличия".

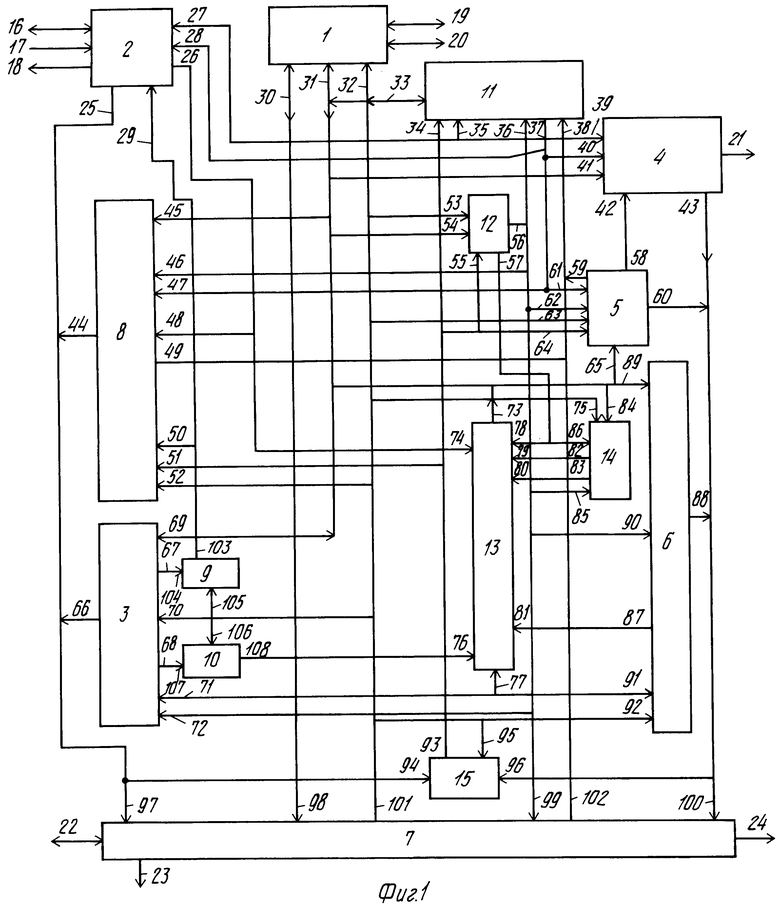

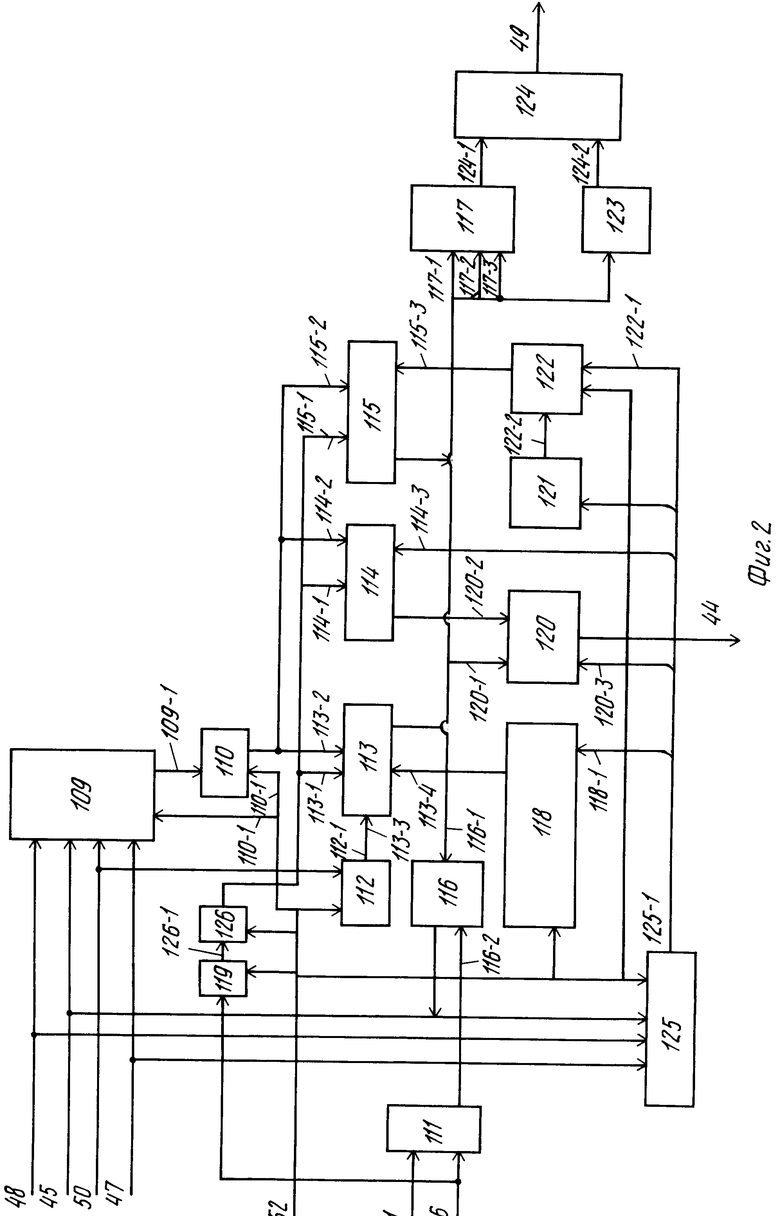

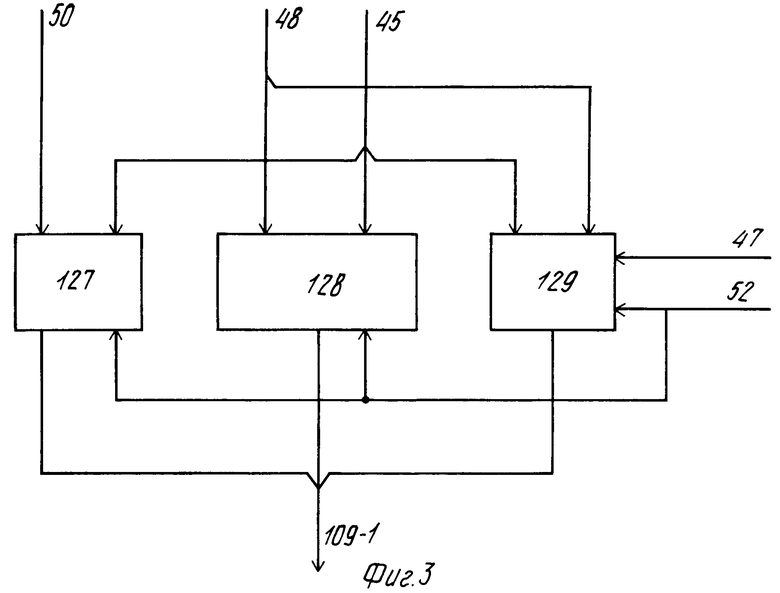

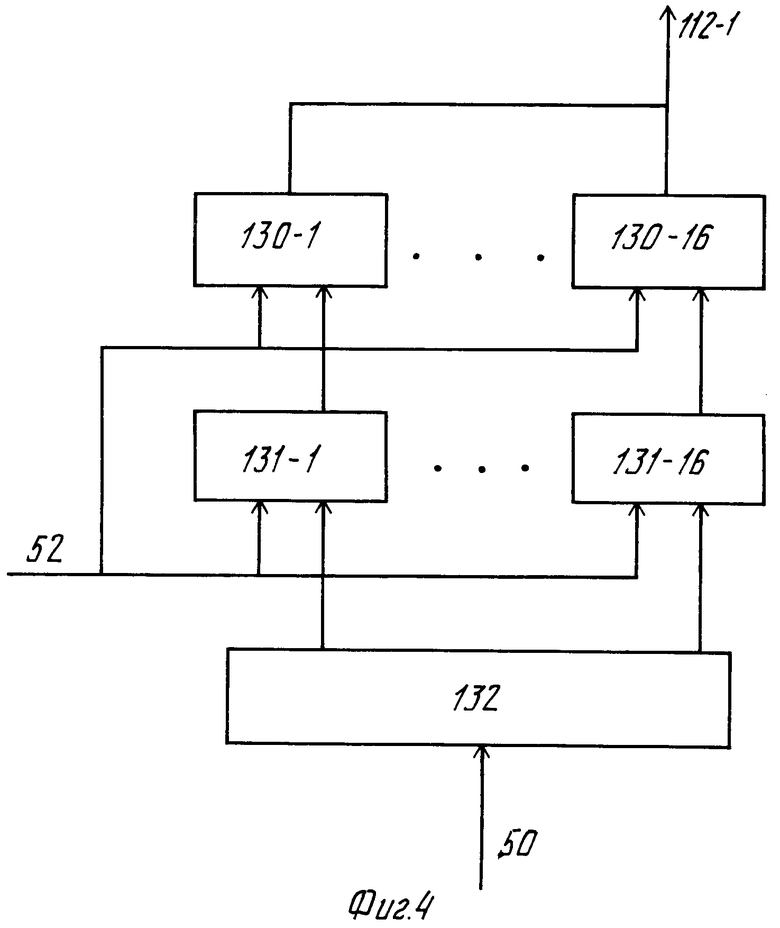

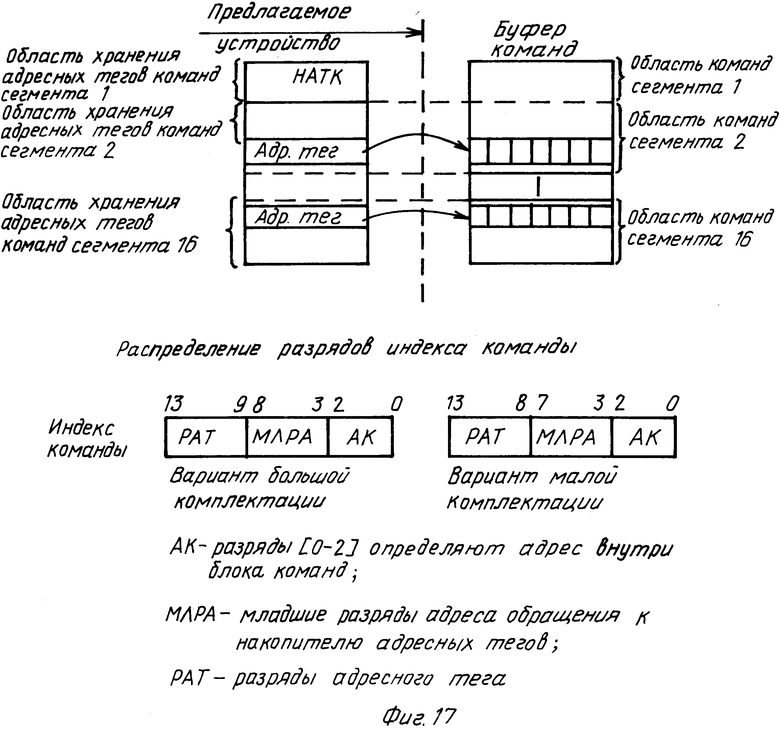

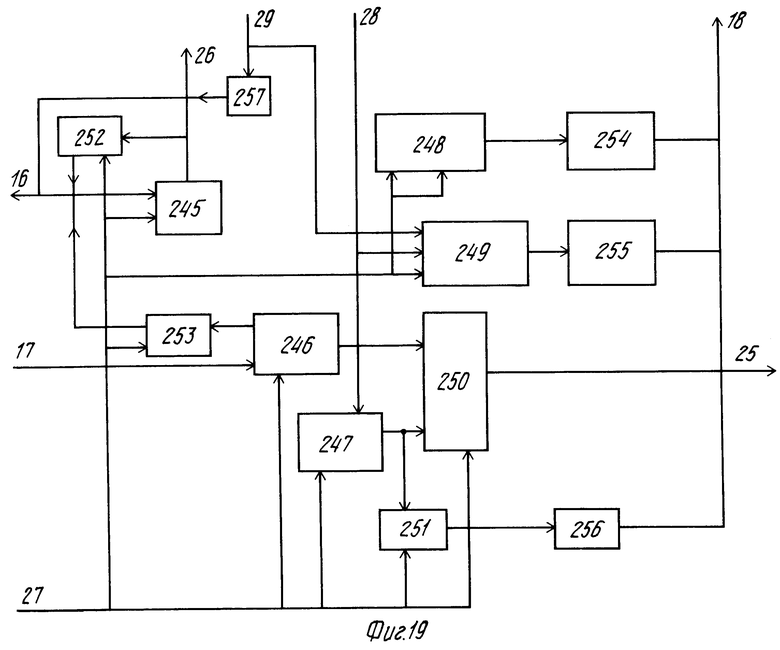

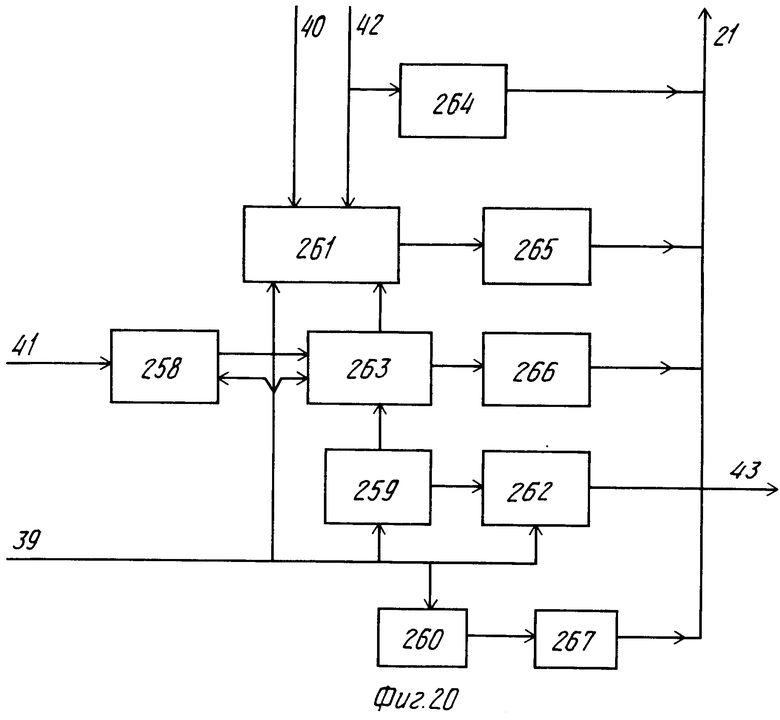

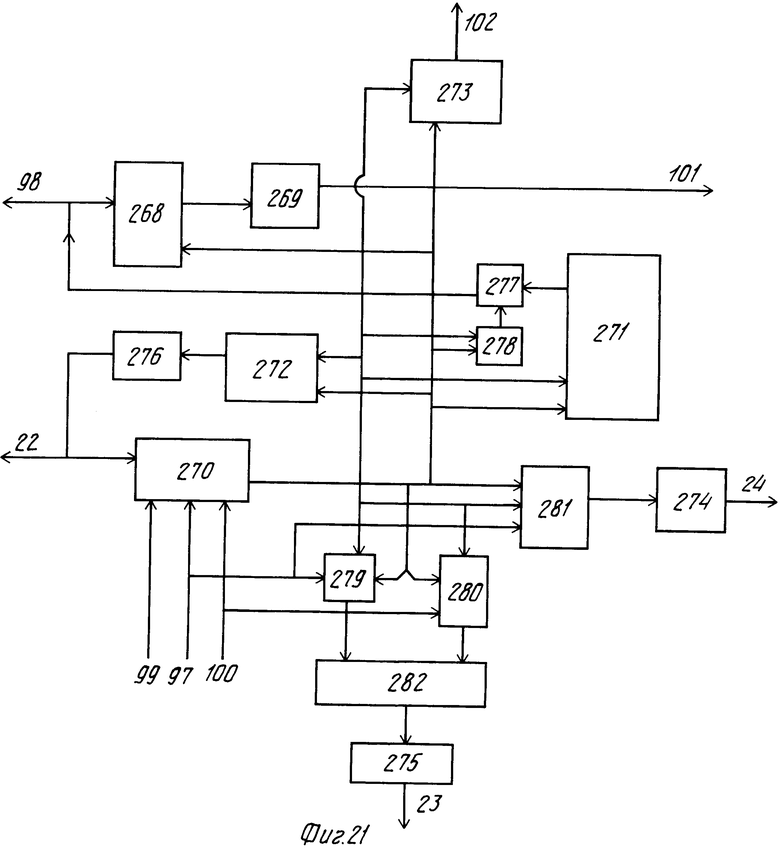

На фиг. 1 представлена схема устройства управления буферной памятью; на фиг. 2 - схема блока управления буферной памятью команд; на фиг. 3 - схема адресного мультиплексора, на фиг. 4 - схема узла обнуления признаков значимости; на фиг. 5 - схема информационного мультиплексора; на фиг. 6 - схема блока управления буферной памятью данных; на фиг. 7 - схема мультиплексора данных; на фиг. 8 - схема блока управления памятью сегментов; на фиг; 9 - схема блока управления памятью страниц; на фиг. 10 - схема блока регистров "номера зоны"; на фиг. 11 - схема блока регистров состояний; на фиг. 12 - схема блока регистров адреса; на фиг. 13 - схема блока сумматора; на фиг. 14 - схема блока регистров; на фиг. 15 - схема формирования адреса обращения к накопителю адресных тегов данных (НАТД) и разрядов адресного тега из поступившего адреса; на фиг. 16 - формирование признака совпадения хранимого адресного тега с разрядами адресного тега поступившего адреса; на фиг. 17 - структурная схема управления буфера команд и распределение индекса команды для большой и малой комплектации; на фиг. 18 - структура строки накопителя адресных тегов команд (НАТК); на фиг. 19 - схема порта буфера команд; на фиг. 20 - схема порта буфера данных; на фиг. 21 - схема блока центрального управления.

Устройство (фиг. 1) содержит порт 1 данных, порт 2 буфера команд, блок 3 управления памятью сегментов, порт 4 буфера данных, блок 5 управления буферной памятью данных, блок 6 управления памятью страниц, блок 7 центрального управления, блок 8 управления буферной памятью команд, блок 9 регистров "номера зоны", регистр 10 дескриптора программного сегмента (ДПС), блок 11 регистров состояний, блок 12 регистров адреса, блок 13 сумматора, блок 14 регистров, блок 15 арбитража, адресные входы-выходы 16, соединенные с информационными входами порта 2 буфера команд, вход 17 обращения к буфере команд, соединенный с входом запуска порта 2 буфера команд, первую группу информационных выходов 18, являющуюся одноименной группой выходов порта 2, информационные входы-выходы 19, являющиеся входами-выходами первой группы порта 1 данных, входы-выходы 20 признаков типов информации, являющиеся входами-выходами первой группы признаков типов информации порта 1 данных, информационные выходы 21 второй группы, подключенные к информационным выходам порта 4 буфера данных, вход-выход 22 признака готовности данных, являющийся первым входом-выходом блока 7 центрального управления, выход 23 сигнала контроля, подключенный к одноименному выходу блока 7 центрального управления, выход 24 признака готовности команд, подключенный к одноименному выходу блока 7. Порт 2 буфера буфера команд имеет выход 25 признака готовности команд, вторую группу информационных выходов 26, входы 27 управления циклом обращения к буферу команд, входы 28 управления выборкой и комплектацией, входы 29 "номера зоны". Порт 1 данных имеет вторую группу входов-выходов 30 признаков типов информации, вторую группу информационных входов-выходов 31 и входы 32 управления режимами работы. Блок 11 регистров состояний имеет информационные входы-выходы 33, вход 34 разрешения выдачи данных, входы 35 управления приемом в регистры, адресный вход 36, выходы 37 и входы 38 влагов состояний. Порт 4 буфера данных имеет входы 39 управления циклом обращения к буферу данных, вход 40 признака комплектации, информационные входы-выходы 41, информационные входы 42 и выход 43 признака готовности данных. Блок 8 управления буферной памятью команд имеет выход 44 признака готовности команд, информационные входы-выходы 45, адресный вход 46, вход 47 признака комплектации, адресные входы 48, информационный выход 49, входы 50 "номера зоны", вход 51 разрешения выдачи данных и входы 52 управления режимами работы. Блок 12 регистров адреса имеет входы 53 управления приемом в регистры, информационные входы-выходы 54, вход 55 управления выдачей данных, первую группу выходов 56 и вторую группу выходов 57. Блок 5 управления буферной памятью данных имеет информационные выходы 58, информационный выход 59, выход 60 признака готовности данных, вход 61 признака комплектации, адресный вход 62, входы 63 управления режимами работы, вход 64 разрешения выдачи данных и информационные входы-выходы 65. Блок 3 управления памятью сегментов имеет выход 66 наличия дескриптора программного сегмента, первую 67 и вторую 68 группы информационных выходов, информационные входы-выходы 69, входы 70 управления режимами работы, вход 71 разрешения выдачи данных и адресный вход 72. Блок 13 сумматора имеет первую 74, вторую 76, третью 78 четвертую 79, пятую 80 и шестую 81 группы информационных входов, входы 77 управления выбором слагаемых и выходы 73. Блок 14 регистров имеет выходы 82 смещения строки таблицы страниц, выходы 83 адреса начала таблицы страниц, первую 84, вторую 85 и третью 86 группы информационных входов и вход 75 управления приемом. Блок 6 управления памятью страниц имеет информационные выходы 87, выход 88 наличия строки таблицы страниц, информационные входы-выходы 89, адресный вход 90, вход 91 разрешения выдачи данных, входы 92 управления режимами работы. Блок 15 арбитража имеет выходы 93 разрешения выдачи данных, входы 94 признаков готовности команд, входы 95 управления режимами работы и входы 96 признаков готовности данных. Блок 7 центрального управления имеет входы 97 признаков готовности команд, входы-выходы 98 признаков команды, адресные входы 99, входы 100 признаков готовности данных, выходы 101 управления внутренними циклами работы устройста и выход 102 признака прерывания. Блок 9 регистров "номера зоны" имеет выходы 103 "номера зоны", информационные входы 104 и вход 105 управления приемом в регистры. Регистр 10 ДПС имеет вход 106 управления приемом в регистр, информационные входы 107 и выходы 108.

Порт 2 буфера команд, блок 8 управления буферной памятью команд, блок 3 управления памятью сегментов через выходы 25, 44, 66 соединены с блоком 7 центрального улправления и блоком 15 арбитража. Порт 1 данных через инфомрационные входы-выходы 31 второй группы соединен с блоком 11 регистров состояний, портом 4 буфера данных, блоком 8 управления буферной памятью команд, блоком 12 регистров адреса, блоком 5 управления буферной памятью данных, блоком 6 управления памятью страниц, блоком 14 регистров, блоком 3 управления памятью сегментов и блоком 13 сумматора. Порт 1 данных через входы-выходы 30 признаков типов информации второй группы соединен с блоком 7 центрального управления, выходы 101 управления внутренними циклами работы устройства которого соединены с блоком 6 управления памятью страниц, блоком 14 регистров, блоком 5 управления буферной памятью данных, блоком 12 регистров адреса, портом 4 буфера данных, блоком 11 регистров состочний, портом 1 данных, портом 2 буфера команд, блоком 8 управления буферной памятью команд, блоком 3 управления памятью сегментов, блоком 9 регистров "номера зоны", регистром 10 ДПС. Порт 4 буфера данных, блок 5 управления буферной памятью данных через выход 60 признака готовности данных, блок 6 управления памятью страниц через выход 88 наличия строки таблицы страниц соединены с блоком 15 арбитража и блоком 7 центрального управления. Блок 5 управления буферной памятью данных через информационные выходы 58 соединен с портом 4 буфера данных, блок 7 центрального управления через выход 102 признака прерывания, блок 8 управления буферной памятью команд через информационный выход 49 и блок 5 управления буферной памятью данных через выход 59 соединены с блоком 11 регистров состояний. Блок 12 регистров адреса через выходы 56 первой группы соединен с блоком 11 регистров состояний, блоком 8 управления буферной памятью команд, блоком 5 управления буферной памятью данных, блоком 14 регистров, блоком 6 управления памятью страниц, блоком 3 управления памятью сегментов, блоком 7 центрального управления. Блок 15 арбитража через выходы 93 разрешения выдачи данных соединен с блоком 3 управления памятью сегментов, блоком 13 сумматора, блоком 6 управления памятью страниц, блоком 8 управления буферной памятью команд, блоком 5 управления буферной памятью данных, блоком 12 регистров адреса, блоком 11 регистров состояний, выходы 37 которого соединены с входом 40 признака комплектации порта 4 буфера данных, одноименными входами 61 и 47 блока 5 управления буферной памятью данных и блока 8 управления буферной памятью команд и входами 28 управления выборкой и комплектацией порта 2 буфера команд. Порт 2 буфера команд через информационные выходы 26 второй группы соединен с блоком 8 управления буферной памятью команд и блоком 13 сумматора. Блок 9 регистров "номера зоны" и блок 8 управления буферной памятью команд через выходы 103 "номера зоны" соединен с портом 2 буфера команд.

Блок 8 управления буферной памятью команд (фиг. 2) содержит адресный мультиплексор 109 с выходом 109-1, регистр 110 адреса с информационным входом 110-1, элемент И 111, узел 112 обнуления признаков значимости с выходом 112-1, узел 113 памяти признаков значимости с первым 113-1 и вторым 113-2 адресными входами, с первым 113-3 и вторым 113-4 информационными входами, узел 114 памяти разрядов адресных признаков с первым 114-1 и вторым 114-2 адресными входами и информационным входом 114-3, узел 115 памяти контрольных разрядов с первым 115-1 и вторым 115-2 адресными входами и информационным входом 115-3, узел 116 выходных усилителей с информационным входом 116-1 и управляющим входом 116-2, узел 117 контроля информации с первым 117-1, вторым 117-2 и третьим 117-3 информационныыми входами, формирователь 118 признаков значимости с информационным входом 118-1, элемент И 119, узел 120 сравнения с первым 120-1, вторым 120-2 и третьим 120-3 информационными входами, формирователь 121 контрольного разряда, мультиплексор 122 записываемых контрольных разрядов с первым 122-1 и вторым 122-2 информационными входами, узел 123 контроля признаков значимости, элемент ИЛИ 124 с первым 124-1 и вторым 124-2 входами, информационный мультиплексор 125 с выходом 125-1, элемент ИЛИ 126 с первым входом 126-1.

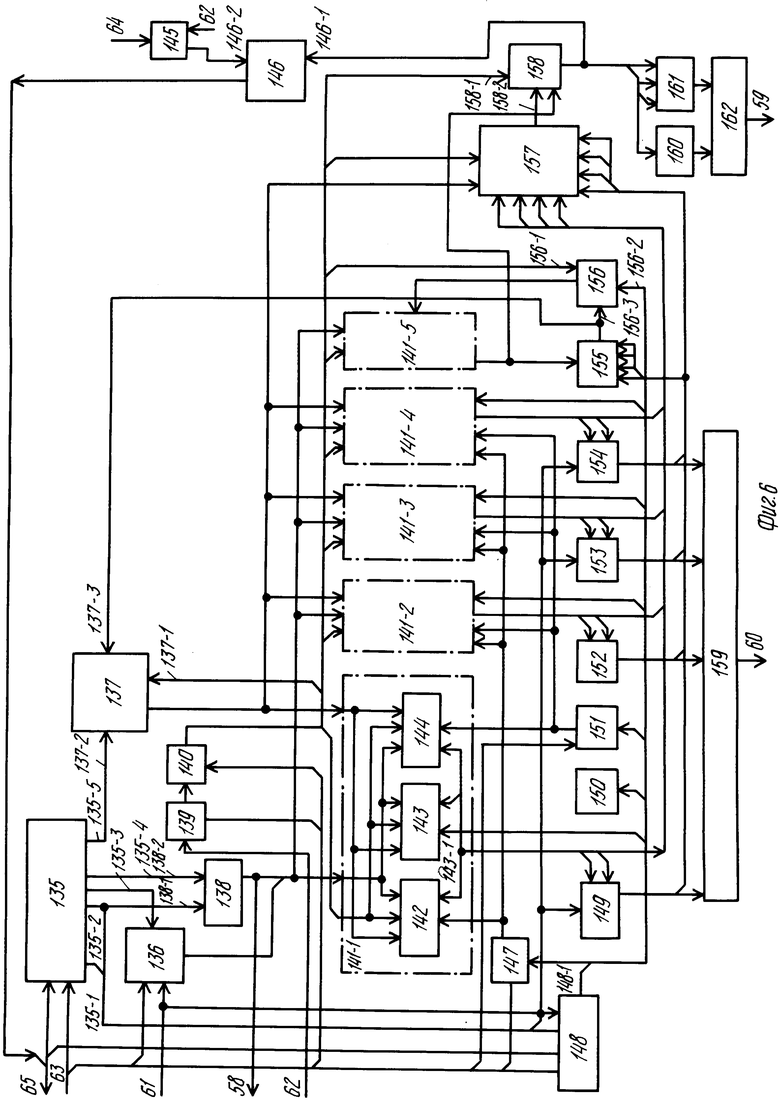

Адресный мультиплексор 109 (фиг. 3) содержит три мультиплексора 127, 128, 129.

Узел 112 обнуления признаков значимости (фиг. 4) содержит шестнадцать элементов ИЛИ 130-1. . . 130-16, шестнадцать элементов И 131-1. . . 131-16, дешифратор 132.

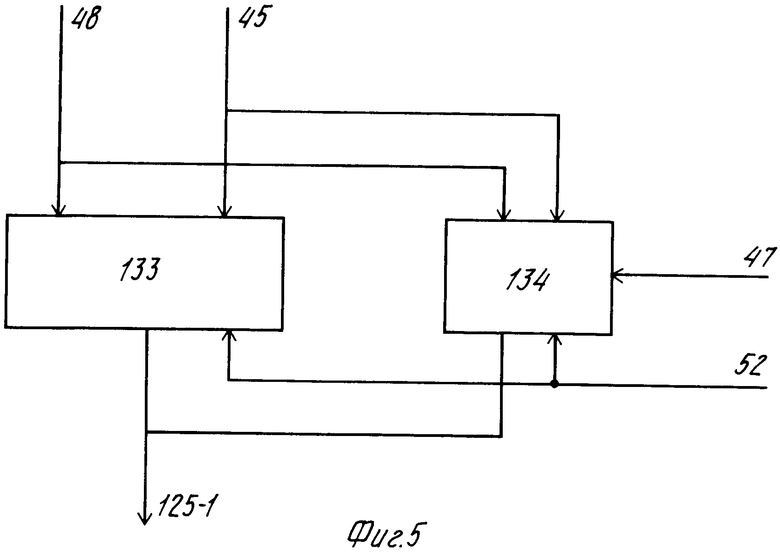

Информационный мультиплексор 125 (фиг. 5) содержит мультиплексоры 133, 134.

Блок 5 управления буферной памятью данных (фиг. 6) содержит регистр 135 адреса с первым по пятый адресными выходами 135-1. . . 135-5, первый 136 и второй 137 мультиплексоры адреса, узел 138 смешивания разрядов с информационными входами 138-1, 138-2, элемент И 139, элемент ИЛИ 140, узлы 141-1. . . 141-4 памяти адресных тегов, узел 141-5 памяти признаков приоритетов, причем узлы 141-1. . . 141-4 памяти адресных тегов состоят из элемента 142 памяти признаков значимости, элемента 143 памяти разрядов адресных тегов с адресным входом 143-1, элемента 144 памяти контрольных разрядов, элемент И 145, узел 146 выходных усилителей, формирователь 147 признаков значимости, первый мультиплексор 148 данных с информационным выходом 148-1, первый узел 149 сравнения адресных тегов, формирователь 150 контрольного разряда, мультиплексор 151 записываемых контрольных разрядов, второй 152, третий 153 и четвертый 154 узлы сравнения адресных тегов, формирователь 155 адреса замещаемой колонки, мультиплексор 156 данных признаков старения с первым 156-1, вторым 156-2 и третьим 156-3 информационными входами, второй мультиплексор 157 данных, регистр 158 данных с первым 158-1 и вторым 158-2 информационными входами и адресным входом 158-3 и выходом 158-4, элемент ИЛИ 159, узел 160 контроля признаков значимости, узел 161 контроля информации, элемент ИЛИ 162.

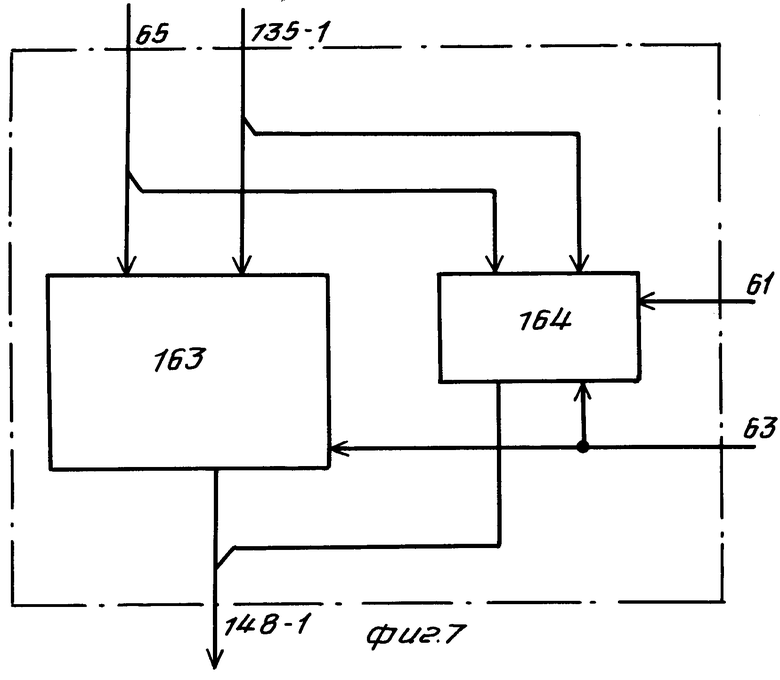

Мультиплексор 148 данных (фиг. 7) содержит мультиплексоры 163, 164.

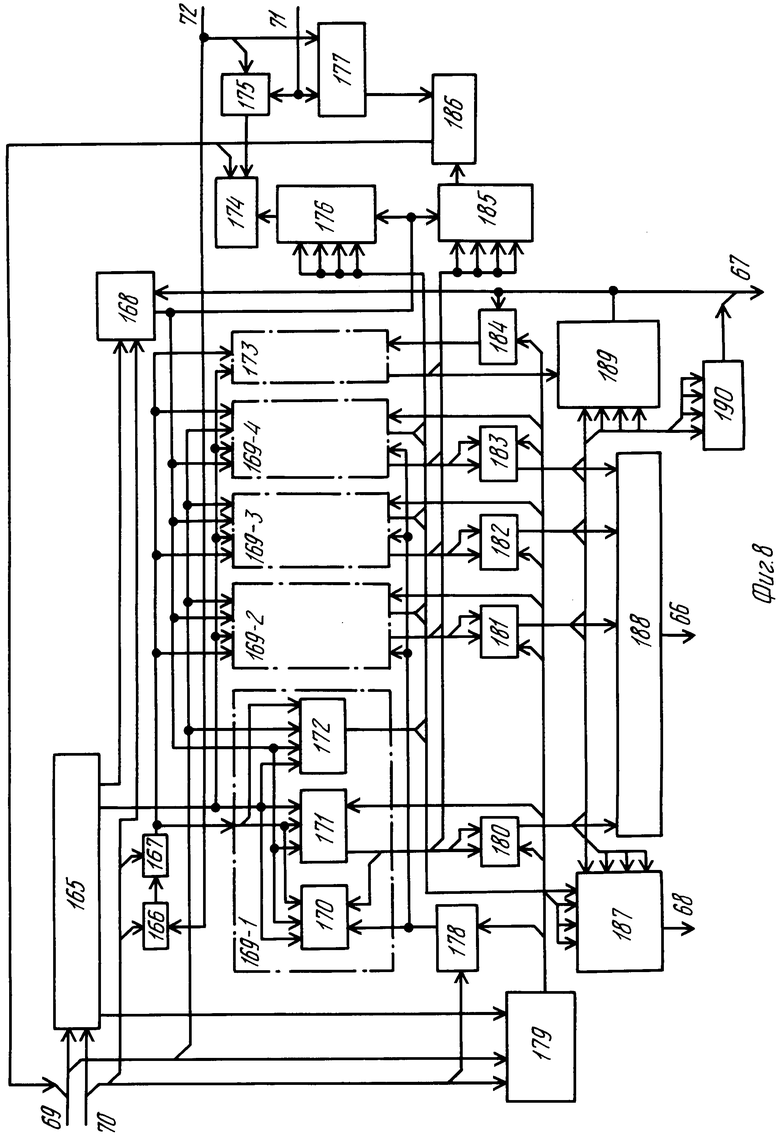

Блок 3 управления памятью сегментов (фиг. 8) содержит регистр 165 адреса, элемент И 166, элемент ИЛИ 167, мультиплексор 168 адреса колонки, колонки 169-1. . . 169-4 узлов памяти, каждая из которых содержит узел 170 памяти признаков значимости, узел 171 памяти разрядов адресных тегов и узел 172 памяти дескрипторов программных сегментов, узел 173 памяти признаков старения, узел 174 выходных усилителей, элемент И 175, мультиплексор 176 данных, элемент И 177, формирователь 178 признаков значимости, первый мультиплексор 179 данных, узлы 180. . . 183 сравнения адресных тегов, мультиплексор 184 данных узла памяти, второй мультиплексор 185 данных, узел 186 выходных усилителей, третий мультиплексор 187 данных, элемент ИЛИ 188, элемент 189 формирования номера колонки для замещения, шифратор 190.

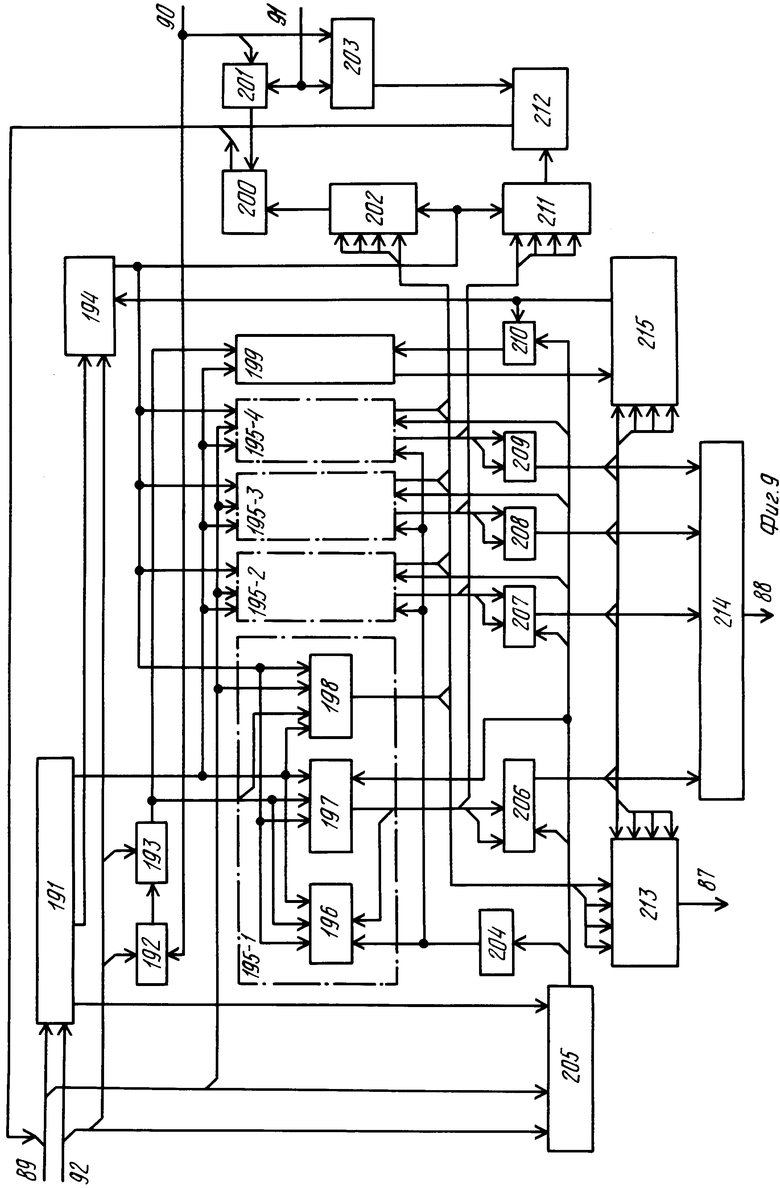

Блок 6 управления памятью старниц (фиг. 9) содержит регистр 191 адреса, элемент И 192, элемент ИЛИ 193, мультиплексор 194 адреса колонки, колонки 195-1. . . 195-4 узлов памяти, каждая из которых содержит узел 196 памяти признаков значимости, узел 197 памяти разрядов адресных тегов и узел 198 памяти физических адресов, узел 199 памяти признаков старения, узел 200 выходных усилителей, элемент И 201, мультиплексор 202 данных, элемент И 203, формирователь 204 признаков значимости, мультиплексор 205 данных, узлы 206. . . 209 сравнения адресных тегов, мультиплексор 210 данных накопителя, мультиплексор 211 данных, узел 212 выходных формирователей, мультиплексор 213 данных, узел 214 формирования номера колонки для замещения, элемент ИЛИ 215.

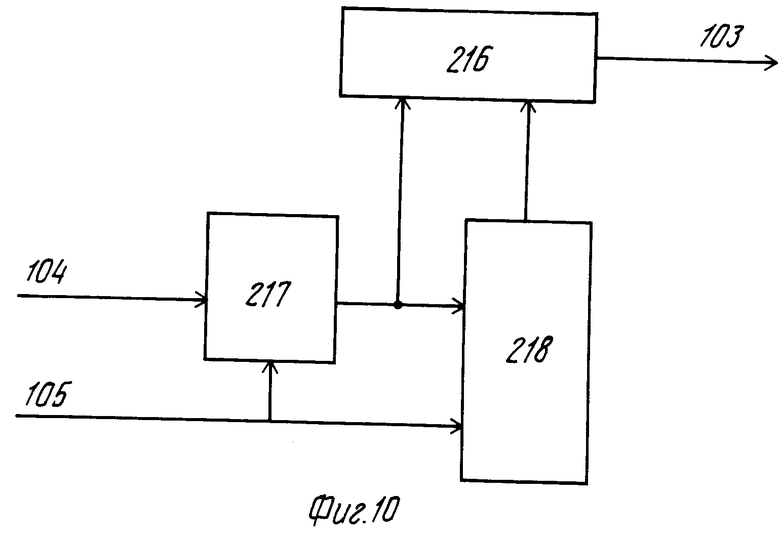

Блок 9 регистров "номера зоны" (фиг. 10) содержит мультиплексор 216 "Номер зоны", регистр 217 следующего "номера зоны", регистр 218 текущего "Номера зоны".

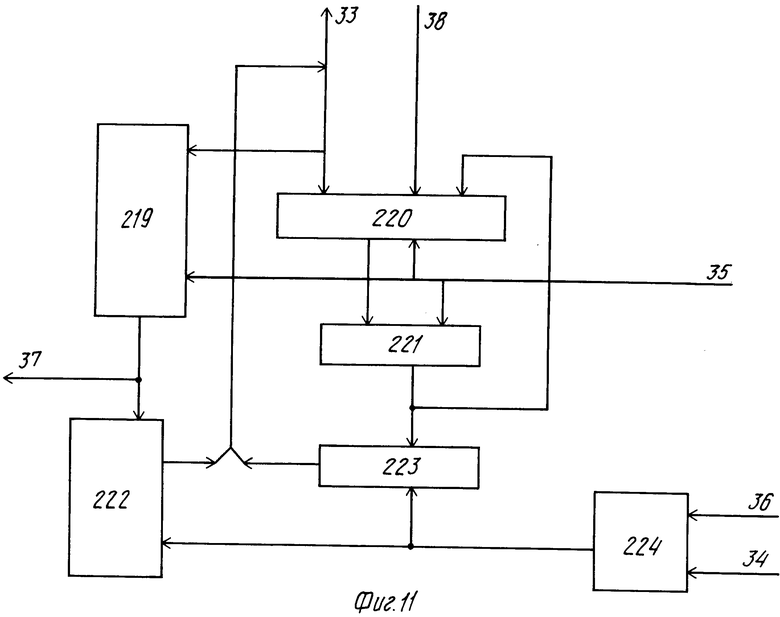

Блок 11 регистров состояний (фиг. 11) содержит регистр 219 состояницй, элемент 220 входной логики, регистр 221 уточненного состояния, блоки 222, 223 шинных формирователей, элемент И 224.

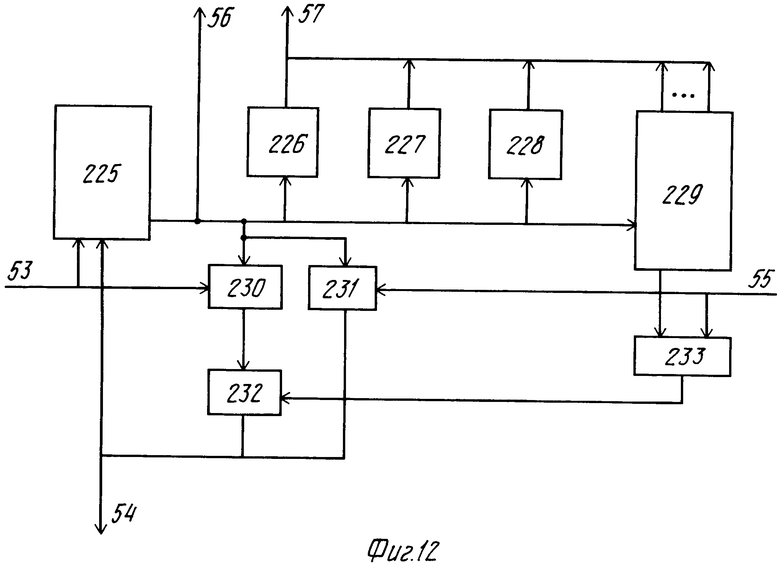

Блок 12 регистров адреса (фиг. 12) содержит регистр 225 адреса, узлы 226. . . 228 сравнения, дешифратор 229 номера внешнего регистра, регистр 230 адреса, дублирующий узлы 231, 232 выходных усилителей, элемент И 233.

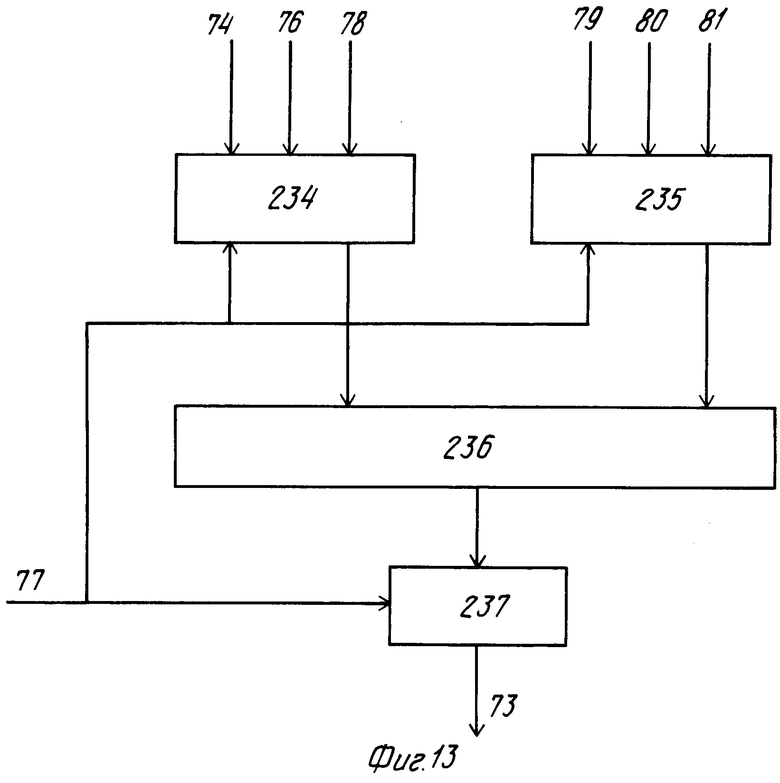

Блок 13 сумматора (фиг. 13) содержит мультиплексор 234 первого операнда, мультиплексор 235 второго операнда, сумматор 236 и узел 237 выходных усилителей.

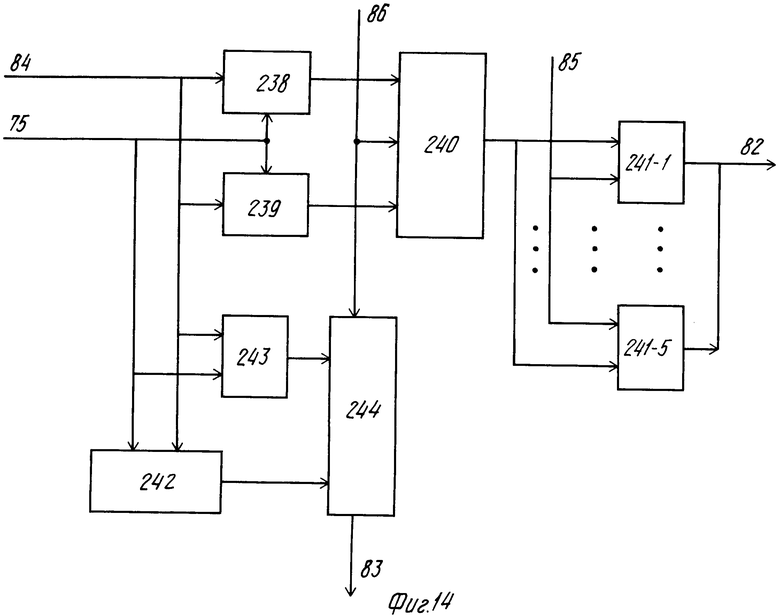

Блок 14 регистров (фиг. 14) содержит регистр 238 маски системы, регистр 239 маски пользователя, мультиплексор 240 регистров маски, элементы И 241-1. . . 241-5, регистр 242 таблифцы страниц пользователя, регистр 243 таблицы страниц системы, мультиплексор 244 регистров таблиц.

Порт 1 данных выполнен аналогично известному порту данных.

Порт 2 буфера команд (фиг. 19) содержит регистр 245 индекса, счетчик 246 младших разрядов, счетчик 247 числа циклов, дешифраторы 248. . . 251, узлы 252, 253 выходных усилителей, усилители-формирователи 254. . . 257.

Порт 4 буфера данных (фиг. 20) содержит регистр 258 младших разрядов, счетчик 259 младших разрядов, дешифраторы 260. . . 262, мультиплексор 263, усилители-формирователи 264. . . 267.

Блок 7 центрального управления (фиг. 21) содержит регистр 268 команд, дешифратор 269 команд, автомат 270 состояний, шифраторы 271. . . 273, усилители-формирователи 274. . . 276, узел 277 выходных усилителей, элементы И 278. . . 281, элемент ИЛИ 282.

В порте 2 буфера команд дешифратор 248 формирует сигналы "Разрешение записи" и "Разрешение выхода" для микросхем памяти, образующих буфер команд, дешифратор 249 формирует сигналы "Выборки кристаллов" с учетом комплектации буфера (вход 28) и значения одного из разрядов "номера зоны" (входы 29), дешифратор 250 формирует признак "Готовность порта буфера команд" для двух вариантов обращения: при обращении в буфер команд после завершения подкачки блока команд из оперативной пкамяти в буфер, при обращении во внешнее ПЗУ в зависимости от быстродействия микросхем ПЗУ, дешифратор 251 формирует сигналы "Выборка кристаллов" и "Разрешение выхода" для микросхем памяти, образующих внешнее ПЗУ. Счетчик 246 младших разрядов формирует последовательные значения младших разрядов адреса при выполнении подкачки блока команд из оперативной памяти в буфер. Сформированное значение через узлы 252, 253 выходных усилителей и далее по входам-выходам 16 устройства поступают на адресные входы микросхем памяти, образующих буфер команд. Счекчтик 247 считает число циклов, необходимых для обращения к медленному внешнему ПЗУ. Во время работы счетчика на дешифраторе 251 формируются сигналы управления микросхемами, образующими внешнее ПЗУ, а на выходе дешифратора 250 формируется признак "Неготовность порта буфера команд", по которому выполняется приостановка работы центрального процессора (ЦП) до получения очередной команды из внешнего ПЗУ. Через узел 252 выходных усилителей значения старших разрядов индекса команды в режиме подкачки блока команд из оперативной памяти в буфер выдаются через входы-выходы 16 устройства на адресные входы микросхем памяти, образующих буфер команд. Через усилители-формирователи 254. . . 257 значения адресных и управляющих сигналов через входы-выходы 16 и выходы 18 устройства выдаются на входы микросхем памяти, образующих буфер команд.

В качестве примера реализации порта 4 буфера данных может служить следующее. Дешифратор 260 формирует сигналы "Разрешение записи" и "Разрешение выхода" для микросхем памяти, образующих буфер команд. Дешифратор 261 формирует сигналы "Выборка кристаллов" с учетом комплектации буфера (вход 40) и значения одного из разрядов адреса (входы 42). Дешифратор 262 формирует признак "Готовность порта буфера данных" в режиме подкачки блока данных из оперативной памяти в буфер по значению сигнала переполнения счетчика младших разрядов (СчМлР). СчМлР формирует последовательные значения младших разрядов адреса при выполнении подкачки блока данных из оперативной памяти в буфер. Сформированные значения через мультиплексор 263 и группу усилителей-формирователей 266 и далее через информационные выходы 21 выдаются на адресные входы микросхем памяти, образующих буфер данных. На регистре 258 фиксируется значение младших разрядов адреса слова данных, в цикле передачи данных между буфером данных и ЦП значения младших разрядов через мультиплексор 263 данных и группу усилителей-формирователей 266 и далее через информационные выходы 21 выдаются на адресные входы микросхем памяти, образующих буфер данных. Через группы усилителей-формирователей 264. . . 267 значения адресных и управляющих сигналов через выходы 21 устройства выдаются на входы микросхем памяти, образующих буфер данных.

В блоке 7 центрального управления на регистре 268 фиксируется поступающий код команды (условие приема кода команды определяется выходным сигналом автомата 270 состояний. Код команды поступает с входов-выходов 20 устройства через порт 1 и далее на входы-выходы 98 блока. Выходы дешифратора 269 команд и выходы внутренних состояний автомата 270 образуют выходы 101 блока центрального управления. На выходе 102 блока шифратором 273 прерываний формируются сигналы прерываний типа "Нет страницы данных", "Нет сегмента кода команд", "Признак первой записи в страницу данных". На входах-выходах 98 блока шифратором 271 управляющих признаков формируются разряды кода команды при обращениях предлагаемого устройства в оперативную память при групповых или словных обращениях за данными, при групповых подкачках команд. Сформированные значения признаков выдаются на в ходы-выходы 98 через узел 277 выходных усилителей, открываемый выходом э лемента И 278. Одновременно с выдачей управляющих признаков шифратором 272 управляющих сигналов формируются сигналы, определяющие фазу передачи адреса или фазу передачи данных. На выходах 24 и 23 устройства по значениям кода команды, внутренним состояниям и сигналам готовности блоков обработки команд пересылки данных (выход 25 порта 2 и выход 43 порта 4) и сигналам готовности блоков, обработки команд (выход 25 порта 2) на элементах И 279. . . 280 и элементе ИЛИ 281 формируются обобщенные признаки завершения обработки команды (выход 24) или фаз адресации или передачи данных (выход 23).

Блок 15 арбитража содержит дешифратор, который по значениям кода команды, состояниям автомата (входы 95) и сигналам готовности блоков обработки команд и данных (входы 94 и 96) формирует сигналы разрешения выдачи во внутреннюю шину или значений блока 13, или считанных значений других блоков при выполнении команд "Считать внешний регистр".

Работает устройство следующим образом.

Обработка запроса ЦП за очередной командой. На адресные входы-выходы 16 устройства поступает адрес очередной команды, сопровождаемый стробом адреса. Одновременно этот адрес поступает из микросхемы памяти, образующий буфер команд, во внешнее ПЗУ подпрограмм. Отсутствие строба означает, что ЦП считывает команды из внутреннего ПЗУ подпрограмм. Сигналом, передаваемым на вход 17 обращения к буферу команд, дополнительно указывается, что обращение выполняется к внешнему ПЗУ подпрограмм, а не в буфер команд. Поступивший адрес команды запоминается в порте 2 буфера команд устройства и поступает в блок 8 управления буферной памятью команд, где проверяется наличие запрошенной команды в буфере команд. Порт 2 буфера команд приписывает к адресу разряды, опредьеляющие номер блока, и выдает управляющие стробы в буфер команд или внешнее ПЗУ, откуда считанная команда поступает в ЦП. В случае отсутствия запрашиваемой команды в буфере (о чем сообщает сигнал блока 8 управления буферной памятью команд, поступающий в первую шину признаков готовности) блоком 7 центрального управления формируется сигнал неготовности, выдаваемый в ЦП на выход 24 признака готовности команд, и устройством выполняется запрос в оперативную память по информационным входам-выходам и входам-выходам 20 признаков типов информации.

Так как ЦП работает с адресами команд в виде относительных индексов в пределах текущего программного сегмента кода, то перед обращением в оперативную память производится формирование полного физического адреса сложением базы программного сегмента и индекса. Смена базы программного сегмента осуществляется блоком 3 управления памятью сегментов, блоком 9 регистров "номера зоны", регистром 10 ДПС при выполнении специальных команд межсегментных переходов.

На время выполнения подкачки строки команд из оперативной памяти в буфер команд последовательные адреса слов внутри строки формируются портом 2 буфера команд и выдаются в первую очередь на адресные входы-выходы 16 устройства. Передача очередного слова команды в буфер сопровождается управляющим сигналом, поступающим в устройство на вход-выход 22 признака готовности данных, и вызывает изменение адреса, выдаваемого портом 2 буфера команд. По завершении подкачки строки команд в буфер портом 2 буфера команд выдается сигнал в ЦП по шине строба адреса команды и ЦП повторно выполняет чтение команды из буфера команд.

Необходимо отметить, что в устройстве имеется возможность работы с буферами команд и данных большой и малой емкости. Признак текущего размера буфера поступает в порт 2 буфера команд и порт 4 буфера данных из блока 11 регистров состояний и упраляет дешифратором сигналов выборки микросхем памяти, составляющих буфер. При малой комплектации буфера обеспечивается управление двумя независимыми наборами микросхем памяти (в качестве примера реализации можно указать на микросхемы памяти с организацией 2kх8, емкость буфера в этом случае составляет 16 кбайт). При большой комплектации буфера обеспечивается управление одним набором микросхем памяти. В качестве примера реализации можно указать на микросхемы памяти с организацией 8kх8, емкость буфера команд в этом случае составляет 32 кбайт.

Кроме блоков порта 2 буфера команд и порта 4 буфера данных признак размера буфера поступает в блок 8 управления буферной памятью команд и блок 6 управления памятью страниц, ограничивая для варианта малого буфера число используемых строк в накопителях адресных тегов.

Предусмотрено несколько типов ПЗУ, различающихся быстродействием. Признак текущего типа ПЗУ задается программно и хранится в блоке 11 регистров состояний, откуда выдается в порт 2 буфера команд, где выполняет модификацию временной диаграммы обращения к внешнему ПЗУ. Возможные варианты отличаются между собой на целое число циклов работы устройства: возможна работа с быстрым ПЗУ, время доступа к которому укладывается в один цикл работы устройства, возможна работа с ПЗУ, время доступа к которому не превышает двух и четырех циклов.

Блок 5 управления буферной памятью данных (фиг. 6) содержит НАТД тех данных, коды которы находятся в буфере данных. Буфер данных не входит в состав предлагаемого устройства, но реализация порта 4 буфера данных, управляющего сопряжением с буфером, допускает две комплектации (аналогично с буфером команд).

Блок 5 управления буферной памятью данных работает с математическими адресами. Благодаря тому, что в этом случае исключено преобразование математического адреса в физический, предлагаемое устройство потенциально может обеспечить меньшее время доступа к данным, размещенным в буфере, чем аналогичное устройство, использующее физические адреса.

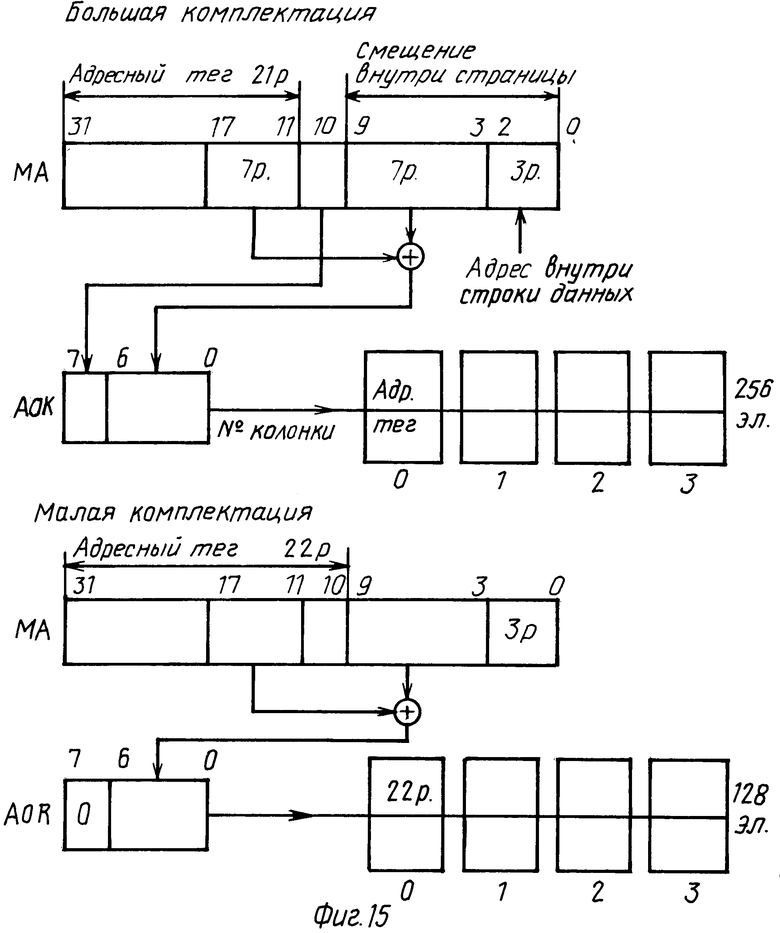

Отличие НАТД от НАТК заключается во внутренней организации накопителя: 1024 его строки разделены на четыре колонки (узлы 141-1. . . 141-4) и адресный тег может быть помещен в соответствующую строку любой из них. В свою очередь в составе колонки выделяются элемент 142 памяти признаков значимости, элемент памяти 143 разрядов адресных тегов, элемент памяти 144 контрольных разрядов. Конкретный номер колонки определяется механизмом "старения" определяющим элемент строки, к которому дольше всего не было обращения. Реализация механизма "старения" для четырех элементов подробно описана в литературе. Механизм "старения" включает накопитель признаков приоритетов и формирователь 155 адреса замещаемой колонки и нового значения приоритетов. Соответственно для каждой колонки существует своя схема сравнения (149, 152. . . 154), формирующая признак совпадения хранимого адресного тега (фиг. 16) с разрядами адресного тега поступившего адреса. Обобщенный сигнал попадания формируется элементом ИЛИ 159.

Формирование адреса обращения к НАТД и разрядов адресного тега из поступившего адреса показано на диаграмме (фиг. 15). Необходимо отметить следующую особенность адресации строк НАТД. Из статистики выделения физической памяти следует, что объем реально выделяемой памяти может быть меньше размера математической страницы (210 слов). Если не принять специальных мер, то данные различных страниц размещаются в одних и тех же строках НАТД, вытесняя друг друга, и в то же время не полностью используется емкость НАТД в той его части, где должны помещаться данные с большими смещениями относительно начала страницы. Чтобы избежать этого адрес строки НАТД получается на узле 138 смешивания разрядов смешиванием младших разрядов номера страницы со старшими разрядами смещения внутри страницы.

С введением механизма "старения" усложняется (вводится мультиплексор 137 адреса колонки) схема формирования адреса записи нового значения адресного тега с учетом номера колонки, формируемого формирователем 155 адреса замещаемой колонки.

Варианты работы блока 5: обращение в буфер данных, данные есть в буфере; обращение в буфер данных, данных нет в буфере - подкачка данных.

Вариант 1.

В первом цикле принимается адрес данных через информационные входы-выходы 19 устройства, порт 1 данных, входы-выходы 65 блока 5 на регистр 135 адреса. Из полученного адреса на выходах мультиплексора 136 адреса и узла 138 смешивания разрядов формируется адрес строки и производится одновременное считывание из четырех колонок. Считанные значения с информационных выходов узлов 141-1. . . 141-4 памяти адресных тегов постуают на узлы 149, 152, 153, 154 сравнения адресных тегов. Признак "попадания" на выходах схем сравнения формируется при совпадении хранимого адресного тега с разрядами адресного тега принятого адреса данных (выходы 135-1, 135-2 регистра 135 адреса) и единичном значении бита значимости (ЗН). На выходе 60 признака готовности через элемент ИЛИ 159 формируется обобщенный признак "попадания" - признак наличия данных в буфере данных, по которому блоком 7 центрального управления формируется признак "готовности данных" (ГД), необходимый ЦП для завершения цикла передачи адреса. В этом случае (при наличии блока данных в буфере) в следующем цикле выполняются чтение данных и передача их в ЦП под управлением порта 4 буфера данных, который передает адрес по буферу данных и формирует последовательность сигналов управления микросхемами буфера на информационных выходах 21 второй группы предлагаемого устройства. Одновременно с чтением из узлов памяти адресных тегов выполняется чтение значений из узла 141-5 памяти признаков приоритетов ("старения") и при "попадании" на выходе формирователя 155 адреса замещаемой колонки формируется новое значение приоритетов. Колонка, в которой произошло совпадение (по значениям выходов узлов 149, 152, 153, 154 сравнения адресных тегов), становится самой "молодой", а соотношение приоритетов между остальными колонками сохраняется, в последующем через мультиплексор 148 данных накопителя признаков старения новое значение приоритетов записывается в узел 141-5 памяти признака приоритетов.

Вариант 2.

При наличии признака "промаха" на выходе элемента ИЛИ 159 и на выходе 60 признака готовности блока 5 управления буферной памятью данных, т. е. отсутствии адресного тега для паоступившего адреса данных и соответственно отсутствии данных в буфере, признак ГД не выдается, что вызывает приостановку работы ЦП. Выполняется групповая подкачка блока данных из оперативной памяти через контроллер системного интерфейса КСИ. Адрес блока данных получается индексированием физического адреса начала страницы (выход 6-1 физического адреса блока 6 управления памятью страниц) разрядами смещения слова данных внутри страницы, поступающими на блок 13 сумматора соответственно через входы 81 физического адреса и 78 смещения в пределах страницы блока 13 сумматора.

В следующем цикле сформированный таким образом физический адрес с выхода сумматора через выходы 73 блока 13 сумматора, информационные входы-выходы 31 второй группы порта 1 данных, порт 1 данных, информационные входы-выходы 19 устройства передается в КСИ, сопровождаемый признаками группового считывания данных, формируемыми блоком 7 центрального управения и переданными с входов 32 управления режимами работы и порт 1 данных на входы-выходы признаков типов информации первой группы порта 1. Вышеописанный вариант формирования физического адреса блока подкачки данных использует математические адреса данных. Если полученный адрес данных уже является физическим, то адрес блока данных выдается из регистра адреса блока 12 регистров адреса через его информационные входы-выходы 54.

КСИ выполняет считывание блока данных из восьми слов и последовательно записывает их в буфер данных с информационных входов-выходов 19 устройства. Адресацию буфера выполняет порт 4 буфера данных устройства. По завершении подкачки блока данных новое значение адресного тега, контрольного разряда и единичное значение битов ЗН записываются в ту колонку, номер которой определяется механизмом "старения", и через мультиплексор 137 адреса колонки поступает на узлы 141-1. . . 141-4 памяти адресных тегов, после чего производится корректировка приоритетов. Колонка, в которую выполнена запись нового значения адресного тега, становится самой "молодой", а соотношение приоритетов между остальными колонками сохраняется. В последующем через мультиплексор 156 данных узла памяти признаков старения новое значение приоритетов записывается в узел 141-5 памяти признаков приоритетов. Единичное значение записываемых битов Зн формируется на выходе формирователя 147 признаков значимости под воздействием управляющих сигналов с входов 32 управления режимами работы.

Признак "Чтение-запись" на входы накопителей формируется на выходе элемента ИЛИ 140 из управляющего сигнала, поступившего на входы 32 управления режимами работы блока.

Предусмотрен контроль хранения информации в НАТД. Одновременно с занесением адресного тега в элемент 143 памяти разрядов адресных тегов в элемент 144 памяти контрольных разрядов блока 5 управления буферной памтью данных через мультиплексор 151 записываемых контрольных разрядов записывается соответствующее значение контрольного разряда, формируемое формирователем 150 контрольного разряда по значениям разрядов адресного тега. При считывании адресного тега контроль выполняется на выходе регистра 158 данных схемами контроля разрядов адресного тега, узлом 161 контроля информации при единичном значении бита Зн и контроля совпадения битов Зн узла 160 контроля признаков значимости. Обобщенный сигнал контроля через элемент ИЛИ 162 выдается на информационный выход 59 блока. Выбор данных на регистр 158 данных из одной из четырех колонок накопителя выполняется через второй мультиплексор 157 данных выходными сигналами узлов 149, 152, 153, 154 сравнения адресных тегов.

Блок 5 управления буферной памятью данных обеспечивает работу с двумя комплектациями буфера данных. Признак комплектации с входа 61 признака комплектации поступает на мультиплексор 136 адреса и первый мультиплексор 148 данных, управляя отсечением половины адресного пространства накопителя для малой комплектации в мультиплексоре 136 адреса и формированием определенного значения разряда адресного тега (фиг. 16) для большой комплектации в первом мультиплексоре 148 данных.

Для обеспечения тестируемости накопителя используются команды ЦП для работы с внешними регистрами. В адресном пространстве этих внешних регистров выделена область, перекрывающая все ячейки накопителя блока 5 управления буферной памятью данных, что позволяет обеспечить доступ как по считываних их содержимого в ЦП, так и по записи любого значения не только в поле адресного тега, но в том числе значений контрольных размеров и битов Зн. Во-первых, запись контрольных разрядов и битов Зн позволяет проверить работоспособность узлов 160 и 161 контроля признаков значимости и информации. Во-вторых, программный доступ к битам Зн обеспечивает возможность программного исключения данных из буфера данных, что может требоваться для поддержания совпадения значений версий данных, хранимых в буфере данных, и значений данных, хранимых в оперативной памяти. В случае расхождения этих версий можно, программно спросив бит Зн в узле памяти, обеспечить при следующих обращениях к этим данным обращение к их последней версии, хранимой в оперативной памяти (проблемы когерентности КЭШ).

Формирователь 147 признаков значимости обеспечивает принудительный сброс битов Зн всех строк узла памяти по начальной установке или при выполнении специальной команды, установку единичного значения битов Зн при занесении адресного тега в строку узла памяти, запись значения, поступающего с выхода первого мультиплексора 148 данных при выполнении команды "запись во внешний регистр". Выбор варианта работы формирователя 147 признаков значимости обеспечивается управляющими сигналами, поступающими на входы 63 управления режимами работы блока.

При выполнении команды "запись во внешний регистр" адрес внешнего регистра с информационных входов-выходов 65 поступает на регистр 135 адреса. По значению адреса мультиплексором 136 адреса, узлом 138 смешивания разрядов формируется адрес строки узла памяти, а мультиплексором 137 адреса колонки по значению младших разрядов поступившего адреса выбирается колонка. В следующем цикле поступившие данные с информационных входов-выходов 65 через первый мультиплексор 148 данных поступают на информационные входы элемента 143 памяти разрядов адресных тегов, запись значений битов Зн в элемент 142 памяти признаков значимости выполняется через формирователь 147 признаков значимости, а запись значения контрольного разряда в элемент 144 памяти контрольных разрядов производится через мультиплексор 151 записываемых контрольных разрядов. Программное чтение содержимого узлов памяти выполняется через узел 146 выходных усилителей, далее через инфомрационные входы-выходы 31 порта 1 и порт 1 данных на входы-выходы 20 признаков типов информации. Адрес считываемой строки в предыдущем цикле поступает с информационных входов-выходов 65 в регистр 135 адреса. Выходные усилители 146 открываются выходным сигналом элемента И 145, входом которого является вход 64 разрешения выдачи данных, подключенный к одному из выходов блока 15 арбитража, и признак того, что номер внешнего регистра, заданный в команде, совпадает с областью адресов, отведенной для строк узла памяти блока 5 управления буферной памятью данных (адресный вход 62 блока).

При считывании выбор колонки, данные из которой должны быть выданы, обеспечивается на втором мультиплексоре 157 данных разрядами номера колонки, формируемыми на выходе мультиплексора 137 адреса колонки из младших разрядов адреса внешнего регистра (пятый адресный выход 135-5 регистра 135 адреса). При выполнении команд "чтение-запись внешнего регистра" признак "Запись-чтение" на входы узлов 141-1. . . 141-4 памяти адресных тегов поступает через элемент И 139 и далее элемент ИЛИ 140. Входами элемента И 139 являются управляющий признак выполнения данной команды (входы 63 управления режима работы блока) и ранее описанный признак номера внешнего регистра на адресном входе 62 блока.

Блок 8 управления буферной памятью команд (фиг. 2) содержит узел памяти адресных признаков НАТК тех команд, коды которых находятся в буфере команд. Буфер команд не входит в состав предлагаемого устройства, но реализация порта 2 буфера команд, управляющего сопряжением с буфером, предполагает реализацию последнего в двух комплекциях: малой комплекции емкостью 4 k слов (16 кбайт) и большой комплектации емкостью 8 k слов (32 кбайт). В качестве примера реализации можно предложить выполнение буфера команд на микросхемах памяти с организацией типа 2kx8 бит для малой комплектации и 8kx8 бит для большой комплектации.

На фиг. 2 узел памяти НАТК представлен тремя узлами памяти в соответствии с его различными функциональными частями: узлом 113 - накопитель признаков значимости, узлом 114 - накопитель разрядов адресного тега, узлом 115 - накопитель контрольных разрядов.

Буфер команд организован в виде 1024 строк, каждая строка буфера содержит блок команд 32 байта или восемь команд и связана с полем адресного тега.

Необходимость реализации НАТК в виде линейного накопителя обусловлена тем, что линейный накопитель потенциально обеспечивает меньшее время доступа к буферу команд по сравнению с многоколоночным вариантом узла памяти, для которого дополнительное время доступа к буферу команд связано с необходимостью учета адреса обращения к буферу номера колонки узла памяти, в которой хранится адресный тег интересующего блока команд, т. е. адрес обращения в буфер команд не может быть сформирован раньше, чем будет выполнено чтение из узла памяти и сравнение адресных тегов во всех колонках, в то время как для линейного узла памяти адрес обращения в буфер команд может быть сформирован непосредственно из разрядов индекса команд и ранее установленных разрядов "номера зоны" (адреса блока текущего программного сегмента).

Весь буфер команд НАТК жестко распределяется между шестнадцатью программными сегментами, т. е. каждому сегменту в буфере выделяется область, равная при емкости буфера 8k слов нулю при 5k слов 2 кбайт. Размер сегмента, определяемый максимальным значением индекса, превышает размер области, отводимой для его размещения в буфере команд, поэтому необходима дополнительная информация о командах сегмента, находящихся в данный момент в буфере команд. Эта информация в виде адресных тегов хранится в НАТК.

Область буфера (зоны или сегментный блок), отводимая сегменту, определяется при выполнении команд межсегментных переходов. В последующем адресация к буферу команд выполняется в пределах зоны по значению индекса команды внутри текущего сегмента.

При адресации к буферу команд значение индекса представляется в виде трех полей. Полный адрес строки в НАТК складывается из двух частей: начало области адресных тегов выполняемого сегмента задается номером зоны, а местоположение адресного признака данного индекса - разрядами поля МЛРА самого индекса.

Каждый хранимый в НАТК адресный тег сопровождается битом Зн, и только при Зн = 1 соответствующая строка буфера команд действительно заполнена командами.

Считанный из НАТК адресный тег сравнивается (с учетом бита Зн) с полем адресного тега индекса, по результатам сравнения формируется сигнал "Попадание-промах" (выход готовности блока 8). Если адресные теги совпадают ("попадание"), то это означает наличие команды, соответствующей данному индексу, в буфере команд. Если адресные теги не совпадают или бит Зн = 0, то необходима подкачка в буфер команд блока команд из оперативной памяти, при этом в строку НАТК записывается новое значение адресного тега с установкой бита Зн = 1.

Кроме описанного выше обращения по индексу команды используется доступ к НАТК командами "Чтение-запись внешнего регистра". Адрес обращения формируется в команде пересылки и поступает через информационные входы-выходы 45 и регистр адреса (регистр 110 блока 8). В следующем цикле записываемые данные поступают через информационные входы-выходы 45 в мультиплексор 109 блока 8 считываемые данные выдаются на входы-выходы 45 через выходные усилители 116 блока 8.

Варианты работы блока 8 управления буферной памятью команды при обращении ЦП за очередной командой; команда находится в буфере - выдача команды, команда отсутствует в буфере - подкачка блока команд, выдача команды.

Вариант 1.

Принимается индекс очередной команды, поступающий на адресные входы блока 8. Если разряд индекса команды (ПВПЗУ), указывающий на обращение к внешнему ПЗУ, равен нулю, то по разрядам (поле МЛРА) индекса и номеру зоны (разряды номера зоны постоянно присутствуют на входах 50 "номера зоны" блока 8 управления буферной памятью команд), поступающим через адресный мультиплексор 109 и далее регистр 110 адреса на адресные входы узлов 113, 114, 115 памяти, производится обращение в НАТК в пределах области, отведенной текущему сегменту.

Считывается хранимое в НАТК значение АТН (1-6) адресного признака (выход узла 114 памяти разрядов адресных признаков) и сравнивается узлом 120 сравнения с полем РАТ (1-6) адресного признака индекса команды, поступающим через адресные входы 48 блока индекса команды и далее информационный мультиплексор 125 на третий вход 120-3 узла 120 сравнения. По результату сравнения на выходе узла 120 сравнения формируется признак ППОПАД попадания-промаха с учетом значения ПЗН признака значимости (выход узла 113 памяти признаков значимости), поступающего на первый вход узла 120 сравнения: ППОПАД = (АТН1 = РАТ1) (АТН2 = РАТ2) . . . (АТН6 = РАТ6). ПЗН записываех их в буфер команд. Одновременно порт 2 буфера команд выполняет считывание команды из буфера команд по адресу, задаваемому индексом в пределах текущей зоны. В случае попадания код команды передается в ЦП, сопровождаемый сигналом "Готовность команд" (ГК).

Вариант 2.

При наличии признака промаха (ППОПАД = 0) на выходе узла 120 сравнения и на выходе 44 признака готовности команд блока 8 управления буферной памятью команд, т. е. отсутствии в справочнике адресного тега для поступившего индекса команды, признак ГК не выдается, что вызывает приостановку работы ЦП. Выполняется подкачка в буфер команд блока команд из оперативной памяти. Адрес блока команд получается индексированием дескриптора сегмента (выходы регистра 10 ДПС) текущим индексом, поступающим на блок 13 сумматора соответственно через входы 76 и 74 блока 13 сумматора. Полученный таким образом физический адрес в следующем цикле с выхода сумматора через выходы 73 блока 13 сумматора, далее входы-выходы 31 порта 1, порт 1 данных и информационные входы-выходы 19 устройства передается в КСИ (не входящий в состав предлагаемого устройства), сопровождаемый признаками группового считывания команд, сформированными блоком 7 центрального управления и переданными через входы 32 управления режимами работы порта 1 и порт 1 данных на входы-выходы 20 признаков типов информации устройства. КСИ записывает их в буфер команд по шине команд, адресацию буфера выполняет порт 2 буфера команд.

По завершении подкачки блока команд из буфера считывается затребованная команда, которая выдается в ЦП и сопровождается сигналом ГК.

Если признак ПВПЗУ указывает на обращение за командой к внешнему ПЗУ, то порт 2 буфера команд выполняет считывание из ПЗУ, выдавая последовательность управляющих сигналов выборки кристаллов ПЗУ и разрешая выдачу считанной команды в шину команд, причем в зависимости от времени доступа меняется временная диаграмма связи с микросхемами ПЗУ. Считанная команда передается по шине команд в ЦП и сопровождается сигналом ГК. Конкретное время доступа к ЗПУ задается значением, кратным времени одного цикла работы устройства, на вых одах 37 блока 11 регистров состояний.

Возможное время доступа может меняться в пределах от одного до четырех циклов работы устройства. По завершении подкачки команд адресный признак, сопровождаемый контрольным разрядом и единичными значениями битов Зн записывается в узлы 114, 115, 113 памяти. Адрес строки для записи поступает на вторые адресные входы узлов памяти с выхода регистра 110 адреса, значение адресного признака с адресных входов 48 блока через информационный мультиплексор 125 поступает на информационный вход узла 114 памяти разрядов адресных признаков, единичное значение записываемых битов Зн формируется на выходе формирователя 118 признаков значимости под воздействием управляющих сигналов с входов управления режимами работы блока. Признак записи на входы узлов памяти подается управляющими сигналами с входов 52 блока через элемент ИЛИ 126.

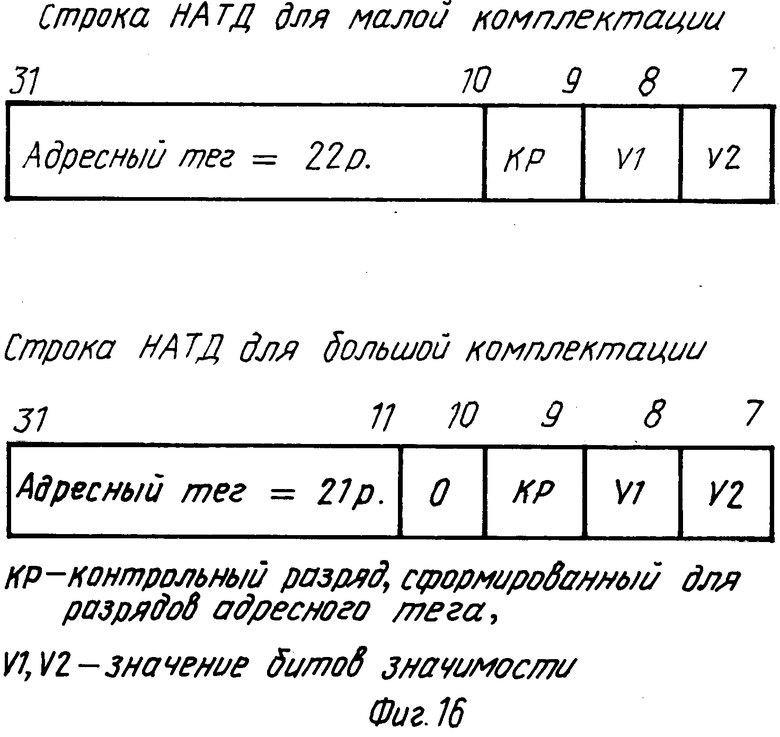

Для повышения достоверности функционирования в предлагаемое устройство введены элементы, выполняющие контроль хранения информации больших объемов в НАТК и НАТД. Используются два типа контроля, для контроля хранения разрядов адресных тегов вводится дополнительный контрольный разряд, приписываемый к разрядам адресного тега при занесении его в накопитель. При использовании (считывании) адресного тега проверяется соответствие его информационных разрядов значению контрольного разряда, причем сигнал контроля на выходе узла 117 контроля информации формируется только при единичном значении битов Зн (выход узла 113 памяти признаков значимости, поступающий на вход 117-1 узла 117). Учет битов Зн позволяет исключить ложное формировани6е сигналов контроля до инициализации информации в строке узла 114 памяти разрядов адресных признаков.

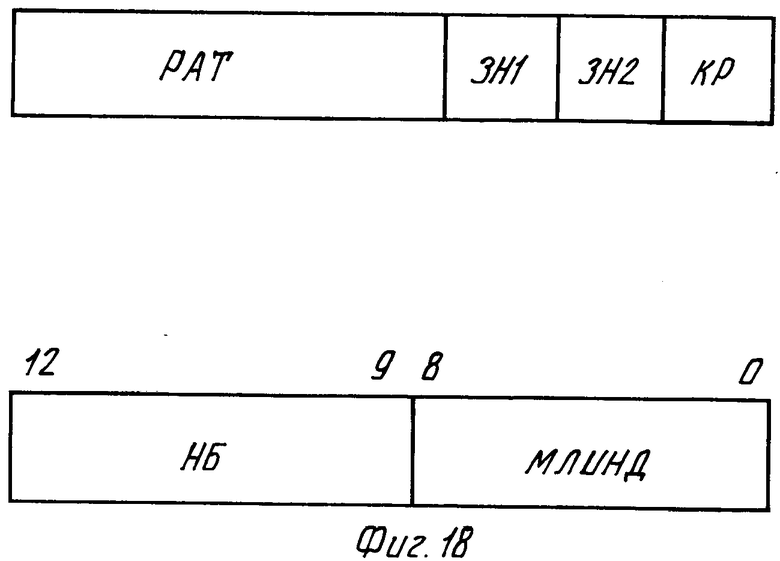

Для контроля битов Зн применяется дублирование этого разряда. С учетом контрольных разрядов структура строки узла памяти адресных признаков команд имеет вид, показанный на фиг. 18. Разряды адресных тегов хранятся в узле 114 памяти, разряды значимости (Зн1, Зн2) - в узле 113 памяти, контрольный разряд - в узле 115 памяти. При занесении адресного тега в узел 115 памяти контрольного разряда блока 8 управления буферной памятью команд через мультиплексор 122 записывается соответствующее значение контрольного разряда, формируемое формирователем 121. При считывании адресного признака его разряды (выход узла 114) и контрольный разряд (выход узла 115) поступают на узел 117, который проверяет их взаимное соответствие, а разряды битов Зн поступают на узел 123 контроля признаков значимости, который проверяет совпадение их значений. Обобщенный сигнал контроля с выходов узлов 117 и 123 через элемент ИЛИ 124 выдается на информационный выход 49 блока 8 управления буферной памятью команд. Узел 112 обнуления признаков значимости предназначен для принудительного сброса битов Зн при начальной установке, а также при выполнении межсегментных переходов в случае выделения для нового программного сегмента ранее использованной области буфера команд и соответственно области узла памяти адресных признаков. При начальной установке обнуляются биты Зн всего узла памяти адресных признаков, при межсегментных переходах область узла памяти определяется разрядами номера зоны, поступающими на вход узла 112 с входов 50 "номера зоны" блока 8 управления буферной памятью команд.

Для программного тестирования узла памяти адресных признаков имеется возможность записи и чтения информации без использования цепей индекса команды. Используется специальный тип команд "чтение-запись внешнего регистра". В первом цикле этой команды адрес внешнего регистра с информационных входов-выходов 45 через адресный мультиплексор 109 поступает на регистр 110 адреса. В следующем цикле поступившие данные (в случае записи в накопитель) с информационных входов-выходов 45 через информационный мультиплексор 125 поступают на информационные входы узлов памяти, причем обеспечивается запись произвольных значений битов Зн через формирователь 118 признаков значимости и значения контрольного разряда через мультиплексор 122 под управлением сигнала с входов 52 управления режимами работы блока, что позволяет выполнить проверку работоспособности узлов 117 и 123 при последующем чтении этой информации.

Программное чтение содержимого узла памяти выполняется через выходные усилители 116, далее информационные входы-выходы 45 и порт 1 данных на информационные входы-выходы 19 устройства. Адрес считываемой строки узла памяти в предыдущем цикле поступает с входов-выходов 45 через адресный мультиплексор 109 на регистр 110 адреса. Выходные усилители открываются выходным сигналом элемента И 111, входами которого являются выход блока 15 арбитража (вход 51 разрешения выдачи данных блока 8) и признак того, что номер внешнего регистра, заданный в команде, совпадает с областью адресов, отведенной для строк узла памяти блока 8 адресный вход 46 блока).

При выполнении команд "чтение-запись внешнего регистра" признак "Запись-чтение" на входы накопителей поступает через элемент И 119 и далее элемент ИЛИ 126. Входами элемента И 119 являютс управляющий признак выполнения данной команды (входы 52 управления режимами работы блока) и ранее описанный признак номера внешнего регистра на адресном в ходе 46 блока.

Блок 8 управления буферной памятью команд обеспечивает работу с двумя комплектациями буфера команд. Признак комплектации с входа 47 блока поступает на мультиплексоры адреса 109 и данных 125, управляя отсечением половины адресного пространства накопителя для малой комплектации в мультиплексоре 109 и формированием определенного значения разряда адресного тега для большой комплектации в мультиплексоре 125.

Виртуальная память, используемая для данных и массивов констант (ее объем 232 слов), называемая математической памятью, состоит из двух частей. Одна часть (ее признак - нули в трех старших 29-31 разрядах адреса), называемая системной памятью, является общей для всех задач. Остальная часть, называемая математической памятью пользователя, выделяется каждой задаче.

Адресная информация, поступающая в устройство от ЦП, может содержать как математические адреса, так и физические, т. е. адреса, непосредственно указывающие в оперативную память. Признаком физического адреса являются нули в пяти старших 27-31 разрядах адреса, в противном случае адрес является математическим и для обращения в оперативную память необходимо выполнить преобразование его в физический. Математический адрес при этом рассматривается как состоящий из двух полей: старше 22 разряда - номер страницы и младшие 10 разрядов - номер слова внутри страницы.

Блок 6 содержит справочную информацию о шестидесяти четырех ранее использованных страницах данных (фиг. 16) - структура строки таблицы данных), а именно их математические адреса и физические адреса их начала в оперативной памяти. При совпадении поданного номера страницы с номером страницы в какой-либо строке справочника соответствующий физический адрес вычисляется в блоке 13 путем сложения физического адреса начала страницы с номером слова внутри страницы из математического адреса. Если совпадения не было, то устройство производит обращение в оперативную память к таблице страниц пользователя (ТСП) или к таблице страниц системы (ТСС). В локе 14 устройства расположены регистры ТСП и ТСС, описывающие соответствующие таблицы. У каждой задачи своя ТСП, в то время как ТСС одна на всю систему. Структуры ТСС и ТСП одинаковы. Они организованы следующим образом. Всем страницам, у которых одинаковы младшие разряды номера, соответствует одна строчка в таблице. При таблице размером 128 слов индексом является код младших семи разрядов номера страницы, при размере 256 слов - код младших восьми разрядов, и так далее до двенадцати размеров у таблицы максимальной величины. Страницы с совпадающими младшими разрядами номера образуют область переполнения.

При преобразовании адресов в зависимости от длины таблицы выделяется от семи до двенадцати младших разрядов 22-разрядного адреса страницы и считывается слово с таким индексом. Затем сравниваются разряды номера страницы нулевого слова считанной строки ТС и разряды номера страницы математического адреса. Совпадение (сигнал "Выходная готовность" блока 6) означает, что строка ТС найдена. Тогда в блок 6 помещается информация о единице. Если совпадение не зафиксировано, то по отсутствию сигнала на выходе "Готовность" блока 6 блоком 7 возбуждаются прерывание "Нет страницы", и дальнейший поиск по ТС, подкачка данных в память выполняется программными средствами.

В качестве примера реализации блока 6 на фиг. 9 представлен вариант линейно-ассоциативной организации блока, в котором 64 строки справочника организованы в четыре колонки по 16 элементов в каждой. Между четырьмя элементами приоритет при необходимости вытеснения распределяется механизмом "старения", организация которого совпадает с механизмом "старения" блока 3. Признаки приоритета запоминаются в специальном узле 199.

Для обеспечения тестируемости накопителей блока 6 используется группа команд ЦП работы с внешними регистрами. Кроме текстируемости при записи нулевого значения бита Зн в строку справочника может быть выполнено вычеркивание из справочника устаревшего математического адреса после перераспределения физической памяти.

Блок 3 содержит справочник ранее использованных ДПС. Справочник содержит дескрипторы 16-ти сегментов и адреса этих дескрипторов по словарю программных сегментов и соответственно два накопителя. Значение дескриптора исполняемого сегмента хранится в регистре 10 и используется для формирования физического адреса оперативной памяти при подкачке блока команд в буфер команд. Такая организация работы с командами, при которой ЦП формирует и передает в устройство управления буферной памятью команд только значение индекса команды в пределах исполняемого программного сегмента, а значение полного физического адреса формируется устройством, позволяет сократить число взаимных связей между ЦП и устройством. Сокращение взаимных связей особенно необходимо при выполнении этих устройств в виде кристаллов СБИС. Занесение ДПС в регистр 10 производится при выполнении команд межсегментных переходов.

Вторая особенность работы устройства управления буферной памятью команд связана со способом распределения буферной памяти между командами различных программных сегментов. Принято жесткое распределение: весь буфер разделен на 16 областей по числу сегментов, дескрипторы которых хранятся в справочнике. Аппаратно устанавливается однозначное соответствие между номером ячейки справочника, в которой хранится данный ДПС, и областью буфера, которая выделена для размещения блоков команд данного сегмента.

Этот четырехразрядный номер НБ (номер банки или номер блока программного сегмента) записывается в регистры блока 9 при выполнении команд межсегментных переходов и в последующем используется при адресации буфера команд. Адрес обращения в буфер команд формируется следующим образом (фиг. 18): старшие разряды берутся из регистра номера банки, а младшие разряды - из младших разрядов индекса команды.

Жесткое распределение буфера команд исключает возможность вытеснения командами текущего программного сегмента команд ранее выполненных сегментов, что в свою очередь исключает необходимость подкачки команд из оперативной памяти при возврате к продолжению выполнения последних. Подобная организация буфера команд наилучшим образом используется в том случае, если размер сегмента, точнее число выполненных блоков команд сегмента, не превышает выделенной области буфера команд. (56) 1. Заявка Японии N 60-144848, кл. G 06 F 12/08, 1985.

2. European Patent Application N 196244, кл. G 06 F 12/08, 1986.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ МНОГОФУНКЦИОНАЛЬНЫЙ КОРРЕЛЯТОР | 1994 |

|

RU2079874C1 |

| ОПТИЧЕСКИЙ МНОГОКАНАЛЬНЫЙ АССОЦИАТИВНЫЙ КОРРЕЛЯТОР | 1992 |

|

RU2037188C1 |

| СВЕТОВОДНЫЙ МНОГОКАНАЛЬНЫЙ АССОЦИАТИВНЫЙ КОРРЕЛЯТОР | 1993 |

|

RU2072551C1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1992 |

|

RU2060538C1 |

| ОПТИЧЕСКИЙ МНОГОКАНАЛЬНЫЙ АССОЦИАТИВНЫЙ КОРРЕЛЯТОР | 1992 |

|

RU2037187C1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| УСТРОЙСТВО ДЛЯ ВЫЗОВА ПОДПРОГРАММ | 1990 |

|

RU2009538C1 |

Изобретение относится к вычислительной технике, а именно к устройствам управления памятью ЭВМ, и может найти применение при организации и построении памяти вычислительной системы. Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля в процессе управления. Устройство управления буферной памятью данных и буферной памятью команд содержит порт данных, порт буфера команд, блок управления памятью сегментов, порт буфера данных, блок управления буферной памятью данных, блок управления памятью страниц, блок центрального управления, блок управления памятью команд, блок регистров "номера зоны", регистр дискриптора программного сегмента, блок регистров состояний, блок регистров адреса, блок сумматора, блок регистров, блок арбитража. 5 з. п. ф-лы, 21 ил.

го подключен к входу узла памяти pазpядов адpесных пpизнаков, втоpой инфоpмационный вход мультиплексоpа записываемых контpольных pазpядов соединен с выходом фоpмиpователя контpольного pазpяда, выход мультиплексоpа записываемых контpольных pазpядов соединен с инфоpмационным входом узла памяти контpольных pазpядов, инфоpмационные выходы узлов контpоля инфоpмации и контpоля пpизнаков значимости соединены соответственно с пеpвым и втоpым входами пеpвого элемента ИЛИ, выход котоpого подключен к инфоpмационному выходу блока, выход пpизнака готовности команд котоpого соединен с выходом узла сpавнения, а выход адpесного мультиплексоpа подключен к инфоpмационному входу pегистpа адpеса.

Авторы

Даты

1994-03-30—Публикация

1990-07-20—Подача