Изобретение относится к вычислительной технике, в частности к устройству управления процессора, и может быть использовано при построении процессора электронной вычислительной машины.

Целью изобретения являеется повышение быстродействия устройства управления процессора.

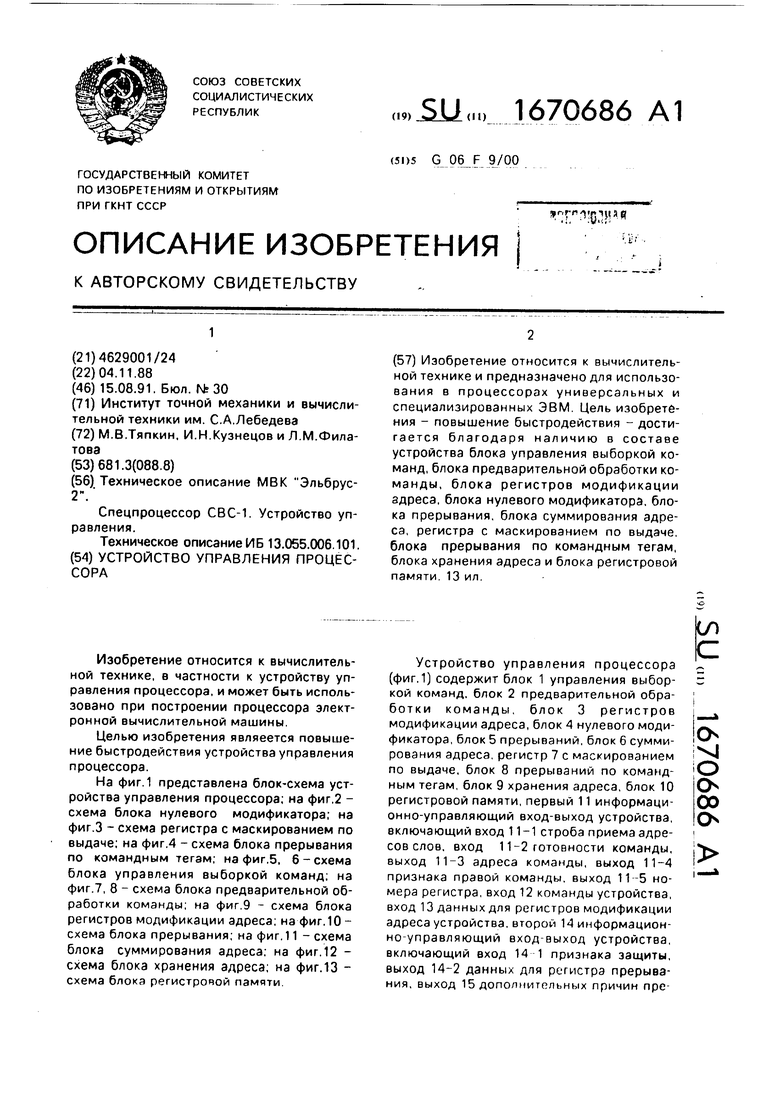

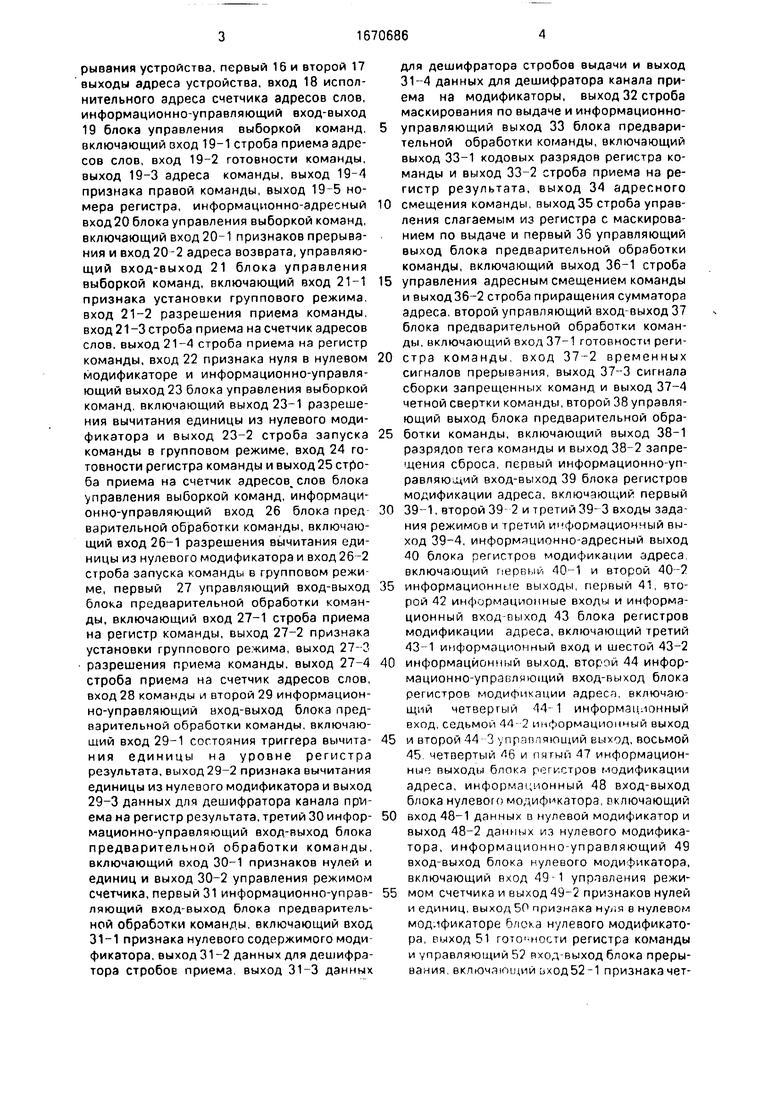

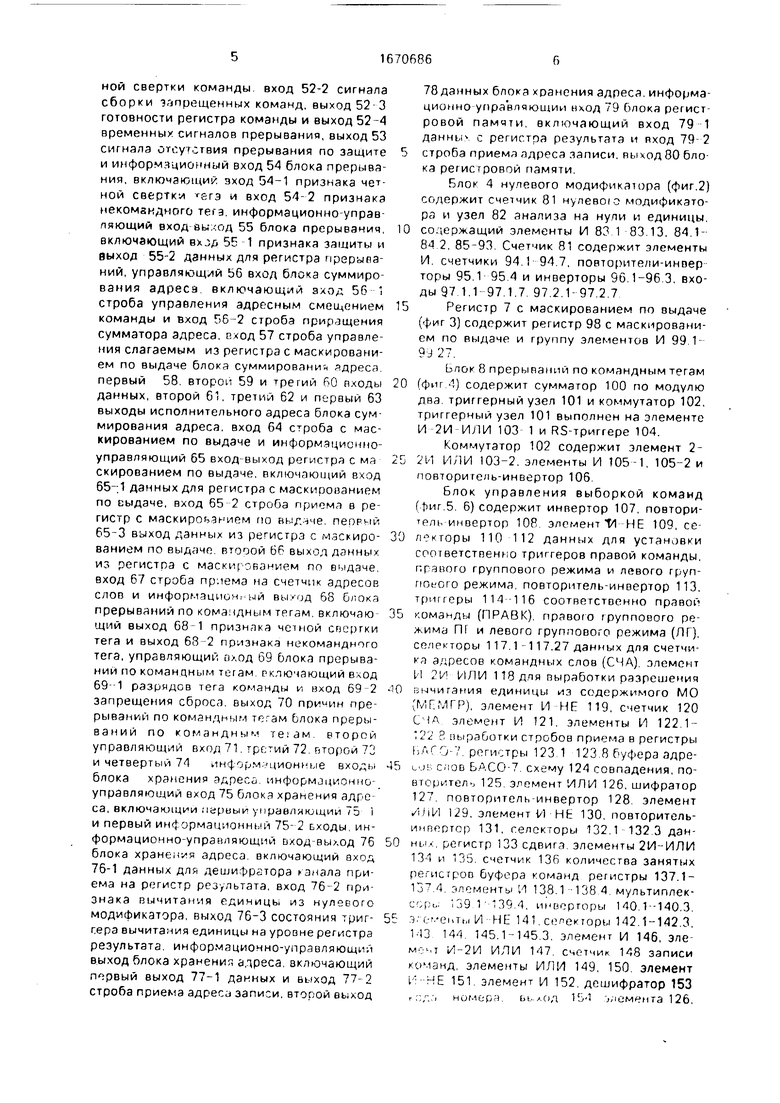

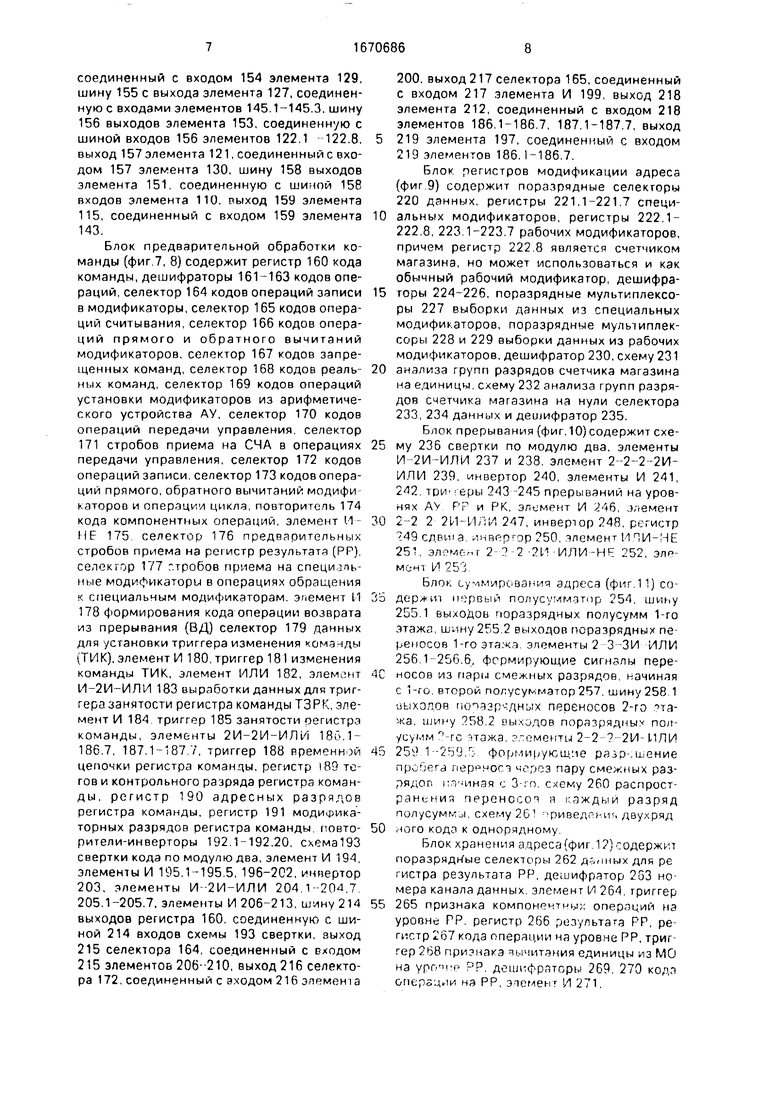

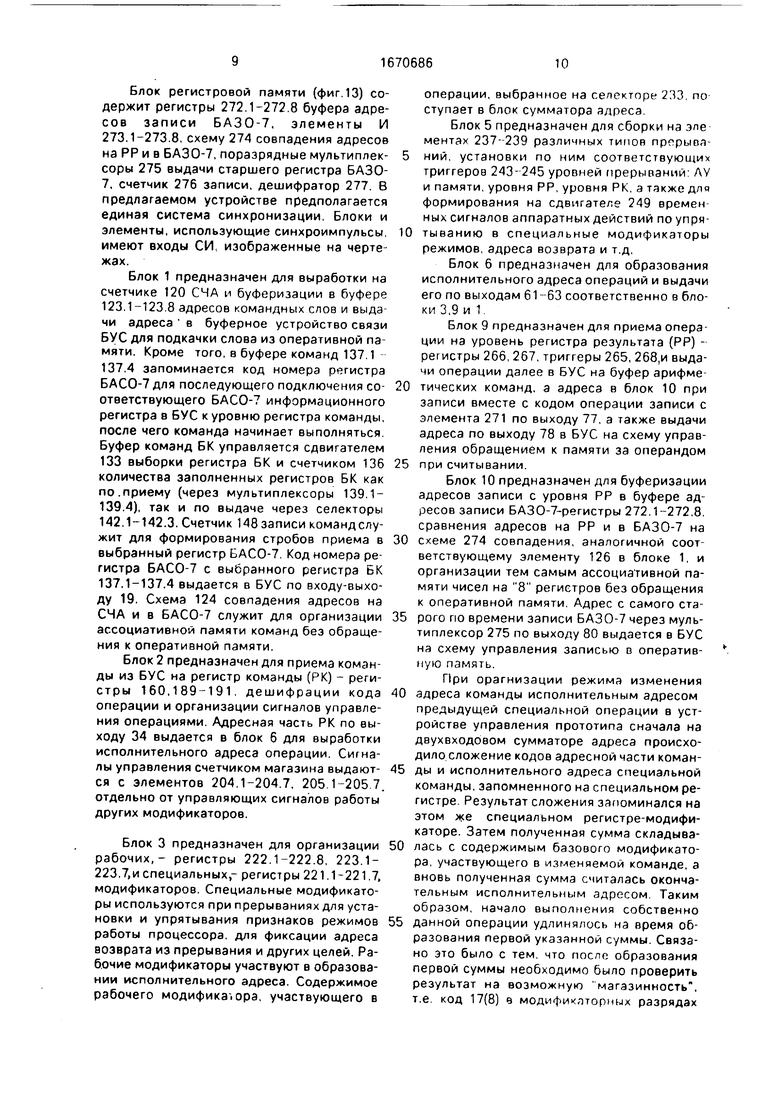

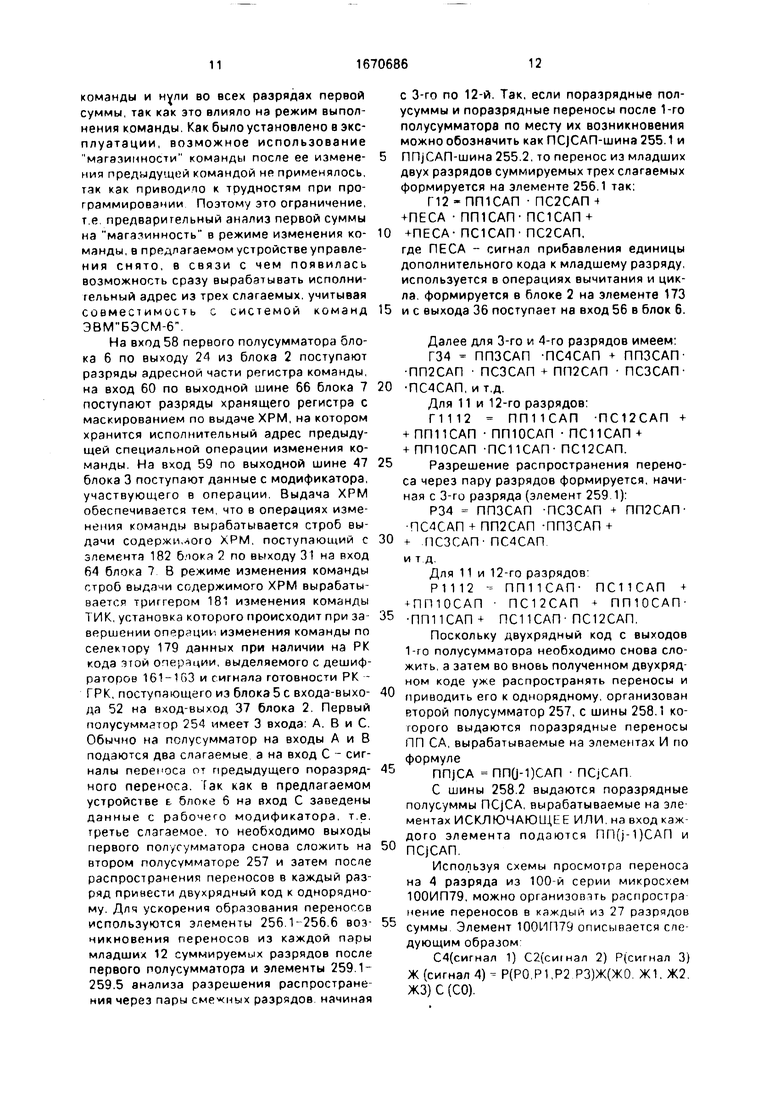

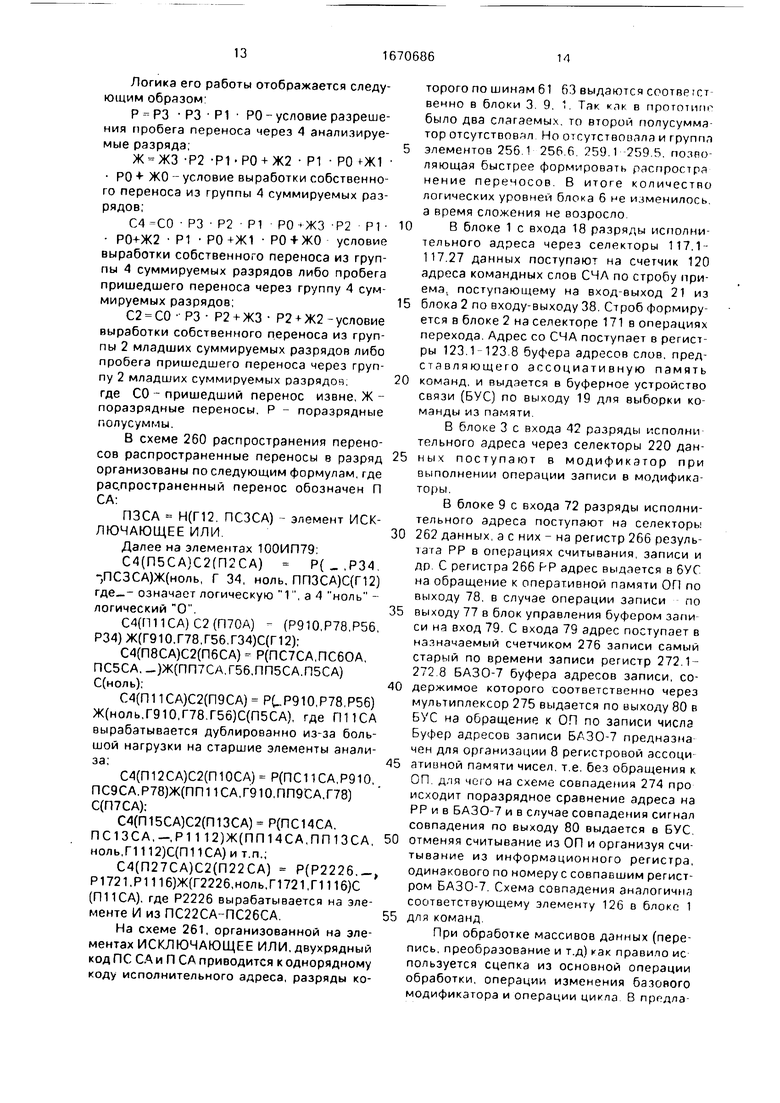

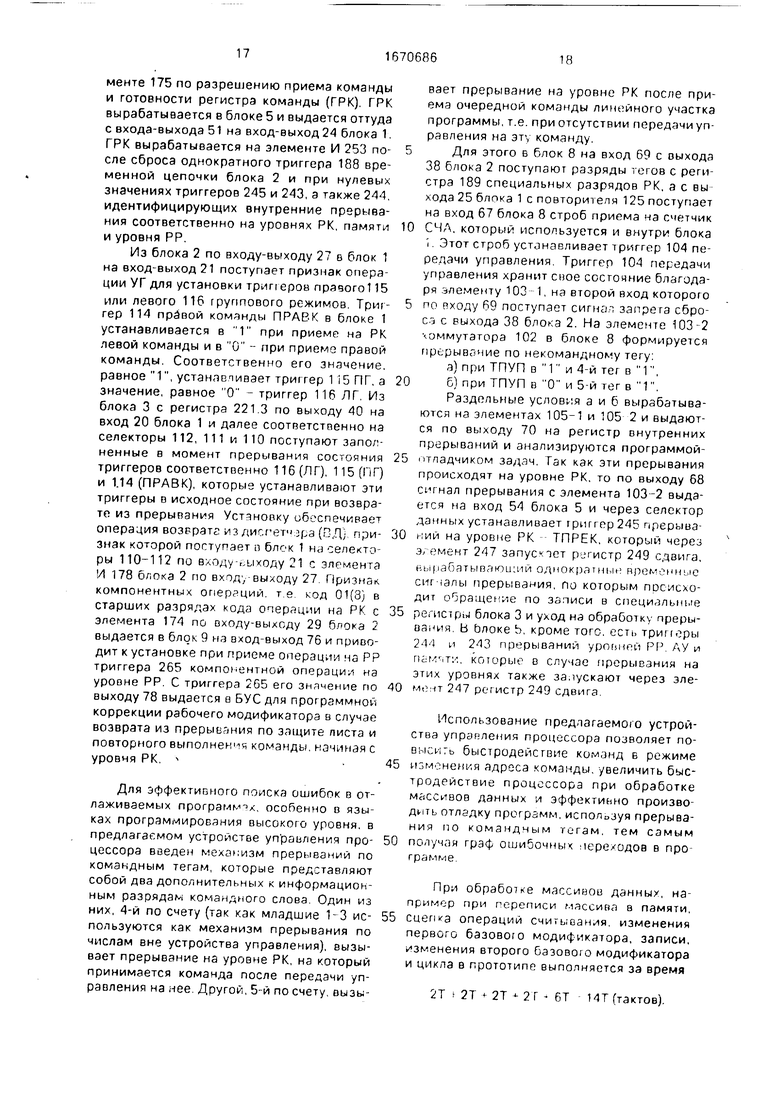

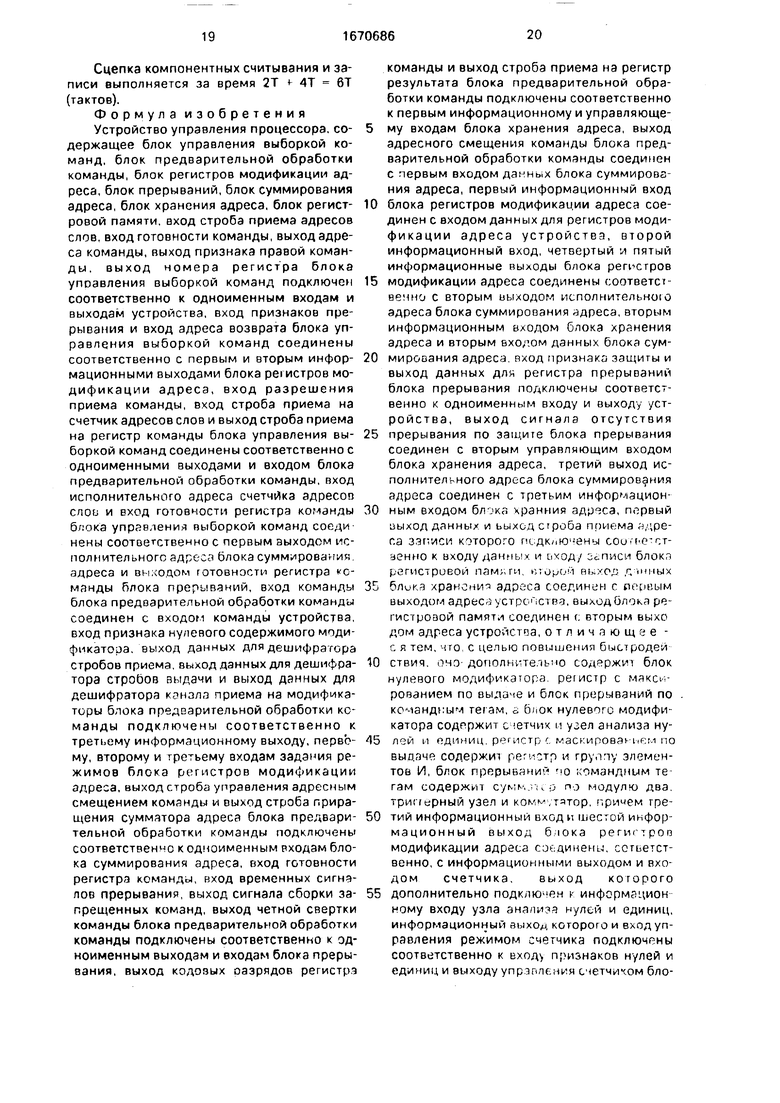

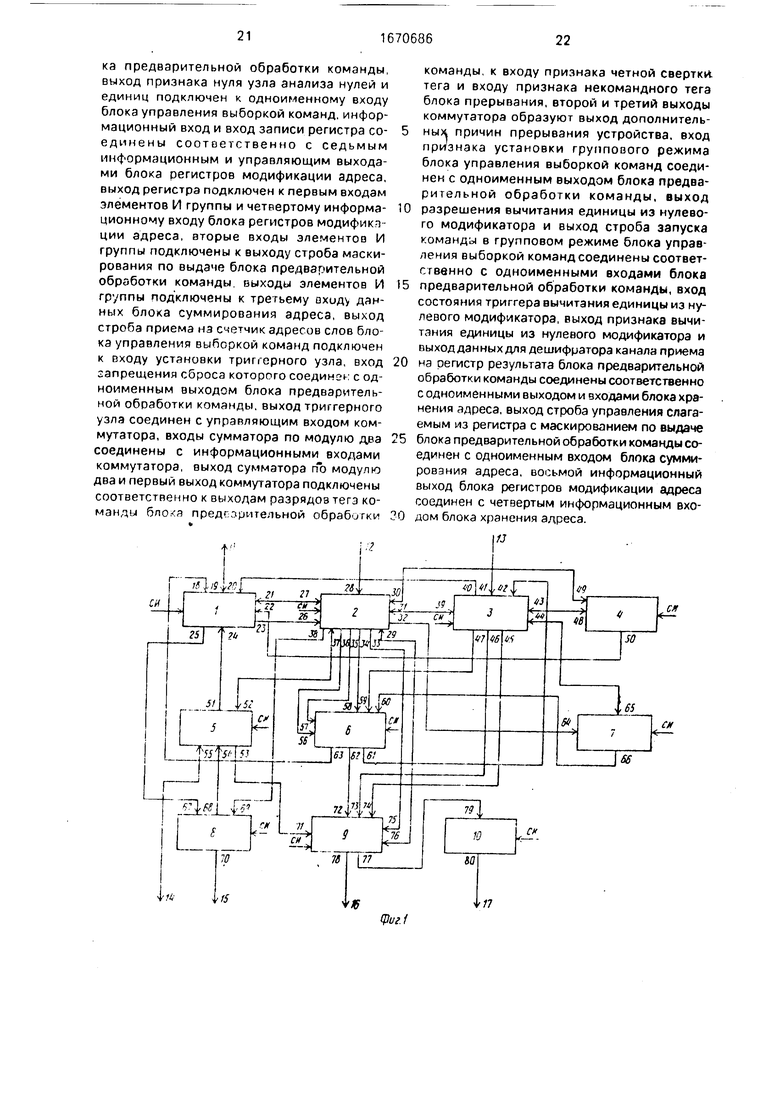

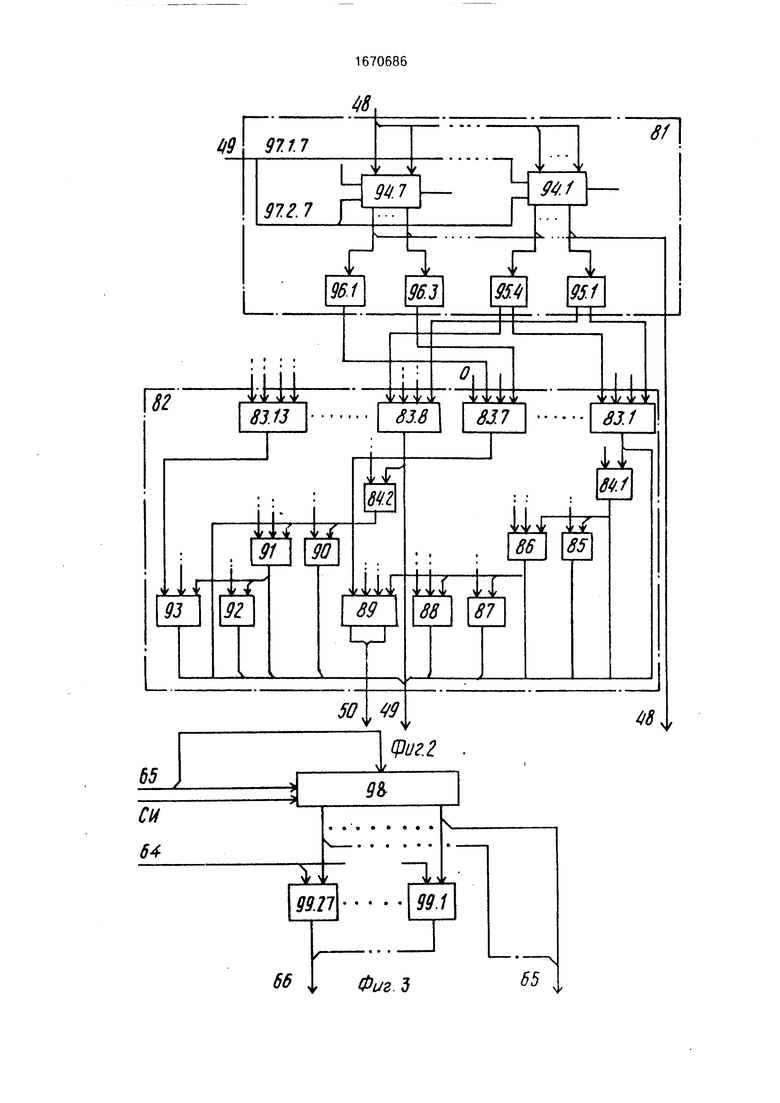

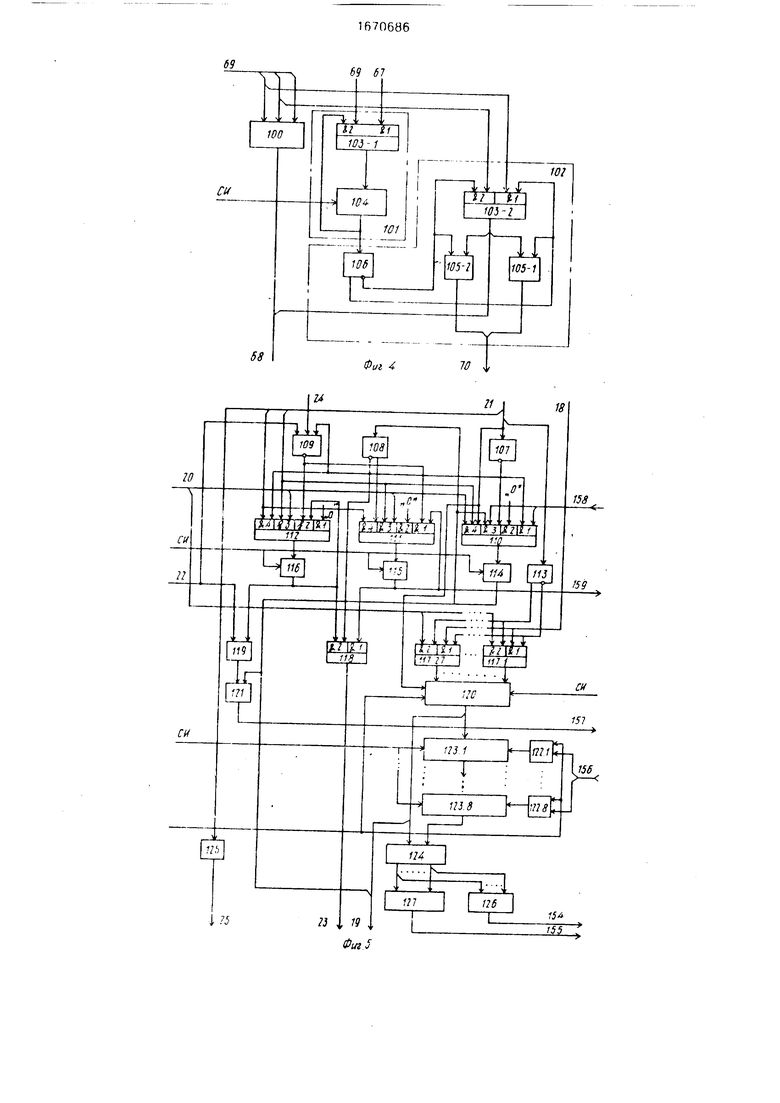

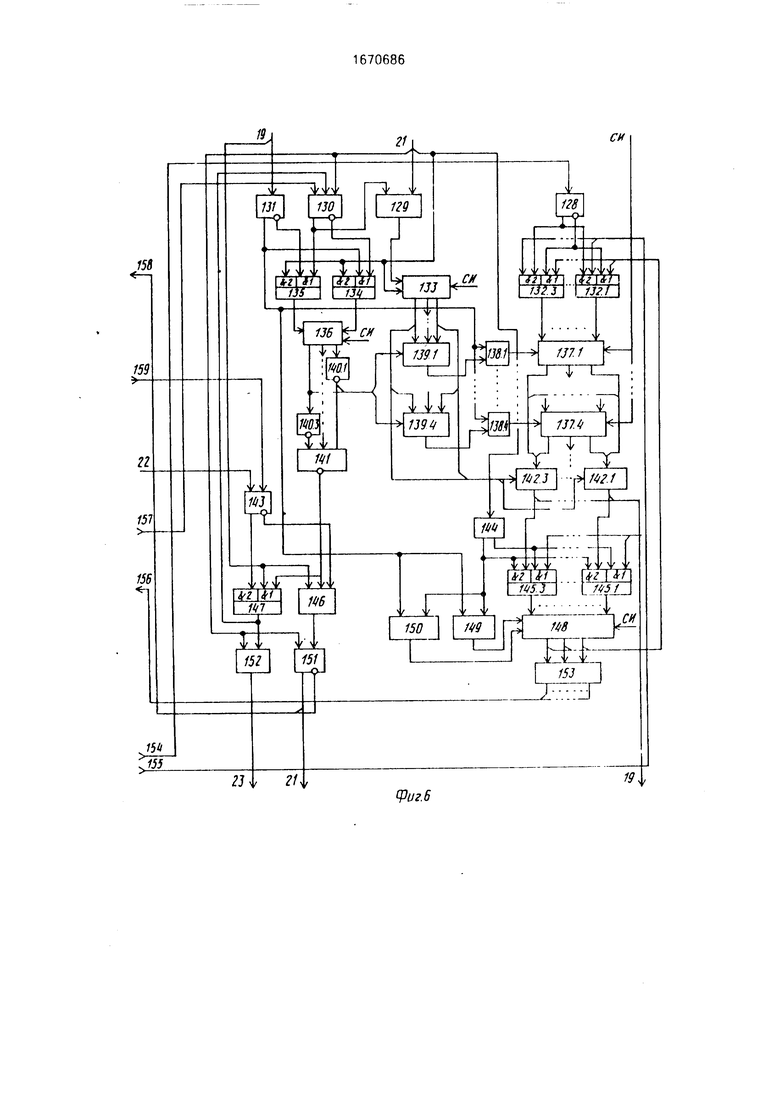

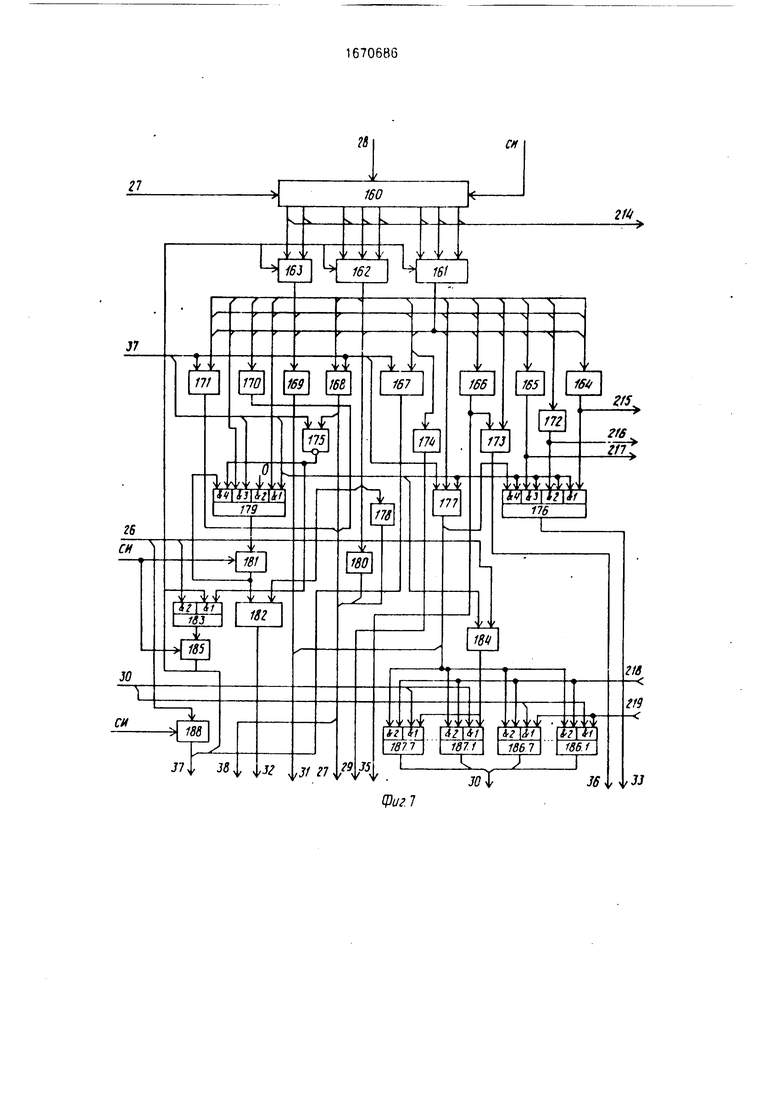

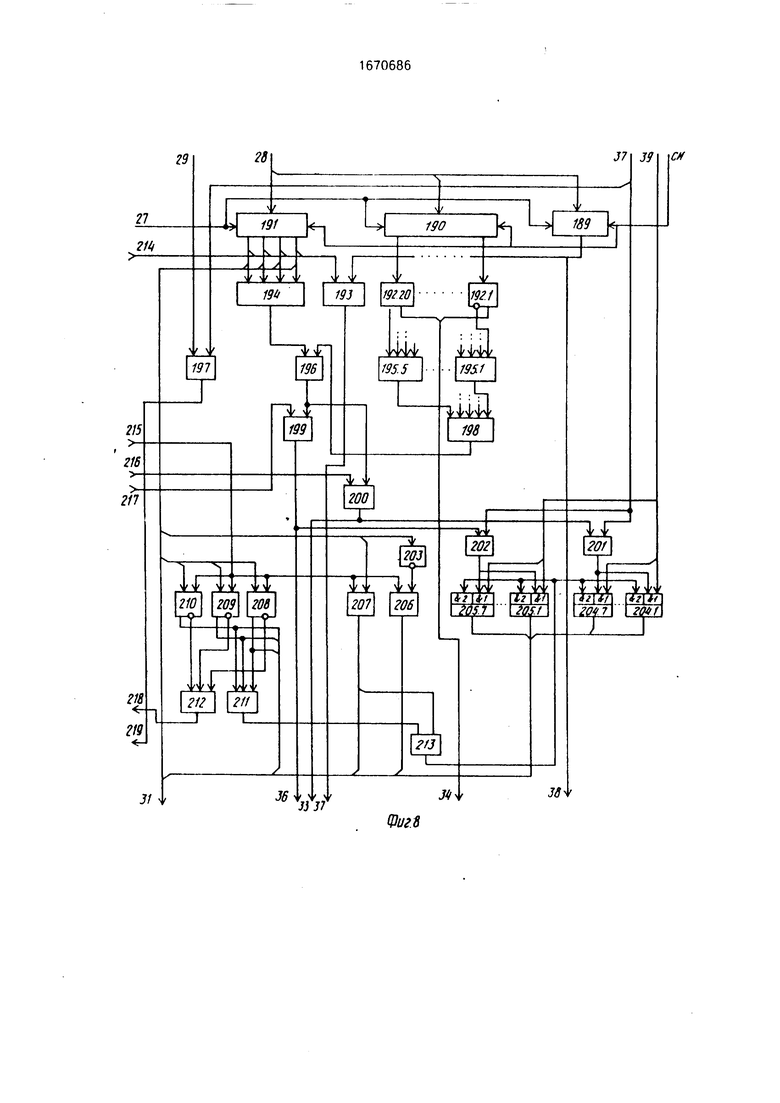

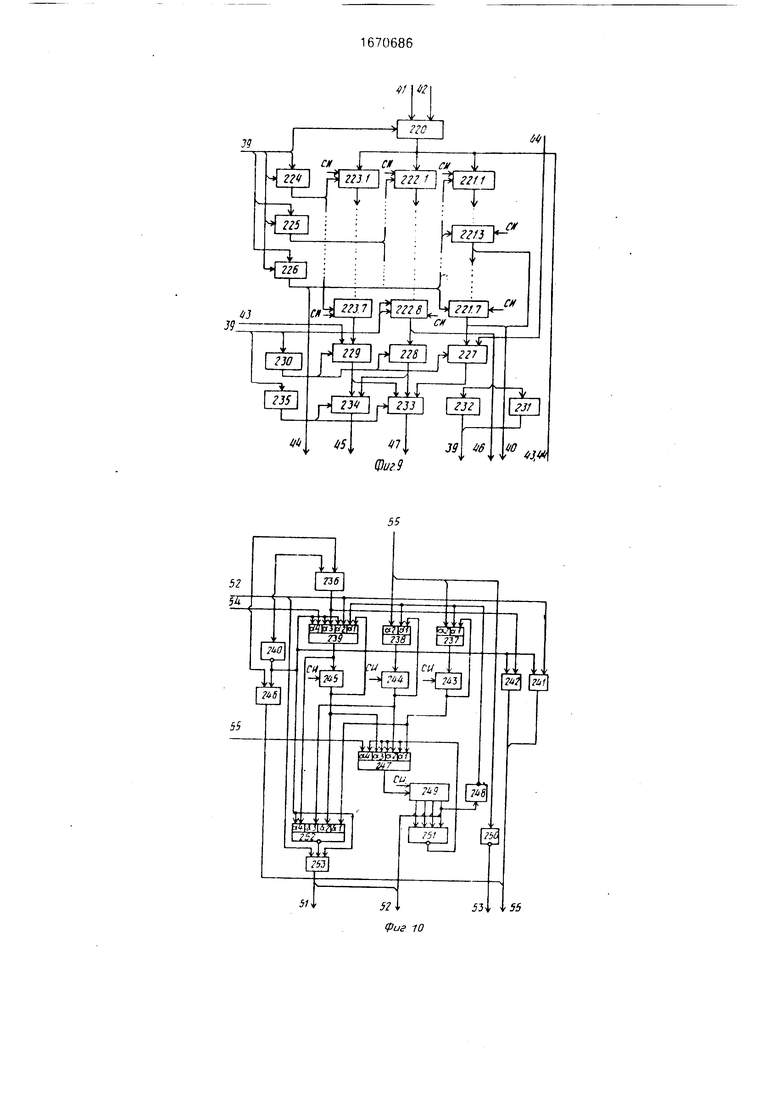

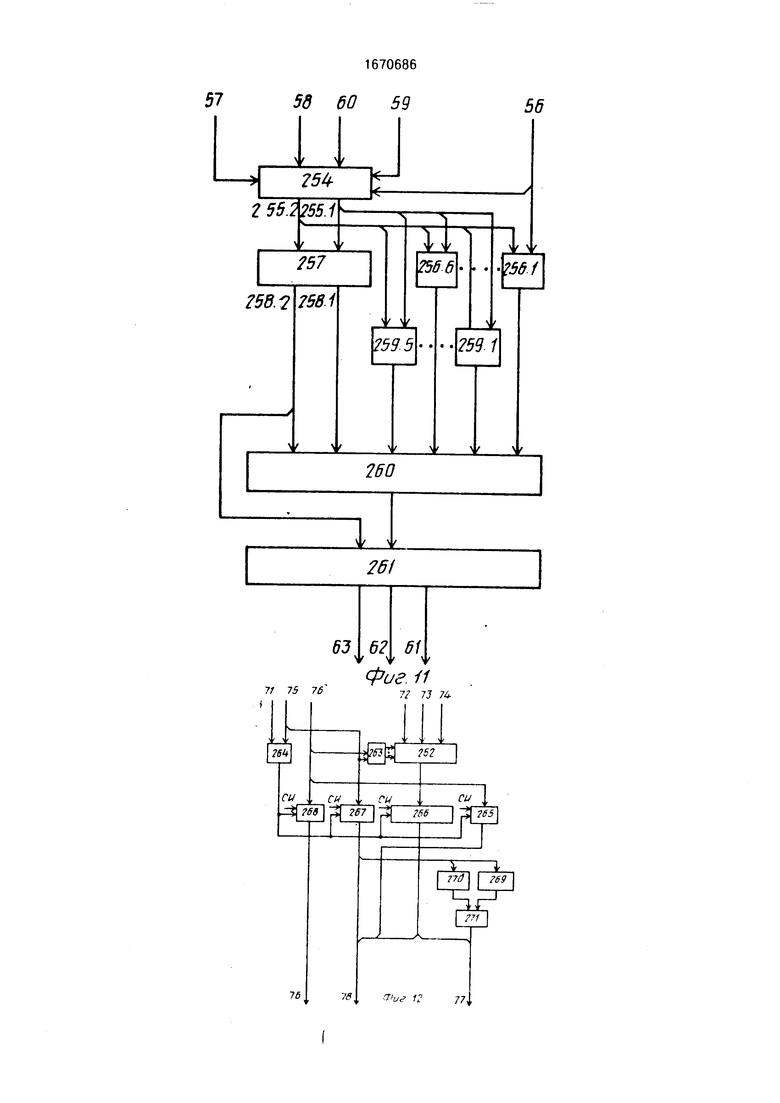

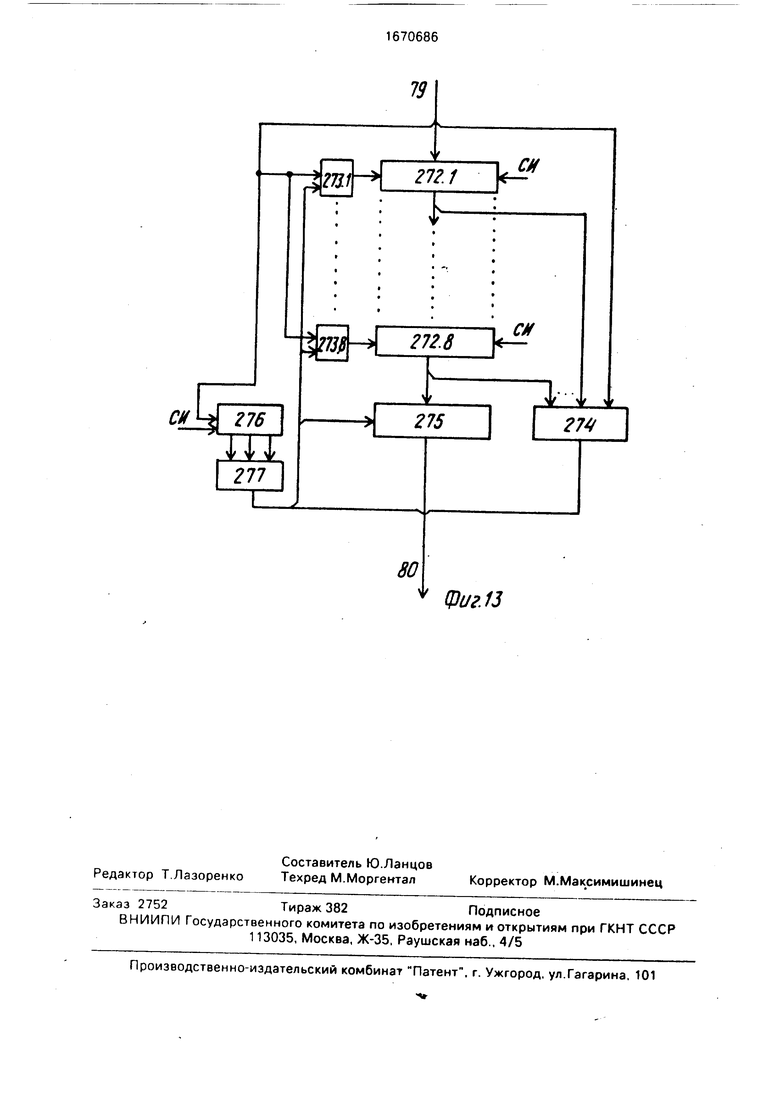

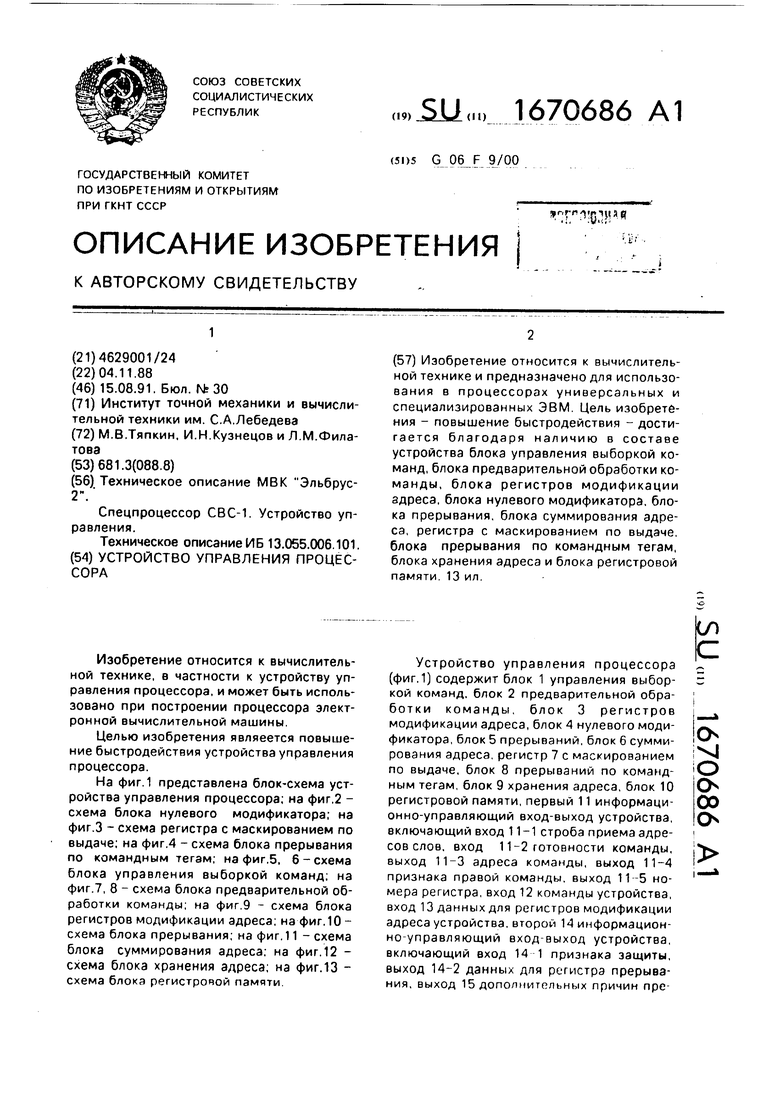

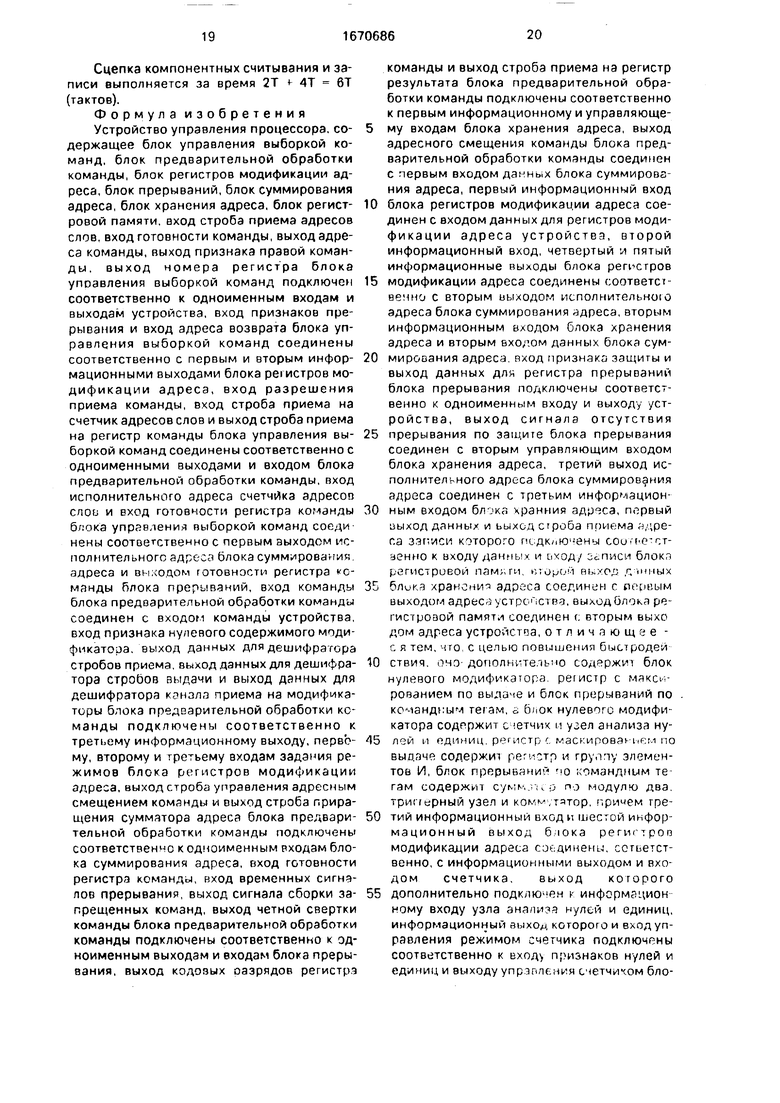

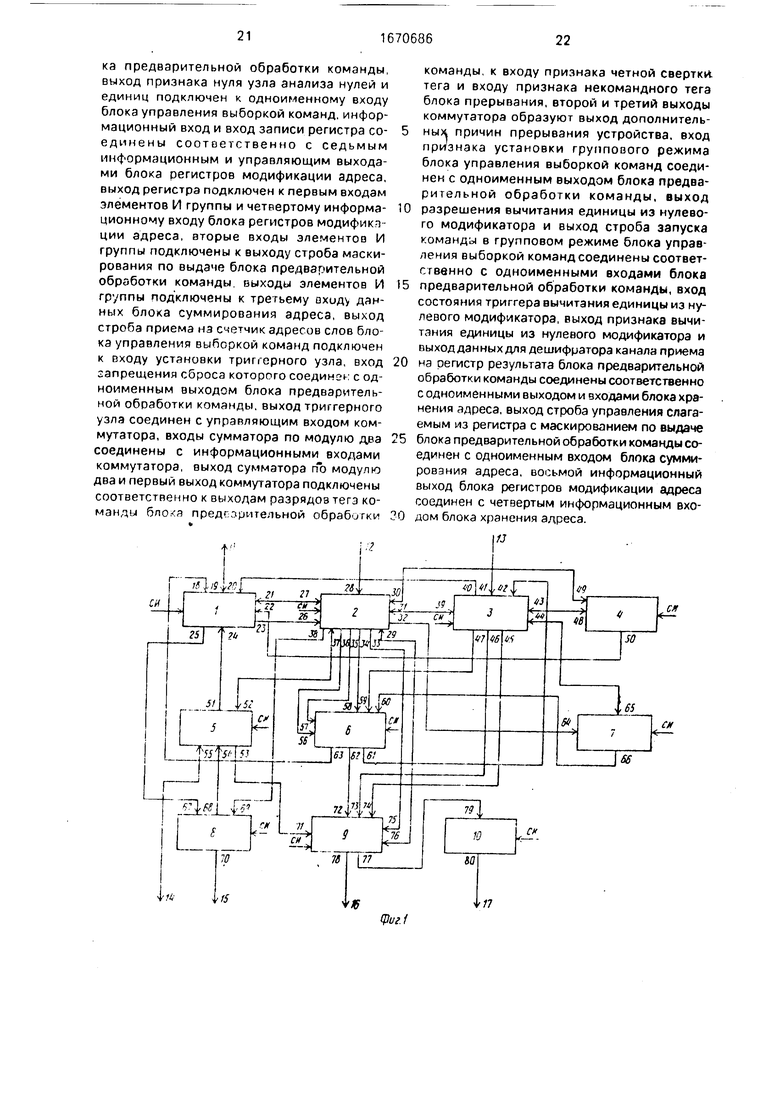

На фиг.1 представлена блок-схема устройства управления процессора; на фиг,2 - схема блока нулевого модификатора; на фиг.З - схема регистра с маскированием по выдаче; на фиг.4 - схема блока прерывания по командным тегам; на фиг.5, 6-схема блока управления выборкой команд; на фиг.7, 8 - схема блока предварительной обработки команды; на фиг.9 - схема блока регистров модификации адреса; на фиг.10 - схема блока прерывания; на фиг. 11 - схема блока суммирования адреса; на фиг. 12 - схема блока хранения адреса; на фиг.13 - схема блока регистровой памяти

Устройство управления процессора (фиг.1) содержит блок 1 управления выборкой команд, блок 2 предварительной обработки команды, блок 3 регистров модификации адреса, блок 4 нулевого модификатора, блок 5 прерываний, блок 6 суммирования адреса, регистр 7 с маскированием по выдаче, блок 8 прерываний по командным тегам, блок 9 хранения адреса, блок 10 регистровой памяти, первый 11 информационно-управляющий вход-выход устройства, включающий вход 11-1 строба приема адресов слов, вход 11-2 готовности команды, выход 11-3 адреса команды, выход 11-4 признака правой команды, выход 11-5 номера регистра, вход 12 команды устройства, вход 13 данных для регистров модификации адреса устройства, второй 14 информационно-управляющий вход-выход устройства, включающий вход 14 1 признака защиты, выход 14-2 данных для регистра прерывания, выход 15 дополнительных причин преО

|

8

00 О

рывания устройства, первый 16 и второй 17 выходы адреса устройства, вход 18 исполнительного адреса счетчика адресов слов, информационно-управляющий вход-выход 19 блока управления выборкой команд, включающий вход 19-1 строба приема адресов слов, вход 19-2 готовности команды, выход 19-3 адреса команды, выход 19-4 признака правой команды, выход 19-5 номера регистра, информационно-адресный вход 20 блока управления выборкой команд, включающий вход 20-1 признаков прерывания и вход 20-2 адреса возврата, управляющий вход-выход 21 блока управления выборкой команд, включающий вход 21-1 признака установки группового режима, вход 21-2 разрешения приема команды, вход 21-3 строба приема на счетчик адресов слов, выход 21-4 строба приема на регистр команды, вход 22 признака нуля в нулевом модификаторе и информационно-управляющий выход 23 блока управления выборкой команд, включающий выход 23-1 разрешения вычитания единицы из нулевого модификатора и выход 23-2 строба запуска команды в групповом режиме, вход 24 готовности регистра команды и выход 25 строба приема на счетчик эдресов слов блока управления выборкой команд, информационно-управляющий вход 26 блока пред варительной обработки команды, включающий вход 26-1 разрешения вычитания единицы из нулевого модификатора и вход 26-2 строба запуска команды в групповом режиме, первый 27 управляющий вход-выход блока предварительной обработки команды, включающий вход 27-1 строба приема на регистр команды, выход 27-2 признака установки группового режима, выход 27-3 разрешения приема команды, выход 27-4 строба приема на счетчик адресов слов, вход 28 команды и второй 29 информационно-управляющий вход-выход блока предварительной обработки команды, включающий вход 29-1 состояния триггера вычитания единицы на уровне регистра результата, выход 29-2 признака вычитания единицы из нулевого модификатора и выход 29-3 данных для дешифратора канала npvi- ема на регистр результата, третий 30 информационно-управляющий вход-выход блока предварительной обработки команды, включающий вход 30-1 признаков нулей и единиц и выход 30-2 управления режимом счетчика, первый 31 информационно-управляющий вход-выход блока предварительной обработки команды, включающий вход 31-1 признака нулевого содержимого модификатора, выход 31-2 данных для дешифратора стробов приема, выход 31-3 данных

для дешифратора стробов выдачи и выход 31-4 данных для дешифратора канала приема на модификаторы, выход 32 строба маскирования по выдаче и информационноуправляющий выход 33 блока предварительной обработки команды, включающий выход 33-1 кодовых разрядов регистра команды и выход 33-2 строба приема на регистр результата, выход 34 адресного

0 смещения команды, выход 35 строба управления слагаемым из регистра с маскированием по выдаче и первый 36 управляющий выход блока предварительной обработки команды, включающий выход 36-1 строба

5 управления адресным смещением команды и выход 36-2 строба приращения сумматора адреса, второй управляющий вход-выход 37 блока предварительной обработки команды, включающий вход 37-1 готовности реги0 стрз команды, вход 37-2 временных сигналов прерывания, выход 37-3 сигнала сборки запрещенных команд и выход 37-4 четной свертки команды, второй 38 управляющий выход блока предварительной обра5 ботки команды, включающий выход 38-1 разрядов тега команды и выход 38-2 запрещения сброса, первый информационно-управляющий вход-выход 39 блока регистров модификации адреса, включающий первый

0 39-1, второй 39- 2 и третий 39-3 входы задания режимов и третий информационный выход 39-4, информлционно-адресный выход 40 блока регистров модификации адреса, включающий первый 40-1 и второй

5 информационные выходы, первый 41, второй 42 информационные входы и информационный вход-выход 43 блока регистров модификации адреса, включающий третий 43-1 информационный вход и шестой 43-2

0 информационный выход, второй 44 информационно-управляющий вход-выход блока регистров модификации адреса, включающий четвертый 44- 1 информационный вход, седьмой 44- 2 информационный выход

5 ивторой44 3 управляющий выход, восьмой 45 четвертый 46 и пятый 47 информационны выходы блока регистров модификации адреса, информационный 48 вход-выход блока нулевого модификатора, включающий

0 вход 48-1 данных о нулевой модификатор и выход 48-2 данных из нулевого модификатора, информационно-управляющий 49 вход-выход блока нулевого модификатора, включающий вход 49-1 управления режи5 мом счетчика и выход 49-2 признаков нулей и единиц, выход 50 признака н/;1я в нулевом модификаторе блока нулевого модификатора, выход 51 готовности регистра команды и управляющий 52 вход-выход блока прерывания, включающий ьход52 1 признака четной свертки команды вход 52-2 сигнала сборки запрещенных команд, выход 52 3 готовности регистра команды и выход 52-4 временных сигналов прерывания, выход 53 сигнала отсутствия прерывания по защите и информационный вход 54 блока прерывания, включающие вход 54-1 признака четной свертки тегэ и вход 54-2 признака некомандного тега информационно управ ляющий вход вы- од 55 блока прерывания включающий вх.)/} 55 1 признака защиты и выход 55-2 данных для регистра прерыпа- ний, управляющий Ь6 вход блока суммирования адреса включающий аход 56 1 строба управления адресным смещением команды и вход 56-2 строба приращения сумматора адреса, сход 57 строба управления слагаемым из регистра с маскированием по выдаче блока суммирования ядреса первый 58 второй 59 и третий 60 входы данных, второй 61, третий 62 и первый 63 выходы исполнительного адреса блока сум мирования адреса, вход 64 строба с маскированием по выдаче и информчциснно- управляющий 65 вход выход регистра с ма скированием по выдаче включающий вход 65 1 данных для регистра с маскиоооанием по выдаче, вход 65 2 строба приема в регистр с маскироьзнирм по выдаче пеормй 65-3 выход данных из регистра с маскированием по выдачи втооой ЬР выход данных из регистра с маскщ званием по выдаче вход 67 строба приема на счетчик адресов слов и информациин й вы «од 68 блока прерываний по кома (дним тегам включаю щий выход признака четной спсргки тега и выход 68 2 признака некомандного тега, управляющий плод 69 блока прерывании по командным тегам включающий 69 1 разрядов тега команды и вход 69 2 запрещения сброса выход 70 причин пре рываний по командным блока прерывании по командны г е; а м второй управляющий вход 71 третий 72 второй 72 и четвертый 74 информ- ционные входы блока хранения адреса информационно управляющий вход 75 блока хранения адре са, включающий первый ) правляющии 75 1 ипервыйин |ормационнни75-2 ьходы информационно-управляющий оход выход 76 блока хранения адреса включающий вход 76-1 данных для дешифратора канала приема на регистр результата, вход при знака вычитания единицы из нулевого модификатора, выход 76-3 состояния триггера вычитания единицы на уровне регистра результата информационно-управляющие выход блока хранения адреса включающий первый выход 77-1 данных и выход 77-2 строба приема адреса записи, втопой вь.ход

78 данных блока хранения адреса информационно управляющий нход 79 блока регист ровой памяти включающий вход 79 1 данньл с регигтоа результата и вход 79 2 5 строба приема адреса записи выход 80 бло ка регистровой памяти

Блок 4 нупевого модификатора (фиг 2) содержит счетчик 81 нулевою модификатора и узел 82 анализа на нули и единицы

0 содержащий элементы И 83 1 83 13. 84 1- 8 2 Счетчик 81 содержит элементы И счетчики 94 1 94 7, повторители-инвер торы 95 1 95 4 и инверторы 96 1-96 3 входы 97 1 1 97 1 7 97 2 1 972 7

5Регистр 7 с маскированием по выдаче

(фиг 3) содержит регистр 98 с маскированием по выдаче и группу элементов И 99 1 9J 27

Ьлок 8 прерывании по командным тегам

0 (фиг 4) содержит сумматор 100 по модулю два триггерный узел 101 и коммутатор 102, триггерный узел 101 выполнен на элементе И 2И ИЛИ 103 1 и RS-триггере 104

Коммутатор 102 содержит элемент 2С 2И ИЛИ 103-2 элементы И 105-1 105-2 и повторитель-инвертор 106

Блок управления выборкой команд ( 5 6) содержит инвертор 107 повторитель инвертор ЮР элемент НЕ 109, се

0 лекторы 110 112 данных для установки соответственно триггеров правой команды, правого группового режима и левого груп- поеого режима повторитель-инвертор 113. триггеры 114 116 соответственно правой

5 команды (ПРАВК) правого группового ре AHMd Ш и левого группового режима (ЛГ) се чек торы 117 1 -117.27 данных для счетчи- кя адресов командных слов (СЧА) элемент И 2И ИЛИ 118 дня выработки разрешения

0 вычитания единицы из содержимого МО (МГМГР), элемент И HF 119, счетчик 120 С 1А элемент И 121 элементы И 122 1- 122 пыработки стробов приема в регистры LAT j / регистры 123 1 123 8 буфера адре5 ь ( Слов 7 схему 124 совпадения, по- втеритело 125 элемент ИЛИ 126, шифратор 127 повторитель инвертор 128 элемент ИЬИ 129. элемент VI Hfc 130 повторитель- инвестср 131, селекторы 132 1 1323 дан0 ни« регистр 133 сдвига элементы 2И-ИЛИ 131 и 135 счетчик 136 количества занятых ре истров буфера команд регистры 137 1- 4 элементы И 1381 1384 мультиплексор 391 139 4 инверторы 1401-1403

5 э (г-еитыИ НЕ 141 селекторы 142 1-142 3 113 144 1451-1453 элемент И 146, эле м-чт И-2И ИЛИ 147 счетчик 148 записи киманд элементы ИЛИ 149, 150 элемент i 151 элемент И 152 дешифратор 153 I- /- i номир ) Ы-. Од 1Ь4 ,,1емрнта 126

соединенный с входом 154 элемента 129, шину 155 с выхода элемента 127, соединенную с входами элементов 145.1-145.3. шину 156 выходов элемента 153, соединенную с шиной входов 156 элементов 122.1 122.8, выход 157 элемента 121, соединенный с входом 157 элемента 130, шину 158 выходов элемента 151, соединенную с шиной 158 входов элемента 110. выход 159 элемента 115, соединенный с входом 159 элемента 143.

Блок предварительной обработки команды (фиг 7, 8) содержит регистр 160 кода команды, дешифраторы 161-163 кодов операций, селектор 164 кодов операций записи в модификаторы, селектор 165 кодов операций считывания, селектор 166 кодов операций прямого и обратного вычитаний модификаторов, селектор 167 кодов запрещенных команд, селектор 168 кодов реаль- ных команд, селектор 169 кодов операций установки модификаторов из арифметического устройства АУ, селектор 170 кодов операций передачи управления, селектор 171 стробов приема на СЧА в операциях передачи управления, селектор 172 кодов операций записи, селектор 173 кодовопера- ций прямого, обратного вычитаний модифи катороо и операции цикла, повторитель 174 кода компонентных операций, элемент И- НЕ 175 селектор 176 предварительных стробов приема на ре1истр результата (РР), селектор 177 гтробов приема на специальные модификаторы в операциях обращения к специальным модификаторам, элемент И 178 формирования кода операции возврата из прерывания (ВД) селектор 179 данных для установки триггера изменения команды (ТИК), элемент И 180, триггер 181 изменения команды ТИК, элемент ИЛИ 182, элемент И-2И-ИЛИ 183 выработки данных для триггера занятости регистра команды ТЗРК, элемент И 184 триггер 185 занятости оегистрэ команды, элементы 2И-2И-ИЛИ 18о.1- 186.7, 187.1-1877, триггер 188 временизй цепочки регистра команды, регистр 189 тегов и контрольного разряда регистра коман- ды, регистр 190 адресных разрядов регистра команды, регистр 191 модифика- торных разрядов регистра команды повто- рители-инверторы 192 1-192,20, схема193 свертки кода по модулю два, элемент И 194, элементы И 195.1 -195 5, 196-202, инвертор 203, элементы И--2И-ИЛИ 204 1-204.7 205.1-205.7. элементы И 206-213, шину 214 выходов регистра 160. соединенную с шиной 214 входов схемы 193 свертки, зыход 215 селектора 164, соединенный с входом 215 элементов 206--210, выход 216 селектора 172, соединенный с входом 216 элемента

200, выход 217 селектора 165, соединенный с входом 217 элемента И 199, выход 218 элемента 212, соединенный с входом 218 элементов 186.1-186.7, 187.1-187.7, выход 219 элемента 197, соединенный с входом

219элементов 186.1-186.7.

Блок регистров модификации адреса (фиг 9) содержит поразрядные селекторы

220данных, регистры 221.1-221.7 специальных модификаторов, регистры 222.1- 222.8, 223 1-223.7 рабочих модификаторов, причем регистр 222 8 является счетчиком магазина, но может использоваться и как обычный рабочий модификатор, дешифраторы 224-226, поразрядные мультиплексоры 227 выборки данных из специальных модификаторов, поразрядные мультиплексоры 228 и 229 выборки данных из рабочих модификаторов, дешифратор 230, схему 231 анализа групп разрядов счетчика магазина на единицы, схему 232 анализа групп разрядов счетчика магазина на нули селектора 233, 234 данных и дешифратор 235.

Блок прерывания (фиг. 10) содержит схему 236 свертки по модулю два, элементы И-2И-ИЛИ 237 и 238. элемент 2-2-2-2И- ИЛИ 239. инвертор 240, элементы И 241, 242 три1 еры 243 245 прерываний на уровнях AV РГ и РК, элемент И 46, элемент 2-2 2 2И-ИЛИ 247, инвертор 248, регистр 49 слви а к1нврргэр 250, элемент 11 П,И-НЕ 251, 2 2 И ИЛИ-НЕ 252. ЭЛР- мочт И 253

Блок суммирования адреса (фиг 11) содержит морвый полусумматор 254, шину 2G5 1 выходов поразрядных полусумм 1-го этажа, шину 255 2 выходов поразрядных пе реносов 1-го этажз элементы 2 3 ЗИ ИЛИ 256 1-256.6, формирующие сигналы переносов из пары смежных разрядов, начиная с 1-го второй полусумматор 257 шину 258 1 чыхолон пспззр - дных переносов 2-го лта- жа, шину 958 2 поразрядны полусумм п гс атажа ементы 2-2- 2И-ИЛИ 259 1 -259 г. формирующие разр.шение прията лер°ногт через пару смежных рэз- рядог. нт-иная с 3 :п схему 260 распространения перенесот я г о ж д ы и разряд полусумг/. схему 2С риведрни, двухряд ного кода к однорядному

Блок хранения ачреса(фиг 1) содержит поразрядные селекторы 262 для ре гистра результата РР, дешифратор 253 номера канала данных элемент И 264 триггер 265 признака компонентных операций на уровне РР регистр 266 результата РР, регистр 267 кода операции на уровне РР, триг rep 68 признака вычитания единицы из МО на ург. ч н DP дешифраторы 269, 270 кода операции на РР,эпеменгИ 271.

Блок регистровой памяти (фиг. 13) содержит регистры 272.1-272.8 буфера адресов записи БАЗО-7, элементы И 273.1-273.8, схему 274 совпадения адресов на РР и в БАЗО-7, поразрядные мультиплексоры 275 выдачи старшего регистра БАЗО 7, счетчик 276 записи, дешифратор 277. В предлагаемом устройстве предполагается единая система синхронизации. Блоки и элементы, использующие синхроимпульсы, имеют входы СИ, изображенные на чертежах.

Блок 1 предназначен для выработки на счетчике 120 СЧА и буферизации в буфере 123.1-123 8 адресов командных слов и выдачи адреса в буферное устройство связи БУС для подкачки слова из оперативной памяти. Кроме того, в буфере команд 137.1 137.4 запоминается код номера регистра БАСО-7 для последующего подключения соответствующего БАСО-7 информационного регистра в БУС к уровню регистра команды, после чего команда начинает выполняться. Буфер команд БК управляется сдвигателем 133 выборки регистра БК и счетчиком 136 количества заполненных регистров БК как по.приему (через мультиплексоры 139.1- 139.4), так и по выдаче через селекторы 142.1-142.3. Счетчик 148 записи команд служит для формирования стробов приема в выбранный регистр БАСО-7. Код номера регистра БАСО-7 с выбранного регистра БК 137.1-137.4 выдается в БУС по входу-выходу 19. Схема 124 совпадения адресов на СЧА и в БАСО-7 служит для организации ассоциативной памяти команд без обращения к оперативной памяти.

Блок 2 предназначен для приема команды из БУС на регистр команды (РК) - регистры 160,189-191. дешифрации кода операции и организации сигналов управления операциями. Адресная часть РК по выходу 34 выдается в блок 6 для выработки исполнительного адреса операции. Сигналы управления счетчиком магазина выдаются с элементов 204.1-204.7. 205 1-2057. отдельно от управляющих сигналов работы других модификаторов.

Блок 3 предназначен для организации рабочих,- регистры 222.1-222.8, 223.1- 223.7,и специальных,- регистры 221.1-221.7. модификаторов. Специальные модификаторы используются при прерываниях для установки и упрятывания признаков режимов работы процессора, для фиксации адреса возврата из прерывания и других целей. Рабочие модификаторы участвуют в образовании исполнительного адреса. Содержимое рабочего модификатора, участвующего в

операции, выбранное на селекторе 233 по ступает в блок сумматора адреса

Блок 5 предназначен для сборки на эле ментах 237-239 различных типов пргрыва- 5 ний, установки по ним соответствующих триггеров 243- 245 уровней прерываний ЛУ и памяти, уровня РР, уровня РК, а также для формирования на сдвигэтеле 249 временных сигналов аппаратных действий по упря0 тыванию в специальные модификаторы режимов, адреса возврата и т.д.

Блок 6 предназначен для образования исполнительного адреса операций и выдачи его по выходам 61-63 соответственно в блоки 3,9 и 1

Блок 9 предназначен для приема операции на уровень регистра результата (РР) - регистры 266, 267, триггеры 265, 268,и выдачи операции далее в БУС на буфер арифме0 тических команд, а адреса в блок 10 при записи вместе с кодом операции записи с элемента 271 по выходу 77, а также выдачи адреса по выходу 78 в БУС на схему управления обращением к памяти за операндом

5 при считывании.

Блок 10 предназначен для буферизации адресов записи с уровня РР в буфере адресов записи БАЗО-7-регистры 272.1-272.8. сравнения адресов на РР и в БАЗО-7 на

0 схеме 274 совпадения, аналогичной соответствующему элементу 126 в блоке 1, и организации тем самым ассоциативной памяти чисел на 8 регистров без обращения к оперативной памяти. Адрес с самого ста5 рого по времени записи БАЗО-7 через мультиплексор 275 по выходу 80 выдается в БУС на схему управления записью в оперативную память.

При орагнизации режима изменения

0 адреса команды исполнительным адресом предыдущей специальной операции в устройстве управления прототипа сначала на двухвходовом сумматоре адреса происходило сложение кодов адресной части коман5 ды и исполнительного адреса специальной команды, запомненного на специальном регистре Результат сложения запоминался на этом же специальном регистре-модификаторе. Затем полученная сумма складывэ0 лась с содержимым базового модификатора, участвующего в изменяемой команде, а вновь полученная сумма считалась окончательным исполнительным адресом Таким образом, начало выполнения собственно

5 данной операции удлинялось на время образования первой указанной суммы. Связано это было с тем. что после образования первой суммы необходимо было проверить результат на возможную магазинность, т.е код 17(8) в модификлтормых разрядах

команды и во всех разрядах первой суммы, так как это влияло на режим выполнения команды. Как было установлено в эксплуатации, возможное использование магазимности команды после ее измене- кия предыдущей командой не применялось, так как приводите к трудностям при программировании Поэтому это ограничение, т.е, предварительный анализ первой суммы на магазинность в режиме изменения ко- манды, в предлагаемом устройстве управления снято, в связи с чем появилась возможность сразу вырабатывать исполнительный адрес из трех слагаемых, учитывая совместимость с системой команд ЭВМ БЭСМ-6.

На вход 58 первого полусумматора блока 6 по выходу 24 из блока 2 поступают разряды адресной части регистра команды, на вход 60 по выходной шине 66 блока 7 поступают разряды хранящего регистра с маскированием по выдаче ХРМ, на котором хранится исполнительный адрес предыдущей специальной операции изменения команды. На вход 59 по выходной шине 47 блока 3 поступают данные с модификатора, участвующего в операции. Выдача ХРМ обеспечивается тем, что в операциях изменения команды вырабатывается строб выдачи содержимого ХРМ, поступающий с элемента 182 блока 2 по выходу 3 на вход 64 блока 7 В режиме изменения команды строб выдачи содержимого ХРМ вырабатывается триггером 181 изменения команды ТИК, установка которого происходит при за- вершении операции изменения команды по селектору 179 данных при наличии на РК кода этой операции, выделяемого с дешифраторов 161-163 и сигнала готовности РК - ГРК, поступающего из блока 5 с входа-выхо- да 52 на вход-выход 37 блока 2. Первый полусумматор 254 имеет 3 входа: А. В и С. Обычно на полусумматор на входы А и В подаются два слагаемые а на вход С - сигналы переноса от предыдущего поразряд- ного переноса. Так как в предлагаемом устройстве Е, блоке 6 на вход С заведены данные с рабочего модификатора, т.е. третье слагаемое, то необходимо выходы первого полусумматора снова сложить на втором полусумматоре 257 и затем после распространения переносов в каждый разряд привести двухрядный код к однорядному. Длч ускорения образования переносов используются элементы 256.1-256.6 воз- никновения переносов из каждой пары младших 12 суммируемых разрядов после первого полусумматора и элементы 259.1- 259.5 анализа разрешения распространения через пары смехных разрядов начиная

с 3-го по 12-й. Так, если поразрядные полусуммы и поразрядные переносы после 1-го полусумматора по месту их возникновения можно обозначить как ПС)САП-шина 255.1 и nnjCAn-шина 255.2, то перенос из младших двух разрядов суммируемых трех слагаемых формируется на элементе 256.1 так;

Г12 -ПП1САП ПС2САП 4 +ПЕСА ПП1САП- ПС1САП + +ПЕСА-ПС1САП ПС2САП, где ПЕСА - сигнал прибавления единицы дополнительного кода к младшему разряду, используется в операциях вычитания и цикла, формируется в блоке 2 на элементе 173 и с выхода 36 поступает на вход 56 в блок 6.

Далее для 3-го и 4-го разрядов имеем:

Г34 - ППЗСАП -ПС4САП + ППЗСАП- ПП2САП ПСЗСАП + ПП2САП ПСЗСАП- ПС4САП, и т.д.

Для 11 и 12-го разрядов:

Г1112 ПП11САП -ПС12САП + + ПП11САП ПП10САП ПС11САП + + ПП10САП -ПС11САП- ПС12САП.

Разрешение распространения переноса через пару разрядов формируется, начиная с 3-го разряда (элемент 259 1):

Р34 ППЗСАП -ПСЗСАП + ПП2САП- ПС4САП + ПП2САП -ППЗСАП + + ПСЗСАП ПС4САП и т д.

Для 11 и 12-го разрядовР1112 - ПП11САП- ПС11САП + +ПП10САП ПС12САП + ПП10САП- ПП11САП+ ПС11САП- ПС12САП.

Поскольку двухрядный код с выходов 1-го полусумматора необходимо снова сложить, а затем во вновь полученном двухрядном коде уже распространять переносы и приводить его к однорядному, организован второй полусумматор 257, с шины 258.1 которого выдаются поразрядные переносы ПП СА, вырабатываемые на элементах И по формуле

ПП(Н)САП

С шины 258.2 выдаются поразрядные полусуммы nCjCA, вырабатываемые на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ. на вход каждого элемента подаются ПП(-1)САП и .

Используя схемы просмотра переноса на 4 разряда из 100-й серии микросхем 100ИП79, можно организовать рэспростра пение переносов в каждый из 27 разрядов суммы Элемент 100ИП79 описывается следующим образом

С4(сигнал 1) С2(си1нал 2) Р(сигнал 3) Ж (сигнал 4)- Р(РО,Р1,Р2 РЗ)Ж(ЖО. Ж1.Ж2. ЖЗ) С (СО).

Логика его работы отображается следующим образом:

Р РЗ РЗ Р1 РО-условие разрешения пробега переноса через 4 анализируемые разряда;

Ж ЖЗ -Р2 -Р1 -РО + Ж2 Р1 РО -Ж1

РО ЖО - условие выработки собственного переноса из группы 4 суммируемых разрядов;

РЗ Р2 Р1 РО+ЖЗ -Р2 Р1

РО+Ж2 Р1 РО+Ж1 PO-f ЖО условие выработки собственного переноса из группы 4 суммируемых разрядов либо пробега пришедшего переноса через группу 4 суммируемых разрядов;

С2 СО РЗ Р2 + ЖЗ Р2 + Ж2 - условие выработки собственного переноса из группы 2 младших суммируемых разрядов либо пробега пришедшего переноса через группу 2 младших суммируемых разрядов, где СО - пришедший перенос извне, Ж - поразрядные переносы. Р - поразрядные полусуммы.

В схеме 260 распространения переносов распространенные переносы в разряд организованы по следующим формулам, где распространенный перенос обозначен П СА:

ПЗСА Н(П2. ПСЗСА) - элемент ИСКЛЮЧАЮЩЕЕ ИЛИ.

Далее на элементах 100ИП79:

С4(П5СА)С2(П2СА) Р{ ,Р34, -,ПСЗСА)Ж(ноль, г 34, ноль. ППЗСА)С(П2) где-- означает логическую 1, а 4 ноль - логический О.

С4(П11СА)С2(П70А) - (Р910,Р78,Р56, Р34) Ж(Г910.Г78,Г56,Г34)С(П2);

С4(П8СА)С2(П6СА) - Р(ПС7СА,ПС60А, ПС5СА, -)Ж(ПП7СА,Г56,ПП5СА.П5СА) С(ноль);

С4(П11СА)С2(П9СА)РиР910,Р78,Р56) Ж(ноль,Г910,Г78.Г56)С(П5СА), где П11СА вырабатывается дублирование из-за большой нагрузки на старшие элементы анализа;

С4(П12СА)С2(П10СА) Р(ПС11СА.Р910. ПС9СА.Р78)Ж(ПП11СА,Г910,ПП9СА,Г78) С(П7СА):

С4(П15СА)С2(П13СА) Р(ПС14СА. ПС13СА,- ,Р11 12)Ж(ПП14СА,ПП13СА, ноль,Г1112)С(П11СА)ит.п.;

С4(П27СА)С2(П22СА) Р(Р2226., Р1721,Р1116)Ж(Г2226,ноль,Г1721,П116)С (П11СА). где Р2226 вырабатывается на элементе И из ПС22СА-ПС26СА.

На схеме 261, организованной на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ, двухрядный код ПС СА и П СА приводится к однорядному коду исполнительного адреса, разряды которого по шинам 61 63 выдаются соотве1ст- венно в блоки 3. 9. 1. Так лк в прототипа было два слагаемых, то второй полусумматор отсутствовал Но отсутствовала и группа элементов 256.1 256.6. 259.1 259.5. позволяющая быстрее формировать распростра нение переносов. В итоге количество логических уровней блока 6 не изменилось, а время сложения не возросло.

В блоке 1 с входа 18 разряды исполнительного адреса через селекторы 117.1- 117.27 данных поступают на счетчик 120 адреса командных слов СЧА по стробу приема поступающему на вход-выход 21 из блока 2 по входу-выходу 38. Строб формируется в блоке 2 на селекторе 171 в операциях перехода. Адрес со СЧА поступает в регистры 123.Ы23.8 буфера адресов слов, представляющего ассоциативную память команд, и выдается в буферное устройство связи (БУС) по выходу 19 для выборки команды из памяти.

В блоке 3 с входа 42 разряды исполнительного адреса через селекторы 220 данных поступают в модификатор при выполнении операции записи в модификаторы.

В блоке 9 с входа 72 разряды исполнительного адреса поступают на селекторы 262 данных, а с них - на регистр 266 результата РР в операциях считывания, записи и др. С регистра 266 РР адрес выдается в 6УС на обращение к оперативной памяти ОП по выходу 78, в случае операции записи по выходу 77 в блок управления буфером запи си на вход 79. С входа 79 адрес поступает в назначаемый счетчиком 276 записи самый старый по времени записи регистр 272.1- 272.8 БАЗО-7 буфера адресов записи, содержимое которого соответственно через мультиплексор 275 выдается по выходу 80 в БУС на обращение к ОП по записи числа Буфер адресов записи БАЗО-7 предназна чен для организации 8 регистровой ассоци атионой памяти чисел, т.е. без обращения к ОП. для чего на схеме совпадения 274 про исходит поразрядное сравнение адреса на РР и в БАЗО-7 и в случае совпадения сигнал совпадения по выходу 80 выдается в БУС. отменяя считывание из ОП и организуя считывание из информационного регистра, одинакового по номеру с совпавшим регистром БАЗО-7. Схема совпадения аналогична соответствующему элементу 126 в блоке 1 для команд.

При обработке массивов данных (перепись, преобразование и т.д) как правило ис пользуется сцепка из основной операции обработки, операции изменения базового модификатора и операции цикла В предлагаемом устройстве управления введением компонентных операций и групповых режимов их работы обработку массива данных можно вести одной основной операцией обработки (компонентной операцией) без дополнительных, либо двумя основными операциями без дополнительных. Для этого вводится аппаратный счетчик числа проходов, т е счетчики 94 1 94 7 в блоке А. схемы триггеров правого и левого группового режимов в блоке в селекторе данных регистра результата в блоке 9 введена дополнительная входная шина 74 данных, выдаваемых по выходу 45 из блока 3. Для организации группового режима введена операция установки группового режима УГ которая свой исполнительный адрес передав в МО и устанавливает правый или левый групповой режим для последующей команды или двух последующих команд Если компонентная операция является правой в командном слове а УГ левой командой то устанавливается правый групповой ре жим, в котором компонентная операция выполняется многократно до исчерпания содержимого МО, который с каждым однократным выполнением компонентной one рации уменьшает свое содержимое на 1 МО организован как сметчик, работающий в режимах вычита ия Т прибастения 1 при прерывании на /ровне РР а пи раллельниго приема данных при загрузке командой УГ.

Если УГ является правой командой, то многократно выполняется сцепка из ДВУХ (омпонентнчх операций, находящихся ь следующем командном слове, до исчерпа НИР содержимого МО, которое уменьшается на 1 после i аждою однократного выпол нениь сцепки из дчуу компонентных оперг цпй.

Посте и черианиа содержимого МО групповой режим сбрасывается и поестз- навг.иваегсч нормальный редким выпол сз- ния последующих команд

В стмих комг онентныхоперациях обр зевавшийся исполнительный адрес засылается в рабочий модификатор указанный в команде, тем самым подготавливая операцию для обработки следующего элемента массива данных а. на регистр результата для обращения за операндом в качестве ад реса выдается предыдущее содерхимое рабочего модификатора Таким образом обрабатываются массивы данных расположенных в оперативной памяти с шагом нг только 1, а и + - к т е элемрнг массива or элемента может находиться на произео1ь ном заранее выбранном расстоянии Кроме того, обработка может вестись в любую сторону, тек началу массива от его конца и наоборот

Компонентные операции могут использоваться и без групповых режимов их выполнения, т е сами по себе

Из блока 3 по выходу 45 с селектора 234 поступает содержимое рабочего модифика rjpa участвующего в операции (компонент- нон) Для выделения этого канала в

0 сечек-ope 62 блока 9 с входа выхода 29 и с выхода 13 блока 2 соответственно на вход- выход 76 г на вход 75 блока 9 подаются сигнз ты выбора канала данных Канал выбирается соответствующим кодом на дешиф5 раторе263 Из блока 9 по входу выходу 76 в блок 2 на вход выход 29 и далее на элемент И выдается значение триггера 268 запоминания вычитания 1 из МО в случае прерывания на РР по защите листа памяти При

0 позррате из этого прерывания код на МО увеличивается на 1, а операция, давшая прерывание, начинает повторно выполняться с уровня РК Из блока 2 по входу выходу 30 в блок 4 на вход выход 49 поступают

5 сигналы управления работой МО как счетчика и на прием Они формируются на элементах 186 1-ч% 7 и 187 1 187 7 в блоке 2 для чего из Спг..ка 4 по входу выходу 49 в блок 2 ча t/од ыход 30 выдаются сигналы чнали0 зг одерхимо. МО на нуг.и и ед1 ницы с резррдох Для этого в опке 4 инверсные вы/оды повторителей инверторов 95 1 95 й и внходи и-.рерторов 96 1 96 Ч анллизиру юте ч на единицы в 4 В, 12 16 20 24 и во

Ј cf/ 27 p,rjpЈr 3 (сигнал АОМО) нэ элементах И 83 1 83 7 90 Сигнал АОМО фиксирующий нулевое значение кода на МО, с з темеита И 90 по выводу 50 поступает в блок

1из иход 22 и . iep нэ элемент И-НЕ 109 О (пяотаниэа ии сброса тритррив 116 и 117

группового оежима как леього так и правого,

Так как при мрчь м , ру товом р ПГ

омзид,1 i3 PK остаб Ся без измe ения но

выполн егсч мнок ратно г- выработка

3 строба Г Р -емо ч, РЧ ПРК нэ ЭЛРМСНТР 151

6nGtc, 1 б ЮКИрО ана И 3rjpCHb M ВЫХОДОМ

элемента И НЕ ИЗ, нч входы которого по ступают АОМО и чначе ие три: гера 115 ПГ по входу-выходу 159 Вырлбативаютгя тишь

0 стробы ПРКК на элементе 152 по разреше что приема очередной команды по входу выходу 21 й по готовности командного слова из БУС по входу вы/оду 19 Эти стробы обеспечивают лишь многократно выпотне

5 v ние одной и той же команды запуская о блоке

2временную цепочк i- K - триггер 188 и устанавливая три гер 185занягосш РК, ко горый асыте я каждый раз пгспе оче редного выполнения команды Сброс трекера эоиитости РК фг рмпруется на ло

менте 175 по разрешению приема команды и готовности регистра команды (ГРК). ГРК вырабатывается в блоке 5 и выдается оттуда с входа-выхода 51 на вход-выход 24 блока 1. ГРК вырабатывается на элементе И 253 по- еле сброса однократного триггера 188 временной цепочки блока 2 и при нулевых значениях триггеров 245 и 243, а также 244. идентифицирующих внутренние прерывания соответственно на уровнях РК, памяти и уровня PP.

Из блока 2 по входу-выходу 27 в блок 1 на вход-выход 21 поступает признак операции УГ для установки триггеров правого 1 15 или левого 116 группового режимов. Триг- гер 114 привой команды ПРАВК в блоке 1 устанавливается в 1 при приеме на РК левой команды и в О - при приеме правой команды. Соответственно его значение. равное 1, устанавпивзет триггер 1 15 ПГ, а значение, равное О - триггер 116 ЛГ. Из блока 3 с регистра 221 3 по выходу 40 на вход 20 блока 1 и далее соответственно на селекторы 112, 111 и 110 поступают заполненные в момент прерывания состояния триггеров соответственно 116 (Л Г), 115(ПГ) и 1.14 (ПРАВК), которые устанавливают эти триггеры в исходное состояние при возврате из прерывания Установку обеспечивает операция возрратг из диг.гет зра (ПД; при- знак которой поступает п блек 1 Hd селекторы 110-112 по входу- ыходу 21 с элрменга Л 178 блока 2 по вход / выходу 27 Признак компонентных операций, т е код 01(3) в старших разрядах кода операции на РК с элемента 174 по входу-выходу 29 блока 2 выдается в блок 9 на вход-выход 76 и приводит к установке при приеме операции на РР триггера 265 компонентной операции на уровне PP. С триггера 265 его знячение по выходу 78 выдается а БУС для программной коррекции рабочего модификатора в случае возврата из прерывания по защите листа и повторного выполнения команды, начиная с уровня РК.

Для эффективного поиска ошибок в отлаживаемых программах, особенно в языках программирования высокого уровня, в предлагаемом устройстве управления про- цессора введен механизм прерываний по командным тегам, которые представляют собой два дополнительных к информационным разрядам командного слова Один из них, 4-й по счету (так как младшие 1-3 не- пользуются как механизм прерывания по числам вне устройства управления), вызывает прерывание на уровне РК, на который принимается команда после передачи управления на нее Другой, 5-й по счету, вызывает прерывание на уровне РК после приема очередной команды линейного участка программы, т.е. при отсутствии передачи управления на эт команду.

Для этого в блок 8 на вход 69 с выхода 38 блока 2 поступают разряды тегов с регистра 189 специальных разрядов РК, а с вы хода 25 блока 1 с повторителя 125 поступает на вход 67 блока 8 строб приема на счетчик СЧЛ, который используется и внутри блока i Этот строб устанавливает триггер 104 передачи управления Триггер 104 передачи управления хранит сиое состояние благодаря элементу 103 1, на второй вход которого по входу 69 поступает сигнап запрета сброса с выхода 38 блока 2. На элементе 103-2 чоммутатора 102 в блоке 8 формируется прерывание по некомандному тегу:

а) при ТПУП в 1 и 4-й тег в 1,

Б) при ТПУП в О и 5-й тег в 1.

Раздельные условия а и б вырабатываются на элементах 105-1 и 105 2 и выдаются по выходу 70 на регистр внутренних прорываний и анализируются программой- отладчиком задач. Так как эти прерывания происходят на уровне РК, то по выходу 68 сигнал прерывания с элемента 103-2 выдается на вход 54 блока 5 и через селектор данных устанавливает триггер 245 прерываний на уровне РК ТПРЕК. который через э, емент 247 запус-тет регистр 249 сдвига, нарабатывающий однократные временные сиг (Злы прерывания, по которым посисхо- дит обращение по записи в специальные регистры блока 3 и уход на обработку прерывания Ь блоке Ь, кроме того, есть триггеры 244 и 243 прерываний уровней РР АУ и пёмг|Т: 1., которые в случае прерывания на этих уровнях также запускают через эле- ме -IT 247 регистр 249 сдвига

Использование предлагаемою устройства управления процессора позволяет повысить быстродействие команд в режиме изменения адреса команды, увеличить быстродействие процессора при обработке массивов данных и эффективно производить отладку программ, используя прерывания по командным тегам, тем самым получая граф ошибочных переходов в программе

При обработке массивов данных, например при переписи массива в памяти, сцепка операций считывания, изменения первого базового модификатора, записи, изменения второго базового модификатора и цикла в прототипе выполняется за время

2Т f 2Т 2Т + 2 Г - 6Т 14Т (тактов).

Сцепка компонентных считывания и записи выполняется за время 2Т 4Т 6Т (тактов).

Формула изобретения Устройство управления процессора, содержащее блок управления выборкой команд, блок предварительной обработки команды, блок регистров модификации адреса, блок прерываний, блок суммирования адреса, блок хранения адреса, блок регистровой памяти, вход строба приема адресов слов, вход готовности команды, выход адреса команды, выход признака правой команды, выход номера регистра блока управления выборкой команд подключен соответственно к одноименным входам и выходам устройства, вход признаков прерывания и вход адреса возврата блока управления выборкой команд соединены соответственно с первым и вторым информационными выходами блока реестров модификации адреса, вход разрешения приема команды, вход строба приема на счетчик адресов слов и выход строба приема на регистр команды блока управления выборкой команд соединены соответственно с одноименными выходами и входом блока предварительной обработки команды, вход исполнительного адреса счетчика адресов слои и вход готовности регистра команды блока управления выборкой команд соеди нены соответственно с первым выходом исполнительного адреса блока суммирований адреса и выходом готовности регистра кс- манды блока прерываний, вход команды блока предварительной обработки команды соединен с входом команды устройства, вход признака нулевого содержимого модификатора, выход данных для дешифратора стробов приема, выход данных для дешифратора строоов выдачи и выход данных для дешифратора канала приема на модификаторы блока предварительной обработки команды подключены соответственно к третьему информационному выходу, первому, второму и третьему входам задания режимов блока регистров модификации адреса, выход строба управления адресным смещением команды и выход строба приращения сумматора адреса блока предварительной обработки команды подключены соответственно к одноименным входам блока суммирования адреса, вход готовности регистра команды, вход временных сигналов прерывания, выход сигнала сборки запрещенных команд, выход четной свертки команды блока предварительной обработки команды подключены соответственно к одноименным выходам и входам блока прерывания, выход кодозых оазрядов регистра

команды и выход строба приема на регистр результата блока предварительной обработки команды подключены соответственно к первым информационному и управляющему входам блока хранения адреса, выход адресного смещения команды блока предварительной обработки команды соединен с первым входом дамных блока суммирования адреса, первый информационный вход

0 блока регистров модификации адреса соединен с входом данных для регистров моди- фикации адреса устройства, второй информационный вход, четвертый и пятый информационные выходы блока регистров

5 модификации адреса соединены соответственно с вторым выходом исполнительною адреса блока суммирования адреса, вторым информационным входом блока хранения адреса и вторым входом данных блока сум0 мирования адреса, вход признака защиты и выход данных для регистра прерываний блока прерывания подключены соответственно к одноименным входу и выходу устройства, выход сигнала отсутствия

5 прерывания по защите блока прерывания соединен с вторым управляющим входом блока хранения адреса, третий выход исполнительного адреса блока суммирования адреса соединен с третьим информэцион0 ным входом блика хранния адреса, первый иыход данных и ьыхсд строба приема й,,ре- г.а записи которого г сдк;|Ю ечы couf O CT- венно к входу дайны и их од/ з&писи блоки регистровой памяти, итороч вь,ход генных

5 блика хранение адреса соединен с первым выходом адреса чет родства, выход Ол ока регистровой памяти соединен (. вторым выхо дом адреса устройства, отличающее - с я тем, чго с целью повышения быстродеи

0 ствия, очз дополнительно содержи блок нулевого модификатора регистр с рованием по выдаче и блок прерываний по командным reiaw, & бпок нулевого модификатора содержит с летчик и уаел анализа ну5 лей и единиц регистр с маскировэь IIRM по выдаче содержит регистр и гру.пу элементов И, блок прерываний Г|о командным тегам содержит сумк о i .3 по модулю два. триггерный узел и ком.тятор, причем тре0 тий информационный вход и шестой инфор- мационный выход б i о к a per ис троп модификации адреса соединены, сстьетст- венно, с информационными выходом и входом счетчика, выход которого

5 дополнительно подключен к информацией ному входу узла анализ нулей и единиц, информационный выход которого и вход управления режимом счетчика ЛОДКЛЮЧРНЫ соответственно к вход признаков нулей и единиц и выходу управления сметчиком блока предварительной обработки команды, выход признака нуля узла анализа нулей и единиц подключен к одноименному входу блока управления выборкой команд, информационный вход и вход записи регистра со- единены соответственно с седьмым информационным и управляющим выходами блока регистров модификации адреса, выход регистра подключен к первым входам элементов И группы и четвертому информа- ционному входу блока регистров модификации адреса, вторые входы элементов И группы подключены к выходу строба маскирования по выдаче блока предварительной обработки команды, выходы элементов И группы подключены к третьему ахиду данных блока суммирования адреса, выход строба приема на счетчик адресов слов блока управления выборкой команд подключен к входу установки триггерного узла, вход запрещения сброса которого соединен с одноименным выходом блока предварительной обработки команды, выход триггерного узла соединен с управляющим входом коммутатора, входы сумматора по модулю два соединены с информационными входами коммутатора, выход сумматора по модулю два и первый выход коммутатора подключены соответственно к выходам разрядов тегэ команды блока предг.зрительной обработки

команды, к входу признака четной свертки. тега и входу признака некомандного тега блока прерывания, второй и третий выходы коммутатора образуют выход дополнительных причин прерывания устройства, вход признака установки группового режима блока управления выборкой команд соединен с одноименным выходом блока предварительной обработки команды, выход разрешения вычитания единицы из нулевого модификатора и выход строба запуска команды в групповом режиме блока управления выборкой команд соединены соответственно с одноименными входами блока предварительной обработки команды, вход состояния триггера вычитания единицы из нулевого модификатора, выход признака вычитания единицы из нулевого модификатора и выход данных для дешифратора канала приема на регистр результата блока предварительной обработки команды соединены соответственно с одноименными выходом и входами блока хранения адреса, выход строба управления слагаемым из регистра с маскированием по выдаче блока предварительной обработки команды соединен с одноименным входом блока суммирования адреса, восьмой информационный выход блока регистров модификации адреса соединен с четвертым информационным входом блока хранения адреса.

а

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Устройство для сопряжения масс-спектрометра с ЭВМ | 1988 |

|

SU1580379A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1605239A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе | 1986 |

|

SU1368883A1 |

| Программируемый логический контроллер | 1984 |

|

SU1497616A1 |

| Устройство для обмена информацией | 1985 |

|

SU1334151A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

Изобретение относится к вычислительной технике и предназначено для использования в процессорах универсальных и специализированных ЭВМ. Цель изобретения - повышение быстродействия - достигается благодаря наличию в составе устройства блока управления выборкой команд, блока предварительной обработки команды, блока регистров модификации адреса, блока нулевого модификатора, блока прерывания, блока суммирования адреса, регистра с маскированием по выдаче, блока прерывания по командным тягам, блока хранения адреса и блока регистровой памяти. 13 ил.

СИ

78

ф. 4

с я

П

60

П

2 гп&

W

Т| Tpf

/t ttt

т

/ k А Ж

ft

7ГЖ7

1

tt

J

k/ V

Л

if

L166

t

9 ИЗ

16

/

99

6b

09

1

гп

69

Т

-Чт

06 16

ТТ 7

Htf

I

г/г

-ftW

..j

l

л л

«J Z

П

LilB

6/7

9890/L91

69

69 67

101

Т Г

W6

t

105-2

Фиг, 4

51

б9г ра

rijf

# r # с: / Е #

и

/л;

J5J 3Ј

W Г/ //

;/ гпф А. & i

19

/V/k/V/ /k/k

/ №

9-gsi

1

И

95

с: / Е #

и

HJ //J /7J

9L SL И

гпф . & i

19

19

Ј9

ЈШ

w/

/

/s

gj h-i

т

б 09 es

IS

9890/.91

Щи г. 13

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство управления | |||

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1991-08-15—Публикация

1988-11-04—Подача