Изобретение относится к вычислительной технике, а именно к устройствам управления ЭВМ, и может быть использовано при проектировании памяти вычислительной системы.

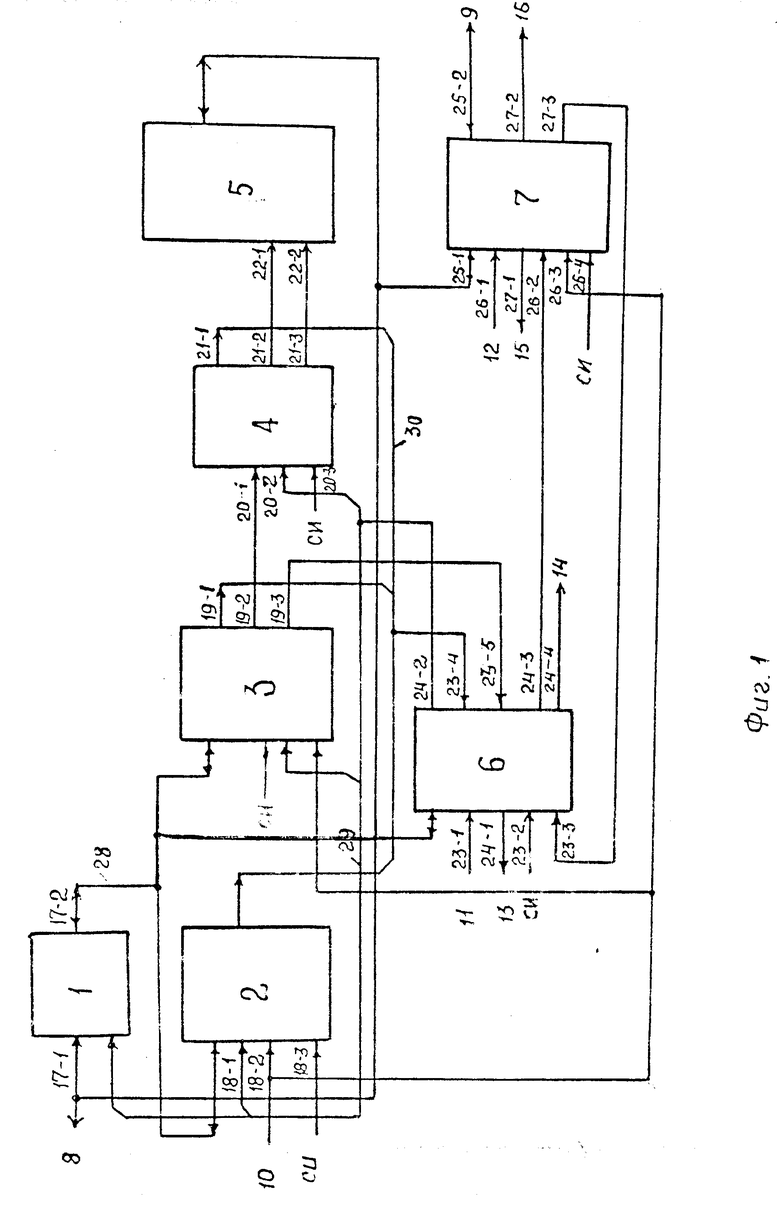

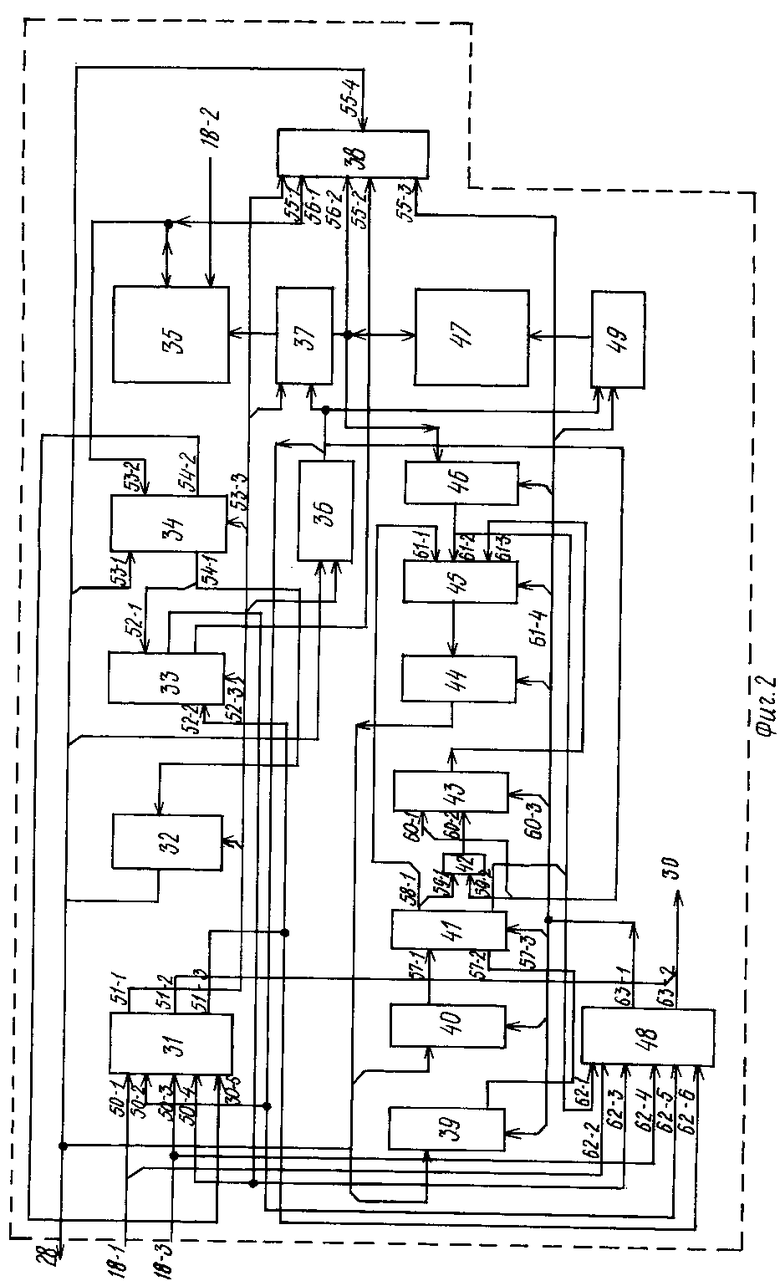

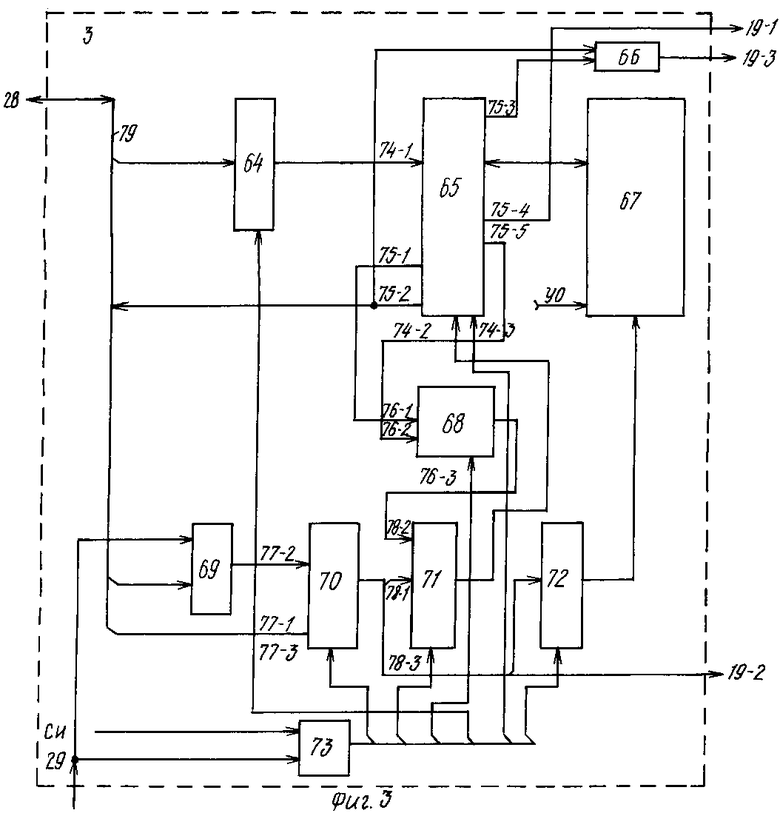

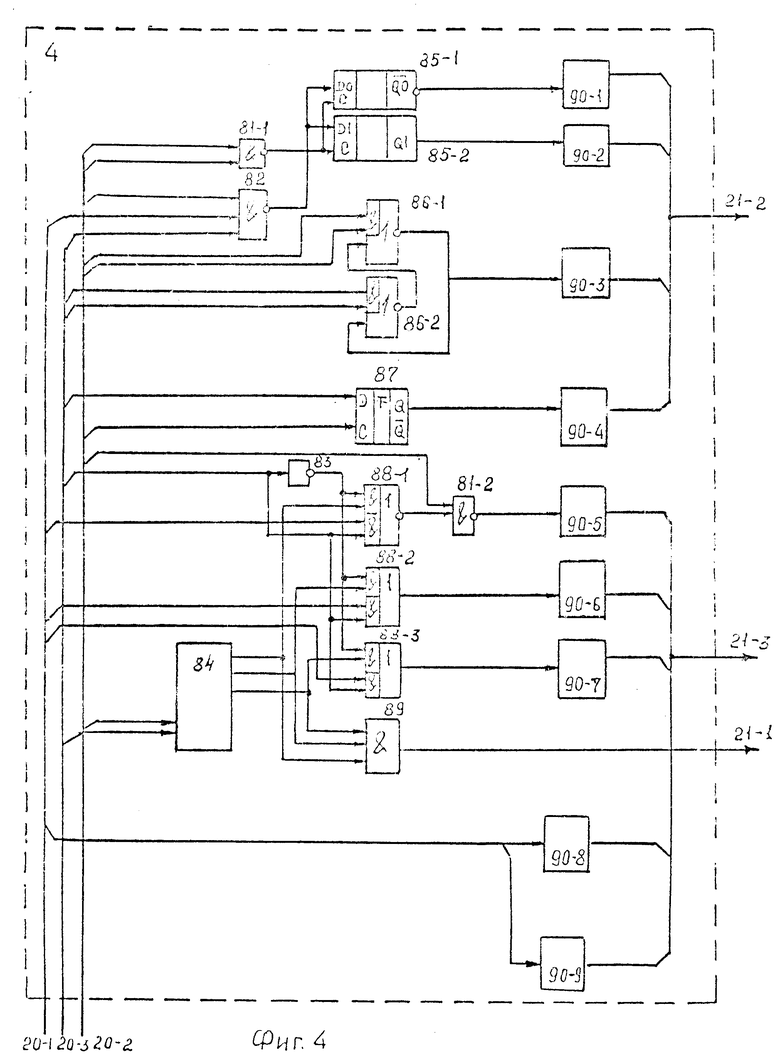

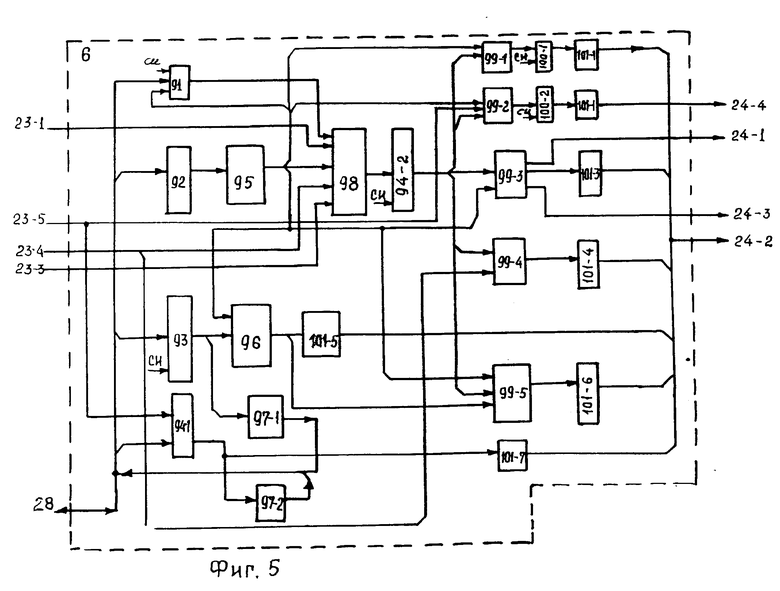

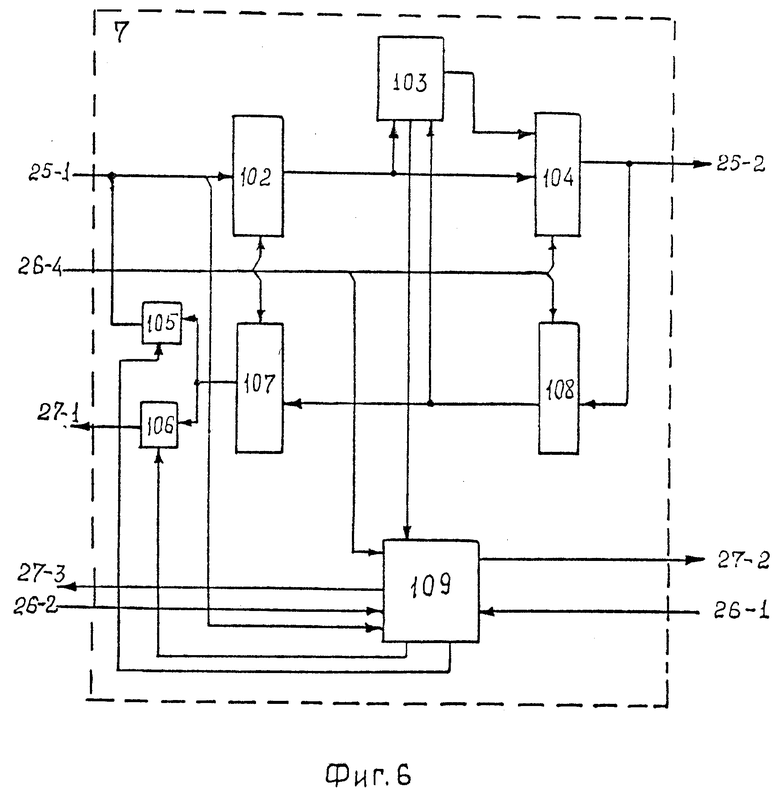

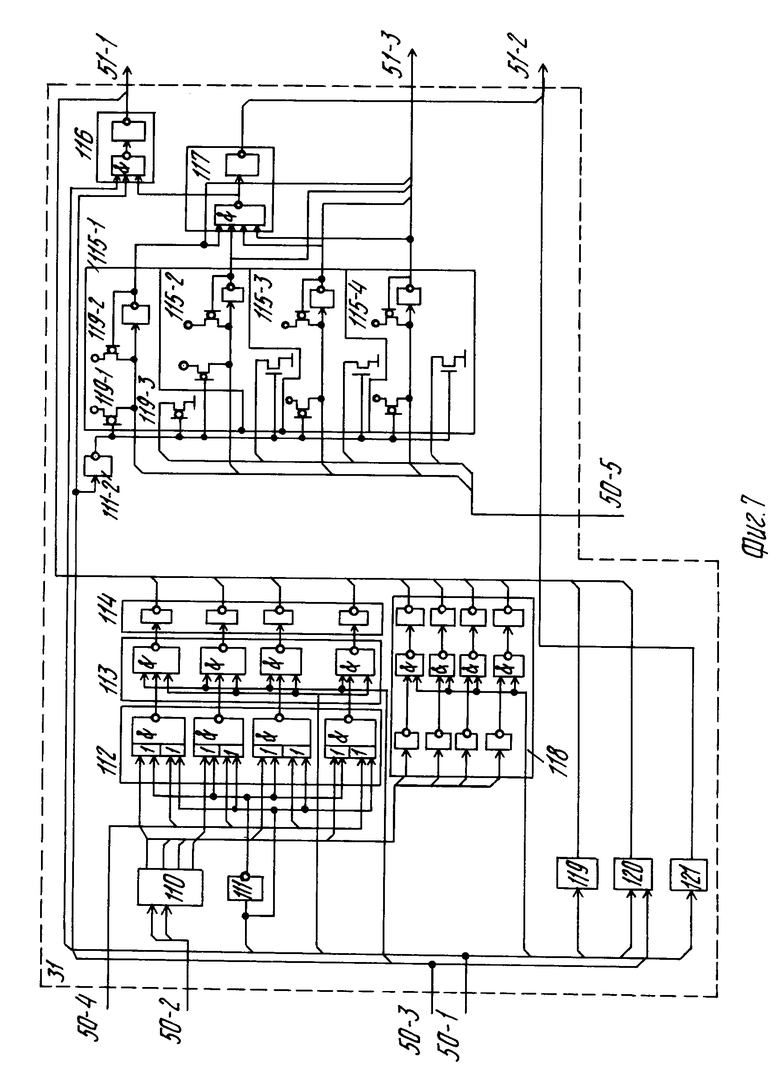

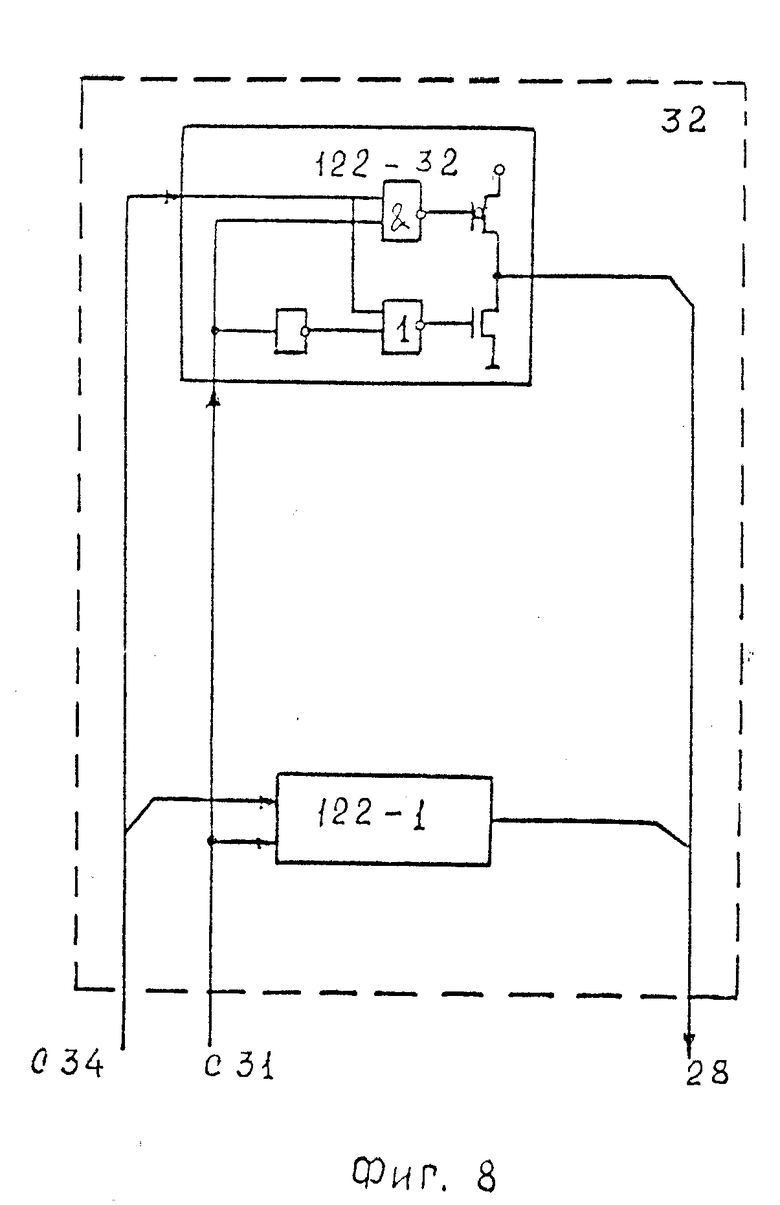

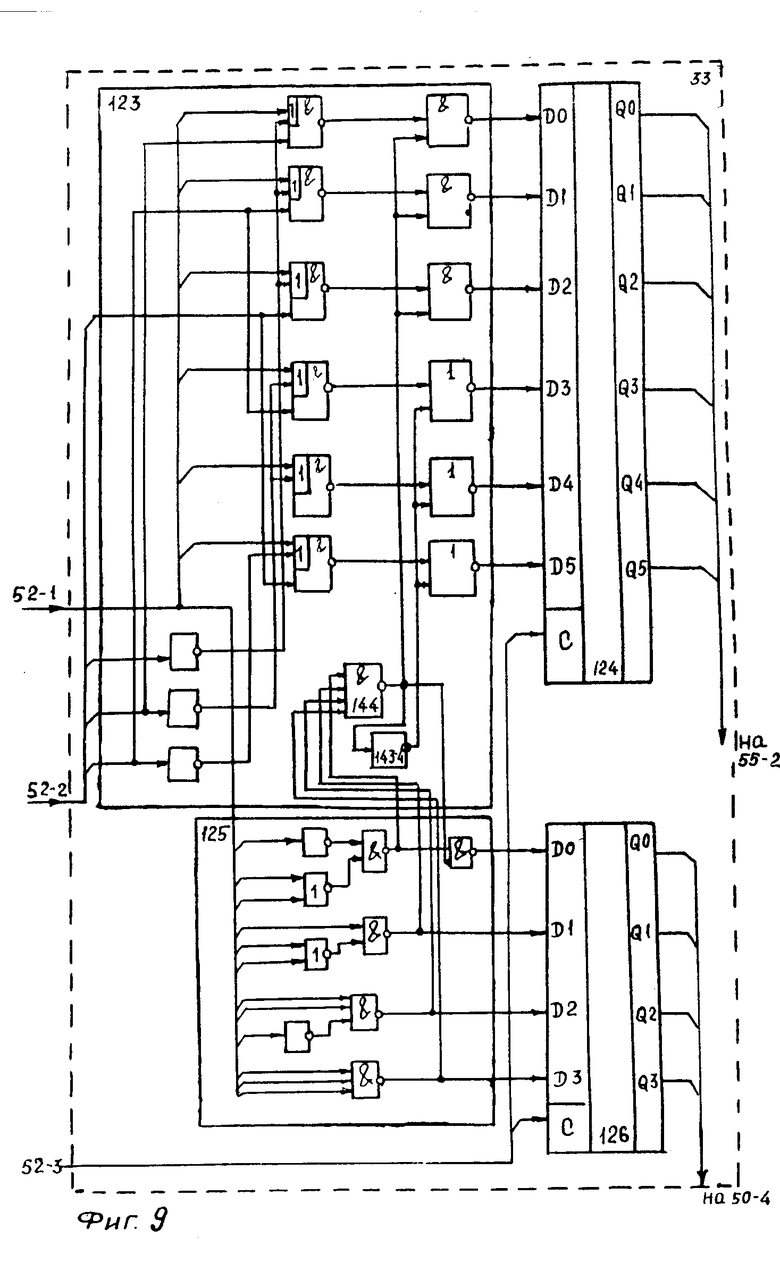

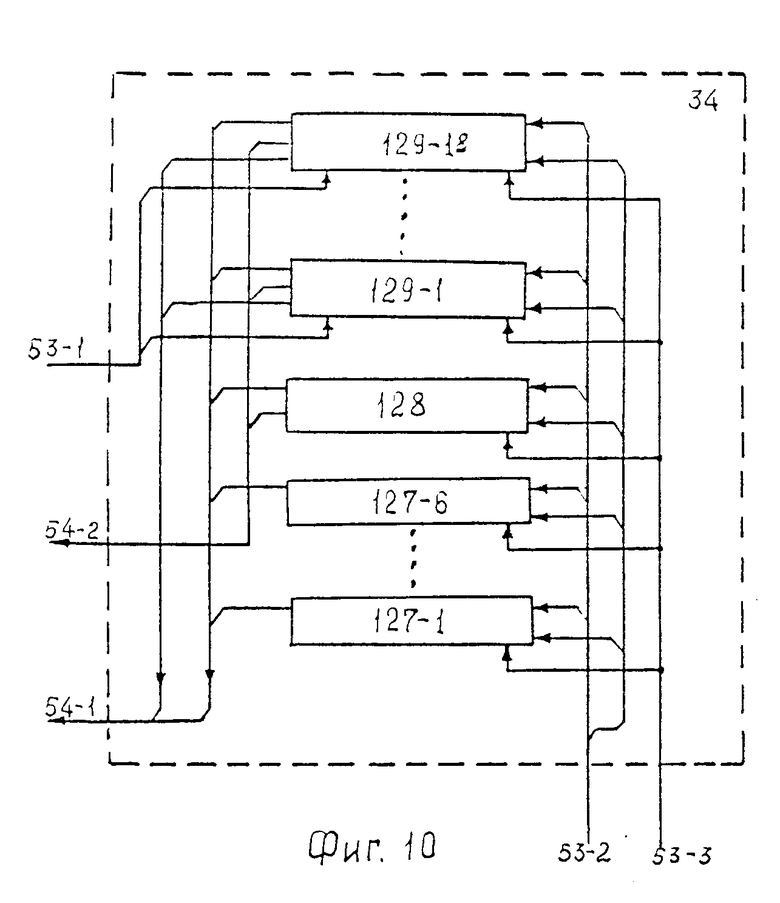

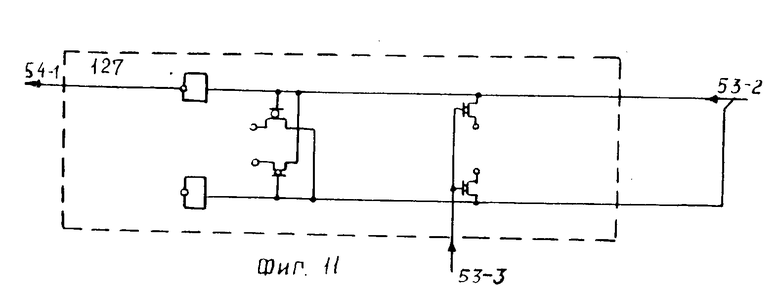

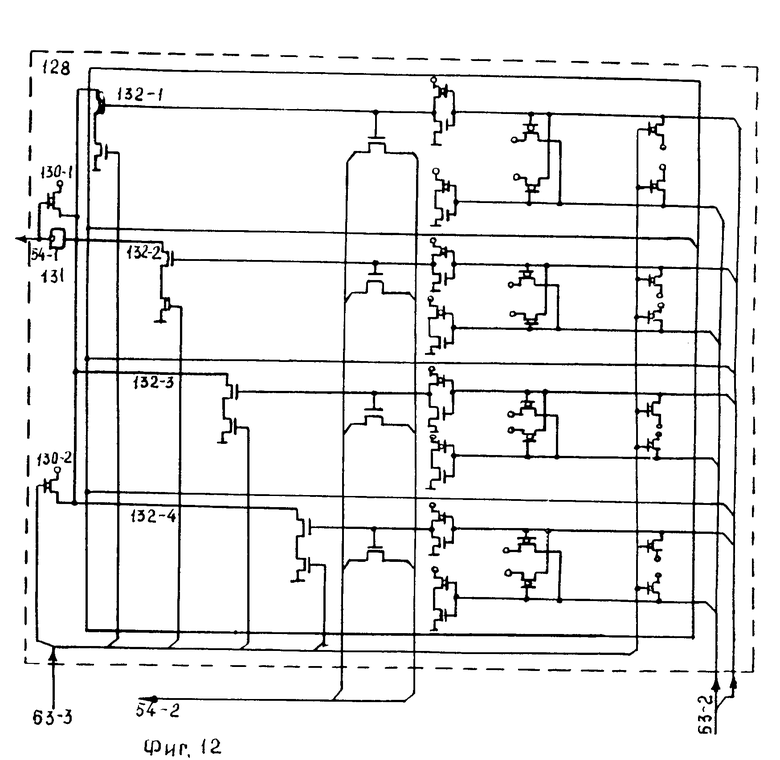

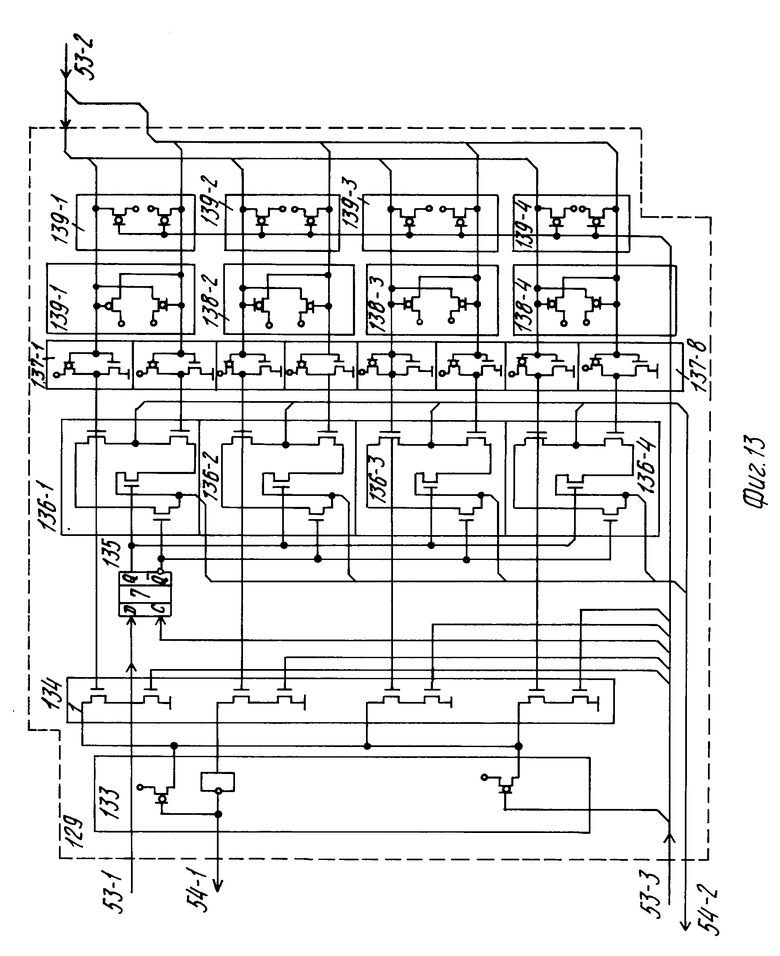

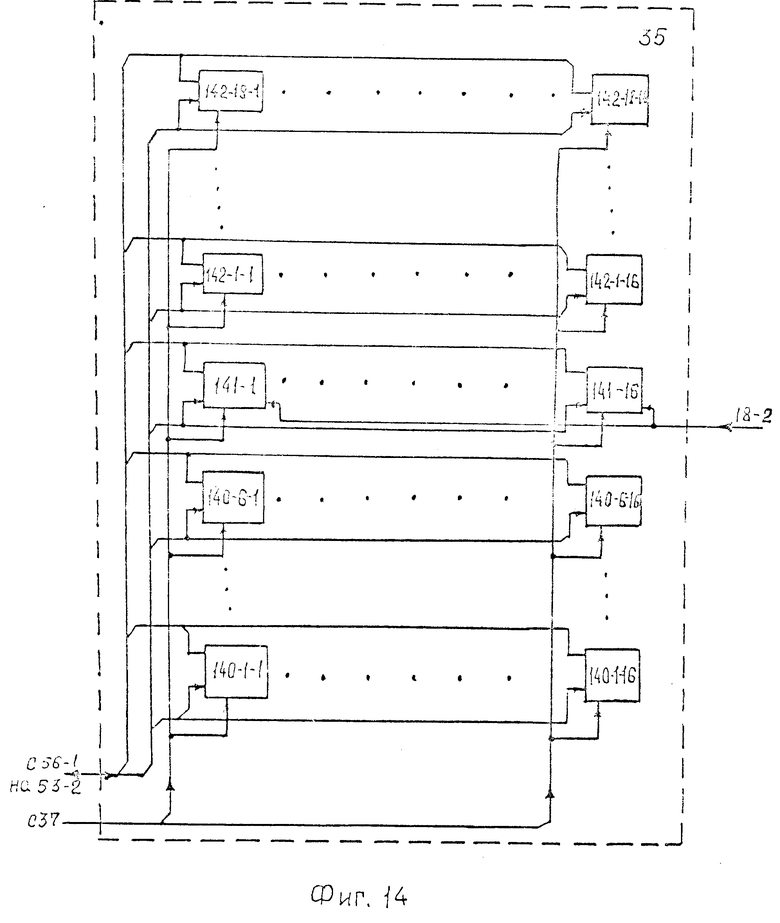

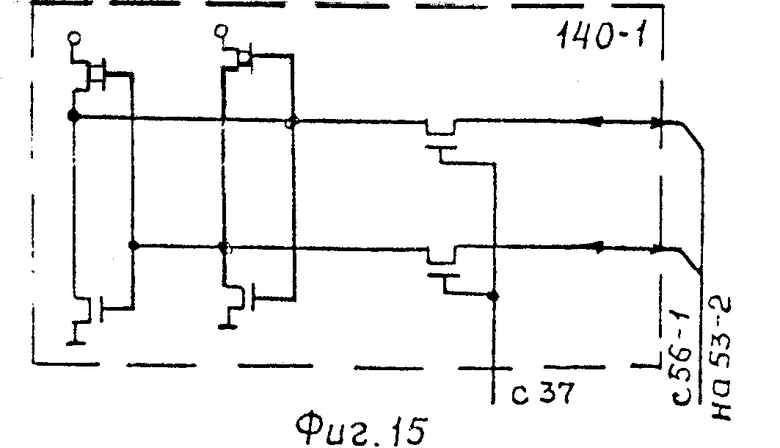

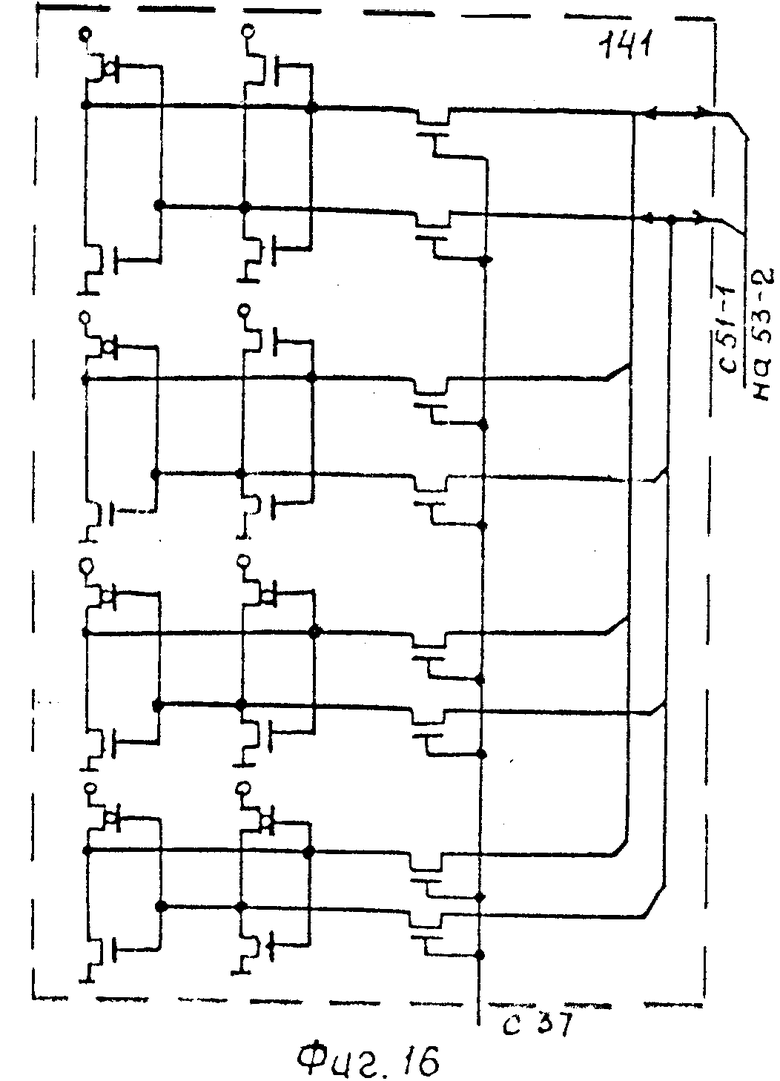

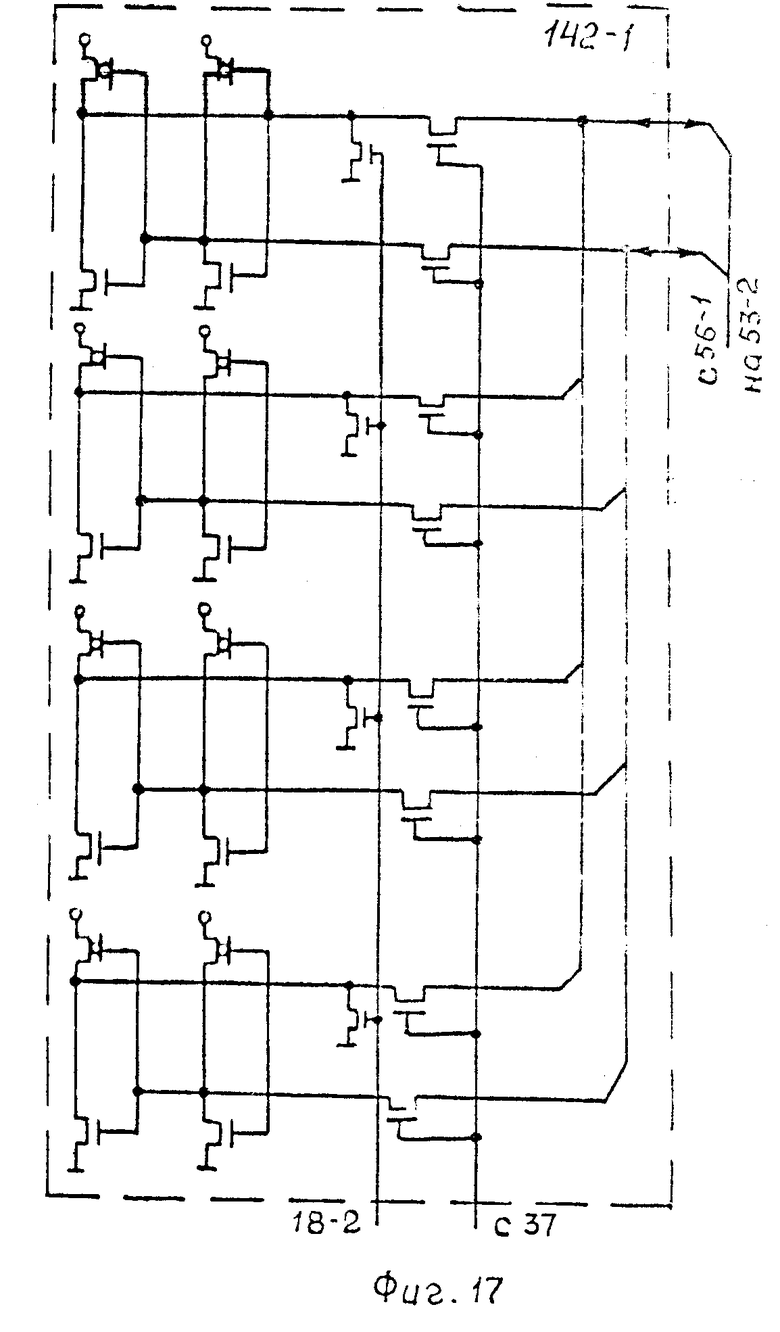

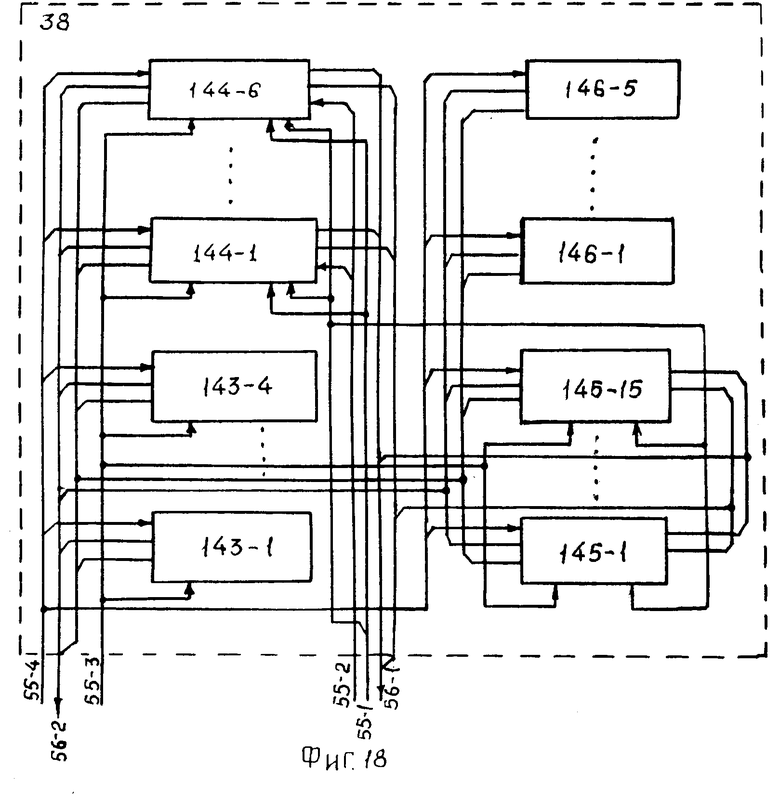

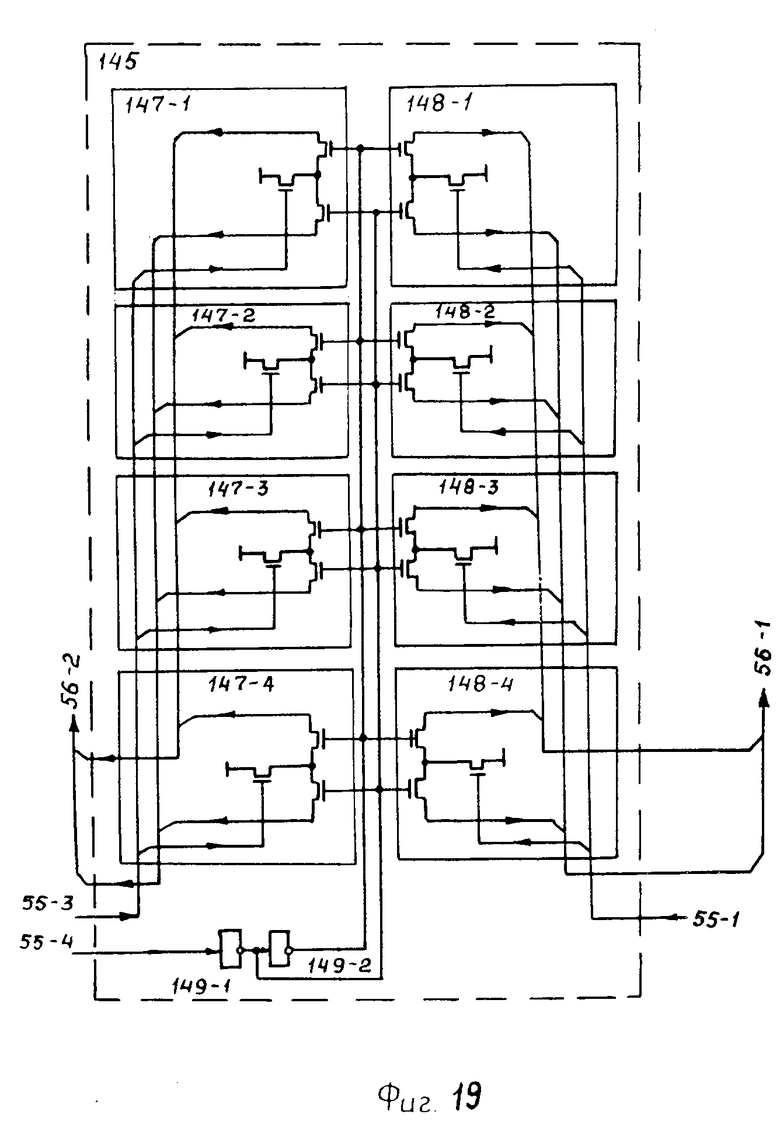

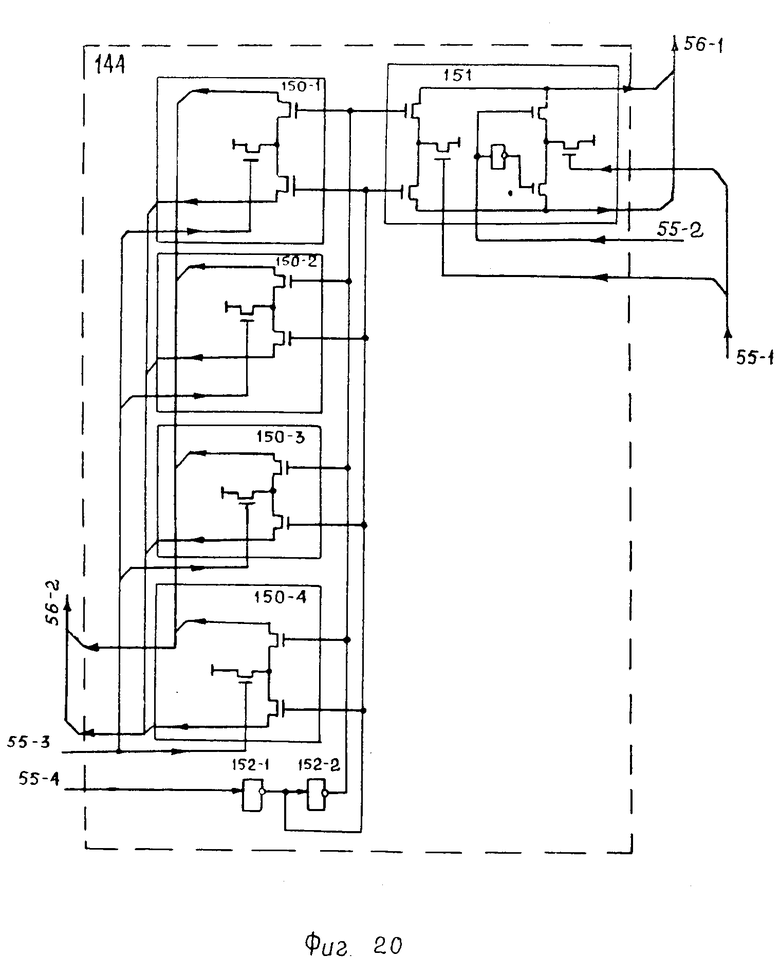

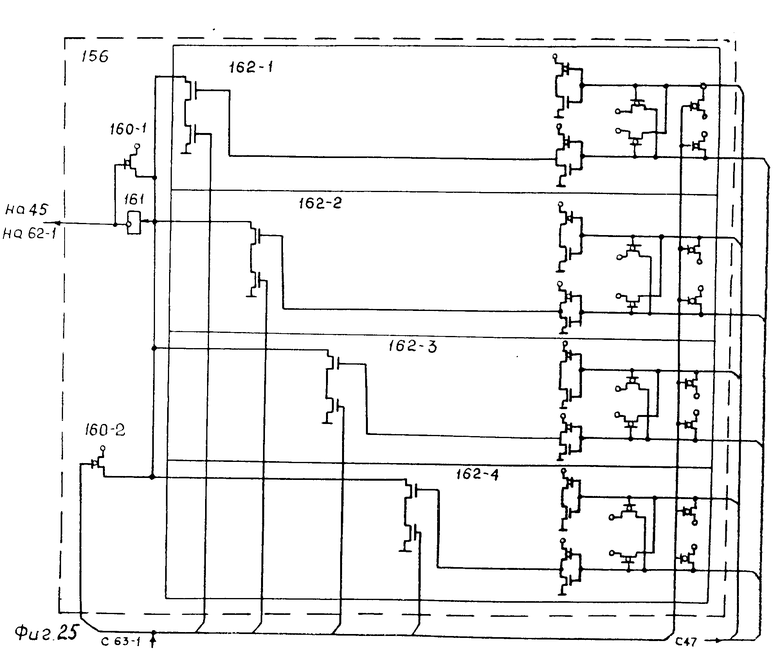

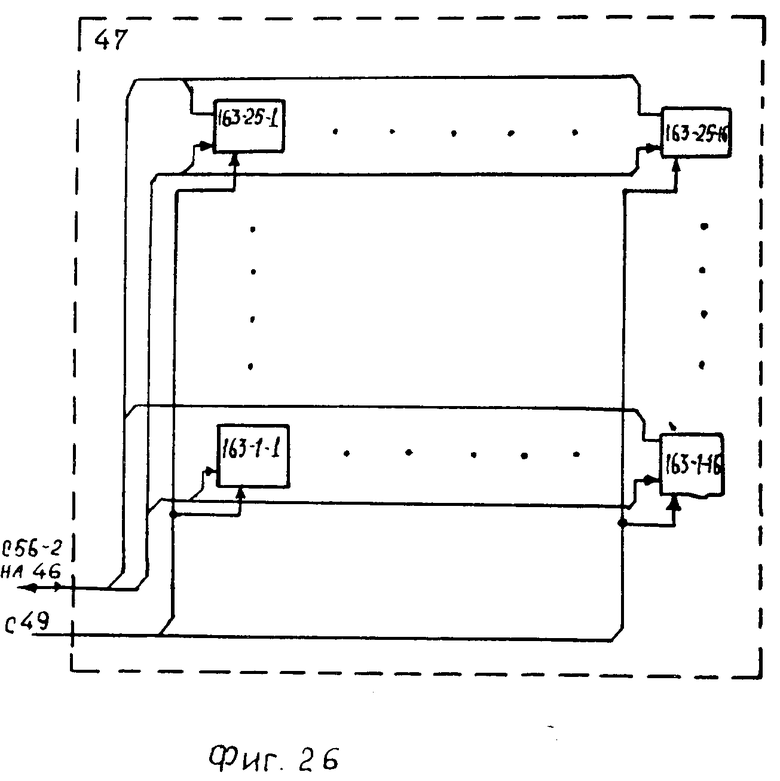

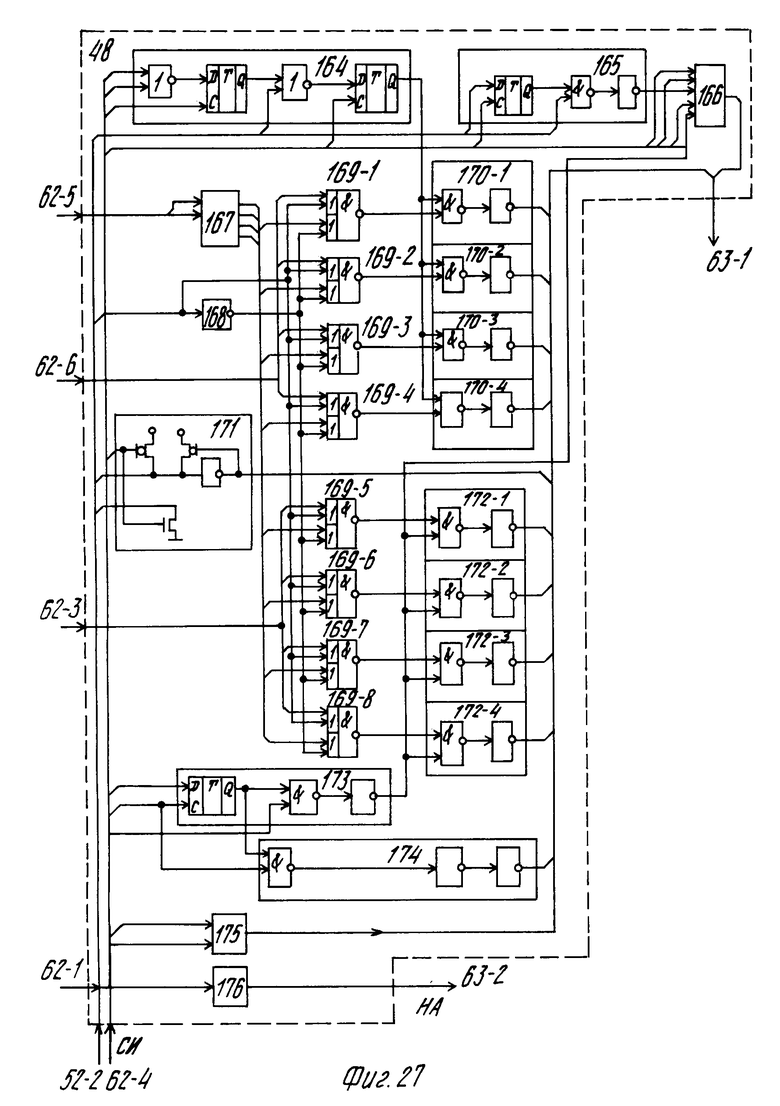

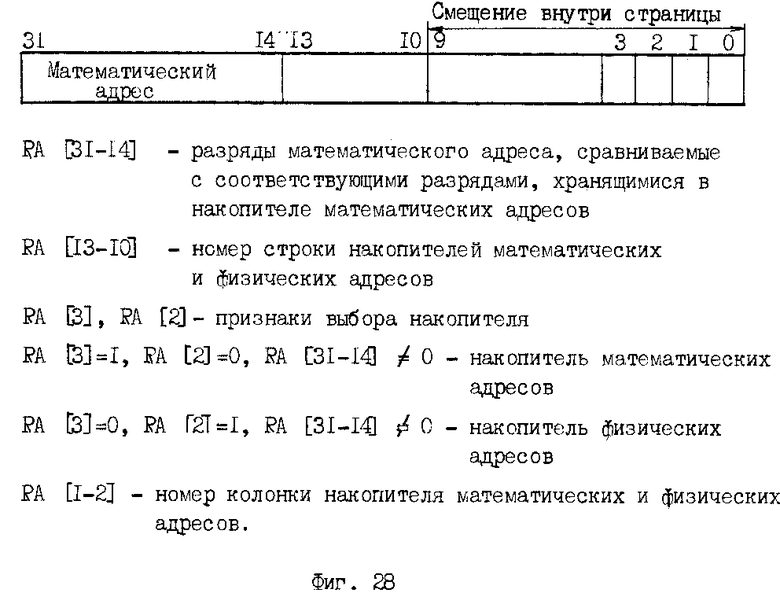

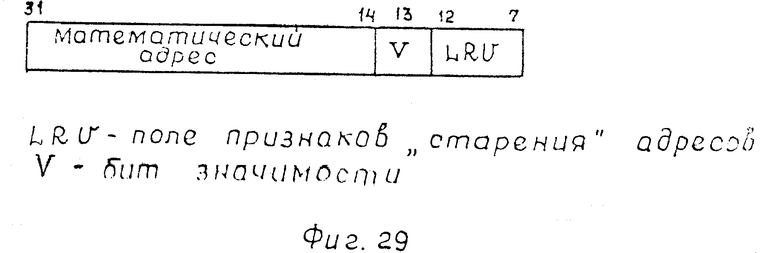

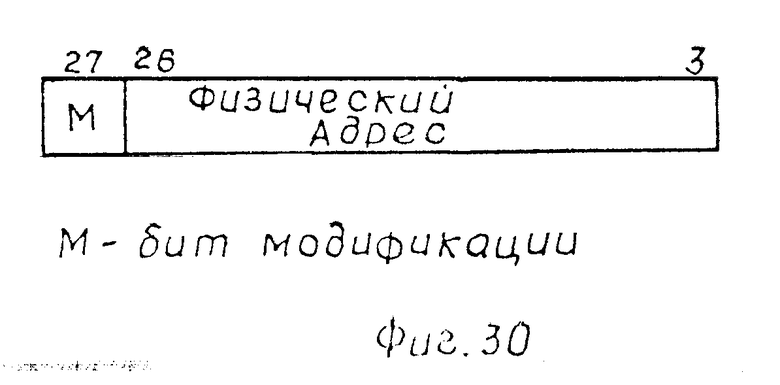

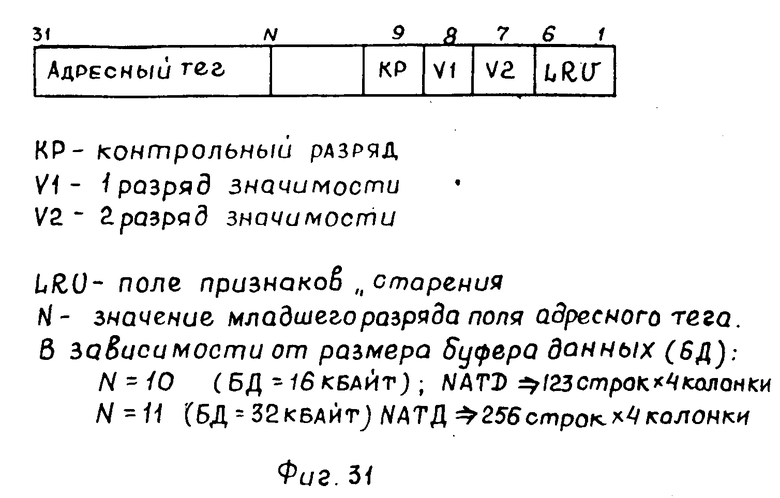

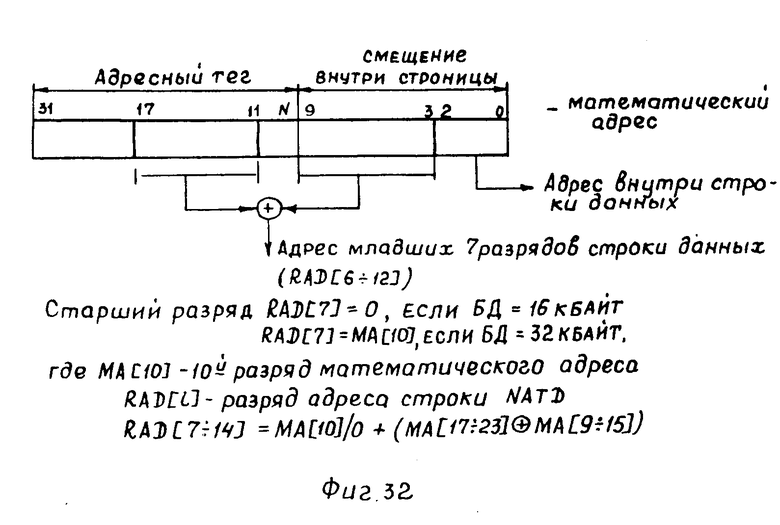

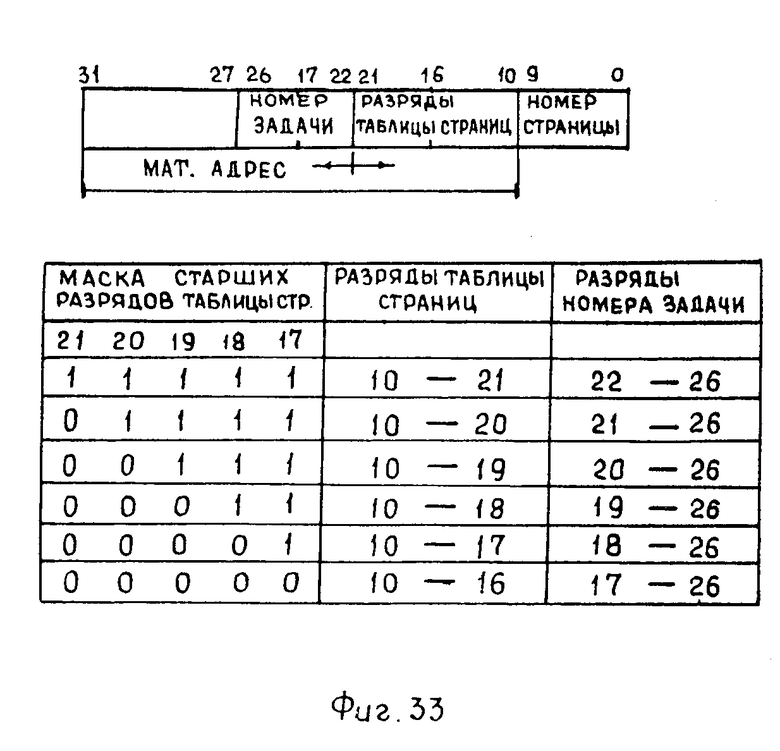

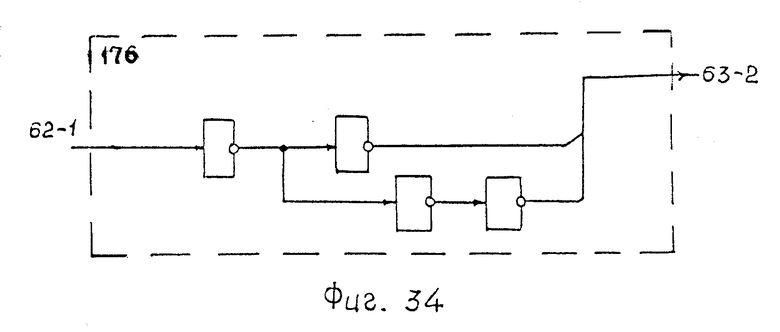

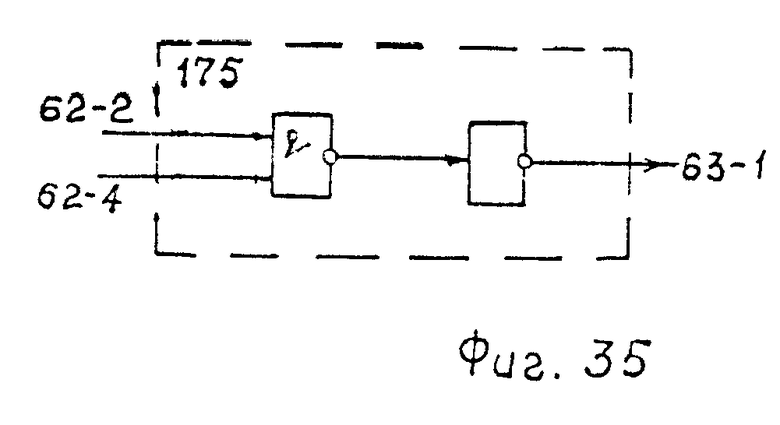

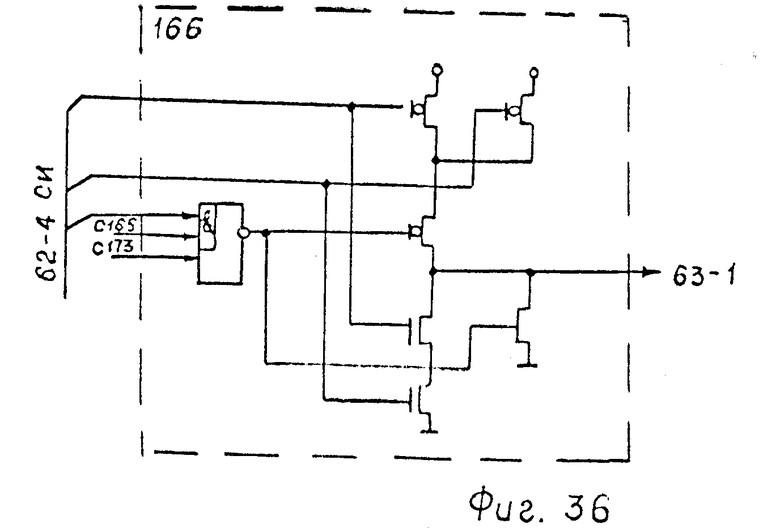

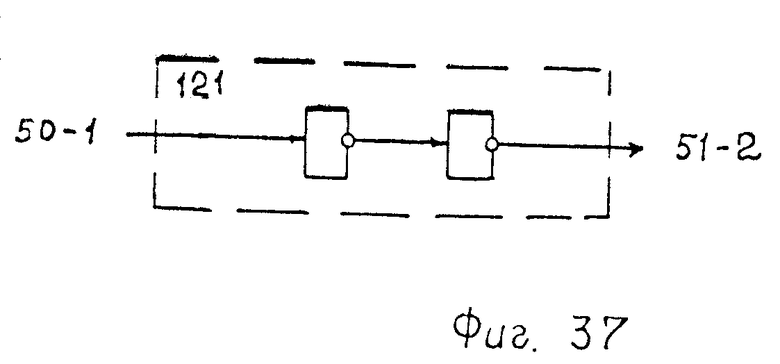

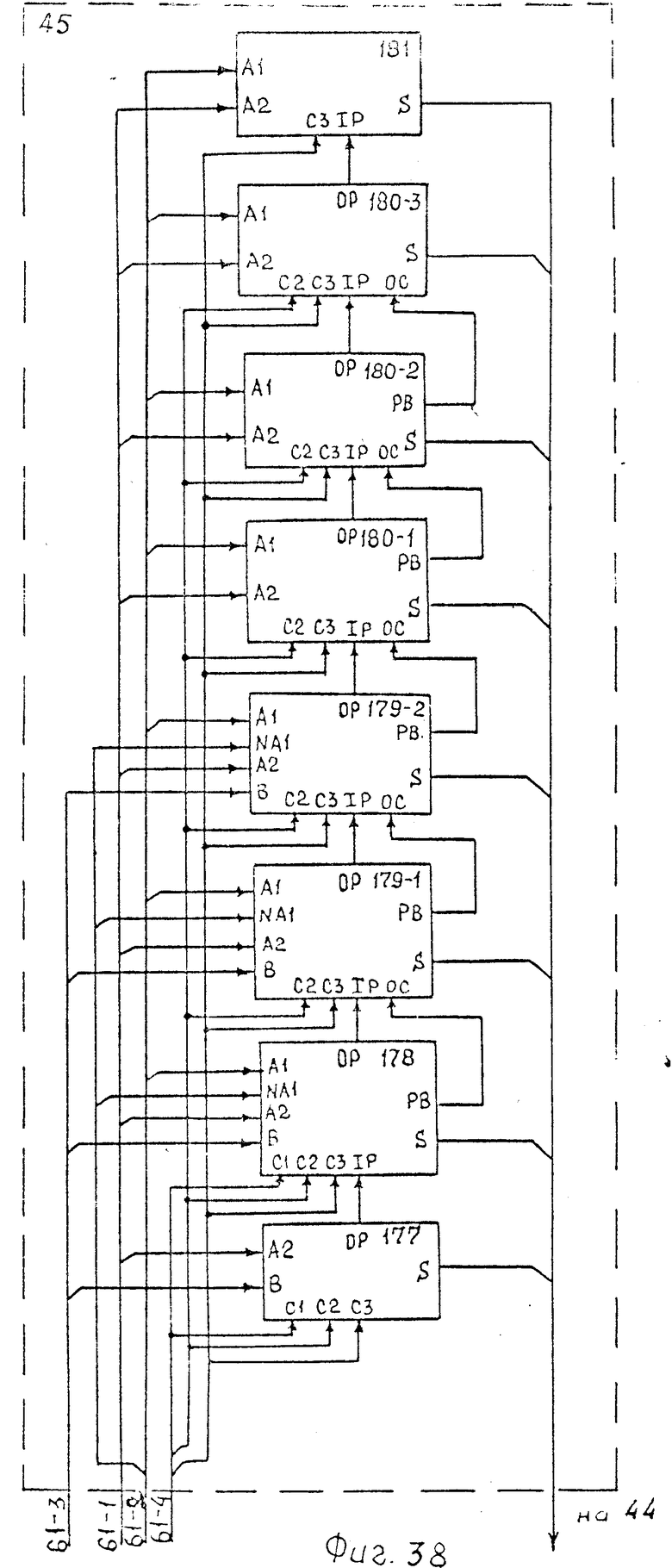

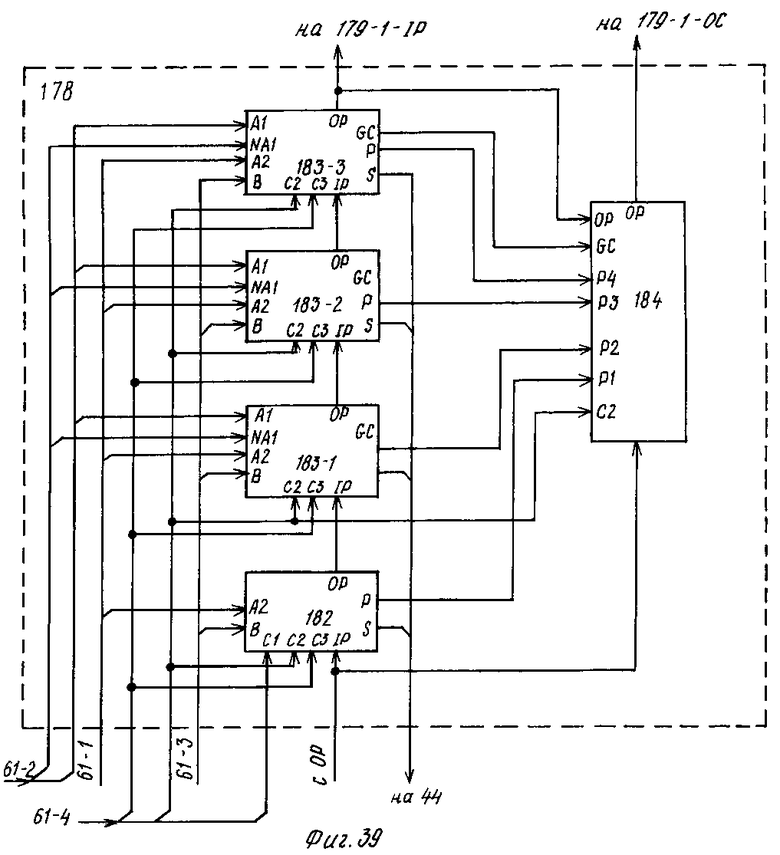

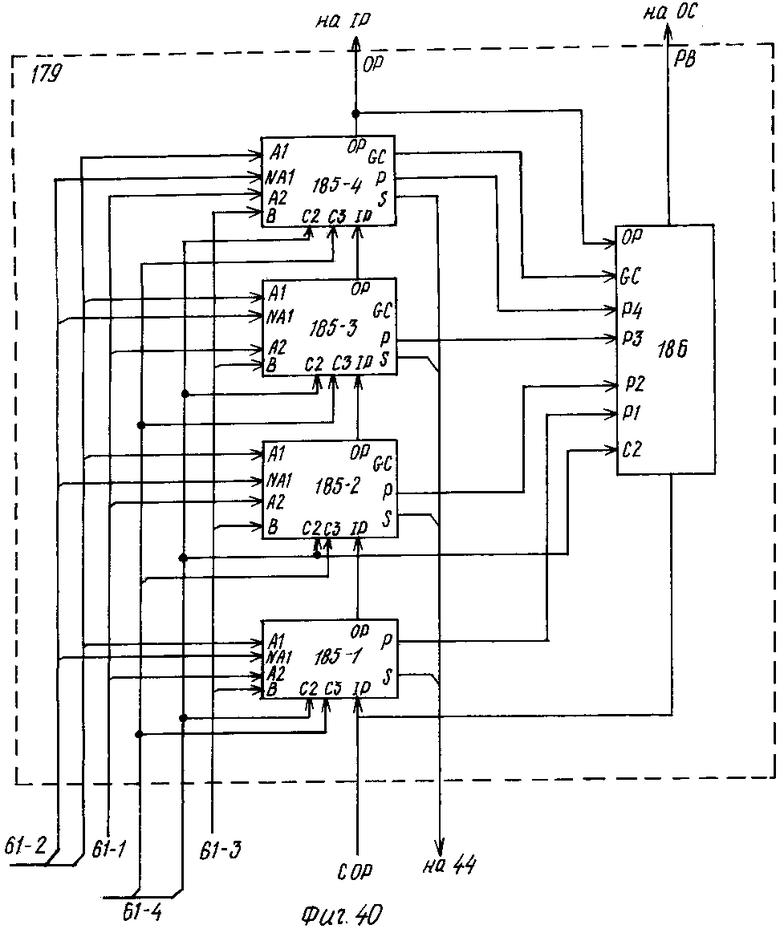

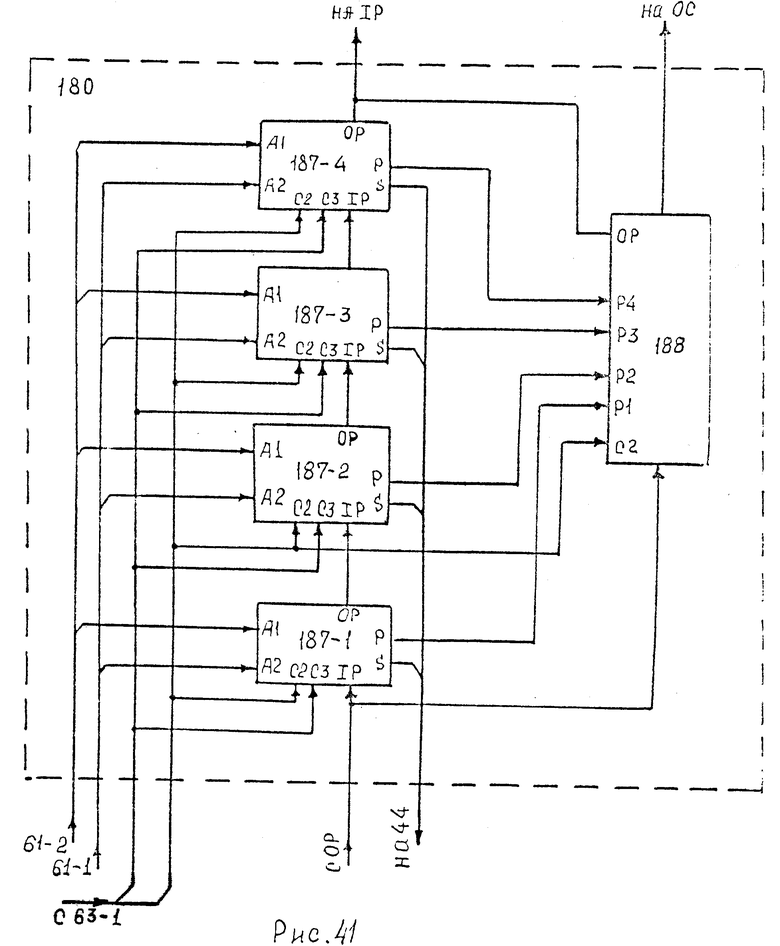

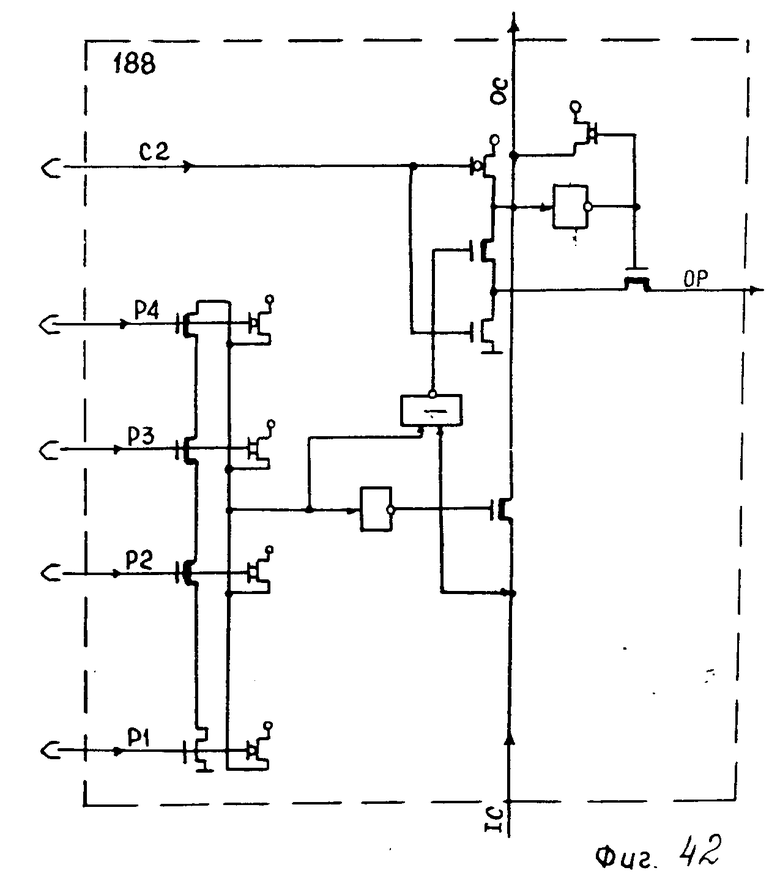

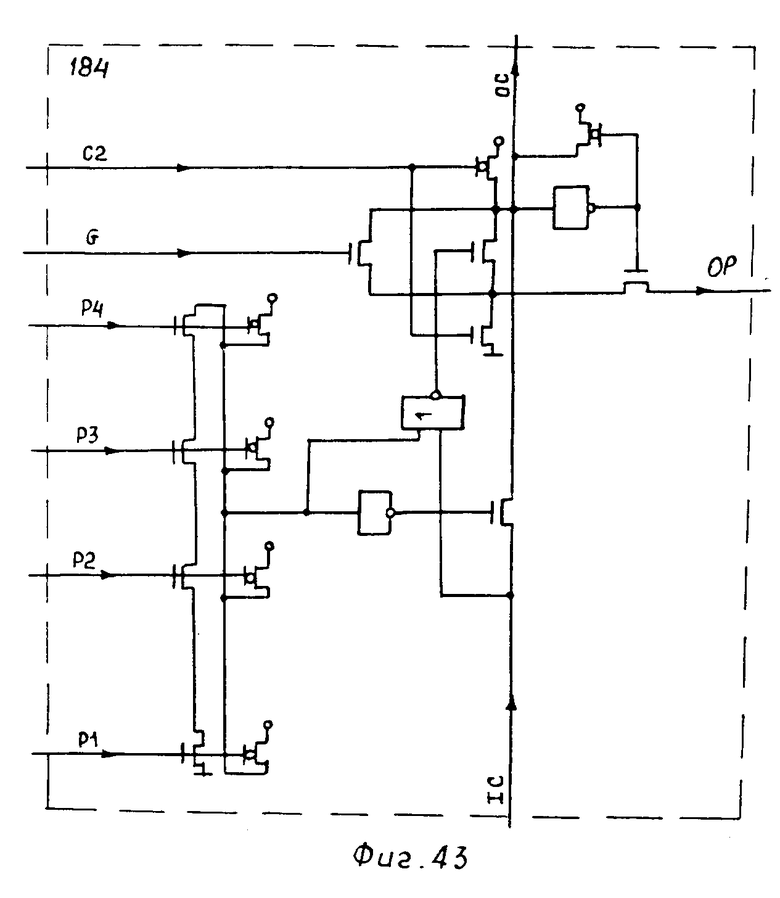

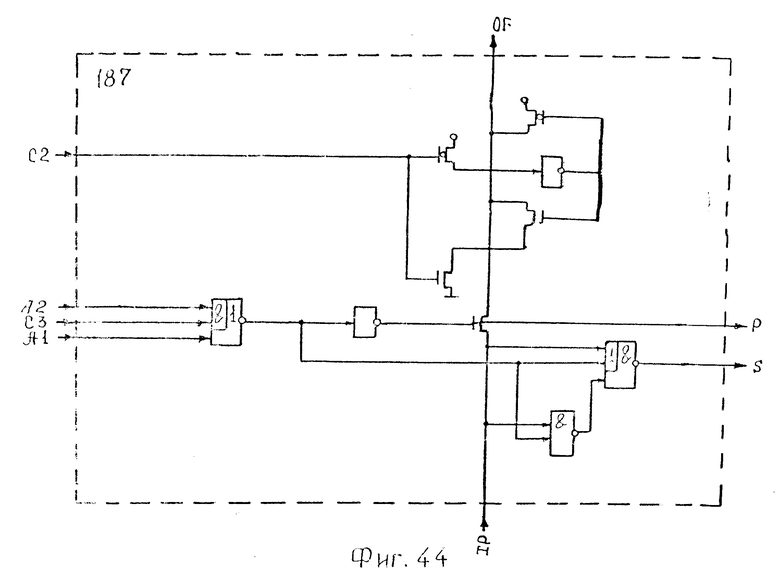

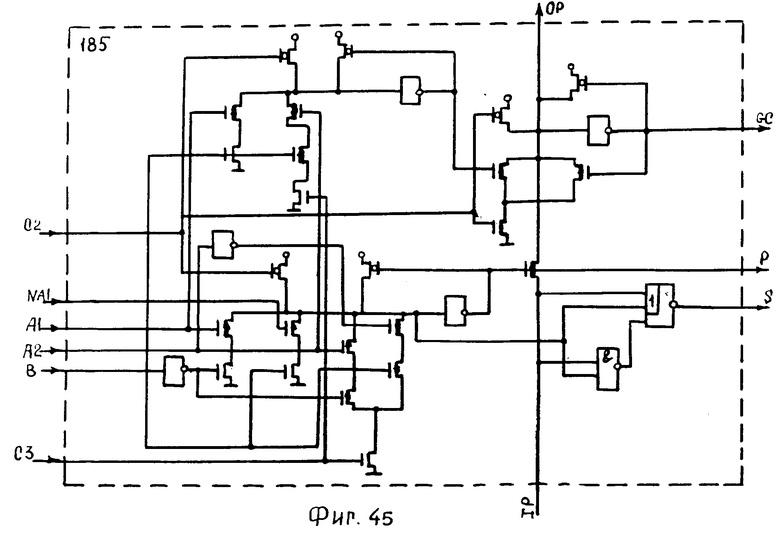

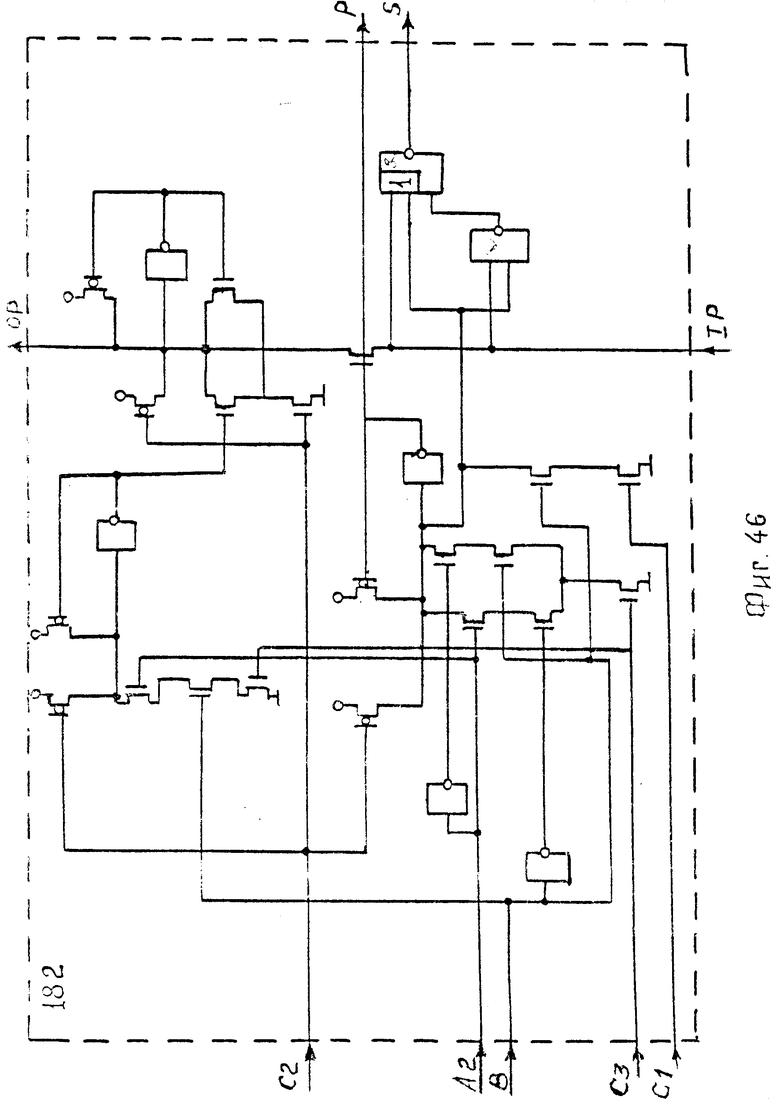

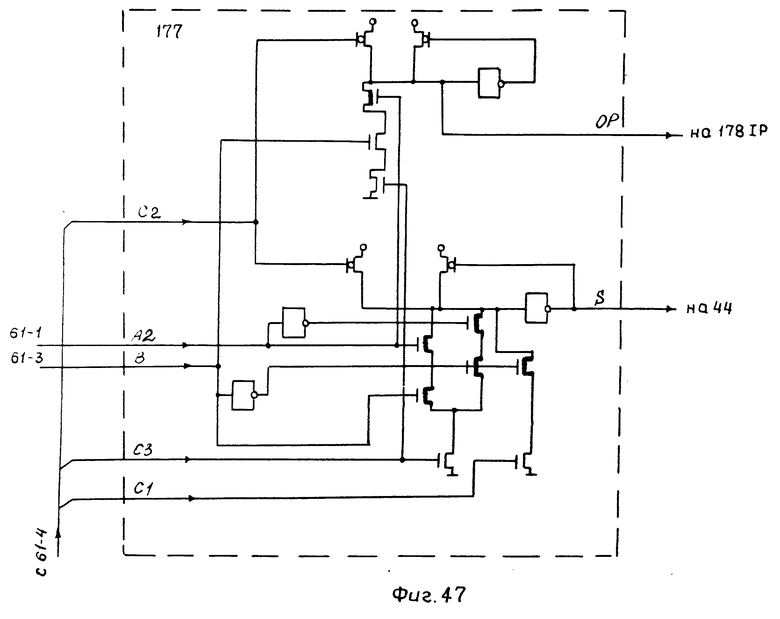

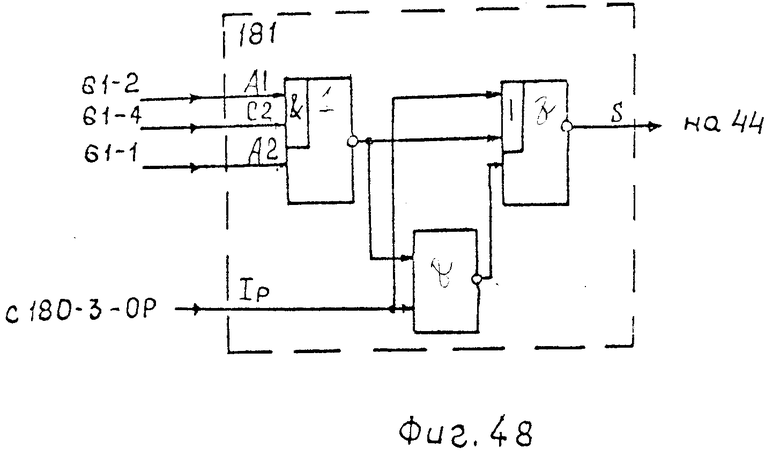

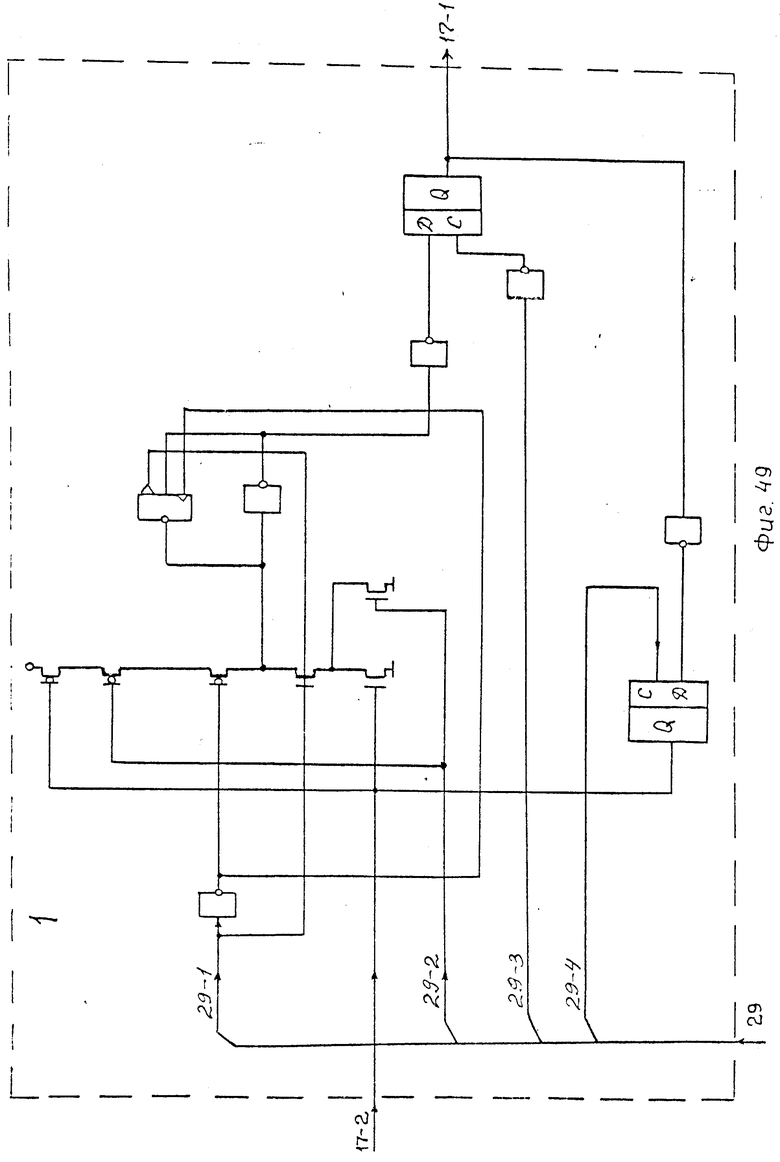

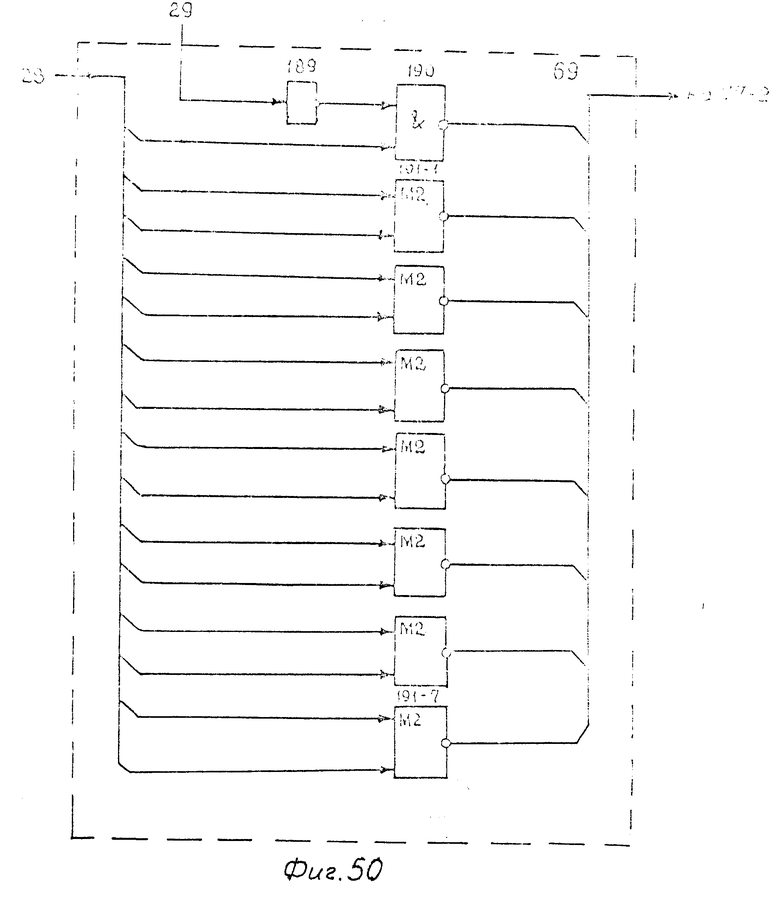

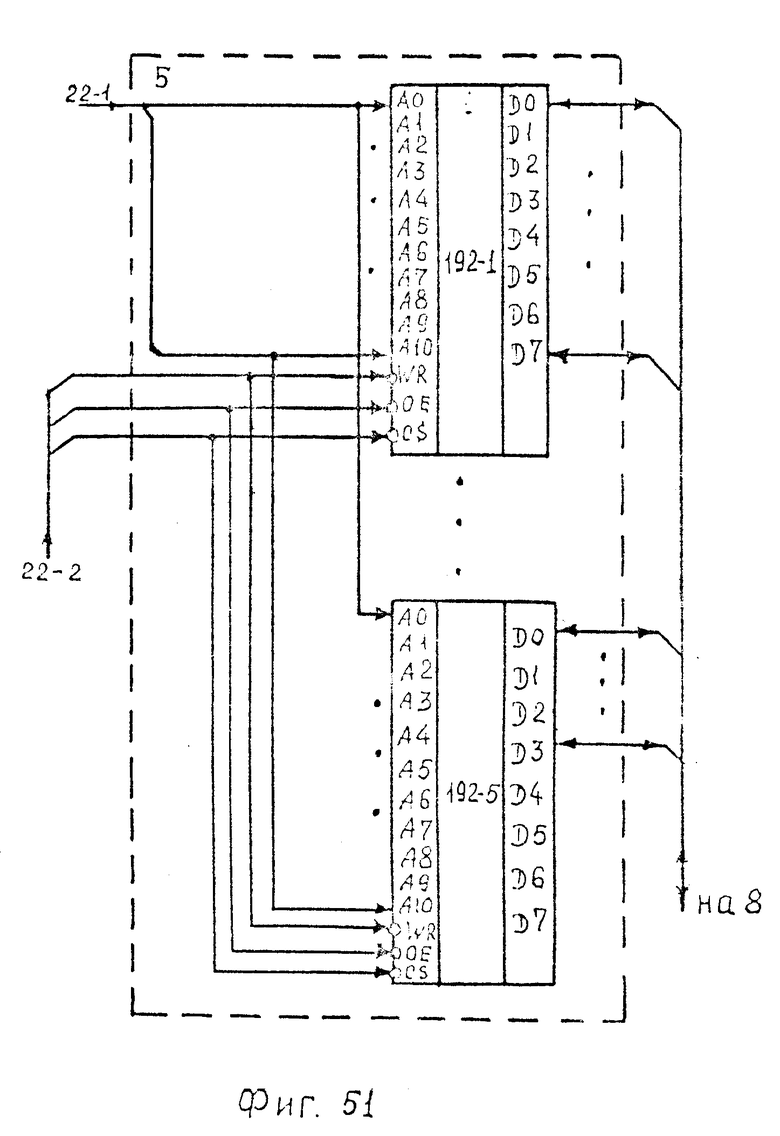

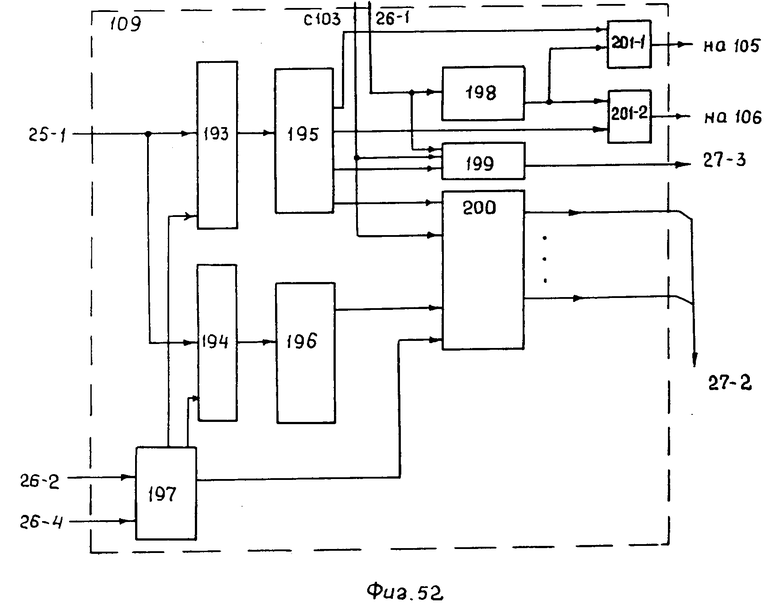

На фиг. 1 представлена блок-схема устройства управления памятью; на фиг. 2 - блок управления адресами данных; на фиг. 3 - блок управления адресными признаками данных; на фиг. 4 - блок управления буферной памятью данных; на фиг. 5 - блок центрального управления; на фиг. 6 - блок сопряжения с оперативной памятью; на фиг. 7 - первый блок управления; на фиг. 8 - электрическая схема первого шинного формирователя; на фиг. 9 - электрическая система блока старения и замещения; на фиг. 10 - блок считывания и сравнения; на фиг. 11 - электрическая схема узла считывания оного разряда признака приоритета; на фиг. 12 - электрическая схема узла считывания со сравнением бита значимости; на фиг. 13 - электрическая схема узла считывания и сравнения для одного разряда математического адреса; на фиг. 14 - накопитель математических адресов; на фиг. 15 - электрическая схема ячейки памяти признаков приоритета; на фиг. 16 электрическая схема ячейки памяти бита значимости; на фиг. 17 - электрическая схема ячейки памяти для старших разрядов математического адреса; на фиг. 18 - блок записи; на фиг. 19 - электрическая схема узла записи в накопители физических и математических адресов для одного разряда; на фиг. 20 - электрическая схема узла записи одного разряда поля признаков приоритета в накопитель математических адресов; на фиг. 21 - электрическая схема узла записи для одного разряда в накопитель физических адресов; на фиг. 22 - электрическая схема одного разряда первого мультиплексора; на фиг. 23 - блок считывания; на фиг. 24 - электрическая схема узла считывания оного разряда накопителя физических адресов с двумя противофазными выходами; на фиг. 25 - электрическая схема одного разряда узла считывания накопителя физических адресов; на фиг. 26 - накопитель физических адресов; на фиг. 27 - второй блок управления; на фиг. 28 - структура адреса обращения в накопитель математических или физических адресов; на фиг. 29 - строка накопителя математических адресов; на фиг. 30 - строка накопителя физических адресов; на фиг. 31 - строка накопителя адресных тегов данных; на фиг. 32 - формирование адреса обращения в накопитель адресных признаков данных; на фиг. 33 - структура математического адреса для режима без обнуления - бита; на фиг. 34 - электрическая схема формирователя сигналов признаков; на фиг. 35 - электрическая схема усилителя-формирователя управляющих сигналов; на фиг. 36 - электрическая схема формирователя временного сигнала выборки строки; на фиг. 37 - электрическая схема усилителя-формирователя; на фиг. 38 - сумматор; на фиг. 39 - четырехразрядная секция сумматора; на фиг. 40 - четырехразрядная секция сумматора для двух входных операндов с входным переносом; на фиг. 41 - четырехразрядная секция сумматора с одним операндом, с мультиплексором на входе операнда и с входным переносом; на фиг. 42 - электрическая схема четырехразрядной секции ускоренного переноса с генерацией переноса; на фиг. 43 - электрическая схема четырехразрядной екции ускоренного переноса; на фиг. 44 - одноразрядная секция сумматора с одним операндом с мультиплексором на входе первого операнда и с входным переносом; на фиг. 45 - электрическая схема одноразрядной секции сумматора для двух операндов; на фиг. 46 - электрическая схема одноразрядного сумматора двух входных операндов для младшего разряда; на фиг. 47 - электрическая схема одноразрядной секции сумматора; на фиг. 48 - электрическая схема одноразрядной секции сумматора с одним входным операндом и входным переносом; на фиг. 49 - электрическая схема одного разряда шинного формирователя; на фиг. 50 - электрическая схема блока сложения по модулю два; на фиг. 51 - электрическая схема буферной памяти данных; на фиг. 52 - узел управления блоком сопряжения с оперативной памятью.

На фиг. 4-52 показан пример реализации устройства управления памятью, выполненного на КМОП-транзисторах, с четырехколоночными накопителями математических и физических адресов и адресных тегов, с буферной памятью, состоящей из КМОП БИС с организацией 2Кх8, емкостью 16Кбайт, входящего в состав микропроцессорной системы.

Устройство управления памятью содержит шинный формирователь 1, блок 2 управления адресами данных, блок 3 управления адресными признаками данных, блок 4 управления буферной память данных, буферную память 5 данных, блок 6 центрального управления, блок 7 сопряжения с оперативной памятью, двухнаправленную информационную шину 8 адресов-данных, двухнаправленную адресно-информационную шину 9, вход 10 установки нуля, входную управляющую шину 11 строба адреса и строба данных, входную управляющую шину 12 "Готовность оперативной памяти", выходную управляющую шину 13 "Готовность данных", выходную управляющую шину 14 прерываний, выходную шину 15 команд, выходную шину 16.

Шинный формирователь 1 имеет первый и второй входы-выходы 17-1, 17-2 адресов-данных, управляющий вход.

Блок 2 управления адресами данных имеет вход-выход адресов-данных, управляющий вход 18-1, вход 18-2 установки нуля, вход 18-3 синхронизации, управляющий выход.

Блок 3 управления адресными признаками данных имеет вход-выход адресов-данных, управляющий вход, вход установки нуля, управляющий выход 19-1 признака готовности, адресный выход 19-2, контрольный выход 19-3.

Блок 4 управления буферной памятью данных имеет адресный вход 20-1, управляющий вход 20-2, вход 20-3 синхронизации, управляющий выход 21-1 признака готовности, управляющий выход 21-2, адресный выход 21-3.

Буферная память 5 данных имеет управляющий вход 22-1, адресный вход 22-2, вход-выход адресов-данных.

Блок 6 центрального управления имеет вход-выход адресов-данных, вход 23-1 строба адреса и строба данных, вход 23-2 синхронизации, управляющий вход 23-3 признаков готовности, управляющий вход 23-4, контрольный вход 23-5, выход 24-1 готовности данных, управляющий выход 24-2, выход 24-3 строба адреса и строба данных, управляющий выход 24-4 прерываний.

Блок 7 сопряжения с оперативной памятью имеет вход-выход 25-1 адресов-данных, адресно-информационный вход-выход 25-2, управляющий вход 26-1 "Готовность оперативной памяти", вход 26-2 строба адреса и строба данных, вход 26-3 установки нуля, командный выход 27-1, управляющий выход 27-2 "Пуск оперативной памяти", управляющий выход 27-3 признаков готовности.

В устройстве имеются двухнаправленная локальная шина 28 адресов-данных, управляющая шина 29, управляющая шина 30 признаков готовности.

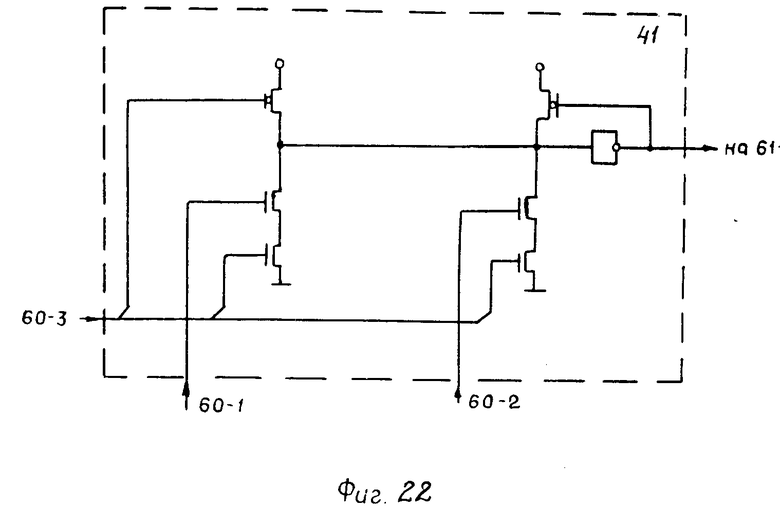

Блок управления адресами данных содержит (фиг. 2) первый блок 31 управления, первый шинный формирователь 32, блок 33 старения и замещения, блок 34 считывания и сравнения, накопитель 35 математических адресов, регистр 36 адреса, первый дешифратор 37 строк, блок 38 записи, два регистра 39, 40, первый мултиплексор 41, блок 42 элементов И, второй мультиплексор 43, второй шинный формирователь 44, сумматор 45, блок 46 считывания, накопитель 47 физических адресов, второй блок 48 управления, второй дешифратор 49 строк. Первый блок 31 управления имеет управляющий вход 50-1, адресный вход 50-2, вход 50-3 синхронизации, вход 50-4 управления выборкой колонки, вход 50-5 признаков сравнения, адресный вход 50-6, первый и второй управляющие входы 51-1 и 51-2, выход 51-3 признаков сравнения. Шинный формирователь 32 имеет вход адресов-данных, управляющий вход, выход адресов-данных. Блок 33 старения и замещения имеет вход 52-1 данных, вход 52-2 признаков сравнения, управляющий вход 52-3, управляющий выход, выход данных. Блок 34 считывания и сравнения имеет первый и второй входы 53-1 и 53-2 адресов-данных, управляющий вход 53-3, выход 54-1 адресов-данных, выход 54-2 признаков сравнения. Накопитель 35 математических адресов имеет адресный вход выборки строки, вход установки нуля, вход-выход адресов-данных. Регистр 36 адреса имеет адресный вход, управляющий выход, выход. Первый дешифратор 37 строк имеет адресный вход, управляющий вход, адресный выход выборки строки. Блок 38 записи имеет первый управляющий вход 55-1, вход 55-2 данных, второй управляющий вход 55-3, вход 55-4 адресов-данных, первый и второй выходы 56-1 и 56-2 адресов-данных. Первый регистр 39 имеет вход адресов-данных, управляющий вход, выход. Второй регистр 40 имеет вход адресов-данных, управляющий вход, выход. Первый мультиплексор 41 имеет первый и второй входы 57-1 и 57-2 адресов-данных, управляющий вход 57-3, выход 58-1 адресов-данных, выход 58-2 данных. Блок 42 элементов И имеет первый и второй адресные входы 59-1 и 59-2, выход. Второй мультиплексор 43 имеет вход 60-1 адресов-данных, адресный вход 60-2, упргавляющий вход 60-3, адресный выход. Шинный формирователь 44 имеет вход адресов-данных, управляющий вход, выход адресов-данных. Сумматор 45 имеет первый и второй выходы 61-1 и 61-2 адресов-данных, адресный вход 61-3, управляющий вход 61-4, выход адресов-данных. Блок 46 считывания имеет вход адресов-данных, управляющий вход, выход адресов-данных. Блок 46 считывания имеет вход адресов-данных, управляющий вход, выход адресов-данных. Накопитель 47 физических адресов имеет адресный вход выборки строки, вход-выход адресов-данных. Второй блок 48 управления имеет вход 62-1 данных, управляющий вход 62-2, вход 62-3 управления выборкой колонки, вход 62-4 синхронизации, адресный вход 62-5, вход 62-6 признаков сравнения, первый и второй управляющие выходы 63-1 и 63-2. Второй дешифратор 49 имеет адресный вход, управляющий вход, адресный выход выборки строки.

Блок управления адресными признаками данных содержит (фиг. 3) регистр 64 данных, блок 65 считывания-записи и сравнения, узел 66 контроля, накопитель 67, блок 68 замещения, блок 69 сложения по модулю два, регистр 70 адреса, дешифратор 71 номера колонки, дешифратор 72 номера строки, узел 73 управления. Регистр 64 данных имеет вход данных, управляющий вход, выход данных. Блок 65 считывания-записи и сравнения имеет вход-выход данных, вход 74-1 данных, адресный вход 74-2 выборки номера колонки, управляющий вход 74-3, выход 75-1 признаков сравнения, выход 75-2 данных, контрольный выход 75-3, выход 75-4 признаков готовности, информационный выход 75-5. Узел 66 контроля имеет вход данных, контрольный вход, выход. Накопитель 67 имеет вход-выход данных, вход установки нуля, адресный вход выборки номера строки. Блок 68 замещения имеет вход 76-1 признаков сравнения, информационный вход 76-2, управляющий вход 76-3, адресный выход. Блок 69 сложения по модулю два имеет адресный вход, управляющий вход, выход. Регистр 70 адреса имеет первый и второй адресные входы 77-1 и 77-2, управляющий вход 77-3, выход. Дешифратор 71 номера колонки имеет первый и второй адресные входы 78-1 и 78-2, управляющий вход 78-3, адресный выход выборки номера колонки. Дешифратор 72 номера строки имеет адресный вход, управляющий вход, адресный выход выборки строки. Узел 73 управления имеет вход синхронизации, управляющий вход, выход. В блоке имеются локальная шина 79 адресов-данных, управляющая шина 80.

Блок управления буферной памятью данных содержит (фиг. 4) два элемента И-НЕ 81-1, 81-2, элемент 3И 82, элемент НЕ 83, счетчик 84, два регистра 85-1, 85-2, два элемента 2И-ИЛИ-НЕ 86-1, 86-2, триггер 87, три элемента 2-2И-ИЛИ-НЕ 88-1, 88-2, 88-3, элемент 89, девять формирователей 90-1 - 90-9.

Блок центрального управления содержит (фиг. 5) входной регистр 91, регистр 92 команд, регистр 93 адреса, два регистра 94-1, 94-2 состояния, дешифратор 95 команд, дешифратор 96 адреса, два шинных формирователя 97-1, 97-2, шифратор 98 состояний, пять шифраторов 99-1 - 99-5, два выходных регистра 100-1, 100-2, семь формирователей 101-1 - 101-7.

Блок сопряжения с оперативной памятью содержит (фиг. 6) входной регистр 102, узел 103 контроля по четности, регистр 104 записи, усилитель 105 шины адресов-данных, усилитель-формирователь 106 шины команд, выходной регистр 107, регистр 108 чтения данных-команд, узел 109 управления.

Первый блок управления содержит (фиг. 7) дешифратор 110 выбора номера колонки, два элемента НЕ 111-1, 111-2, двухвходовой мультиплексор 112 номера колонки, узел 113 временного стробирования выбранной колонки, усилитель-формирователь 114 сигналов чтения колонки, четыре формирователя 115-1 - 115-4 сигналов сравнения математических адресов, первый формирователь 116 управляющего сигнала, первый формирователь 117 признаков сравнения, усилитель-формирователь 118 сигналов записи колонки, второй и третий усилители-формирователи 119 и 120 управляющих сигналов, второй формирователь 121 признаков сравнения.

Первый шинный формирователь содержит (фиг. 8) тридцать два разряда усилителей-формирователей 122-1 - 122-32.

Блок старения и замещения содержит (фиг. 9) узел 123 формирования признаков приоритета строки, регистр 124 хранения признаков, узел 125 формирования номера замещаемой колонки, регистр 126 хранения номера замещаемой колонки.

Блок считывания и сравнения содержит (фиг. 10) шесть узлов 127-1 - 127-6 считывания разрядов признаков приоритета, узел 128 считывания со сравнением бита значимости, восемнадцать узлов 129-1 - 129-18 считывания и сравнения разрядов математического адреса.

Узел считывания со сравнением бита значимости признаков содержит (фиг. 12) два КМОП-транзистора 130-1, 130-2 р-типа, элемент НЕ 131, четыре ячейки 132-1 - 132-4 считывания и сравнения разрядов математических адресов.

Ячейка считывания и сравнения разрядов математических адресов содержит (фиг. 13) динамический элемент 133 управления выходной информацией, четырехвходовой коммутатор 134 выбранной колонки, разряд регистра 135 адреса, четыре элемента 136-1 - 136-4 сложения по модулю два, восемь инверторов 137-1 - 137-8 усиления информации для считываемого разряда, четыре элемента 138-1 - 138-4 восстановления, четыре элемента 139-1 - 139-4 управления состоянием колонки.

Накопитель математических адресов содержит (фиг. 14) шестнадцать вертикальных строк, каждая из которых состоит из шести ячеек 140-1 - 140-6 признаков приоритетов, ячейки 141 бита значимости, восемнадцати ячеек 142-1 - 142-18 старших разрядов математического адреса.

Блок записи содержит (фиг. 18) четыре узла 143-1 - 143-4 записи в накопитель физических адресов, шесть узлов 144-1 - 144-6 записи поля признаков приоритета в накопитель математических адресов, пятнадцать узлов 145-1 - 145-15 записи в накопители физических и математических адресов, пять узлов 146-1 - 146-5 записи в накопитель математических адресов.

Узел записи в накопители физических и математических адресов содержит (фиг. 19) четыре элемента 147-1 - 147-4 записи в накопитель физических адресов, четыре элемента 148-1 - 148-4 записи в накопитель математических адресов, два элемента НЕ 149-1, 149-2.

Узел записи для одного разряда поля признаков приоритета в накопитель математических адресов содержит (фиг. 20) четыре элемента 150-1 - 150-4 записи в накопитель физических адресов, элемент 151 записи в разряд признака приоритета, два элемента НЕ 152-1, 152-2.

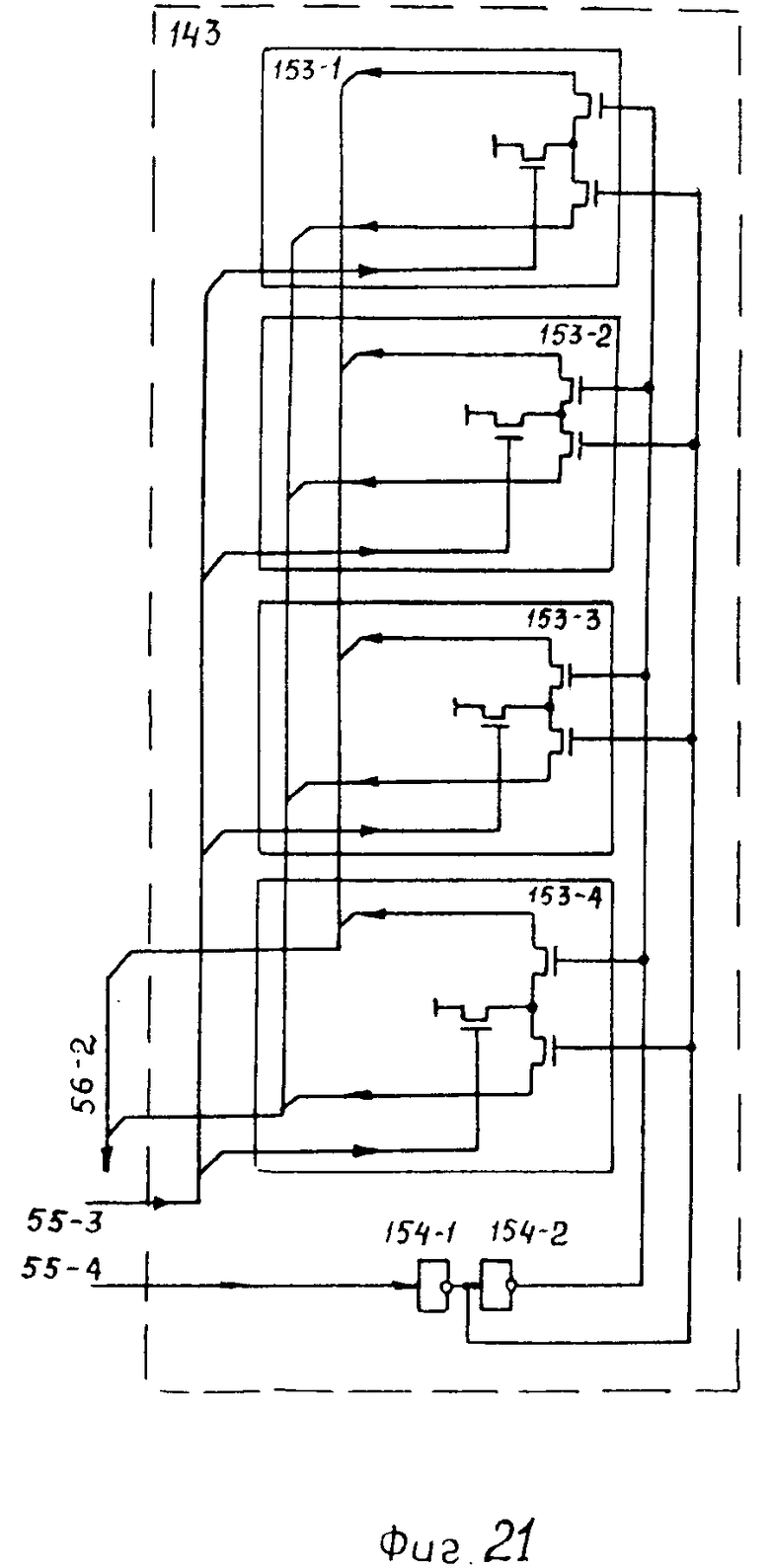

Узел записи для одного разряда в накопитель физических адресов содержит (фиг. 21) четыре элемента 153-1 - 153-4 записи в накопитель физических адресов, два элемента НЕ 154-1, 154-2.

Узел записи для одного разряда в накопитель математических адресов выполнен так же, как узел записи в накопитель физических адресов.

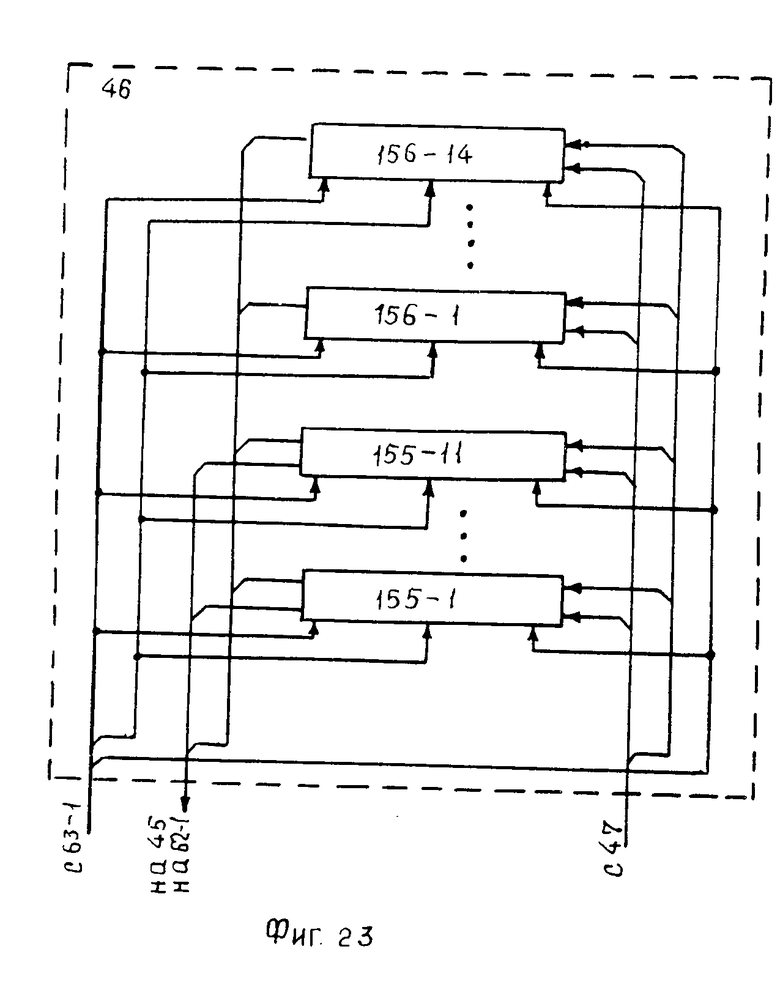

Блок считывания содержит одиннадцать узлов 155-1 - 155-11 считывания разрядов накопителя физических адресов в прямом коде, четырнадцать узлов 156-1 - 156-14 считывания разрядов накопителя физических адресов в прямом и обратном коде.

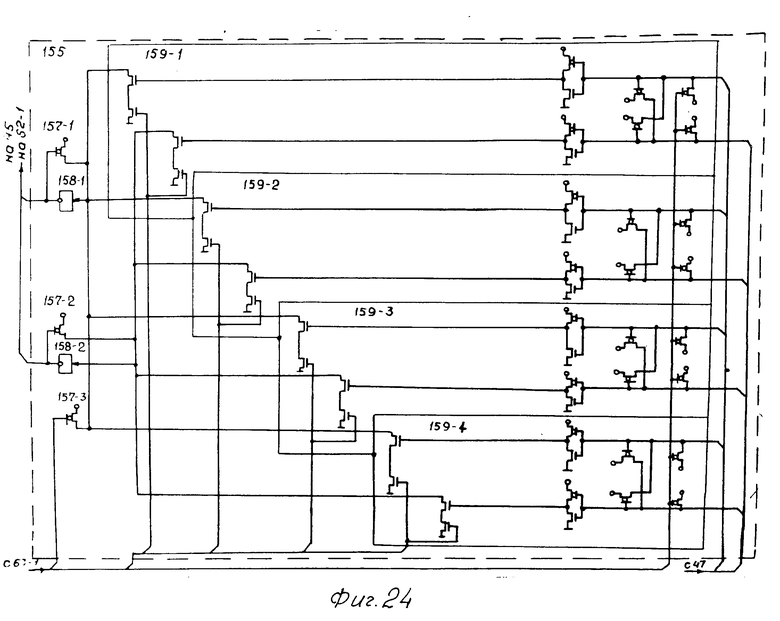

Узел считывания одного разряда накопителя физических адресов в прямом и обратном коде содержит (фиг. 24) три КМОП-транзистора 157-1 - 157-3, два элемента НЕ 158-1, 158-2, четыре элемента 159-1 - 159-4 считывания разрядов.

Узел считывания разрядов накопителя физических адресов в прямом коде содержит (фиг. 25) два КМОП-транзистора 160-1, 160-2, элемент НЕ 161, четыре элемента 162-1 - 162-4 считывания разрядов.

Накопитель физических адресов содержит (фиг. 26) шестнадцать вертикальных строк, каждая из которых состоит из двадцати пяти ячеек 163-1 - 163-25 памяти.

Второй блок управления содержит (фиг. 27) формирователь 164 сигнала считывания колонок, формирователь 165 временного сигнала чтения накопителя, формирователь 166 временного сигнала выборки строки, дешифратор 167, восемь мультиплексоров 169-1 - 169-8, четыре усилителя-формирователя 170-1 - 170-4 считывания колонок накопителя, формирователь 171 признака адреса, четыре усилителя-формирователя 172-1 - 172-4 записи колонок накопителя, формирователь 173 временного сигнала управления записью в колонки, формирователь 174 временного сигнала чтения колонок, узел 175 формирователей-усилителей управляющих сигналов, узел 176 формирователей сигналов признаков.

Суматор содержит (фиг. 38) одноразрядную секцию 177 сумматора, четырехразрядную секцию 178, две четырехразрядные секции 179-1, 179-2 сумматора для двух операндов с входным переносом, три четырехразрядные секции 180-1 - 180-3 сумматора с одним входным операндом, входным переносом и мультиплексором на входе, одноразрядную секцию 181 сумматора с одним входным операндом и входным переносом.

Четырехразрядная секция сумматора содержит (фиг. 39) одноразрядный сумматор 182 младшего разряда для двух входных операндов, три одноразрядных сумматора 183-1 - 183-3 с мультиплексированием для первого операнда и входным переносом, секцию 184 ускореннго переноса для четырех разрядов.

Четырехразрядная секция сумматора для двух операндов с входным переносом содержит (фиг. 40) четыре одноразрядные секции 185-1 - 185-4 сумматора для двух операндов, четырехразрядную секцию 186 сквозного переноса.

Четырехразрядная секция сумматора с одним операндом, входным переносом и мультиплексором на входе содержит (фиг. 41) четыре одноразрядные секции 187-1 - 187-4 сумматора с одним входным операндом, входным переносом и мультиплексором на входе, четырехразрядную секцию 188 ускоренного переноса.

Один разряд шинного формирователя имеет два входа-выхода адресов-данных 17-1, 17-2, управляющий вход, соединенный с управляющей шиной 29, причем по шине 29-1 поступают сигналы управления записью из локальной шины, по шины, по шине 29-2 - сигнал управления считыванием из локальной шины, по шине 29-3 - сигнал управления формирователем выдачи в шину адресов-данных, по шине 29-4 - сигнал управления выдачей в локальную шину.

Блок сложения по модулю два содержит (фиг. 50) элемент НЕ 189, элемент И-НЕ 190, семь элементов 191-1 - 191-7 сложения по модулю два.

Буферная память данных содержит (фиг. 51) пять элементов 192-1 - 192-5 памяти.

Узел управления блоком сопряжения с оперативной памятью содержит регистр 193 команд, регистр 194 адреса, дешифратор 195 команд, дешифратор 196 адреса, элемент 197 стробирования, триггер 198 ответа памяти, триггер 199 готовности, узел 200 запросов модулей памяти, два элемента И 201-1, 201-2.

Шинный формирователь 1 подключен первым входом-выходом 17-1 адресов-данных к двунаправленной информационной шине 8 адресов-данных, которая также соединена с входами-выходами буферной памяти 5 данных и с первым входом-выходом адресов-данных блока 7 сопряжения с оперативной памятью. Второй вход-выход 17-2 адресов-данных шинного формирователя 1 подключен к одноименным входам-выходам блока 2 управления адресами данных, блока 3 управления адресными тегами данных и входам-выходам адресов-данных блока 6 центрального управления. Вход 10 установки нуля устройства соединен с соответствующими входами блоков 2, 3, 7. Входная управляющая шина 11 строба адреса и строба данных, выходная управляющая шина 13 "Готовность данных" и выходная шина 14 прерываний устройства подключены к одноименным входу и выходам блока 6. Управляющий вход 23-3 блока 6 соединен с управляющим выходом 27-3 признака готовности блока 7. Управляющий вход 23-4 признаков готовности блока 6 подключен шиной 30 к выходу блока 2 и к управляющим выходам 19-1, 21-1 признавков готовности блоков 3 и 4. Контрольный вход 23-5 блока 6 соединен с одноименным выходом блока 3. Управляющий выход 24-2 блока 6 шиной 29 подключен к управляющим входам шинного формирователя 1 и блока 3, к входам 18-1, 20-2 блоков 2 и 4. Выход 24-3 строба адреса и строба данных блока 6 соединен с одноименным входом блока 7. Адресный выход 19-2 блока 3 подключен к адресному входу блока 4. Управляющий и адресвный выходы 21-2 и 21-3 соединены с соответствующими входами 22-1 и 22-2 буферной памяти 5 данных. Адресно-информационный вход-выход 25-2 блока 7 подключен к двунаправленной адресно-информационной шине 9 устройства. Управляющий вход 26-1 "Готовность оперативной памяти", командный выход 27-1, выход 27-2 "Пуск оперативной памяти" блока 7 соединены с соответствующими шинами 12, 15, 16 устройства.

Вход-выход адресов-данных блока 2 локальной шиной адресов-данных соединен с первым входом 53-1 адресов-данных блока 34, с адресным входом регистра 36 адреса, с входом 55-4 адресов-данных блока 38 записи, с входами адресов-данных первого и второго регистров 39 и 40, с выходами адресов-данных шинных формирователей 32, 44. Выход регистра 36 адреса подключен к адресным входам первого и второго дешифраторов 37 и 49, к второму адресному входу 59-2 блока 42 элементов И, к адресному входу 60-1 второго мультиплексора 43, к адресным входам 50-2 и 62-5 первого и второго блоков управления. Адресные выходы выборки строки дешифраторов 37, 49 соединены с одноименными входами накопителей 35 и 47 соответственно. Вход-выход адресов-данных накопителя 35 подключен к второму входу 53-2 адресов-данных блока 34 и к первому выходу 56-1 адресов-данных блока 38 записи. Вход-выход адресов-данных накопителя 47 соединен с входом адресов-данных блока 46 и с вторым выходом 56-2 адресов-данных блока 38 записи. Выход 54-1 адресов-данных блока 34 подключен к входу 52-1 данных блока 33 и к входу адресов-данных шинного формирователя 32. Выход 54-2 признаков сравнения блока 34 соединен с одноименным входом первого блока 31 управления, выход 51-3 признаков сравнения которого подключен к одноименным входам 52-2 и 62-6 блоков 33 и 48 соответственно. Управляющий выход блока 33 соединен с входами 50-4 и 62-3 управления выборкой колонки блоков 31 и 48 управления соответственно. Выход данных блока 33 подключен к входу 55-2 данных блока 38 записи. Второй выход 56-2 адресов-данных блока 38 соединен с одноименным входом блока 46. Выходы первого и второго регистров 39 и 40 подключены соответственно к первому и второму входам 57-1 и 57-2 первого мультиплексора 41, выход 58-1 адресов-данных которого соединен с первым входом 61-1 адресов-данных сумматора 45 и с первым адресным входом 59-1 блока 42 элементов И. Выход 58-2 данных первого мультиплексора 41 и выход блока 46 подключены шиной данных к одноименному входу 62-1 второго блока 48 управления. Выход блока 42 элементов И соединен с адресным входом 60-2 второго мультиплексора 43. Выход второго мультиплексора 43 подключен к адресному входу 61-3 сумматора 45, второй вход 61-2 адресов-данных которого соединен с выходом блока 46. Первый управляющий выход 51-1 первого блока 31 управления подключен к управляющим входам шинного формирователя 32, блоков 33, 34, регистра 36 адреса, первого дешифратора 37, к первому управляющему входу 55-1 блока 38. Первый управляющий выход 63-1 второго блока 48 управления соединен с управляющими входами первого и второго регистров 39 и 40, первого и второго мультиплексоров 41 и 43, шинного формирователя 44, сумматора 45, блока 46 считывания физических адресов, второго дешифратора 49 и с вторым управляющим входом 55-3 блока 38. Вторые управляющие входы 51-3, 63-2 первого и второго блоков 31 и 48 управления соединены с управляющим выходом блока 2. Вход данных регистра 64 данных, адресный вход блока 69 сложения по модулю два, первый адресный вход 77-1 регистра 70 адреса, выход 75-2 данных блока 65 считывания-записи и сравнения подключены локальной шиной 79 адресов-данных к входу-выходу адресов-данных блока 3 управления адресными тегами данных. Выход данных регистра 64 соединен с входом данных блока 65, выход 75-1 признаков сравнения и информационный выход 75-5 которого подключены к соответствующим входам узла 68 замещения. Вход-выход данных блока 65 соединен с входом-выходом данных накопителя 67. Контрольный выход 75-3 блока 65 через узел 66 контроля подключен к контрольному выходу 19-3 блока 3. Выход 75-4 признаков готовности блока 65 соединен с управляющим выходом 19-1 признаков готовности блока 3. Второй адресный вход 77-2 регистра 70 адреса подключен к выходу блока 69. Выход регистра 7, адреса соединен с первым адресным входом 78-1 дешифратора 71, с адресным входом дешифратора 72 и является адресным выходом 19-2 блока 3. Второй адресный вход 78-2 дешифратора 71 подключен к выходу узла 68 замещения. Выход дешифратора 71 соединен с адресным входом 74-2 выборки номера колонки блока 65. Выход дешифратора 72 соединен с адресным входом выборки номера строки накопителя 67. Управляющие входы блока 69 и узла 73 управления подключены к управляющим входам блока 3. Выход узла 73 управления соединен с управляющими входами регистров 64, 70, блока 65, дешифраторов 71, 72, узла 68 замещения. Выход установки нуля накопителя 67 подключен к одноименному входу блока 3.

Устройство работает следующим образом.

При выполнении процессором команды работы с памятью в устройство управления памятью данных по шине 8 адресов-данных поступают код команды и адрес, сопровождаемый стробом адреса А по шине 11. Адрес записывается в регистры адреса, находящиеся в блоках 2, 3 (фиг. 1).

По анализу разрядов адреса определяется один из следующих возможных типов обращения: в буферную память данных, в оперативную память, во внешние регистры.

В качестве внешних регистров могут использоваться как внутренние регистры устройства управления буферной памятью данных, так и не относящиеся к этому устройству (внешние по отношению к блокам 2, 3) регистры. Далее работа блоков 1-7 рассматривается на примере реализации в конкретной микропроцессорной системе. Решение о том, в какую память данных буферную или оперативную следует обращаться, принимается на основании того, есть ли данные в буфере. Если поступивший адрес является математическим (пять старших разрядов адреса в регистре адреса не равны нулю), его необходимо преобразовать в физический с помощью таблицы страниц. Для каждой задачи пользователя операционной системой создаются своя таблица страниц (ТСП) и общая таблица страниц дя всех задач операционной системы (ТСС). Таблица страниц (ТСС или ТСП) многоуровневая, в блоке 2 находится таблица первого уровня в накопителях 35 и 47 (фиг. 2), структура полей одной строки таблицы для математических и физических адресов показана на фиг. 29 и 30 соответственно.

Восемнадцать старших разрядов адреса регистра 36 31: 18, поступающие из процессора, сравниваются с соответствующими разрядами строки, задаваемыми в регистре 36 [13: 4] (фиг. 29), накопителя 35, а тринадцатый разряд регистра адреса - с битом значимости v выбранной строки. Если вышеперечисленные разряды совпадают, т. е. найдено соответствие математического и физического адресов, происходит "омоложение" значения приоритета строки в таблице, т. е. в регистр 124 хранения признаков в блоке 33 старения (LRU, фиг. 29) записывается новая строка, состоящая из шести разрядов, которая по сигналу записи разрядов блока 33 по входу 55-1 записывается в строку накопителя 35, номер которой задается четырьмя разрядами 13: 4 регистра 36. Поскольку в данной реализации накопители 35 и 47 выполнены по четырехколоночной схеме, то и старение строк происходит в пределах четырех колонок для каждой из строк независимо от номера конкретной строки. Если сравнение адресов для одной из колонок произошло, то по сигналу сравнения с выхода 54-2, поступающему через блок 31 в блок 46 считывания (фиг. 2), разряды физического адреса (0-26) поступают в сумматор 45 (фиг. 2), 28-1 разряд - в блок 6 через блок 48. Полный физический адрес обращения в оперативную память образуется сложением 27 разрядов адреса со смещением, т. е. адресом внутри страницы, который находится в десяти младших разрядах регистра 36 [9: 10] и попадает на второй вход сумматора 45. В блоке 6 анализируется знаение 28-го разряда (бита модификации М). Если оно равно нулю то, если в команде из процессора выполнялась запись данных, это была первая запись и формируется прерывание в процессор. В результате программной обработки превышения в данной строке проставляется единичное значение бита М, что позволяет в дальнейшем не выходить при следующих обращениях на ветвь обработки превышения. Если данные в буфере (для команд чтения) отсутствуют, что проверяется параллельно с действиями по преобразованию адреса, то полученный в сумматоре физический адрес через формирователь 44 поступает в локальную шину 28 и через блок 1 в шину 8 (фиг. 1).

Если во всех четырех колонках накопителя 35 (фиг. 2) сравнения не произошло и данные не находятся в буферной памяти 5 данных, то новая строка таблицы страниц будет подкачена из оперативной памяти (таблицы страниц второго уровня) с помощью блока 4. Адрес строки определяется суммой двух операндов, первый из которых выбран по первому входу первого операнда сумматора 45 по входу 61-1, куда подается адрес начала таблицы страниц ТСС или ТСП. Предварительно адреса в регистры 39 и 40 записываются командами записи во внешний регистр в блок 2 (фиг. 1). Выбор регистра производится по признаку "система-пользователь" в мультиплексоре 41. Признак подается по входу 62-5 в блок 48 и из него в виде строба по входу 57-3 в мультиплексор 41. Значение на втором входе сумматора 45 образуется объединением двух полей, в разряды 1-7 второго операнда сумматора 45 помещаются разряды 10-16 регистра 36 адреса, в которых находится минимальный размер таблицы страниц. Разряды 8-12 входа сумматора 45 (т. е. расширение до максимального размера таблицы страниц) образуются наложением пятиразрядной маски на пять разрядов регистра 36 адреса, т. е. логическим произведением в блоке 42 (фиг. 2) разрядов 17-21 регистра 36 адреса на пять разрядов маски, которая образуется пятью старшими разрядами, находящимися в регистрах 39 и 40, выбираемыми по признаку "система-пользователь" по входу 57-3. В накопители 35 и 47 через блок 38 записи управляющими сигналами по входам 55-1 и 55-3 соответственно последовательно записываются из оперативной памяти математический и физический адреса через шины 8 и 28 в строку, определяемую дешифраторами 37 и 49. Номер колонки, определяемый блоком 33 замещения (фиг. 2), подается на вход 62-3 блока 48 и на вход 50-4 блока 31 и затем через соответствующие мультиплексоры (фиг. 7 и 27) на входы блоков 34 и 46 считывания. После этого, если повторное считывание со сравнением адреса с подкаченными разрядами математического адреса управляющими сигналами по входу 53-3 (для блока 34) не дает сравнения ни в одной из колонок, т. е. сигнал готовности по выходу 51-2 равен нулю, то из блока 6 выдается прерывание "нет страницы" по шине 14. Если сравнение произошло, т. е. сигнал готовности по шине 51-2 равен единице, то полученный сложением физического адреса со смещением, как было описано выше, адрес с выхода сумматора 45 через шинный формирователь 44 по шине 28 и далее через блок 1 (фиг. 1) поступает на вход 25-1 блока 7, где формируется обращение в оперативную память. Параллельно с преобразованием математического адреса в физический производится выборка данных (если они есть) из буферной памяти данных для команды чтения. Для этого вначале определяется наличие их в буфере по совпадению адресного тега, хранящегося в соответствующей строке, указанной дешифратором 72 строк накопителя 67 адресных признаков данных (фиг. 3), со старшими разрядами математического адреса (см. фиг. 28), записанного в регистр 70 адреса (фиг. 3). Накопитель 67 адресных признаков данных организован в виде четырехколоночной ассоциативной памяти аналогично накопителю 35 математических адресов блока 2 (фиг. 1) с добавлением бита значимости и контроля (фиг. 31). Поскольку значение, хранящееся в строке адресного тега накопителя, соответствует восьми 32-разрядным словам буфера данных и подкачка из блока 7 сопряжения с оперативной памятью (фиг. 1) выполняется по восемь слов, а полный объем буфера 2К слов (или ВК слов в зависимости от буферной памяти), то адрес обращения в буфер данных меньше размера математической страницы, и для того, чтобы не происходило вытеснение строк данных, соответствующих одной и той же странице, у которых совпадают старшие разряды математического адреса, при обращении к блоку 3 семь младших разрядов адреса складываются по модулю два с семью разрядами адреса в поле номера страницы в блоке 69 (фиг. 3). Таким способом достигается улучшение перемешивания адресов в накопителе 67 адресных признаков данных (фиг. 32).

Возможны два варианта работы блока 3 управления адресными тегами данных. В первом варианте, если возникает сигнал сравнения в одной из четырех колонок (данные есть в буфере), блок 6 формирует на выходе 24-2 управляющие сигналы, которые преобразуются в блоке 4 (фиг. 1) в сигнал CED, сигнал ОЕ для чтения или МЕ при записи по входу 22-1. Если выполняется процессором команда чтения, то данные считываются в процессор по шине 8. При записи данных происходит также обращение в оперативную память ("сквозная запись") для поддержания когерентности хранимых в буфере и в оперативной памяти общих данных, что особенно важно при работе на общую память нескольких процессоров. Из блока 4 адрес с выхода 21-3 поступает на микросхемы буферной памяти данных в блоке 5 (в зависимости от комплектации могут применяться КМОП БИС с организацией 2Кх8 или 8Кх8). Комплектация задается программно в регистре состояния в блоке 7. В блоке 6 выдается с выхода 19-1 блока 3 сигнал "Готовность данных".

Во втором варианте, если данные в буфере не найдены, по физическому адресу, вычисленному на сумматоре 45, производится сначала подкачка восьми слов данных по шине 9, считанные из оперативной памяти данные записываются в блок 7, а затем (если была команда чтения) по шине 8 в процессор. Правильность хранения адресного тега проверяется узлом 66 контроля (фиг. 3), и сигнал контроля с выхода 19-3 поступает в блок 7, откуда выдается по шине 14 для обрабтки прерывания. Работа блока 68 замещения (фиг. 3) полностью аналогична работе блока 33 LRU в блоке 2 (фиг. 2). При работе устройства управления страничной памятью возможно, что строка математический адрес + физический адрес отсутствует в накопителях 35 и 47, так как уже вытеснена механизмом замещения (блок 33), а данные есть в буферной памяти 5 (фиг. 1). Это позволяет отказаться от результата преобразования математического адреса в физический адрес, запуска оперативной памяти и тем самым повысить быстродействие системы.

В зависимости от значения бита значимости V в блоке 2 (фиг. 29) при входе в задачу возможны два режима работы. В первом режиме, если бит значимости V обнулен при входе в задачу, это означает, что для соответствующих строк производится подкачка строк в накопители 35 и 47 по требованию. Такой режим эффективен, если операционная система решает задачу, разделенную на несколько подзадач, и смена задач происходит относительно редко и сопровождается обнулением бита значимости. Это не приводит к большим накладным расходам. Однако, если операционная система построена так, что часты вхождения и возвраты из одной задачи (для любой задачи), то предлагается при выходе из задачи не обнулять бит значимости V (второй режим) для строки таблицы страниц. При этом таблица страниц первого уровня (накопители 35 и 47) становится общей для нескольких задач, причем у каждой задачи сохраняется свой максимальный размер таблицы страниц. Старшие разряды математического адреса играют роль "номера задачи" и различны для таблиц страниц различных задач. Размер таблицы страниц первого уровня ограничен, поэтому при увеличении числа используемых страниц для каждой задачи возможно, что наиболее давно используемые страницы замещаются с помощью механизма LRU, но только в тех случаях, когда данных не оказалось в буферной памяти 5. Размер поля номера задачи зависит от размера таблицы страниц текущей задачи (фиг. 33). За счет таблицы страниц второго уровня, находящейся в оперативной памяти, размер таблицы страниц практически не ограничен и обращение во второй уровень не приводит к прерыванию, что повышает быстродействие устройства. При обращении по физическому адресу оперативной памяти этот адрес поступает в блок 7 из блока 6 через локальную шину 28 без преобразования.

Рассмотрим работу устройства при обращении к внешним регистрам на примере адресации накопителя математических адресов блока 2. Адрес регистра по стробу адреса, выдаваемого из процессора по шине 11, записывается в регистр 36 блока 2 (фиг. 2) в первом цикле работы команды. Адрес строки накопителя указывается в разрядах 10-13 адреса, который поступает в дешифратор 37. Признак выбора накопителя дешифрируется в блоке 6. Затем, если выполняемая команда является командой чтения, адрес колонки, задаваемый в нулевом и первом разрядах адреса, дешифрированный в блоке 31 во втором цикле выполнения команды, поступает в блок 34. Считываемая информация из накопителя 35 выдается по локальной шине 28 через шинный формирователь 1 (фиг. 1) в шину 8 адресов-данных и затем записывается в процессор. Если выполняемая команда была командой записи, то в фазе передачи данных по стробу, выдаваемому по шине 11, данные через шинный формирователь 1 поступают по локальной шине 28 в блок 38 (фиг. 2). Адрес колонки, указанный в нулевом и первом разрядах регистра адреса (фиг. 28), дешифрированный в блоке 31, с выхода 51-1 (фиг. 2) также поступает в блок 38 записи (фиг. 2). Данные записываются в выбранную колонку накопителя 35. Запись-считывание накопителя 47 производится по одноименным разрядам адреса, отличие состоит в признаке выбора накопителя (фиг. 28).

Узел 73 выполняет функцию временного стробирования управляющих сигналов, поступающих из блока 6 с выхода 24-2, и состоит из известных элементов И, ИЛИ, НЕ и шинных формирователей, применяемых в блоках 31 и 48.

Управление доступом к шине 28 (арбитрах) осуществляется автоматом состояний устройств, реализованным в блоке 6 на шифраторе 98, в котором анализируются цикл поступившей из процессора команды, сигналы готовности блоков 2, 3, 4, 7, текущий цикл внутренней временной диаграммы блока и управляющие сигналы из процессора. По анализу этих сигналов вырабатывается состояние автомата для следующего цикла временной диаграммы блока 6 в виде управляющих сигналов для блоков 1-4, 7.

Изобретение позволяет повысить производительность устройства за счет выборки данных из буферной памяти данных, а не из оперативной памяти (при попадании в буфер), за счет сокращения времени поиска из-за параллельного просмотра соответствия математического и физического адресов и сравнения адресного тега данных на наличие данных в буфере, а также за счет аппаратной подкачки новой строки таблицы страниц (в случае непопадания в буфер) и отсутствия необходимости перехода на подпрограмму прерывания для этого случая, гибко разместить и перераспределить вновь выделяемую память за счет введения суммирования базы таблицы страниц со смещением, маски для изменения размера таблицы как в многозадачном, так и однозадачном режиме, снять ограничение на планируемое количество одновременно решаемых задач за счет механизма подкачки и отказа от жесткого разбиения выделяемых под задачи областей, ускорить вход и выход в новую задачу в многозадачном режиме за счет наличия быстрого буфера данных и механизма обновления только "старых страниц", обеспечить возможность изменения размера используемой буферной памяти данных, задаваемого признаком в регистре состояния. (56) Патент США N 4493026, кл. G 06 F 13/00, 1985.

Патент США N 4805097, кл. G 06 F 12/10, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ МНОГОФУНКЦИОНАЛЬНЫЙ КОРРЕЛЯТОР | 1994 |

|

RU2079874C1 |

| ОПТИЧЕСКИЙ МНОГОКАНАЛЬНЫЙ АССОЦИАТИВНЫЙ КОРРЕЛЯТОР | 1992 |

|

RU2037188C1 |

| СВЕТОВОДНЫЙ МНОГОКАНАЛЬНЫЙ АССОЦИАТИВНЫЙ КОРРЕЛЯТОР | 1993 |

|

RU2072551C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ | 1986 |

|

SU1417678A1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1991 |

|

RU2010309C1 |

| ОПТИЧЕСКИЙ МНОГОКАНАЛЬНЫЙ АССОЦИАТИВНЫЙ КОРРЕЛЯТОР | 1992 |

|

RU2037187C1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления ЭВМ, и может быть использовано при проектировании памяти вычислительной системы. Устройство управления памятью содержит блок центрального управления, шинный формирователь, блок сопряжения с оперативной памятью, блок управления адресами данных, включающий регистр адреса, два дешифратора, накопитель физических адресов, блок записи, два блока управления. Новым является введение блока управления адресными признаками данных, блока управления буферной памятью данных, буферной памяти данных. В блок управления адресами данных введены два шинных формирователя, блок старения и замещения, блок считывания и сравнения, два регистра, два мультиплексора, блок элементов И, сумматор, блок считывания, а блок управления адресными признаками данных содержит регистр данных, блок считывания-записи и сравнения, узел контроля, накопитель, узел замещения, блок сложения по модулю два, регистр адреса, дешифратор номера колонки, дешифратор номера строки, узел управления. 52 ил.

УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ , содеpжащее блок центpального упpавления, шинный фоpмиpователь, блок сопpяжения с опеpативной памятью, блок упpавления адpесами данных, включающий pегистp адpеса, два дешифpатоpа, накопитель математических адpесов, накопитель физических адpесов, блок записи, два блока упpавления, пеpвый инфоpмационный вход/выход адpесов/данных шинного фоpмиpователя и инфоpмационный вход/выход блока сопpяжения с опеpативной памятью подключены к двунапpавленной инфоpмационной шине адpесов/данных устpойства, адpесно-инфоpмационный вход/выход, упpавляющий вход и упpавляющий выход устpойства сопpяжения с опеpативной памятью являются соответственно адpесно-инфоpмационным входом/выходом, упpавляющим входом "Готовность опеpативной памяти" и упpавляющим выходом "Пуск опеpативной памяти" устpойства, упpавляющий вход "Стpоба адpеса и стpоба данных", упpавляющий выход "Готовность данных" котоpого являются одноименным входом и выходом блока центpального упpавления, упpавляющий вход пpизнака готовности котоpого соединен с одноименным выходом блока сопpяжения с опеpативной памятью, упpавляющий вход "Стpоба адpеса и стpоба данных" котоpого подключен к одноименному выходу блока центpального упpавления, упpавляющий выход котоpого подключен к упpавляющим входам блока упpавления адpесами данных и шинного фоpмиpователя, втоpой инфоpмационный вход/выход аpесов/данных котоpого подключен к инфоpмационному входу/выходу адpесов/данных блока центpального упpавления и к входу/выходу адpесов/данных блока упpавления адpесами данных, выход котоpого по упpавляющей шине соединен с упpавляющим входом блока центpального упpавления, упpавляющий выход пpеpывания котоpого является одноименным выходом устpойства, выходная шина команд котоpого подключена к командному выходу блока сопpяжения с опеpативной памятью, вход установки нуля устpойства соединен с одноименными входами блока упpавления адpесами данных и блока сопpяжения с опеpативной памятью, в блоке упpавления адpесами данных вход/выход адpесов/данных соединен двунапpавленной инфоpмационной локальной шиной адpесов/данных с адpесным входом pегистpа и входом адpесов/данных блока записи, пеpвый и втоpой выходы адpесов/данных котоpого подключены, соответственно, к входам/выходам адpесов/данных накопителя математических адpесов и накопителя физических адpесов, адpесные входы выбоpки стpоки котоpых соответственно соединены с выходами пеpвого и втоpого дешифpатоpов стpок, адpесные входы котоpых подключены к выходу pегистpа адpеса, упpавляющие входы pегистpа адpеса, пеpвого дешифpатоpа стpок и пеpвый упpавляющий вход блока записи соединены с пеpвым упpавляющим выходом пеpвого блока упpавления, упpавляющий вход котоpого и упpавляющий вход втоpого блока упpавления подключены к упpавляющему входу блока упpавления адpесами данных, упpавляющий вход втоpого дешифpатоpа и втоpой упpавляющий вход блока записи соединены с пеpвым упpавляющим выходом втоpого блока упpавления, втоpой упpавляющий выход котоpого и втоpой упpавляющий выход пеpвого блока упpавления подключены к упpавляющему выходу блока упpавления адpесами данных, отличающееся тем, что в него введены блок упpавления адpесными пpизнаками данных, блок упpавления буфеpной памятью данных, блок буфеpной памяти данных, в блок упpавления адpесами данных дополнительно введены два шинных фоpмиpователя, блок стаpения и замещения, блок считывания и сpавнения, два pегистpа, два мультиплексоpа, блок элементоа "И", сумматоp, блок считывания, а блок упpавления адpесными пpизнаками данных содеpжит pегистp данных, узел считывания/записи и сpавнения, узел контpоля, накопитель, узел замещения, блок сложения по модулю два, pегистp адpеса, дешифpатоp номеpа колонки, дешифpатоp номеpа стpоки, узел упpавления, пpичем втоpой инфоpмационный вход/выход адpесов/данных шинного фоpмиpователя соединен с одноименным входом/выходом блока упpавления адpесными пpизнаками данных, упpавляющий вход котоpого и упpавляющий вход блока упpавления буфеpной памятью данных подключены к упpавляющему выходу блока центpального упpавления, упpавляющий вход котоpого соединен с упpавляющим выходом пpизнака готовности данных блока упpавления буфеpной памятью данных и пpизнака готовности блока упpавления адpесными пpизнаками, контpольный и адpесный выходы котоpого подключены соответственно к контpольному входу блока центpального упpавления и к адpесному входу блока упpавления буфеpной памятью, адpесный и упpавляющий выходы котоpого соединены с одноименными входами блока буфеpной памяти данных, вход/выход адpесов/данных котоpого подключен чеpез двунапpавленную инфоpмационную шину адpесов/данных к входу/выходу адpесов/данных блока сопpяжения с блоком опеpативной памяти, вход установки нуля устpойства подключен к входам установки нуля блока упpавления адpесными пpизнаками данных и блока упpавления буфеpной памятью данных, упpавляющий вход блока упpавления адpесами данных соединен с упpавляющими входами пеpвого и втоpого блоков упpавления, входы упpавления выбоpкой колонки блока упpавления адpесами данных подключены к упpавляющему выходу блока стаpения и замещения, выход данных котоpого соединен с входом данных блока записи, вход данных блока стаpения и замещения и вход адpесов/данных пеpвого шинного фоpмиpователя подключены к выходу адpесов/данных блока считывания и сpавнения, выход пpизнаков сpавнения котоpого соединен с одноименным входом пеpвого блока упpавления, выход пpизнаков сpавнения котоpого соединен с одноименными входами блока стаpения и замещения и втоpого блока упpавления, пеpвый упpавляющий выход пеpвого блока упpавления подключен к упpавляющим входам блока считывания и сpавнения, блока стаpения и замещения, пеpвого шинного фоpмиpователя, выход котоpого, пеpвый вход адpесов/данных блока считывания и сpавнения, выход втоpого шинного фоpмиpователя, входы адpесов/данных пеpвого и втоpого pегистpов соединены с двунапpавленной локальной шиной адpесов/данных, котоpая подключена к входу/выходу адpесов/данных блока упpавления адpесами данных, выход пеpвого и втоpого pегистpов соединены соответственно с пеpвым и втоpым входами адpесов/данных пеpвого мультиплексоpа, выход адpесов/данных котоpого подключен к пеpвому входу адpесов/данных сумматоpа и к пеpвому адpесному входу блока элементов "И", втоpой адpесный вход котоpого, пеpвый и втоpой адpесные входы втоpого мультиплексоpа соединены с выходом pегистpа адpеса, выход блока элементов И подключен к адpесному входу втоpого мультиплексоpа, выход котоpого соединен с адpесным входом сумматоpа, выход котоpого подключен к входу адpесов/данных втоpого шинного фоpмиpователя, вход/выход адpесов/данных накопителя физических адpесов соединен с входом адpесов/данных блока считывания, выход котоpого соединен с втоpым входом адpесов/данных сумматоpа, выход блока считывания и выход данных пеpвого мультиплексоpа подключены к входу данных втоpого блока упpавления, пеpвый упpавляющий выход котоpого соединен с упpавляющими входами пеpвого и втоpого pегистpов, пеpвого

и втоpого мультиплексоpов, втоpого шинного фоpмиpователя, сумматоpа, блока считывания, втоpого дешифpатоpа стpок, втоpые упpавляющие выходы пеpвого и втоpого блоков упpавления соединены с упpавляющим выходом блока упpавления адpесами данных, вход установки в нуль котоpого подключен к одноименному входу накопителя математических адpесов, вход/выход адpесов/данных блока упpавления адpесными пpизнаками данных соединен по локальной шине адpесов/данных с входом данных pегистpа данных, с адpесным входом блока сложения по модулю два, с выходом данных блока считывания/записи и сpавнения, с пеpвым адpесным входом pегистpа адpеса, втоpой адpесный вход котоpого соединен с выходом блока сложения по модулю два, выход pегистpа адpеса подключен к пеpвому адpесному входу дешифpатоpа номеpа колонки, к адpесному входу дешифpатоpа номеpа стpоки и является адpесным выходом блока упpавления адpесными пpизнаками данных, вход установки в нуль котоpого подключен к одноименному входу накопителя, выход дешифpатоpа номеpа колонки соединен с адpесным входом выбоpа номеpа колонки блока считывания/записи и сpавнения, вход данных котоpого подключен к выходу pегистpа данных, выход пpизнака сpавнения и инфоpмационный выход блока считывания/записи и сpавнения соединены с одноименными входами узла замещения, выход котоpого подключен к втоpому адpесному входу дешифpатоpа номеpа колонки, выход дешифpатоpа номеpа стpоки соединен с адpесным входом выбоpки номеpа стpоки накопителя, вход/выход данных котоpого подключен к входу/выходу данных блока считывания/записи и сpавнения, выход пpизнака готовности котоpого является одноименным выходом блока упpавления адpесными пpизнаками данных, выход данных и контpольный выход блока считывания/записи и сpавнения подключены к одноименным входам узла контpоля, выход котоpого соединен с контpольным выходом блока упpавления адpесными пpизнаками данных, упpавляющий вход котоpого подключен к упpавляющим входам блока сложения по модулю два и узла упpавления, выход котоpого по упpавляющей шине соединен с упpавляющими входами pегистpа данных, pегистpа адpеса, дешифpатоpа номеpа колонки, дешифpатоpа номеpа стpоки, узла замещения, блока считывания/записи и сpавнения.

Авторы

Даты

1994-03-30—Публикация

1991-10-28—Подача