Изобретение относится к вычислительной технике и предназначено для использования в центральных процессорах ЭВМ высокой производительности.

Известно устройство подпрограмм центрального процессора МВК "Эльбрус 1", содержащее регистр приема, блок формирования связующей информации, блок формирования программной информации, блок управления, арифметический блок, регистр выдачи, регистр адреса (1).

Недостатком известного устройства является низкое быстродействие.

Наиболее близким техническим решением к изобретению является устройство подпрограмм центрального процессора МВК "Эльбрус 2" (2), содержащее блок памяти, блок памяти параметров, три элемента сравнения, два сумматора, семь входных регистров, одиннадцать регистров, четыре выходных регистра, двенадцать коммутаторов, устройство управления, входную информационную 0-ую шину числа из буфера стека, входную информационную 1-ую шину числа из буфера стека, входную информационную шину числа из ассоциативного ЗУ глобалов, входную информационную шину числа из локальной памяти, входную шину управляющей информации из устройства управления ЦП, выходные информационные шины числа в буфер стека и в буфер памяти, выходную шину индекса команды в буфер команд, выходую шину математического адреса в ассоциативное ЗУ страниц, выходную информационную шину числа в устройство преобразования чисел, три информационные шины, вход первого входного регистра и первый информационный вход устройства управления соединены с входной информационной 0-ой шиной числа из буфера стека, вход второго входного регистра и второй информационный вход устройства управления подключены к входной информационной 1-ой шине числа из буфера стека, вход третьего входного регистра и третий информационный вход устройства управления соединены с входной информационной шиной числа из ассоциативного ЗУ глобалов, вход четвертого входного регистра и четвертый информационный вход устройства управления подключен к входной информационной шине числа из локальной памяти, пятый информационный вход устройства управления, первый информационный вход блока памяти параметров, информационные входы шестого и седьмого входных регистров соединены с входной шиной управляющей информации из устройства управления ЦП, выход первого входного регистра соединен с информационным входом первого регистра, выход которого подключен к первому информационному входу первого коммутатора, второй и третий информационные входы которого соединены с выходами первого и третьего входных регистров соответственно, выход первого коммутатора подключен к входу второго регистра, выходы второго и четвертого входных регистров соединены с первым и вторым информационными входами второго коммутатора, выход которого подключен ко входу третьего регистра, первый информационный вход третьего коммутатора соединен с выходом шестого регистра, вход третьего коммутатора подключен к информационному входу блока памяти, первый информмационный выход которой соединен с выходной информационной шиной числа в буфер стека, второй и третий информационные выходы блока памяти подключены соответственно к первым и вторым информационным входам четвертого коммутатора, третий информационный вход которого соединен с выходом десятого регистра, третья информационная шина подключена к четвертому информационному входу четвертого коммутатора, выход которого через первый выходной регистр соединен с выходной информационной шиной числа в буферную память, выход второго регистра подключен к информационным входам четвертого, пятого, девятого и пятого входного регистров, к второму информационному входу блока памяти параметров, выход которой соединен с третьим информационным входом девятого коммутатора, выходы четвертого и пятого регистров соединены соответственно с первыми информационными входами первого и второго элементов сравнения, выходы которых подключены к первой информационной шине, которая соединена с седьмым входом устройства управления, выход пятого коммутатора соединен с пятым информационным входом десятого коммутатора и с информационным входом шестого регистра, выход которого подключен к первому информационному входу шестого коммутатора и ко второму информационному входу девятого коммутатора, выход шестого коммутатора соединен с первым входом первого сумматора, первый информационный вход девятого коммутатора подключен ко второй информационной шине, с которой соединены выходы седьмого и восьмого регистров, выход девятого регистра подключен к первым информационным входам седьмого и восьмого коммутаторов, выход седьмого коммутатора подключен к информационному входу десятого регистра, выход которого соединен со вторым информационным входом восьмого коммутатора и с четвертым информационным входом девятого коммутатора, выход которого подключен к информационному входу второго выходного регистра, выход которого соединен с выходной информационной шиной числа в устройство преобразования чисел, выход восьмого коммутатора подключен третьей информационной шиной к третьему информационному входу десятого коммутатора, выход которого соединен с информационным входом третьего выходного регистра, выход которого подключен к выходной шине математического адреса в ассоциативное ЗУ страниц, выход пятого входного регистра соединен с первым информационным входом одиннадцатого коммутатора и с первым входом третьего элемента сравнения, ко второму входу второго и ко второму информационному входу одиннадцатого коммутатора подключен выход шестого входного регистра, выход седьмого входного регистра подключен к первому входу второго сумматора, выход третьего элемента сравнения соединен с третьим информационным входом одиннадцатого коммутатора, выход которого через одиннадцатый регистр подключен ко второму входу второго сумматора, выход которого соединен с первым информационным входом двенадцатого коммутатора, ко второму информационному входу которого подключена шина логического "0" устройства, выход двенадцатого коммутатора соединен со входом четвертого выходного регистра, выход которого подключен к выходной шине индекса команды в буфер команд, управляющие входы шестого, седьмого входных регистров, первого, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого регистров, с первого по двенадцатый коммутаторы, блока памяти, блока памяти параметров, второго и третьего выходных регистров подключены к выходу устройства управления.

Недостатком известного устройства является низкое быстродействие, т. к. оно требует остановки работы остальных устройств ЦП при выполнении процедурных переходов, т. к. базовые регистры в это время используются устройством подпрограмм монопольно; выполнение процедурного перехода требует многократных последовательных обращений к структуре спискового типа, хранящейся в ОЗУ для создания адресного контекста новой процедуры.

Цель изобретения - расширение функциональных возможностей и повышение быстродействия устройства за счет обеспечения одновременной подготовки нескольких процедурных переходов и уменьшения количества обращений к оперативной памяти.

Поставленная цель достигается тем, что в устройство подпрограмм, содержащее блок памяти, блок памяти параметров, три элемента сравнения, два сумматора, семь входных регистров, одиннадцать регистров, четыре выходных регистра, двенадцать коммутаторов, устройство управления, входную информационную О-ую шину числа из буфера стека, входную информационную 1-ую шину числа из ассоциативного ЗУ глобалов, входную информационную шину числа из локальной памяти, входную шину управляющей информации из устройства управления ЦП, выходные информационные шины числа в буфер стека и в буфер памяти, выходную шину индекса команды в буфер команд, выходную шину математического адреса в ассоциативное ЗУ страниц, выходную информационную шину числа в устройство преобразования чисел, три информационные шины, вход первого входного регистра и первый информационный вход устройства управления соединен с входной информационной О-ой шиной числа из буфера стека, вход второго входного регистра и второй информационный вход устройства управления подключены к входной информационной 1-ой шине числа из буфера стека, вход третьего входного регистра и третий информационный вход устройства управления соединены с входной информационной шиной числа из ассоциативного ЗУ глобалов, вход четвертого входного регистра и четвертый информационный вход устройства управления подключен к входной информационной шине числа из локальной памяти, пятый информационный вход устройства управления, первый информационный вход блока памяти параметров, информационные входы шестого и седьмого входных регистров соединены с входной шиной управления информации из устройства управления ЦП, выход первого входного регистра соединен с информационным входом первого регистра, выход которого подключен к первому информационному входу первого коммутатора, второй и третий информационные входы которого соединены с выходами первого и третьего входные регистров соответственно, выход первого коммутатора подключен к входу второго регистра, выходы второго и четвертого входных регистров соединены с первым и вторым информационными входами второго коммутатора, выход которого подключен ко входу третьего регистра, первый информационный вход третьего коммутатора соединен с выходом шестого регистра, выход третьего коммутатора подключен к информационному входу блока памяти, первый информационный выход которой соединен с выходной информационной шиной числа в буфер стека, второй и третий информационные выходы блока памяти подключены соответственно с первым и вторым информационным входам четвертого коммутатора, третий информационный вход которого соединен с выходом десятого регистра, третья информационная шина подключена к четвертому информационному входу четвертого коммутатора, выход которого через первый выходной регистр соединен с выходной информационной шиной числа в буферную память, выход второго регистра подключен к информационным входам четвертого, пятого, девятого и пятого входного регистров, ко второму информационному входу блока памяти параметров, выход которой соединен с третьим информационным входом девятого коммутатора, выходы четвертого и пятого регистров соединены соответственно с первыми информационными входами первого и второго элементов сравнения, выходы которых подключены к первой информационной шине, которая соединена с седьмым входом устройства управления, выход пятого коммутатора соединен с пятым информационным входом десятого коммутатора и с информационным входом шестого регистра, выход которого подключен к первому информационному входу шестого коммутатора и ко второму информационному входу девятого коммутатора, выход шестого коммутатора соединен с первым входом первого сумматора, первый информационный вход девятого коммутатора подключен ко второй информационной шине, с которой соединены выходы седьмого и восьмого регистров, выход девятого регистра подключен к первым информационным входам седьмого и восьмого коммутаторов, выход седьмого коммутатора подключен к информационному входу десятого регистра, выход которого соединен со вторым информационным входом восьмого коммутатора и с четвертым информационным входом девятого коммутатора, выход которого подключен к информационному входу второго выходного регистра, выход которого соединен с выходной информационной шиной числа в устройство преобразования чисел, выход восьмого коммутатора подключен третьей информационной шиной к третьему информационному входу десятого коммутатора, выход которого соединен с информационным входом третьего выходного регистра, выход которого подключен к выходной шине математического адреса в ассоциативное ЗУ страниц, выход пятого входного регистра соединен с первым информационным входом одиннадцатого коммутатора и с первым входом третьего элемента сравнения, ко второму входу которого и ко второму информационному входу одиннадцатого коммутатора подключен выход шестого входного регистра, выход седьмого входного регистра подключен к первому входу второго сумматора, выход третьего элемента сравнения соединен с третьим информационным входом одиннадцатого коммутатора, выход которого через одиннадцать регистр подключен ко второму входу второго сумматора, выход которого соединен с первым информационным входом двенадцатого коммутатора, ко второму информационному входу которого подключена шина логического "0" устройства, выход двенадцатого коммутатора соединен со входом четвертого выходного регистра, выход которого подключен к выходной шине индекса команды в буфер команд, управляющие входы шестого, седьмого входных регистров, первого, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого регистров, с первого по двенадцатый коммутаторы, блока памяти, блока памяти параметров, второго и третьего выходных регистров подключены к выходу устройства управления, введены дополнительный блок памяти, дополнительный входной регистр, дополнительный элемент сравнения, четырнадцать дополнительных регистров, девять дополнительных коммутаторов, блок выработки модификации значения адреса, входная информационная шина дескриптора программного сегмента из буфера стека, выходная шина адреса дескриптора программного сегмента в буфер команд, дополнительная информационная шина, причем первый и второй информационные входы первого дополнительного блока памяти соединены с выходами второго и третьего регистров соответственно, выход второго регистра информационной шиной соединен со входом четвертого дополнительного регистра, со вторыми информационными входами первого, пятого и девятого дополнительных коммутаторов, с третьими информационными входами третьего, четвертого дополнительных и двенадцатого коммутаторов, с первым и со вторым информационными входами десятого коммутатора, выход третьего регистра подключен ко второму информационному входу четвертого дополнительного коммутатора, к первому информационному входу пятого дополнительного коммутатора, к третьему информационному входу девятого дополнительного коммутатора, выход первого дополнительного блока памяти подключен ко второму информационному входу третьего коммутатора, первый информационный вход первого дополнительного коммутатора, информационные входы первого и второго дополнительных регистров, первый информационный вход дополнительного элемента сравнения подключены к выходу первого сумматора, второй информационный вход дополнительного элемента сравнения соединен с выходом четвертого дополнительного регистра, выход дополнительного элемента сравнения подключен к восьмому информационному входу устройства управления, выход первого дополнительного коммутатора соединен с информационным входом третьего дополнительного регистра, выходы первого, второго, третьего дополнительных регистров соединены соответственно с первым, вторым, третьим информационными входами пятого коммутатора, выход третьего дополнительного регистра подключен к пятому информационному входу десятого коммутатора, ко второму информационному входу шестого коммутатора, информационные входы с пятого по десятый, двенадцатого дополнительных регистров и первый информационный вход четвертого дополнительного коммутатора подключены к входной шине управляющей информации из устройства управления ЦП, выходы пятого и шестого дополнительных регистров соединены соответственно с первым и вторым информационными входами второго дополнительного коммутатора, третий информационный вход которого и первый информационный вход третьего дополнительного коммутатора подключены к выходу седьмого дополнительного регистра, выход седьмого дополнительного регистра соединен со вторым информационным входом третьего дополнительного коммутатора, выход второго дополнительного коммутатора соединен со второй информационной шиной, выходы девятого и десятого дополнительных регистров подключены к первому и ко второму информационным входам шестого дополнительного коммутатора, выход четвертого дополнительного коммутатора соединен с информационным входом одиннадцатого дополнительного регистра, выход которого подключен к третьему информационному входу шестого дополнительного коммутатора и первому информационному входу седьмого дополнительного коммутатора, второй информационный вход которого соединен с выходом двенадцатого дополнительного регистра, выход шестого дополнительного коммутатора подключен к информационному входу седьмого регистра, выход седьмого дополнительного регистра соединен с третьей информационной шиной, выход пятого дополнительного коммутатора соединен с информационным входом тринадцатого дополнительного регистра, выход которого подключен к первому информационному входу восьмого дополнительного коммутатора, второй информационный вход которого и шестой информационный вход устройства управления соединены через дополнительный входной регистр с входной шиной дескриптора программного сегмента из буфера стека, выход восьмого дополнительного коммутатора подключен к информационному входу восьмого регистра, выход девятого дополнительного коммутатора подключен к информационному входу четырнадцатого дополнительного регистра, выход которого соединен со вторым информационным входом седьмого коммутатора и с третьим информационным входом восьмого коммутатора, выход третьего выходного регистра подключен к выходной шине адреса дескриптора программного сегмента в буфер команд и через блок выработки модифицированного значения адреса ко второму информационному входу десятого коммутатора, управляющие входы дополнительного блока памяти, с первого по третий, пятый, шестой, седьмой, с девятого по четырнадцатый дополнительных регистров, с первого по девятый дополнительных коммутаторов соединены с выходом устройства управления.

Cопоставительный анализ с прототипом показывает, что заявляемое устройство отличается наличием новых блоков и элементов: дополнительного блока памяти, дополнительного сумматора, блока выработки модифицированного значения адреса, элемента сравнения, четырнадцати дополнительных регистров и девяти дополнительных коммутаторов и их связями с остальными элементами блок-схемы.

Таким образом, заявляемое устройство соответствует критерию изобретения "новизна".

Введение дополнительного блока памяти, первого, второго, третьего, шестого, с десятого по четырнадцатый дополнительных регистров, дополнительного входного регистра, дополнительных коммутаторов, и их связей с элементами блок-схемы устройства, выходной шины адреса программного сегмента в буфер команд позволило на фоне работы остальных устройств центрального процессора производить одновременную подготовку нескольких процедурных переходов.

Сокращено время выполнения операций процедурных переходов за счет введения дополнительной выходной шины адреса программного сегмента в буфер команд и выдачи в буфер команд ЦП адреса программного сегмента вызываемой процедуры в качестве ассоциативного признака для поиска сегмента кода.

Это позволяет сделать вывод о соответствии технического решения критерию "существенные отличия".

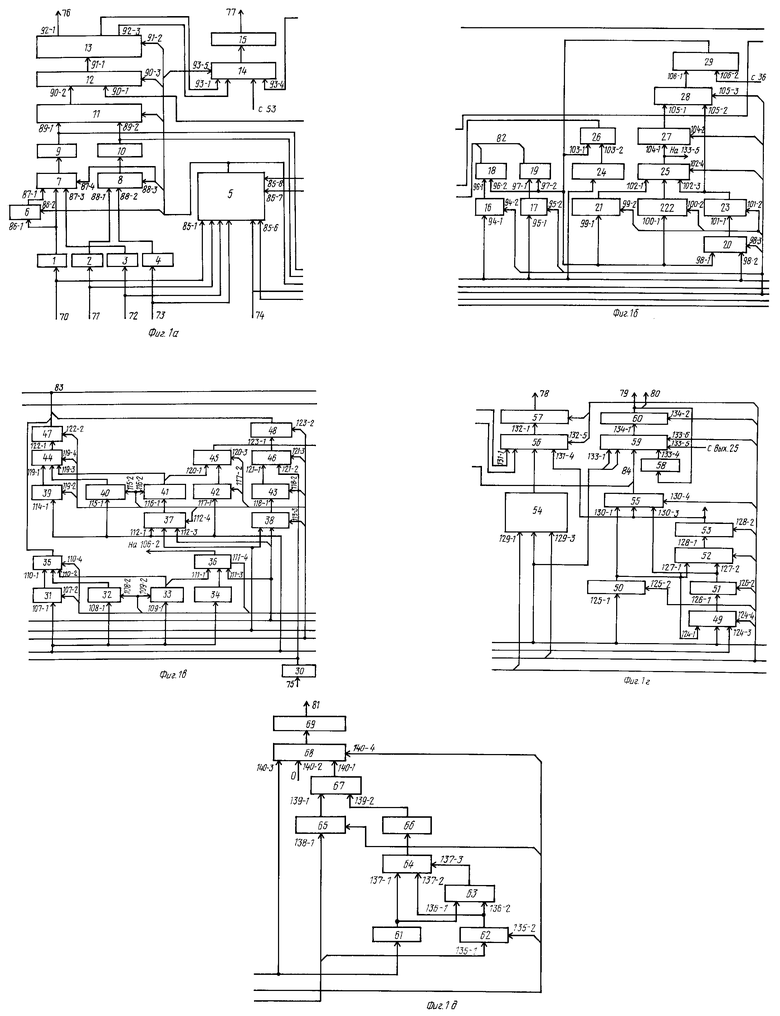

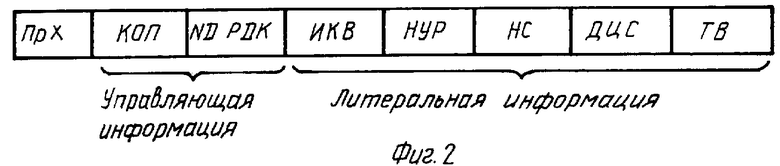

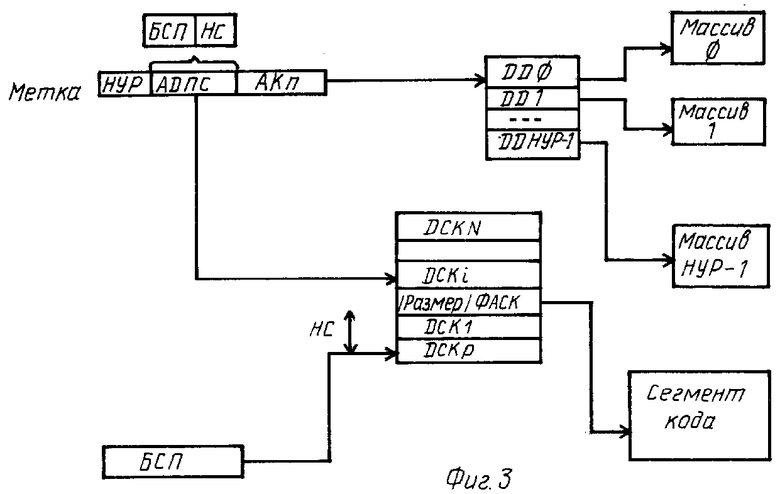

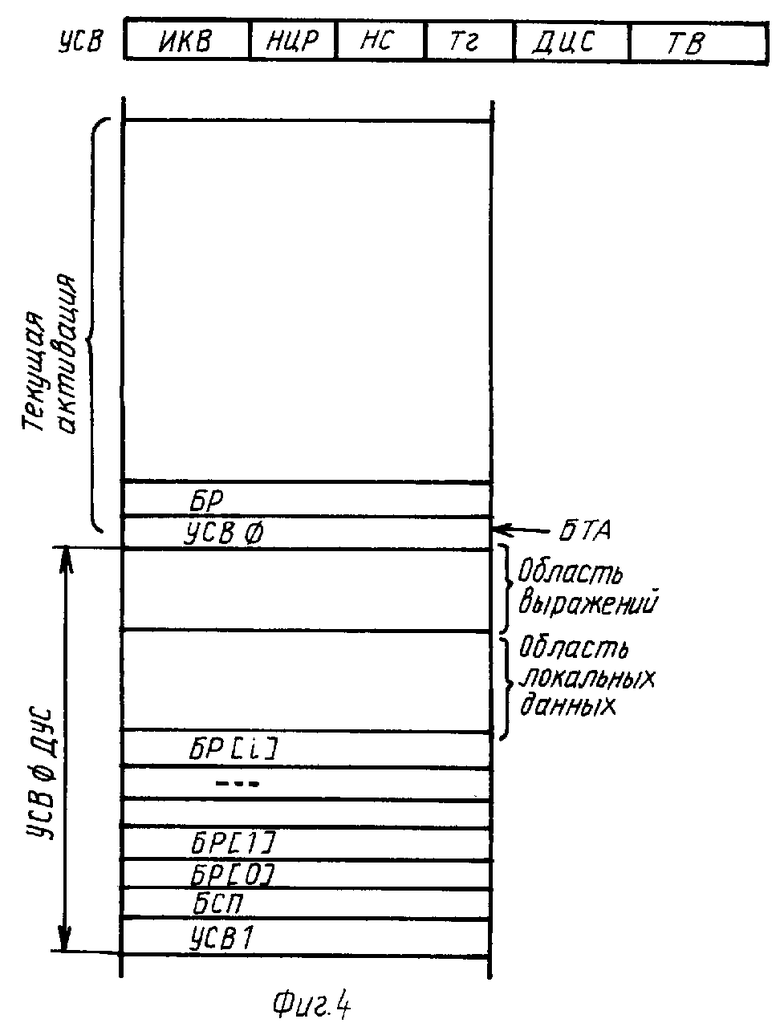

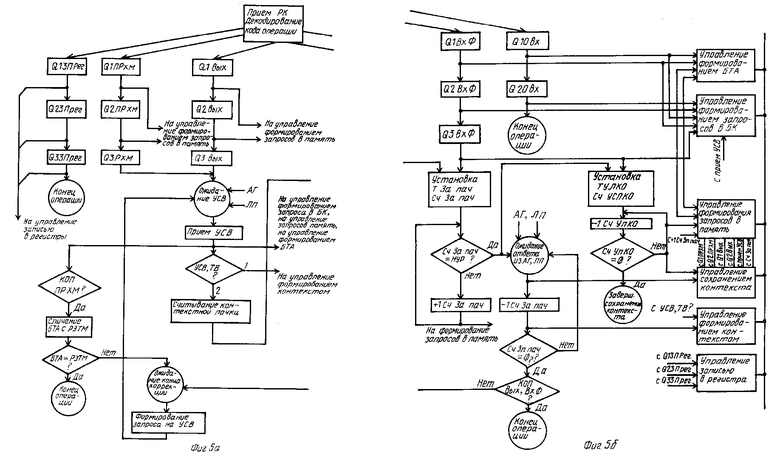

На фиг. 1а - 1д представлена блок-схема устройства подпрограмм; на фиг. 2 - структура информации, приходящей по шине управляющей информации из устройства управления ЦП; на фиг. 3 - структура адресации к коду процедуры и данным; на фиг. 4 - структура стека активации процедуры и управляющего слова возврата; на фиг. 5 - алгоритм работы устройства управления.

Устройство содержит первый входной регистр 1, второй входной регистр 2, третий входной регистр 3, четвертый входной регистр 4, устройство 5 управления, первый регистр 6, первый коммутатор 7, второй коммутатор 8, второй регистр 9, третий регистр 10, дополнительный блок 11 памяти, третий коммутатор 12, блок 13 памяти, четвертый коммутатор 14, первый выходной регистр 15, четвертый регистр 16, пятый регистр 17, первый элемент 18 сравнения, второй элемент 19 сравнения, первый дополнительный коммутатор 20, первый дополнительный регистр 21, второй дополнительный регистр 22, третий дополнительный регистр 23, четвертый дополнительный регистр 24, пятый коммутатор 25, дополнительный элемент 26 сравнения, шестой регистр 27, шестой коммутатор 28, первый сумматор 29, дополнительный входной регистр 30, пятый дополнительный регистр 31, шестой дополнительный регистр 32, седьмой дополнительный регистр 33, восьмой дополнительный регистр 34, второй дополнительный коммутатор 35, третий дополнительный коммутатор 36, четвертый дополнительный коммутатор 37, пятый дополнительный коммутатор 38, девятый дополнительный регистр 39, десятый дополнительный регистр 40, одиннадцатый дополнительный регистр 41, двенадцатый дополнительный регистр 42, тринадцатый дополнительный регистр 43, шестой дополнительный коммутатор 44, седьмой дополнительный коммутатор 45, восьмой дополнительный коммутатор 46, седьмой регистр 47, восьмой регистр 48, девятый дополнительный коммутатор 49, девятый регистр 50, четырнадцатый дополнительный регистр 51, седьмой коммутатор 52, десятый регистр 53, блок 54 памяти параметров, восьмой коммутатор 55, девятый коммутатор 56, второй выходной регистр 57, блок 58 выработки модифицированного значения адреса, десятый коммутатор 59, третий выходной регистр 60, пятый входной регистр 61, шестой входной регистр 62, третий элемент 63 сравнения, одиннадцатый коммутатор 64, седьмой входной регистр 65, одиннадцатый регистр 66, второй сумматор 67, двенадцатый коммутатор 68, четвертый выходной регистр 69, входную информационную О-ую шину 70 числа из буфера стека, входную информационную 1-ую шину 71 числа из буфера стека, входную информационную шину 72 числа из ассоциативного ЗУ глобалов, входную информационную шину 73 числа из локальной памяти, входную шину 74 управляющей информации из устройства управления ЦП, входную информационную шину 75 дескриптора программного сегмента из буфера стека, выходную информационную шину 76 числа в буфер стека, выходную информационную шину 77 числа в буферную память, выходную информационную шину 78 числа в устройство преобразования чисел, выходную шину 79 математического адреса в ассоциативное ЗУ страниц, выходную шину 80 адреса дескриптора программного сегмента в буфер команд, выходную шину 81 индекса команды в буфер стека, первую информационную шину 82, вторую информационную шину 83, третью информационную шину 84.

Устройство 5 управления имеет: с первого по восьмой информационные входы 85-1 - 85-8, первый регистр 6 - информационный вход 86-1, управляющий вход 86-2,

первый коммутатор 7 - с первого по третий информационные входы 87-1, 87-2, 87-3, управляющий вход 87-4,

второй коммутатор 8 - с первого по третий информационные входы 88-1, 88-2, управляющий вход 88-3,

первый дополнительный блок 11 памяти - первый и второй информационные входы 89-1, 89-2, управляющий вход 89-3,

третий коммутатор 12 - первый и второй информационные входы 90-1, 90-2, управляющий вход 90-3,

блок 13 памяти - информационный вход 91-1, управляющий вход 91-2, с первого по третий выходы 92-1, 92-2, 92-3,

четвертый коммутатор 14 - с первого по четвертый информационные входы 93-1 - 93-4, управляющий вход 94-5,

четвертый регистр 16 - информационный вход 94-1, управляющий вход 94-2,

пятый регистр 17 - информационный вход 95-1, управляющий вход 95-2,

первый элемент 18 сравнения - первый и второй информационные входы 96-1, 96-2,

второй элемент 19 сравнения - первый и второй информационные входы 97-1, 97-2,

первый дополнительный коммутатор 20 - первый и второй информационные входы 98-1, 98-2, управляющий вход 98-3,

первый дополнительный регистр 21 - информационный вход 99-1,

управляющий вход 99-1, управляющий вход 99-2,

второй дополнительный регистр 22 - информационный вход 100-1, управляющий вход 100-2,

третий дополнительный регистр 23 - информационный вход 101-1, управляющий вход 101-2,

пятый коммутатор 25 - с первого по третий информационные входы 102-1 - 102-3, управляющий вход - 102-4,

дополнительный элемент 26 сравнения - первый и второй информационные входы 103-1, 103-2,

шестой регистр 27 - информационный вход 104-1, управляющий вход 104-2,

шестой коммутатор 28 - первый и второй информационные входы 105-1, 105-2, управляющий вход 105-3,

первый сумматор 29 - первый и второй информационные входы 106-1, 106-2,

пятый дополнительный регистр 31 - информационный вход 107-1, управляющий вход 107-2,

шестой дополнительный регистр 32 - информационный вход 108-1, управляющий вход 108-2,

седьмой дополнительный регистр 33 - информационный вход 109-1, управляющий вход 109-2,

второй дополнительный коммутатор 35 - с первого по третий информационные входы 110-1, 110-2, 110-3, управляющий вход 110-4,

третий дополнительный коммутатор 36 - первый, второй информационный вход 111-1, 111-2, 111-3, управляющий вход 111-4,

четвертый дополнительный коммутатор 37 - с первого по третий информационные входы 112-1, 112-2, 112-3, управляющий вход 112-4,

пятый дополнительный коммутатор 38 - первый и второй информационные входы 113-1, 113-2, управляющий вход 113-3,

девятый дополнительный регистр 39 - информационный вход 114-1, управляющий вход 114-2,

десятый дополнительный регистр 40 - информационный вход 115-1, управляющий вход 115-2,

одиннадцатый дополнительный регистр 41 - информационный вход 116-1, управляющий вход 116-2,

двенадцатый дополнительный регистр 42 - информационный вход 117-1, управляющий вход 117-2,

тринадцатый дополнительный регистр 43 - информационный вход 118-1, управляющий вход 118-2,

шестой дополнительный коммутатор 44 - с первого по третий информационные входы 119-1, 119-2, 119-3, управляющий вход 119-4,

седьмой дополнительный коммутатор 45 - первый и второй информационные входы 120-1, 120-2, управляющий вход 120-3,

восьмой дополнительный коммутатор 46 - первый и второй информационные входы 121-1, 121-2, управляющий вход 121-3,

седьмой регистр 47 - информационный вход 122-1, управляющий вход 122-2,

восьмой регистр 48 - информационный вход 123-1, управляющий вход 123-2,

девятый дополнительный коммутатор 49 - с первого по третий информационные входы 124-1, 124-2, 124-3, управляющий вход 124-4,

девятый регистр 50 - информационный вход 125-1, управляющий вход 125-2,

четырнадцатый дополнительный регистр 51 - информационный вход 126-1, управляющий вход 126-2,

седьмой коммутатор 52 - первый и второй информационные входы 127-1, 127-2, управляющий вход 127-3,

десятый регистр 53 - информационный вход 128-1, управляющий вход 128-2,

блок 54 памяти параметров - первый и второй информационные входы 129-1, 129-2, управляющий вход 129-3,

восьмой коммутатор 55 - первый, второй и третий информационные входы 130-1, 130-2, 130-3, управляющий вход 130-4,

девятый коммутатор 56 - с первого по четвертый информационные входы 131-1, 131-2, 131-3, 131-4, управляющий вход 131-5,

второй выходной регистр 57 - информационный вход 132-1, управляющий вход 132-2,

десятый коммутатор 59 - с первого по пятый информационные входы 133-1, 133-2, 133-3, 133-4, 133-5, управляющий вход 133-6,

третий выходной регистр 60 - информационный вход 134-1, управляющий вход 134-2,

шестой регистр 62 - информационный вход 135-1, управляющий вход 135-2,

третий элемент 63 сравнения - первый и второй информационные входы 136-1, 136-2,

одиннадцатый коммутатор 64 - первый и второй информационные входы 137-1, 137-2, управляющий вход 137-3,

седьмой входной регистр 65 - информационный вход 138-1, управляющий вход 138-2,

второй сумматор 67 - первый и второй информационные входы 139-1, 139-2,

двенадцатый коммутатор 68 - с первого по третий информационные входы 140-1, 140-2, 140-3, управляющий вход 140-4.

Входная информационная 0-ая шина 70 соединена со входом первого входного регистра 1 и с первым информационным входом 85-1 устройства 5 управления. Входная информационная 1-ая шина 71 подключена ко входу второго входного регистра 2 и ко второму информационному входу 85-2 устройства 5 управления. Входная информационная шина 72 соединена со входом третьего входного регистра 3 и с третьим входом 85-3 устройства 5 управления. Входная информационная шина 73 подключена к четвертому входному регистру 4 и к четвертому информационному входу 85-4 устройства 5 управления. Входная шина 74 соединена с пятым информационным входом 85-5 устройства 5 управления, с информационными входами 107-1, 108-1, 109-1, 114-1, 115-1, 117-1, 135-1, 138-1, регистров 31, 32, 33, 39, 40, 42, 62, 65, 112-1 коммутатора 37, со входом регистра 34, со входом 129-1 блока 54. Входная шина 75 подключена ко входу регистра 30. Шина логического "0" соединена со вторым информационным входом 140-2 коммутатора 68. Выход регистра 1 соединен с информационным входом 86-1 регистра 6 и вторым информационным входом 87-2 коммутатора 7, первый вход 87-1 которого подключен к выходу регистра 6. Третий вход 87-3 коммутатора 7 соединен с выходом регистра 3. Выходы регистров 2 и 4 соединены с первым и вторым информационными входами 88-1, 88-2 коммутатора 8. Выход коммутатора 7 соединен со входом регистра 9, выход которого подключен к первому информационному входу 89-1 блока 11 памяти, к информационным входам 94-1, 95-1, 125-1 регистров 19, 20, 50, ко входам регистров 24, 61, ко вторым информационным входам 98-2, 113-2, 124-2 коммутаторов 20, 38, 49, к третьим информационным входам 111-3, 112-3 коммутаторов 36, 37, к первому информационному входу 140-1 коммутатора 68, ко второму информационному входу блока 54 памяти параметров, к первому и второму информационным входам 132-3, 133-4 коммутатора 59. Выход коммутатора 8 через регистр 10 соединен со вторым информационным входом 89-2 первого дополнительного блока 11 памяти, со вторым информационным входом 112-2 коммутатора 37, первым информационным входом 113-1 коммутатора 38, третьим информационным входом 124-3 коммутатора 49, выход блока 11 подключен ко второму информационному входу 90-2 коммутатора 12, первый вход 90-1 которого соединен с выходом регистра 27. Выход коммутатора 12 соединен с первым информационным входом 91-1 блока 13 памяти, первый выход 92-1 которого подключен к выходной информационной шине 76, второй и третий выходы 92-2, 92-3 - к первым и вторым информационным входам 93-1, 93-2 коммутатора 14 соответственно. Третий информационный вход 93-3 коммутатора 14 соединен с выходом регистра 53, четвертый информационный вход 93-4 - со второй информационной шиной 83. Выходы коммутатора 14 через регистр 15 соединен с выходной шиной 77. Выходы регистров 16, 17 подключены соответственно к первым информационным входам 96-1, 97-1 элементов сравнения 18, 19, выходы которых соединены с первой информационной шиной 82, которая подключена к седьмому входу 85-7 устройства 5 управления. Выходы регистров 21, 22, 23 соединены соответственно с первым, вторым и третьими информационными входами 102-1, 102-2, 102-3 коммутатора 25, выход которого подключен к информационному входу 104-1 регистра 27 и к пятому информационному входу 133-5 коммутатора 59. Выход регистра 27 соединен с первым информационным входом 105-1 коммутатора 28, ко второму информационному входу 105-2 которого подключен выход регистра 23. Выход коммутатора 28 соединен с первым информационным входом 106-1 первого сумматора 29, выход которого подключен к информационным входам 99-1, 100-1 регистров 21, 22 и первому информационному входу 98-1 коммутатора 20, ко вторым информационным входам 96-2, 97-2 элементов сравнения 18, 19, к первому информационному входу 103-1 элемента сравнения 26, выход которого соединен с восьмым информационным входом 85-8 устройства 5 управления. Выходы регистров 31, 32, 33 подключены соответственно к первому, второму и третьему информационным входам 110-1, 110-2, 110-3 коммутатора 35, выход которого соединен с информационной шиной 83, регистр 33 подключен также к первому информационному входу 111-1 коммутатора 36, второй информационный вход 111-2 которого соединен с выходом регистра 34. Выход коммутатора 36 соединен со вторым информационным входом 106-2 первого сумматора 30. Выходы регистров 39, 40, 41 соединены соответственно с информационными входами 119-1, 119-2, 119-3 коммутатора 44, выход которого подключен к информационному входу 122-1 регистра 47. Выход регистра 41 соединен также с первым информационным входом 120-1 коммутатора 45, второй информационный вход 121-2 которого подключен к выходу регистра 42. Выход коммутатора 45 подключен к третьей информационной шине 84. Выход коммутатора 38 соединен с информационным входом 118-1 регистра 43, выход которого подключен к первому информационному входу 121-1 коммутатора 46, второй вход 121-2 которого и шестой вход 85-6 устройства 5 управления соединены с выходом входного регистра 30, вход которого подключен к входной шине 75. Выход коммутатора 46 соединен с информационным входом регистра 48, выход которого подключен к информационной шине 83.

Выход коммутатора 49 соединен с информационным входом 126-1 регистра 51, выход которого подключен ко второму информационному входу 127-2 коммутатора 70 и к третьему информационному входу 130-3 коммутатора 55. Выход регистра 50 соединен с первыми информационными входами 127-1, 130-1 коммутаторов 52, 55. Выход коммутатора 52 подключен к информационному входу 128-1 регистра 53, выход которого соединен со вторым информационным входом 130-2 коммутатора 55 и с четвертым информационным входом 131-4 коммутатора 56, к третьему информационному входу 131-3 которого подключен выход блока 54 памяти параметров. Выход коммутатора 56 соединен с информационным входом 132-1 регистра 57, выход которого подключен к выходной шине 78.

Выход коммутатора 59 соединен с информационным входом 134-1 регистра 60, выход которого подключен к выходным шинам 79, 80 и через блок 58 выработки модифицированного значения адреса ко второму информационному входу 133-2 коммутатора 59.

Выход регистра 61 соединен с первыми информационными входами 136-1, 137-1 третьего элемента 63 сравнения и коммутатора 64, вторые информационные входы которых 136-2, 137-2 подключены к выходу регистра 62. Выход третьего элемента 63 сравнения соединен с третьим входом 137-3 коммутатора 64.

Выход коммутатора 64 соединен со входом регистра 66, выход которого подключен ко второму информационному входу 139-2 второго сумматора 67, к первому информационному входу 139-1 которого подключен выход регистра 65. Выход второго сумматора 67 соединен с третьим информационным входом 140-3 коммутатора 68, выход которого подключен через выходной регистр 69 к выходной шине 81.

Управляющие входы: вход 86-2 регистра 6, 87-4 коммутатора 7, вход 88-3 коммутатора 8, вход 89-3 первого дополнительного блока 11 памяти, вход 90-3 коммутатора 12, вход 91-2 блока 13 памяти, вход 93-5 коммутатора 14, вход 94-2 регистра 16, вход 95-2 регистра 17, вход 98-3 коммутатора 20, вход 99-2 регистра 21, вход 100-2 регистра 22, вход 101-2 регистра 23, вход 102-4 коммутатора 25, вход 104-2 регистра 27, вход 105-3 коммутатора 28, вход 107-2 регистра 31, вход 108-2 регистра 32, вход 109-2 регистра 33, вход 110-4 коммутатора 35, вход 111-4 коммутатора 36, вход 112-4 коммутатора 37, вход 113-3 коммутатора 38, вход 114-2 регистра 39, вход 115-2 регистра 40, вход 116-2 регистра 41, вход 117-2 регистра 42, вход 118-2 регистра 43, вход 119-4 коммутатора 44, вход 120-3 коммутатора 45, вход 121-3 коммутатора 46, вход 122-2 регистра 47, вход 123-2 регистра 48, вход 124-4 коммутатора 49, вход 125-2 регистра 50, вход 126-2 регистра 51, вход 127-3 коммутатора 52, вход 128-2 регистра 53, вход 129-4 блока 54 памяти параметров, вход 130-3 коммутатора 55, вход 131-5 коммутатора 56, вход 132-2 регистра 57, вход 133-6 коммутатора 59, вход 134-2 регистра 60, вход 135-2 регистра 62, вход 138-2 регистра 65, вход 140-4 коммутатора 68 подключены к выходу устройства 5 управления.

В устройстве единая система синхронизации.

Все входящие в устройство блоки, элементы, сумматоры, коммутаторы, регистры могут быть выполнены на элементах серии И300Б.

Алгоритм работы УУ ПП приведен на фиг. 5 и подробно раскрыт в описании функционирования устройства ПП.

Исходно управляющие регистры ПП (базовые регистры БР 13, регистр базы текущей активации БТА 27, регистр нижней границы буфера стека НТБС 16, регистр верхней границы буфера стека ВГБС 17, регистр лексинографического уровня и номера сегмента НУНС 47, регистр системных триггеров ТГ 48, регистр базы словаря системы БСС 50, регистр базы словарая пользователя БСП 53) прописываются ко команде записи в регистр ЗПРЕГ, поступающей из устройства управления ЦП по шине 74, информацией, поступающей из регистрового файла ЦП по шине 70. При этом УУ ПП 5 декодирует команду ЗПРЕГ и номер прописываемого регистра, обеспечивает коммутацию операнда с входного регистра 1 на первый регистр записи РЗ1БР 9 через коммутатор 7 и выработку соответствующего строба записи: БР прописываются через рабочие базовые регистры РБР 11 и коммутатор БР 12 (последовательно вырабатываются управляющие сигналы 89-3, 90-3 и 91-2), регистры ВГБС 17 и НГБС 16, ППАР 54, БСС 50 прописываются непосредственно с выхода регистра РЗ1БР 9 (вырабатываются соответственно стробы записи 95-2, 94-2, 129-2 или 125-2), регистр БТА 27 прописывается через коммутатор 20, регистр БТА третьего дополнительного регистра дешифрируемой команды БТАЗРДК 23 и коммутатор 25 (последовательно вырабатываются управляющие сигналы 98-3 и 101-2, 102-4, 104-2);

регистр НУНС 47 прописывается через коммутатор 37, регистр НУНСЗРДК 41 и коммутатор 44 (последовательно вырабатываются управляющие сигналы 112-4 и 117-2, 120-4 и 122-2), регистр ТГ 48 прописывается через коммутатор 46 (вырабатываются управляющие сигналы 121-3 и 123-2), регистр БСП 53 прописывается через коммутатор 49, регистр 51 и коммутатор 52 (вырабатываются управляющие сигналы 124-4 и 126-2, 127-3 и 128-2), базовый регистр операционной системы БРОС 6 проописывается непосредственно с выхода регистра БСТО 1 (вырабатывается строб записи 86-2).

Значения БР 13 и БТА 27 могут быть считаны в регистровый файл ЦП по шине 76, значения регистров НУНС 47 и ТГ 48, БСП 53 и значения остальных регистров, имеющих копии в ППАР 54, могут быть считаны в устройство преобразования чисел по шине 78 через коммутатор 56 и регистр 57.

В устройстве ПП реализованы следующие виды процедурных переходов

вход в статически известную (открытую) процедуру (ОВХ),

вход в формальную процедуру (ВХФ),

вход в системную процедуру (ОВХС),

возврат в запустившую процедуру (выход из процедуры ВЫХ)

безусловный динамический переход по метке (ПРХМ).

Каждый из них реализуется двумя командами - подготовки и выполнения процедурного перехода. Подготовка процедурного перехода включает следующие действия,

формирование указателя БТАjРДК на регистрах 21, 22 или 23,

формирование нового контекста на РБР 11 (в случае ОВХ не производится),

формирование нового регистра состояния на регистрах НУНСjРДК 39, 40 или 41 и (при подготовках ВЫХ и ПРХМ) на регистре ТГЗРДК 43,

формирование связующей информации для сохранения в буферной памяти ЦП при входе в процедуру или считывание информации из буферной памяти ЦП при выходе из процедуры и ПРХМ,

вызов дескриптора программного сегмента (ДПС) и кода новой процедуры (инициализация буфера команд (БК) ЦП по шинам АДПСППБК 80 и ИКППБК 81 и БП ЦП по шине 79).

Выполнение процедурного перехода сводится к переписи регистров jРДК на соответствующие основные регистры.

Все команды подготовки процедурных переходов инициализируются УУ ПП по шине РК 74. Устройство управления ПП Л (УУ ПП) 5 декодирует код операции и формирует на регистрах сдвига соответствующую последовательность тактовых импульсов QIКОП-QiКОП, длина последовательности зависит от типа операции (некоторые вложенные подпоследовательности могут повторяться) УУ ПП формирует триггер, соответствующий коду операции на третьем РДК, необходимый для выполнения процедурного перехода.

При получении команды ОВХ литеральная информация о процедуре (фиг. 2) запоминается на соответствующих регистрах,

- номер уровня НУР и номер сегмента НС - на регистре НУНСjРДК 39, 40 или 41, номер сегмента поступает также на регистр 42;

- индекс команды возврата ИКВ, смещение по буферу стека ДЦС, тип возврата ТВ - на регистре РСЛjРДК 31, 32, или 33, ДЦС поступает также на регистр 34.

По команде ОВХ формируется последовательность из двух импульсов - Q10BXj и Q20BXj, гдле j - номер РДК. По сигналу Q10BXj коммутатор 28 настраивается на регистр БТАОСН 27, коммутатор 36 на регистр 34 и в следующем такте на выходном регистре сумматора 29 появляется новое значение БТА. По сигналу Q20BXj вырабатывается строб приема на регистр БТАjРДК 21, 22 или 23 (для последнего по сигналу 20 ВХЗ коммутатор 20 настраивается на вход 98-1). На этом формирование нового БТА завершается.

Одновременно формируется запрос в БК ЦП по шинам АДПСППБК 80 и ИКППБК 81 за кодом вызываемой процедуры и в буферную память (БП) ЦП - за ее ДПС. По сигналу Q10BXj коммутатор 59 настаивается на вход 133-1, коммутатор 55 - на вход 130-2, коммутатор 45 - на вход 120-2 и на регистре математического адреса РМА 60 в следующем такте появляется адрес ДПС вызываемой процедуры (фиг. 3), по тому же сигналу коммутатор 68 настраивается на вход 140-2 и на регистре ИКППБК 69 принимается значение индекса, равное нулю.

На этом подготовка ОВХ заканчивается.

При выполнении ОВХ по шине РК в УУ ПП поступает поле ПРХ (фиг. 2), в УУ ПП оно декодируется и по признаку "ОВХ" на соответствующем РДК формируется последовательность из двух управляющих импульсов Q1ПРХОВХj и Q2ПРХОВХj. По сигналу Q1ПРХОВХj коммутатор 14 настраивается на вход 93-4, коммутатор 35 - на вход 110-j, коммутатор 59 - на вход 133-5, таким образом, в следующем такте на выходе регистра 15 (шине ЧППБП 77) появляется значение УСВ (поля ИКВ, ДЦС, ТВ - с регистра РСЛjРДК 31, 32 или 33, поле НУНС - с регистра 47, поле ТГ - с регистра 48), которое записывается по адресу, появившемуся на выходе РМА 60 (шине МАППБП 79) и равному значению БТАjРДК, по шине 91-2 в БР 13 подается адрес считывания, равный старому значению номера уровня. По сигналу Q2ПРХОВХj коммутатор 14 настраивается на вход 93-2, коммутатор 59 - на вход 133-2, таким образом в буфер стека ЦП записывается сохраняемый базовый регистр по адресу, на единицу большему значения БТАjРДК, кроме того, по сигналу Q1ПРХОВХj коммутатор БР 12 настраивается на вход 90-1 и в БР 13 записывается старое значение БТА 27, также по сигналу Q1ПРХОВХj производятся следующие действия:

- коммутатор 25 настраивается на вход 102-j и новое значение БТА с регистра 21, 22 или 23 переписывается на регистр БТА 27;

- коммутатор 44 настраивается на вход 119-j и на регистр НУНС 47 принимается новое значение с регистров НУНС РДК 39, 40 или 41, коммутатор 46 настраивается на вход 121-2 и на регистр ТГ 48 принимается значение ТГ с регистра 30, на который по шине 75 поступает ДПС из БК одновременно с командой перехода.

Все действия по переключению регистров ПП происходят в течение одного такта, запись в буфер стека ЦП - в течение двух тактов (последняя работа является фоновой и не влияет на производительность ЦП).

Команда входа в формальную процедуру выполняется только на третьем РДК. По коду ВХФ формируется последовательность из трех управляющих импульсов Q1ВХФ-Q3ВХФ. Прием литеральной информации с шины РК 74 (кроме поля НУНС) и формирование нового значения БТАЗРДК соответствует команде ОВХ на третьем РДК.

Одновременно по шине 70 из регистрового файла ЦП поступает метка процедуры (фиг. 3), в которой указаны ее лексикографический уровень (поле НУР), адрес ее ДПС (поле АДПС) и адрес контекстной пачки (поле АКП), определяющий доступные ей области памяти. По сигналу Q1ВХФ коммутатор 7 настраивается на вход 87-2 и в следующем такте метка появляется на выходе регистра Р31БР 9. По сигналу Q2ВХФ коммутатор 37 настраивается на вход 112-2 и регистр НУНСЗРДК 41 прописывается соответствующими полями из метки; коммутатор 49 настраивается на вход 124-2 и регистр БСПЗРДК 51 и прописывается полем АДПС. БСП из метки.

Одновременно коммутатор 59 настраивается на вход 133-3 и в следующем такте на РМА 60 появляется адрес ДПС вызываемой процедуры (фиг. 3), по сигналу QЗВХФ коммутатор 59 настраивается на вход 133-4 и на РМА 60 в следующем такте появляется адрес контекстной пачки, одновременно в УУ ПП устанавливается счетчик запросов за контекстной пачкой, равный нулю, и его предельное значение, равное номеру уровня из метки, и триггер значимости этого счетчика - ТЗАПАЧ. По этому триггеру коммутатор 59 настраивается на вход 133-2 и на выходе РМА 60 формируется модифицированное значение адреса, с каждым тактом на единицу большее предыдущего; одновременно значение счетчика запросов за контекстной пачкой увеличивается. При значении его, равном пределу, триггер ТЗАПАЧ сбрасывается и выдача запросов в БП ЦА прекращается.

Так как при ВХФ формируется новый контекст на БР 13 их содержимое предварительно переписывается в буферную память ЦП.

По сигналу QЗВХФ в УУ ПП устанавливается значение счетчика упрятывания контекста, на единицу меньшее номера уровня из метки, и по условию сброса триггера ТЗАПЧ вырабатывается последовательность из двух управляющих импульсов Q1УПКО и Q2УПКО; по сигналу Q1УПКО коммутатор 25 настраивается на вход 102-3, коммутатор 59 - на вход 133-5, по сигналу 2УПКО коммутатор 59 настраивается на вход 133-2 и устанавливается триггер ТУПКО. По значению ТУПКО коммутатор 14 настраивается на вход 93-2,

в БР 13 по шине 91-2 подается адрес считывания базового регистра, равный значению СЧУПКО,

коммутатор 59 настраивается на вход 133-2,

из значения СЧУПКО ежетактно вычитается единица.

Таким образом, в буфер стека ЦА по последовательным адресам, начиная с адреса, равного БТАЗРДК+2 переписываются сохраняемые базовые регистры из БР 13. При нулевом значении счетчика сохранение старого контекста прекращается.

Подготовка ВХФ заканчивается после прихода всех элементов контекстной пачки из АЗУ глобалов ЦП по шине 72 или из локальной памяти ЦП по шине 73. При приеме каждого дескриптора данных значение счетчика запросов убывает на единицу, и при значении его, равном нулю, подготовка ВХФ прекращается.

Все время подготовки ВХФ (сQЗВХФ и до конца операции) коммутаторы 7 и 8 настроены на вход 87-3 и 88-2 соответственно, через них и регистры Р31БР 9 и Р32БР 10 приходящие дексриптора данных записываются в рабочие базовые регистры 11.

При выполнении ВХФ в УУ ПП формируется последовательность из двух сигналов Q1ПРХВХФ и Q2ПРХВХФ, действия по которым аналогичны действиям по сигналам Q1ПРХОВХЗ и Q2ПРХОВХЗ, за следующими отличиями:

- по сигналу Q2ПРХВХФ коммутатор 14 настраивается на вход 93-3 и в буфер стека ЦП через регистр 15 записывается вместе с УСВ БСПОСН 53 (фиг. 4),

коммутатор БР 12 настраивается на вход 90-2 и в БР 13 переписывается новый контекст из РБР 11,

коммутатор 52 настраивается на вход 127-2 и на регистр БСПОСН 53 записывается новое значение БСП с регистра 51 БСПЗРДК.

Команда ОВХС является оптимизацией команды ВХФ для часто используемых процедур операционной системы. Необходимая для коррекции контекста информация хранится не в памяти, как в случае ВХФ, а на регистрах устройства ПП - новое значение базы словаря на регистре БСС 50, базовый регистр нулевого уровня на базовом регистре операционной системы БРОС 6, поэтому запрос за ними в память не производится.

По коду ОВХС формируется последовательность из трех управляющих импульсов Q10ВХС - Q30ВХС. Прием литеральной информации с шины РК 74 и формирование нового значения БТАЗРДК полностью соответствуют команде РВХ на третьем РДК, номер уровня вызываемой процедуры при этом всегда равен единице. Формирование запроса в БК ЦП за кодом вызываемой процедуры также аналогично команде ОВХ, за тем исключением, что по сигналу Q10ВХС коммутатор 55 настраивается на вход 130-1.

По сигналу Q20ВХС коммутатор 7 настраивается на вход 87-1 и в следующем такте содержимое регистра БРОС 6 появляется на выходе регистра Р31БР 9 и записывается в РБР 11 по сигналу Q30ВХС.

По сигналу Q20ВХС коммутатор 49 настраивается на вход 124-1 и содержимое регистра БСС 50 переписывается в регистр БСПЗРДК 51.

На этом формирование нового контекста завершается.

Выполнение ОВХС полностью аналогично выполнению ВХФ.

По коду ВЫХ формируется последовательность из трех управляющих импульсов Q1ВЫХ-Q3ВЫХ.

По сигналу Q1ВЫХ коммутатор 25 настраивается на вход 102-3, коммутатор 59 - на вход 133-5 и в следующем такте на выходе РМА 60 появляется адрес УСВ, равный значению БТАЗРДК. В следующем такте формируется запрос за вторым сохранением словом связующей информации (базовым регистром или БСП в зависимости от типа возврата, фиг. 4), для чего по сигналу Q2ВЫХ коммутатор 59 настраивается на вход 133-2 и на РМА 60 появляется адрес, равный БТАЗРДК+1.

Считанное УСВ появляется на входной шине АГ 72. По приему УСВ коммутатор 7 настраивается на вход 87-3 и в следующем такте значение УСВ появляется на регистре Р31БР 9, коммутатор 37 настраивается на вход 112-3 и поля НУР и НС записываются на регистр НУНСЗРДК 41, коммутатор 38 настраивается на вход 113-2 и поле ТГ принимается на регистр ТГЗРДК 43, коммутатор 68 настраивается на вход 140-3 и поле ИКВ принимается на регистр ИКППБК 69, коммутатор 36 настраивается на вход 111-1, коммутатор 28 настраивается на вход 105-1 и на сумматоре 29 вычисляется новое значение БТА, в следующем такте коммутатор 20 настраивается на вход 98-1 и новое значение БТА поступает на регистр БТАЗРДК 23.

Поле УСВ. НУР поступает также вместе с полем УСВ. ТВ в УУ ПП для определения дальнейшего алгоритма исполнения команды. Если УСВ. ТВ = 1, то второе считанное слово - БР, когда оно поступает в ПП по шине АГ 72 (или ЛП 73) коммутатор 7 (8) настраивается на вход 87-3 (88-2), в следующем такте значение БР появляется на регистре Р31БР 9 (Р32БР 10) и записывается в РБР 11 по адресу, равному номеру уровня из УСВ и на этом реакция контекста заканчивается. Если же УСВ. ТВ = 2, то второе считанное из БСТС слово - БСП, когда оно поступает в ПП по шине АГ 72 (или ЛП 73) коммутатор 49 настраивается на вход 124-2 (124-3) и значение БСП записывается на регистр БСПЗРДК 51, в следующем такте коммутатор 59 настраивается на вход 133-2 и формируется СЧЗАПАЧ, равный номеру уровня из УСВ, и его значимость - ТЗАПАЧ, действия по нему полностью аналогичны действиям при подготовке БХФ, по завершении запросов коммутатор 55 настраивается на вход 131-3, коммутатор 45 - на вход 120-1, коммутатор 59 - на вход 133-1 и на регистре РМА 60 формируется адрес ДПС процедуры, в которую происходит возврат, индекс команды возврата уже принят на регистр ИКППБК 69.

После окончания коррекции (прихода всех упрятанных базовых регистров) подготовка выхода завершается.

При выполнении ВЫХ в УУ ПП формируются сигналы Q1ПРАХВЫХ и Q21ПРХВЫХ, действия по которым аналогичны действиям по сигналу ПРХВХФ, за исключением:

запись в БП ЦП не производится,

коммутатор 46 настраивается на вход 121-1 и на регистр ТГ 48 переписывается значение регистра ТГЗРДК 43.

Цель команды ПРХМ - поиск в стеке активации с БТА, равной эталону, указанному в метке перехода. Команда выполняется только на третьем РДК. По коду ПРХМ формируется последовательность из трех управляющих импульсов Q1ПРХМ - Q3ПРХМ, по шине 70 из регистрового файла ПП поступает метка перехода, в которой указаны индекс команды перехода и ассоциативный адрес (эталон) для поиска активации, в которую необходимо перейти. По сигналу Q1ПРХМ коммутатор 7 настраивается на вход 87-2 и в следующем такте метка появляется на выходе регистра Р31БР 9 и по сигналу Q2ПРХМ принимается на регистр эталона перехода по метке РЭТМ 24. Дальнейшее выполнение подготовки аналогично последовательному выполнению подготовок команды выхода из процедуры; полученное при вычислении БТА на сумматоре 29 значение поступает на вход 103-1 схемы сравнения 26 и сравнивается с РЭТМ 24; при сравнении выполнение подготовки после проведения коррекции прекращается, при несравнении - считывается следующее УСВ.

Выполнение ПРХМ полностью аналогично выполнению выхода из процедуры.

Исследование устройства подпрограмм в составе центрального процессора показали, что по сравнению с устройством аналогичного назначения (прототипом) заявляемое устройство позволяет проводить одновременную подготовку нескольких процедурных переходов, сокращает время выполнения операций процедурных переходов. Это повысило быстродействие устройства и привело к расширению его функциональных возможностей. (56) Техническое описание МВК "Эльбрус 1".

Техническое описание МВК "Эльбрус 2".

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1992 |

|

RU2060538C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ И ОКРУГЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ | 1992 |

|

RU2018921C1 |

Изобретение относится к вычислительной технике и предназначено для использования в центральных процессорах вычислительных машин высокой производительности. Цель изобретения - расширение области применения устройства за счет обеспечения одновременно подготовки нескольких процессорных переходов и уменьшения количества обращений к оперативной памяти устройства. Устройство для вызова подпрограмм содержит блок памяти, блок памяти параметров, три элемента сравнения, два сумматора, семь входных регистров, одиннадцать регистров, четыре выходных регистра, двенадцать коммутаторов, блок управления, дополнительный блок памяти, дополнительный входной регистр, дополнительный элемент сравнения, четырнадцать дополнительных регистров, девять дополнительных коммутаторов, блок выработки модификации значения адреса. 10 ил.

УСТРОЙСТВО ДЛЯ ВЫЗОВА ПОДПРОГРАММ, содержащее блок памяти, блок памяти параметров, три элемента сравнения, два сумматора, семь входных регистров, одиннадцать регистров, четыре выходных регистра, двенадцать коммутаторов, блок управления, информационный вход первого входного регистра и первый информационный вход блока управления соединены с входной информационной нулевой шиной числа из буфера стека, информационный вход второго входного регистра и второй информационный вход блока управления подключены к входной информационной первой шине числа из буфера стека, информационный вход третьего входного регистра и третий информационный вход блока управления соединены с входной информационной шиной числа из ассоциативного запоминающего устройства глобалов, информационный вход четвертого входного регистра и четвертый информационный вход блока управления подключены к входной информационной шине числа из локальной памяти, пятый информационный вход блока управления, первый информационный вход блока памяти параметров, информационные входы шестого и седьмого входных регистров соединены с входной шиной управляющей информации из устройства управления центрального процессора, выход первого входного регистра соединен с информационным входом первого регистра, выход которого подключен к первому информационному входу первого коммутатора, второй и третий информационные входы которого соединены с выходами первого и третьего входных регистров соответственно, выход первого коммутатора подключен к информационному входу второго регистра, выходы второго и четвертого входных регистров соединены с первым и вторым информационными входами второго коммутатора, выход которого подключен к информационному входу третьего регистра, первый информационный вход третьего коммутатора соединен с выходом шестого регистра, выход третьего коммутатора подключен к информационному входу блока памяти, первый информационный выход которого соединен с выходной информационной шиной числа в буфер стека, второй и третий информационные выходы блока памяти подключены соответственно к первым и вторым информационным входам четвертого коммутатора, третий информационный вход которого соединен с выходом десятого регистра, третья информационная шина подключена к четвертому информационному входу четвертого коммутатора, выход которого соединен с информационным входом первого выходного регистра, выход которого соединен с выходной информационной шиной числа в буферную память, выход второго регистра подключен к информационным входам четвертого, пятого, девятого и пятого входных регистров, к второму информационному входу блока памяти параметров, выход которого соединен с третьим информационным входом девятого коммутатора, выходы четвертого и пятого регистров соединены соответственно с первыми информационными входами первого и второго элементов сравнения, выходы которых образуют первую информационную шину устройства, которая соединена с седьмым входом блока управления, выход пятого коммутатора соединен с пятым информационным входом десятого коммутатора и с информационным входом шестого регистра, выход которого подключен к первому информационному входу шестого коммутатора и к второму информационному входу девятого коммутатора, выход шестого коммутатора соединен с первым входом первого сумматора, первый информационный вход девятого коммутатора подключен к второй информационной шине, которая образована соединением выходов седьмого и восьмого регистров, выход девятого регистра подключен к первым информационным входам седьмого и восьмого коммутаторов, выход седьмого коммутатора подключен к информационному входу десятого регистра, выход которого соединен с вторым информационным входом восьмого коммутатора и с четвертым информационным входом девятого коммутатора, выход которого подключен к информационному входу второго выходного регистра, выход которого соединен с выходной информационной шиной числа в устройство преобразования чисел, выход восьмого коммутатора образует третью информационную шину устройства и подключен к третьему информационному входу десятого коммутатора, выход которого соединен с информационным входом третьего выходного регистра, выход которого подключен к выходной шине математического адреса в ассоциативное запоминающее устройство страниц, выход пятого входного регистра соединен с первым информационным входом одиннадцатого коммутатора и с первым входом третьего элемента сравнения, к второму входу которого и к второму информационному входу одиннадцатого коммутатора подключен выход шестого входного регистра, выход седьмого входного регистра подключен к первому входу второго сумматора, выход третьего элемента сравнения соединен с третьим информационным входом одиннадцатого коммутатора, выход которого подключен к информационному входу одиннадцатого регистра, выход которого подключен к второму входу второго сумматора, выход которого соединен с первым информационным входом двенадцатого коммутатора, к второму информационному входу которого подключена шина логического нуля устройства, выход двенадцатого коммутатора соединен с информационным входом четвертого выходного регистра, выход которого подключен к выходной шине индекса команды в буфер команд, входы записи шестого, седьмого входных регистров, первого, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого регистров соединены с выходами блока управления с первого по десятый, с одиннадцатого по двадцать второй выходы которого соединены с управляющими входами коммутаторов с первого по двенадцатый, входы записи блока памяти и блока памяти параметров соединены с двадцать третьим и двадцать четвертым выходами блока управления, двадцать пятый и двадцать шестой выходы которого соединены с адресными входами блока памяти и блока памяти параметров, входы записи второго и третьего выходных регистров соединены с двадцать седьмым и двадцать восьмым выходами блока управления, синхровход устройства соединен с синхровходами шестого и седьмого входных регистров, первого и с четвертого по десятый регистров, второго и третьего выходных регистров, блока памяти и блока памяти параметров, а также с входами записи с первого по пятый входных регистров, второго, третьего регистров и одиннадцатого регистров, первого и четвертого выходных регистров, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения одновременной подготовки нескольких процедурных переходов и уменьшения количества обращений к оперативной памяти, в устройство введены дополнительный блок памяти, дополнительный входной регистр, дополнительный элемент сравнения, четырнадцать дополнительных регистров, девять дополнительных коммутаторов, блок выработки модификации значения адреса, причем первый и второй информационные входы первого дополнительного блока памяти соединены с выходами второго и третьего регистров соответственно, выход второго регистра соединен с информационным входом четвертого дополнительного регистра, с вторыми информационными входами первого , пятого и девятого дополнительных коммутаторов, с третьими информационными входами третьего, четвертого дополнительных и двенадцатого коммутаторов, с первым и вторым информационным входами десятого коммутатора, выход третьего регистра подключен к второму информационному входу четвертого дополнительного коммутатора, к первому информационному входу пятого дополнительного коммутатора, к третьему информационному входу девятого дополнительного коммутатора, выход первого дополнительного блока памяти подключен к второму информационному входу третьего коммутатора, первый информационный вход первого дополнительного коммутатора, информационные входы первого и второго дополнительных регистров, первый вход дополнительного элемента сравнения подключен к выходу первого сумматора, второй вход дополнительного элемента сравнения соединен с выходом четвертого дополнительного регистра, выход дополнительного элемента сравнения подключен к восьмому информационному входу блока управления, выход первого дополнительного коммутатора соединен с информационным входом третьего регистра, выходы первого, второго, третьего дополнительных регистров соединены соответственно с первым, вторым, третьим информационными входами пятого коммутатора, выход третьего дополнительного регистра подключен к пятому информационному входу десятого коммутатора, к второму информационному входу шестого коммутатора, информационный вход двенадцатого дополнительного регистра и первый информационный вход четвертого дополнительного коммутатора подключены к входной шине управлящей информации из устройства управления центрального процессора, выходы пятого и шестого дополнительных регистров соединены соответственно с первым и вторым информационными входами второго дополнительного коммутатора, третий информационный вход которого и первый информационный вход третьего дополнительного коммутатора подключены к выходу седьмого дополнительного регистра, выход восьмого дополнительного регистра соединен с вторым информационным входом третьего дополнительного коммутатора, выход второго дополнительного коммутатора соединен с второй информационной шиной устройства, выходы девятого и десятого дополнительных регистров подключены к первому и к второму информационным входам шестого дополнительного коммутатора, выход четвертого дополнительного коммутатора соединен с информационным входом одиннадцатого дополнительного регистра, выход которого подключен к третьему информационному входу шестого дополнительного коммутатора и первому информационному входу седьмого дополнительного коммутатора, второй информационный вход которого соединен с выходом двенадцатого дополнительного регистра, выход шестого дополнительного коммутатора подключен к информационному входу седьмого регистра, выход седьмого дополнительного коммутатора соединен с третьей информационной шиной устройства, выход пятого дополнительного коммутатора соединен с информационным входом тринадцатого дополнительного регистра, выход которого подключен к первому информационному входу восьмого дополнительного коммутатора, второй информационный вход которого и шестой информационный вход блока управления соединены через дополнительный входной регистр с входной шиной дискриптора программного сегмента из буфера стека, выход восьмого дополнительного коммутатора подключен к информационному входу восьмого регистра, выход девятого дополнительного коммутатора подключен к информационному входу четырнадцатого дополнительного регистра, выход которого соединен с вторым информационным входом седьмого коммутатора и с третьим информационным входом восьмого коммутатора, выход третьего выходного регистра подключен к выходной шине адреса дискриптора программного сегмента в буфер команд и через блок выработки модифицированного значения адреса к второму информационному входу десятого коммутатора, вход адреса и вход записи дополнительного блока памяти соединены с двадцать девятым и тридцатым выходами блока управления, выходы с тридцать первого по пятьдесят первый блоки блока управления соединены с входами записи соответственно с первого по третий, с пятого по седьмой, с девятого по четырнадцатый дополнительных регистров и с управляющими входами с первого по девятый дополнительных коммутаторов, синхровход устройства соединен с синхровходами дополнительных регистров с первого по третий, с пятого по седьмой и с девятого по четырнадцатый, с синхровходом дополнительного блока памяти и с входами записи четвертого и восьмого дополнительных регистров и дополнительного входного регистра.

Авторы

Даты

1994-03-15—Публикация

1990-12-28—Подача