Изобретение относится к вычислительной технике и может быть использовано, например, для обработки данных физических экспериментов, для решения задач автоматизированного управления в реальном масштабе времени и для научных расчетов, требующий высокой производительности и большого объема памяти.

Известна высокопроизводительная вычислительная система, содержащая центральные процессоры, процессоры ввода-вывода данных, коммутатор, основное запоминающее устройство, пульт управления, внешние устройства, внешние запоминающие устройства, блоки управления внешними запоминающими устройствами, процессоры передачи данных.

Все компоненты системы динамически распределяются операционной системой для обслуживания очередных задач. Все центральные процессоры равноправны и работают в мультипроцессорном режиме.

Отличительной особенностью системы команд и внутренней структуры системы является приспособленность их для программирования на языках высокого уровня, что позволяет достигнуть значительного упрощения системы математического обеспечения и осуществлять эффективную компиляцию программ в машинный код.

Универсальный стековый механизм, тегированные данные, выполненные команды в зависимости от типа и формата данных, ресурсивное использование процедур, работа нескольких пользователей с общими данными, практически неограниченный объем математической памяти, разветвленная система прерываний значительно облегчают программирование.

Высокое быстродействие системы достигается максимальным распараллеливанием обработки команд; перенесением задачи распределения регистров ЦП с этапа компилляции программы на этап ее выполнения, где эта задача решается динамически наиболее эффективным образом; выполнением обработки данных в простых случаях без дополнительных издержек, связанных с анализом типа и формата данных; широким применением сверхоперативных ассоциативных запоминающих устройств.

Для достижения параллелизма в обработке команд используется организация работы по принципу поточной линии, когда в процессе обработки на разных стадиях выполнения одновременно находятся несколько команд, а также имеются специализированные блоки сложения, умножения, деления, индексации, формирования процедур, работающие параллельно и независимо один от другого.

Недостатком этой системы является большой объем и сложность аппаратуры и, как следствие, невысокая надежность.

Наиболее близкой по технической сущности к предлагаемому устройству является вычислительная система, содержащая процессор, устройство системной памяти, устройство буферной памяти данных, устройство буферной памяти команд и устройство управления буферными памятями, причем первый информационный вход-выход процессора через магистраль адреса-данных подключен к первому информационному входу-выходу устройства управления буферными памятями, к информационному входу-выходу устройства буферной памяти данных и к первому информационному входу-выходу устройства системной памяти, выход адреса процессора подключен к информационному входу устройства управления буферными памятями и к первому адресному входу устройства буферной памяти команд, информационный вход-выход которого через магистраль управления подключен ко входу команд процессора и к выходу устройства системной памяти, первый и второй выходы устройства управления буферными памятями подклены соответственно к управляющему входу устройства буферной памяти команд и к адресному входу устройства буферной памяти данных, вход-выход режима устройства управления буферными памятями подключен к управляющему входу-выходу устройства системной памяти, при этом процессор содержит блок обработки целых чисел, блок обработки вещественных чисел, блок логической обработки, первый и второй блоки сопряжения, первый блок регистров, причем в процессоре первый информационный вход-выход подключен к адресно-числовому входу-выходу первого блока сопряжения, вход команд процессора подключен к первому информационному входу второго блока сопряжения, первый выход которого подключен к выходу адреса процессора, второй выход второго блока сопряжения через информационную магистраль подключен к первым информационным входам-выходам блока обработки целых чисел, блока обработки вещественных чисел, блока логической обработки, первого блока сопряжения и первого блока регистров, с первого по пятый выходы группы второго блока сопряжения подключены соответственно к управляющим входам блока обработки целых чисел, блока обработки вещественных чисел, блока логической обработки, первого блока сопряжения и к первому управляющему входу первого блока регистров.

Однако, известная вычислительная система не отличается высокой производительностью и удобством в эксплуатации по следующим причинам.

В рассматриваемой системе, построенной на базе архитектуры с сокращенным набором команд, сложные операции, а также исключительные ситуации, такие как преобразование форматов и типов, реализуются путем выполнения последовательности простых команд, генерируемых компилятором в процессе трансляции программ. В этом случае, однако, увеличивается количество обращений в устройство буферной памяти команд, что приводит к снижению производительности из-за потерь времени, связанных с подкачкой команд из оперативной памяти при отсутствии их в буферной памяти. Кроме того, отсутствие возможности работы с различными типами операндов требует более жесткой дисциплины программирования и дополнительного контроля при трансляции.

Это усложняет процесс создания и отладки программ, т.е. эксплуатацию вычислительной системы.

Целью изобретения является повышение быстродействия и надежности за счет контроля типов и форматов операндов при трансляции в процессоре.

Поставленная цель достигается тем, что в вычислительную систему, содержащую процессор, устройство системной памяти, устройство буферной памяти данных, устройство буферной памяти команд и устройство управления буферными памятями, причем первый информационный вход-выход процессора через магистраль адреса-данных подключен к первому инфор- мационному входу-выходу устройства управления буферными памятями, к информационному входу-выходу устройства буферной памяти данных и к первому информационному входу-выходу устройства системной памяти, выход адреса процессора подключен к информационному входу устройства управления буферными памятями и к первому адресному входу устройства буферной памяти команд, информационный вход-выход которого через магистраль управления подключен ко входу команд процессора и к выходу устройства системной памяти, первый и второй выходы устройства управления буферными памятями подключены соответственно к управляющему входу устройства буферной памяти команд и к адресному входу устройства буферной памяти данных, вход-выход режима устройства управления буферными памятями подключен к управляющему входу-выходу устройства системной памяти, при этом процессор содержит блок обработки целых чисел, блок обработки вещественных чисел, блок логической обработки, первый и второй блоки сопряжения, первый блок регистров, причем в процессоре первый информационный вход-выход подключен к адресно-числовому входу-выходу первого блока сопряжения, вход команд процессора подключен к первому информационному входу второго блока сопряжения, первый выход которого подключен к выходу адреса процессора, второй выход второго блока сопряжения через информационную магистраль подключен к первым информационным входам-выходам блока обработки целых чисел, блока обработки вещественных чисел, блока логической обработки, первого блока сопряжения и первого блока регистров, с первого по пятый выходы группы второго блока сопряжения подключены соответственно к управляющим входам блока обработки целых чисел, блока обработки вещественных чисел, блока логической обработки, первого блока сопряжения и к первому управляющему входу первого блока регистров, введены постоянное запоминающее устройство подпрограмм и запоминающее устройство признаков наличия информации, при этом выход управления буферной памятью процессора подключен ко входу режима устройства управления буферными памятями, выход адреса процессора и первый выход устройства управления буферными памятями подключены соответственно к первому и ко второму адресным входам постоянного запоминающего устройства подпрограмм, выход которого через магистраль управления подключен ко входу команд процессора, к информационному входу-выходу устройства буферной памяти команд, к третьему выходу устройства управления буферными памятями и к выходу устройства системной памяти, второй выход устройства управления буферными памятями подключен к адресному входу запоминающего устройства признаков наличия информации, информационный вход-выход которого через магистраль признаков наличия информации подключен ко второму информационному входу-выходу блока управления буферными памятями, ко второму информационному входу-выходу устройства системной памяти и ко второму информационному входу-выходу процессора, при этом процессор содержит второй блок регистров, блок контроля и блок постоянной памяти, причем в процессоре первый информационный вход-выход второго блока регистров через информационную магистраль подключен к первым информационным входам-выходам блока обработки целых чисел, блока обработки вещественных чисел, блока логической обработки, первого блока регистров, первого блока сопряжения и ко второму выходу второго блока сопряжения, шестой и седьмой выходы группы которого подключены соответственно к управляющему входу блока контроля и к первому управляющему входу второго блока регистров, второй информационный вход-выход блока обработки целых чисел через магистраль контроля подключен ко вторым информационным входам-выходам блока обработки вещественных чисел, блока логической обработки, первого и второго блока регистров, первого блока сопряжения и к информационному входу блока контроля, выход которого подключен ко вторым управляющим входам первого и второго блока регистров, к управляющему входу второго блока сопряжения и ко входу считывания блока постоянной памяти, первый выход которого подключен ко второму информационному входу второго блока сопряжения, первый выход которого подключен к адресному входу блока постоянной памяти, второй выход которого подключен к выходу управления буферной памятью процессора, второй информационный вход-выход которого подключен к третьему информационному входу-выходу первого блока сопряжения.

Сущность изобретения заключается в том, что в предлагаемой вычислительной системе, разработанной на базе архитектуры, использующей сокращенный набор аппаратно-реализуемых простых команд большинство исключительных ситуаций обрабатывается без прерывания процессора и выхода на процедуры операционной системы. Это осуществляется за счет перехода в такой режим, когда команды берутся не из устройства буферной памяти команд, а из блока постоянной памяти или из постоянного запоминающего устройства. К исключительным ситуациям относятся, в частности случаи обработки разноформатных и разнотипных операндов. Информация о типе и формате хранится в разрядах тела операнда и позволяет автоматически определять алгоритм операции. Такой подход обеспечивает повышение производительности системы и удобство работы программиста, который в процессе написания и отладки программ может не заботиться о специальном контроле типов используемых операндов. Кроме того в блоке постоянной памяти и в постоянном запоминающем устройстве могут храниться часто используемые стандартные процедуры, в частности, набор библиотечных функций. В этом случае, при обращении к этим процедурам не требуется их подкачка в устройство буферной памяти команд, что также повышает производительность системы. Наличие, наряду с блоком постоянной памяти постоянного запоминающего устройства позволяет перенастраивать вычислительную систему, используя один и тот же процессор с различными подсистемами памяти и, соответственно, различным содержимым постоянного запоминающего устройства.

Сравнение предлагаемого технического решения с прототипом позволило установить соответствие его критерию "новизна". При излучении других известных технических решений в данной области техники признаки, отличающие предлагаемое изобретение от прототипа, не были выявлены и потому они обеспечивают предлагаемому техническому решению соответствие критерию "существенные отличия".

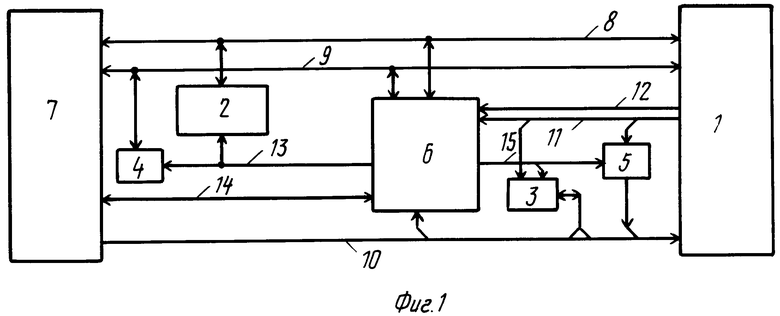

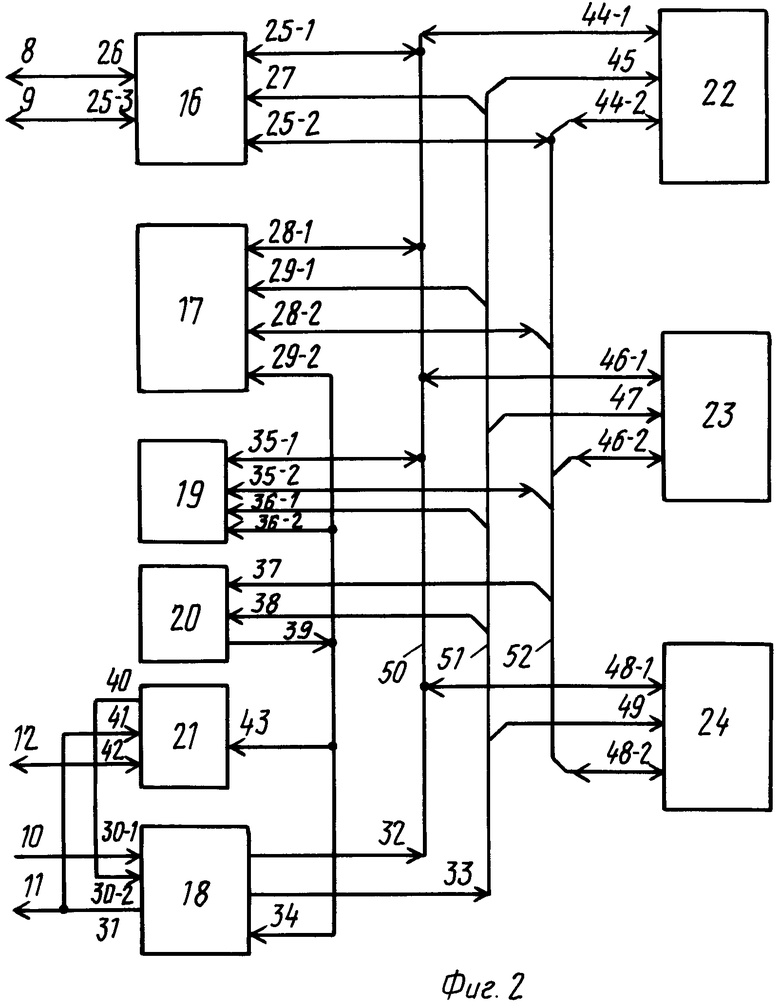

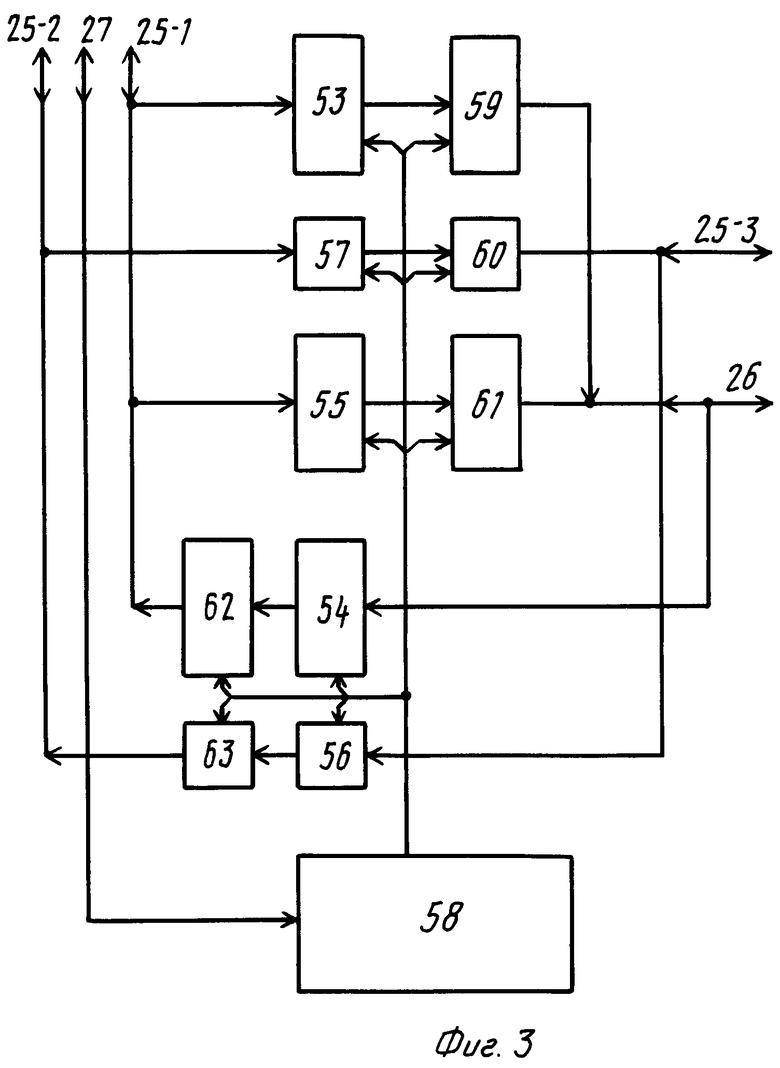

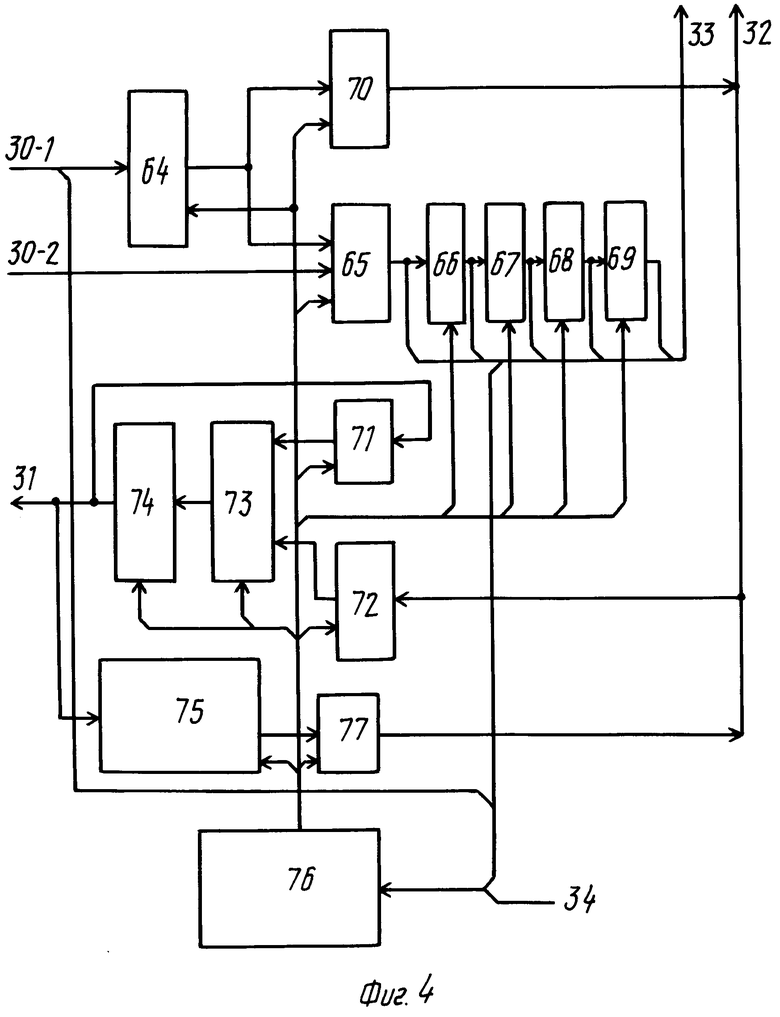

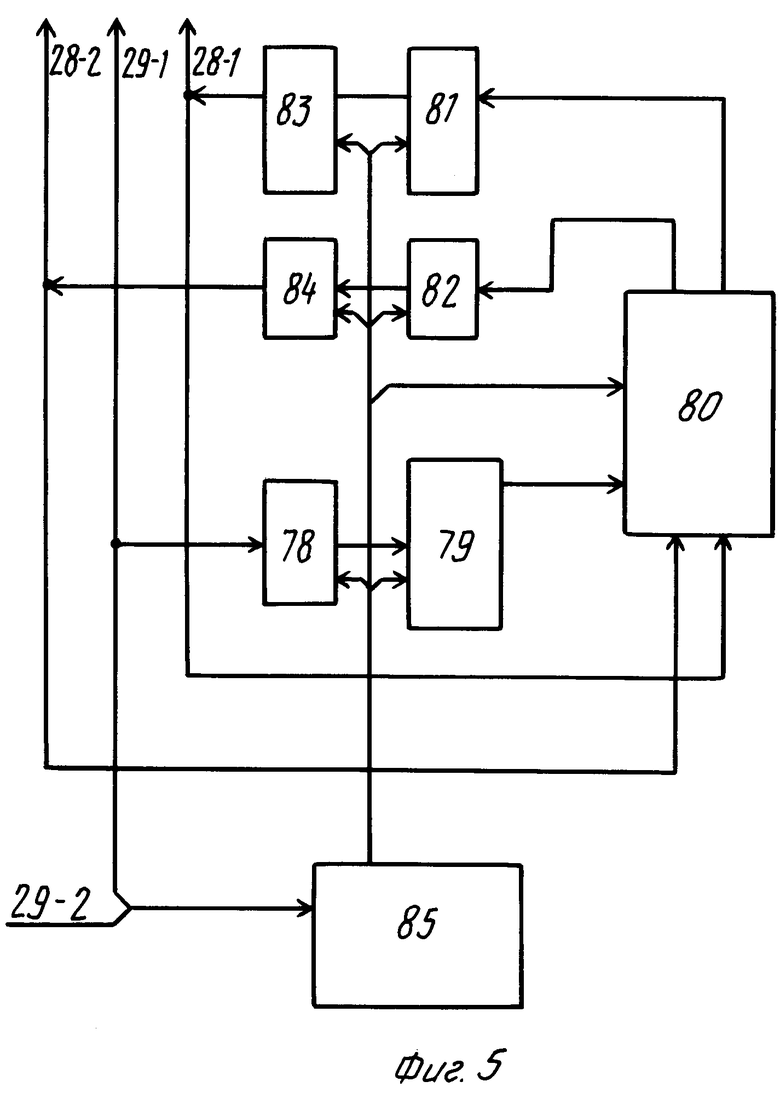

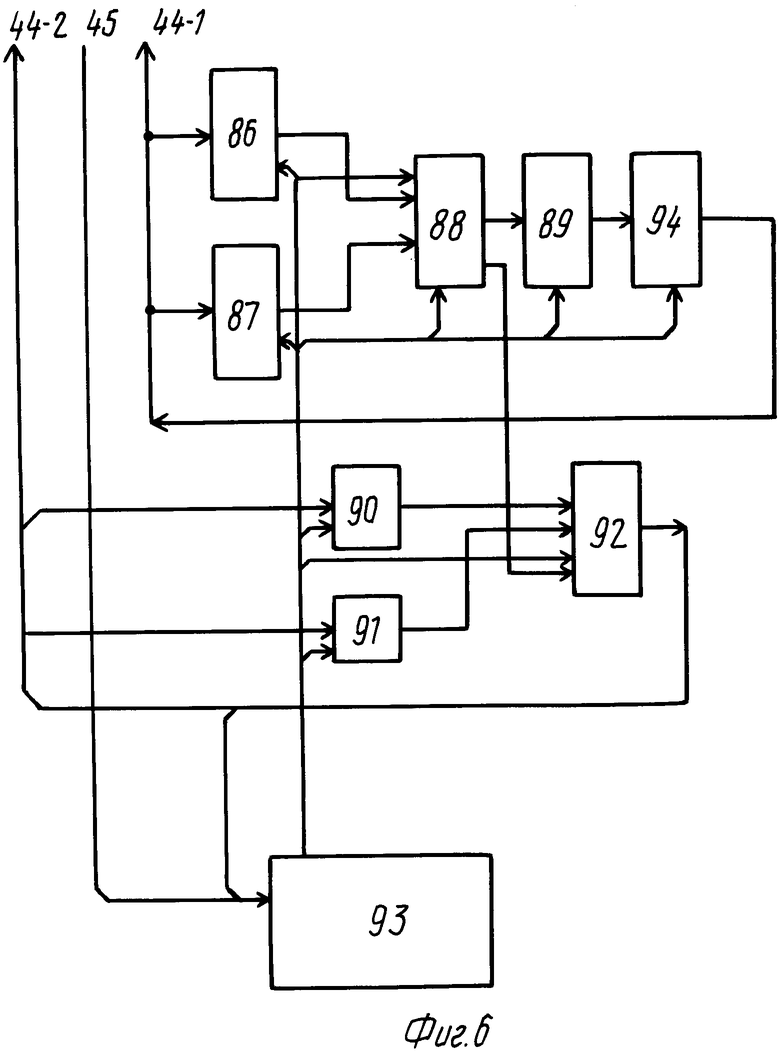

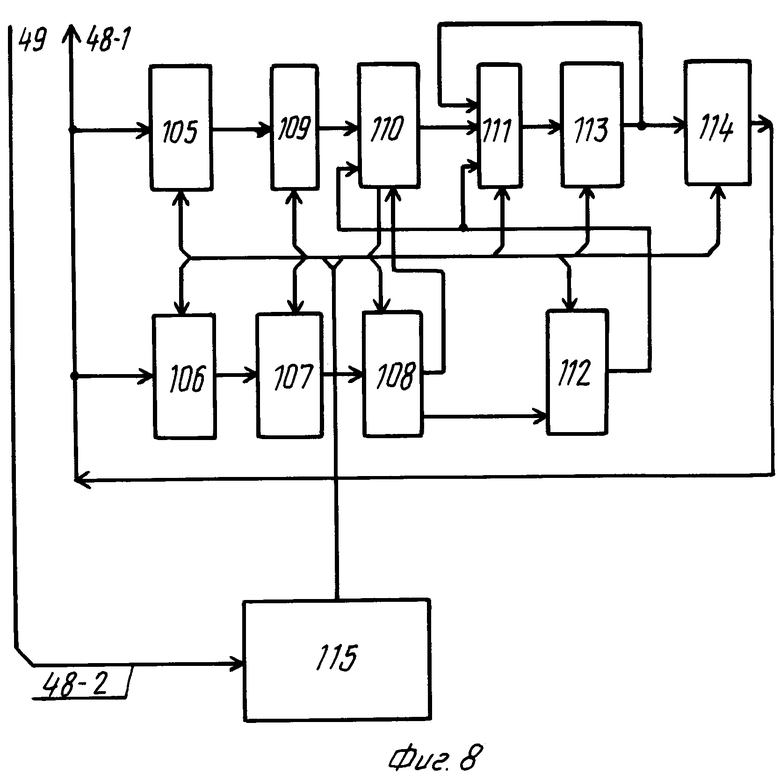

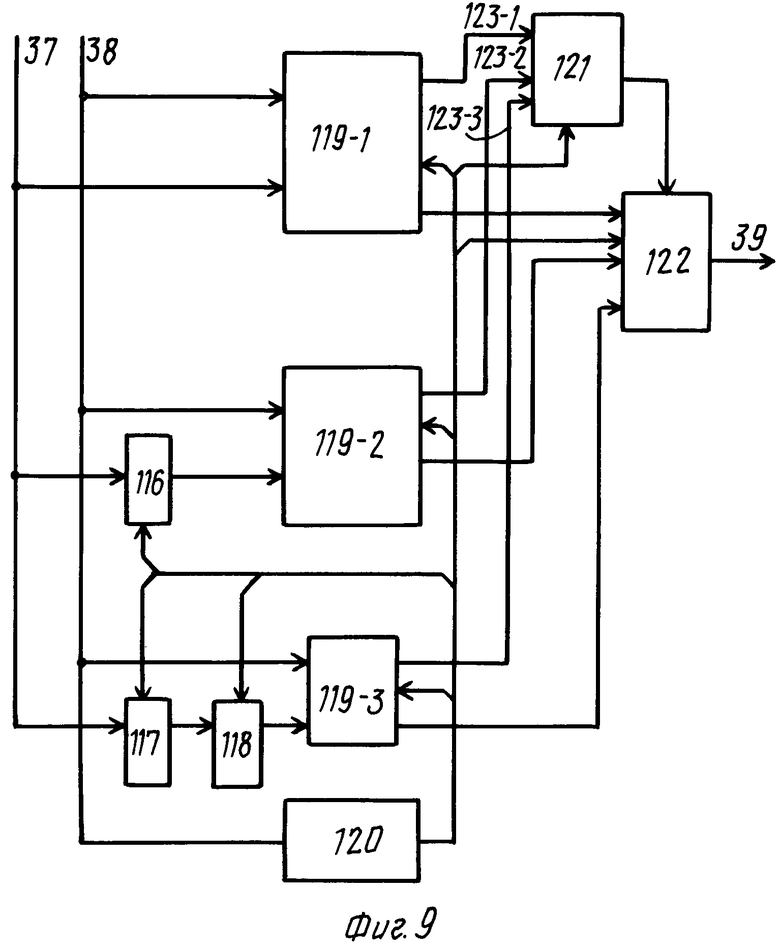

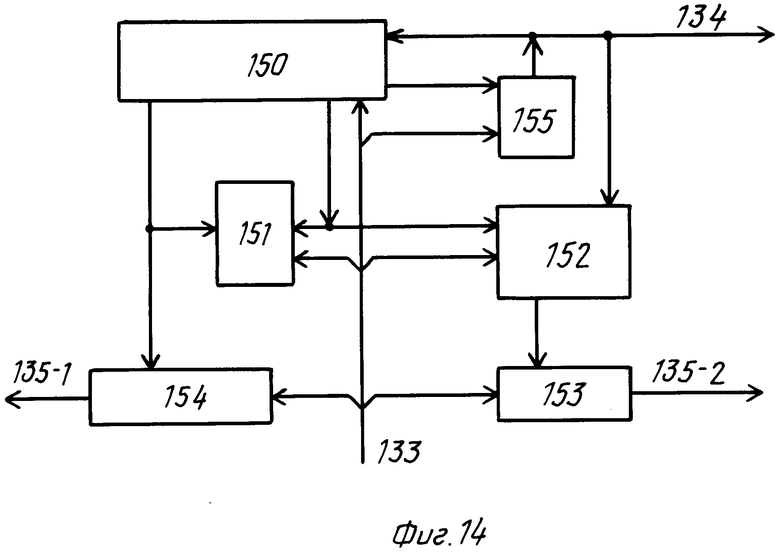

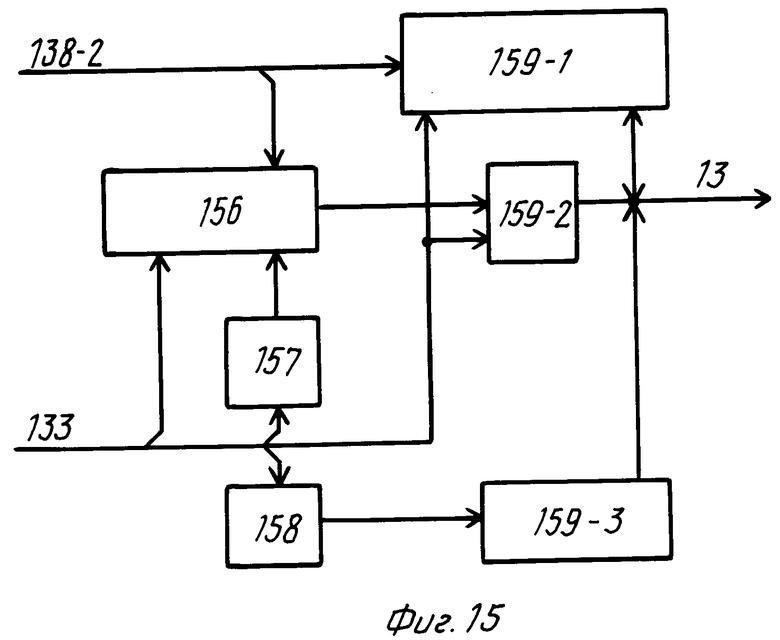

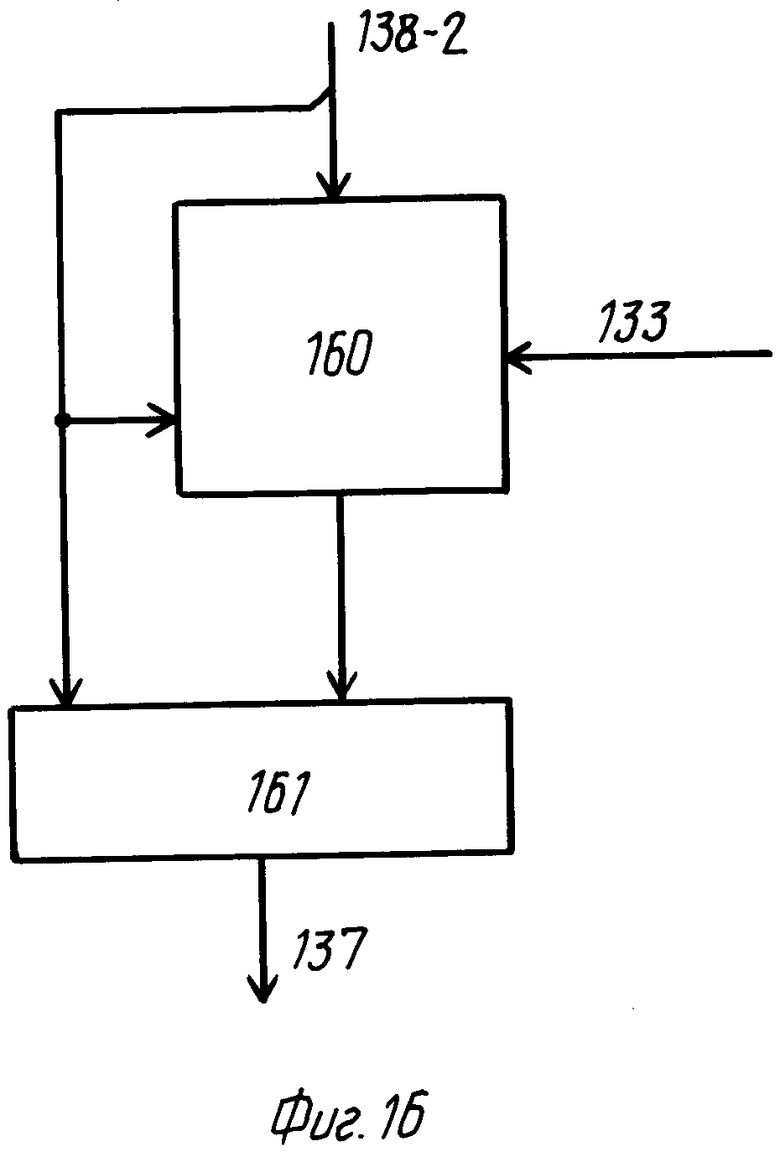

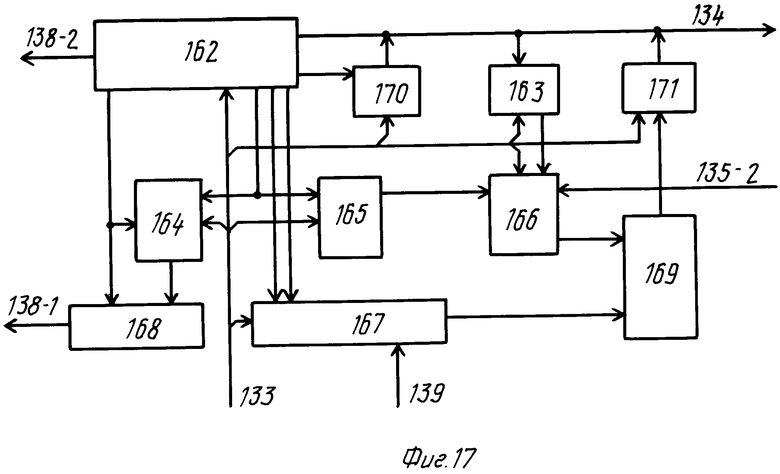

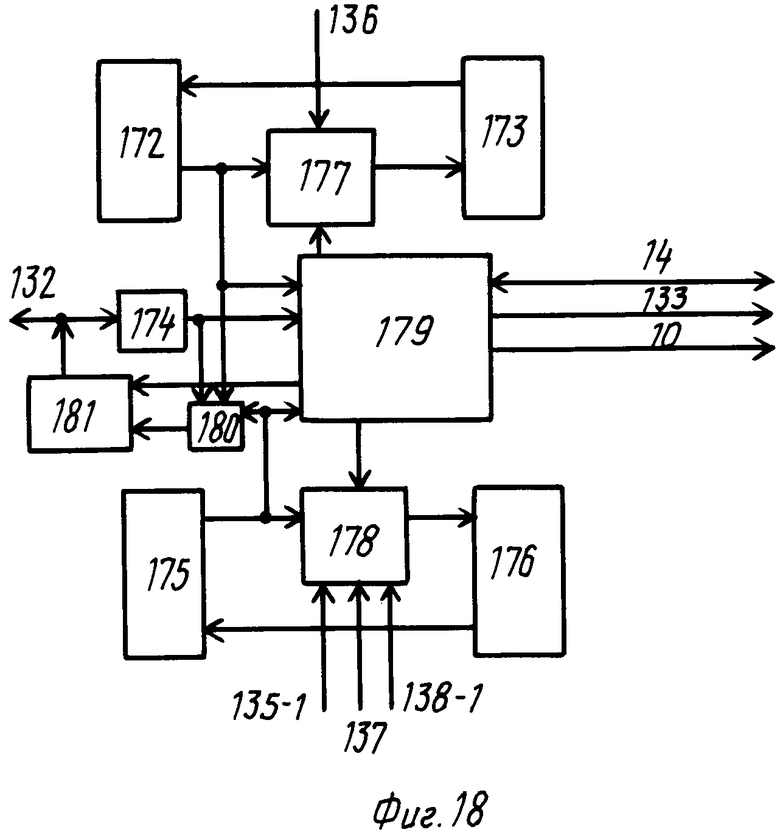

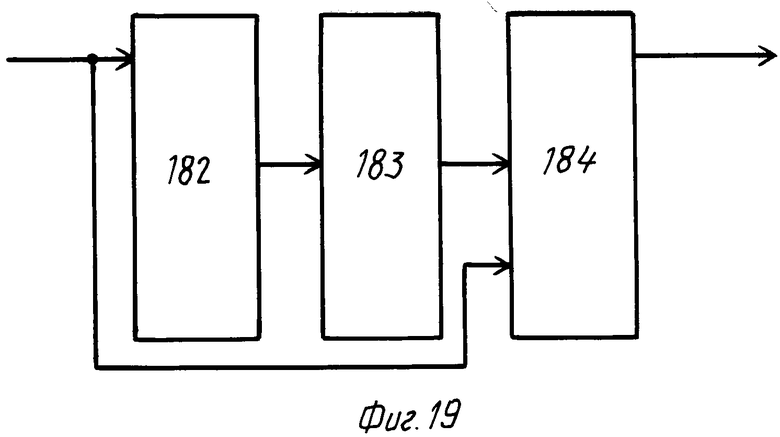

На фиг. 1 представлена блок-схема вычислительной системы; на фиг. 2 - схема процессора; на фиг. 3 - пример реализации первого блока сопряжения; на фиг. 4 - пример реализации второго блока сопряжения; на фиг. 5 - пример реализации первого блока регистров; на фиг. 6 - пример реализации блока обработки целых чисел; на фиг. 7 - пример реализации блока обработки вещественных чисел; на фиг. 8 - пример реализации блока логической обработки; на фиг. 9 - пример реализации блока контроля; на фиг. 10 - пример реализации устройства управления буферными памятями; на фиг. 11 - пример реализации порта данных; на фиг. 12 - пример реализации порта буфера команд; на фиг. 13 - пример реализации блока управления буферной памятью команд; на фиг. 14 - пример реализации блока управления памятью сегментов; на фиг. 15 - пример реализации порта буфера данных; на фиг. 16 - пример реализации блока управления буферной памятью данных; на фиг. 17 - пример реализации блока управления памятью страниц; на фиг. 18 - пример реализации блока центрального управления; на фиг. 19 - пример реализации узла управления.

Вычислительная система (фиг.1) содержит процессор 1, устройство 2 буферной памяти данных, устройство 3 буферной памяти команд, запоминающее устройство 4 признаков наличия информации, постоянное запоминающее устройство 5, устройство 6 управления буферными памятями, устройство 7 системной памяти.

Процессор соединен магистралью 8 адреса-данных, магистралью 9 признаков наличия информации и магистралью 10 управления с устройством 7 системной памяти и с устройством 6 управления буферными памятями, с которым также соединен первой адресной шиной 11 и управляющими выходной шиной 12.

Устройство 2 буферной памяти данных и запоминающее устройство 4 признаков наличия информации соединены с устройством 6 управления буферными памятями второй адресной шины 13. Устройство системной памяти 7 и устройство 6 управления буферными памятями соединены двунаправленной шиной 14 управления.

Устройство 6 управления буферными памятями соединено с устройством 3 буферном памяти команд и постоянным запоминающим устройством 5 третьей адресной шиной 15.

Процессор содержит первый блок 16 сопряжения, первый блок 17 регистров, второй блок 18 сопряжения, второй блок 19 регистров, блок 20 контроля, блок 21 постоянной памяти, блок 22 обработки целых чисел, блок 23 обработки вещественных чисел, блок 24 логической обработки.

Первый блок 16 сопряжения имеет информационные входы-выходы 25-1... 25-3, адресно-числовой вход-выход 26, управляющий вход 27, первый блок 17 регистров имеет информационные входы-выходы 28-1, 28-2, управляющие входы 29-1, 29-2, второй блок 18 сопряжения имеет информационные входы 30-1, 30-2, первый выход 31, второй выход 32, выходы 33 группы, управляющий вход 34, второй блок 19 регистров имеет информационные входы-выходы 35-1, 35-2, управляющие входы 36-1, 36-2, блок 20 контроля имеет информационный вход 37, управляющий вход 38, выход 39, блок 21 постоянной памяти имеет первый выход 40, адресный вход 41, второй выход 42, вход 43 считывания, блок 22 обработки целых чисел имеет информационные входы-выходы 44-1, 44-2, управляющий вход 45, блок 23 обработки вещественных чисел имеет информационные входы-выходы 46-1, 46-2, управляющий вход 47, блок 24 логической обработки имеет информационные входы-выходы 48-1, 48-2, управляющий вход 49.

Кроме того, в ЦП имеются информационная магистраль 50, магистраль 51 управления, магистраль 52 контроля.

В состав первого блока 16 сопряжения входят регистр 53 адреса, регистр 54 считываемых данных, регистр 55 записываемых данных, регистр 56 тега считываемых данных, регистр 57 тега записываемых данных, узел 58 управления, блоки шинных формирователей 59...63.

В состав второго блока сопряжения входят регистр 64 команд, дешифратор 65 команд, регистр 56 управляющего слова первого уровня, регистр 67 управляющего слова второго уровня, регистр 68 управляющего слова третьего уровня, регистр 69 управляющего слова четвертого уровня, регистр 70 константы, счетчик 71 индекса команды, регистр 72 индекса перехода, мультиплексор 73, выходной регистр 74 индекса, блок 75 регистров индексов исполняемых команд, узел 76 управления, блоки шинных формирователей 77.

В состав первого блока 17 регистров входят регистр 78 номера, дешифратор 79 номера, регистровый накопитель 80, регистр 81 данных, регистр 82 тега, блоки шинных формирователей 83,84, узел 85 управления.

В состав блока 22 обработки целых чисел входят регистр 86...87 операндов, сумматор 88, регистр 89 результата, регистры 90,91 тегов операндов, узел контроля 92, узел 93 управления, блок шинных формирователей 94.

Узлы контроля 92 и 103 могут быть выполнены на многовходных логических схемах И-ИЛИ-НЕ.

В состав блока 23 обработки вещественных чисел входят регистры 95,96 операндов, регистры 97, 98 тегов операндов, сумматор 99, умножитель 100, мультиплексор 101, блок шинных формирователей 102, узел контроля 103, узел 104 управления.

В состав блока 24 логической обработки входят регистры 105, 106 операндов, сумматор 107, дешифратор 108, мультиплексор 109, сдвигатель 110, логический элемент 111 И, генератор 112 маски, регистр 113 результата, блок шинных формирователей 114, узел 115 управления.

В состав блока 20 контроля входят регистры 116...118, программируемые логические матрицы 119...1-119...3, узел 120 управления , блок 121 приоритета, мультиплексор 122. Блок 121 приоритета имеет входы 123-1...123-3 запросов прерываний и вход 123-4, несущий функции входов синхронизации, строба разрешения, кода уровня текущего приоритета.

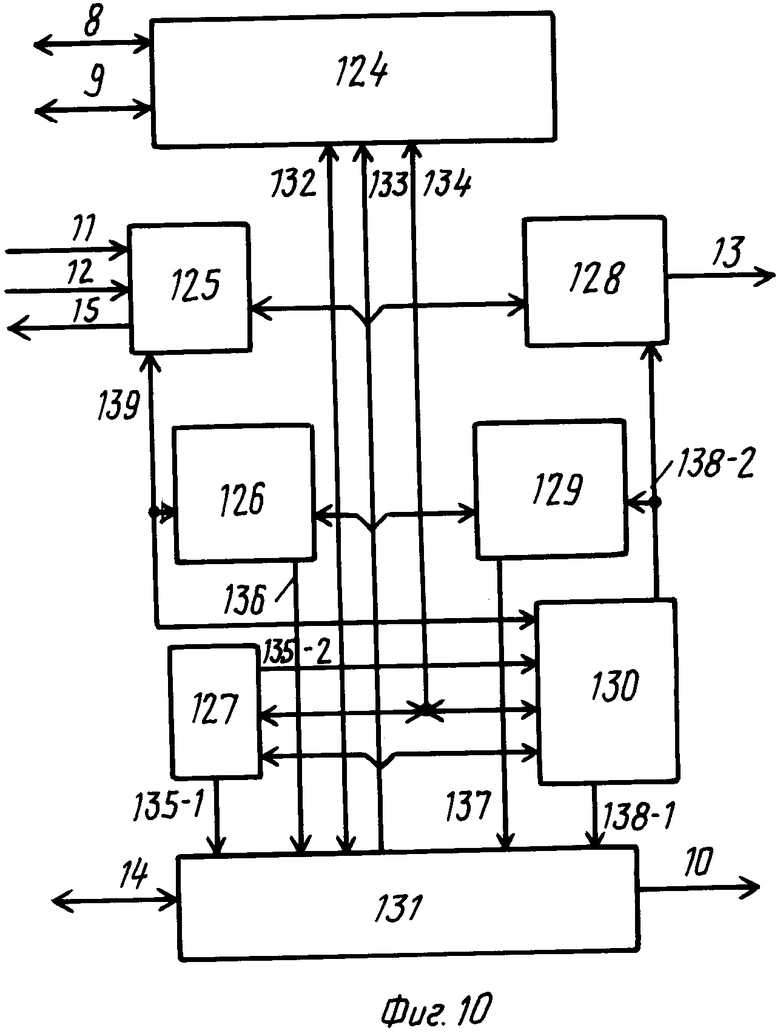

В состав устройства 6 управления буферными памятями и входят порт 124 данных, порт 125 буфера команд, блок 126 управления буферной памятью команд, блок 127 управления памятью сегментов, порт 128 буфера данных, блок 129 управления буферной памятью данных, блок 130 управления памятью страниц, блок 131 центрального управления.

Устройство 6 управления буферными памятями имеет двунаправленную шину 132 тегов, двунаправленную шину 133 сигналов управления, двунаправленную шину 134 данных, сигнал 135-1 попадания/промаха в буферную память сегметов, второй информационный выход 135-2, сигнал 136 попадания/промаха в память адресных тегов команд, сигнал 137 попадания/промаха в память адресных тегов данных, сигнал 138-1 попадания/промаха в буферную память страниц, шину 138-2 адреса, шину 139 индекса команд.

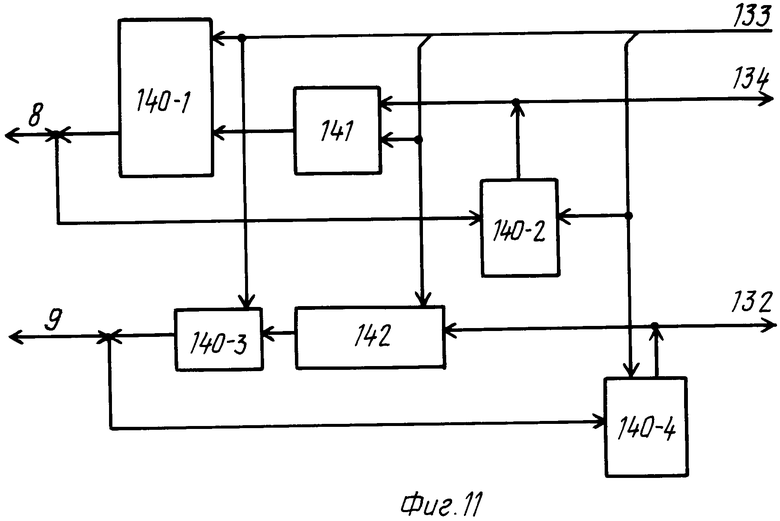

В состав порта 124 данных входят регистр 141 данных, регистр 142 тегов и блоки шинных формирователей 140-1...140-4.

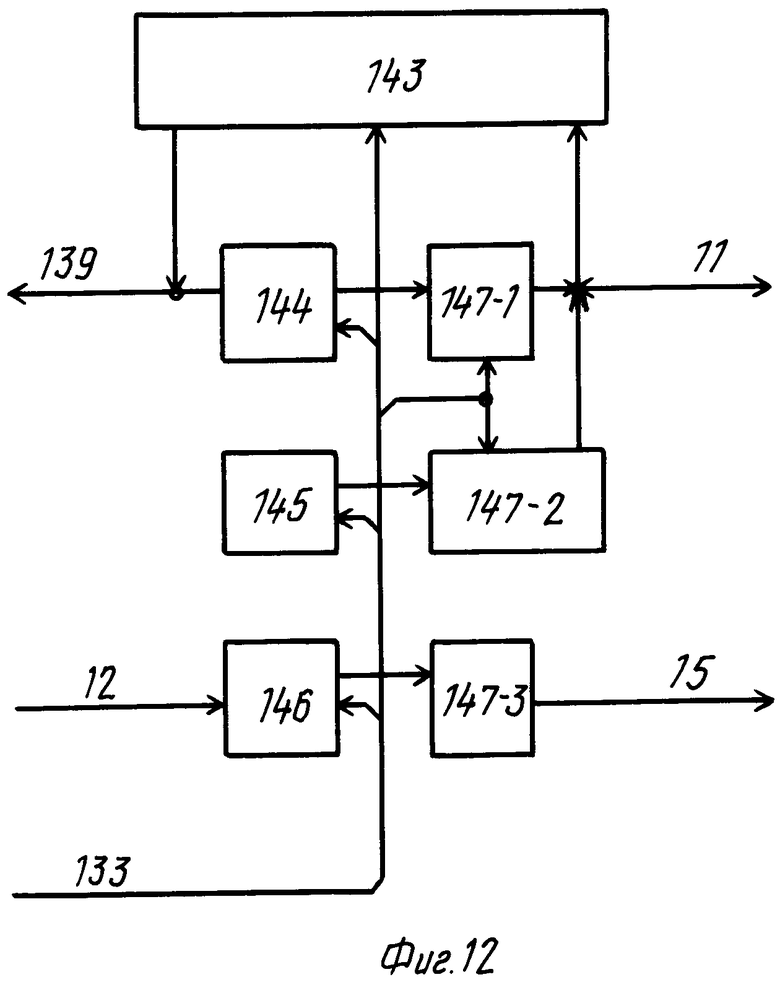

В состав порта 125 буфера команд входят регистр 143 старших разрядов индекса команды, регистр 114 младших разрядов индекса команды, счетчик 145, блок формирования 146 и блоки шинных формирователей 147-1...147-3.

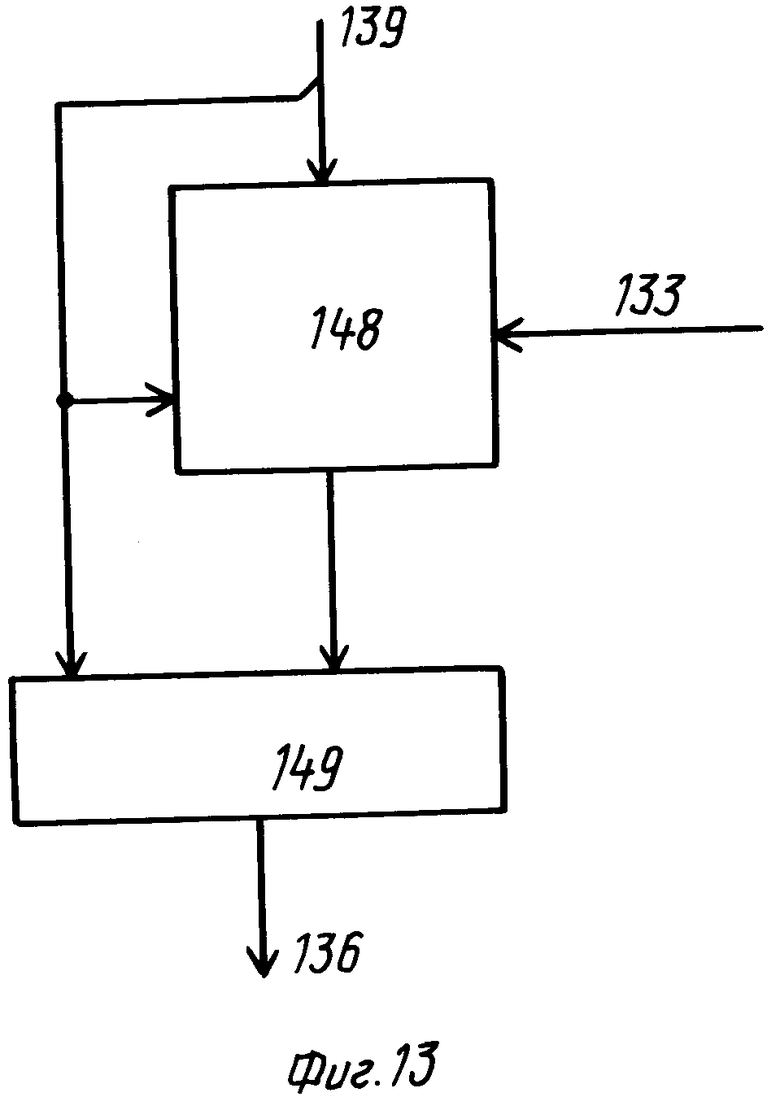

В состав блока 126 управления буферной памятью команд входят накопитель 148 и элемент 149 сравнения.

В состав блока 127 управления памятью сегментов входят регистр 150 адреса, накопитель 151 адресов дескрипторов сегментов, накопитель 152 дескрипторов сегментов, регистр 153 текущего дескриптора сегмента, элемент 154 сравнения и блок шинных формирователей 155.

В состав порта 128 буфера данных входят мультиплексор 156, счетчик 157, блок формирования 158, блоки шинных формирователей 159-1...159-3.

В состав блока 129 управления буферной памятью данных входят накопитель 160 и элемент 161 сравнения.

В состав блока 130 управления памятью страниц входят регистр 162 адреса, блок регистров 163, накопитель 164 математических адресов, накопитель 165 физических адресов, мультиплексор 166 первого операнда сумматора, мультиплексор 167 второго операнда сумматора, элемент 168 сравнения, сумматор 169, блоки шинных формирователей 170, 171.

В состав блока 131 центрального управления входят регистры 172, 173 состояний автомата обработки команд,регистр 174 операций, регистры 175, 176 состояний автомата обработки данных, блоки 177, 178 формирования следующего состояния автоматов, дешифратор 179 управляющих сигналов, шифратор 180 шины тегов, блок шинных формирователей 181.

Каждый из узлов 58, 76, 85, 93, 104, 115, 120 управления (фиг.19) содержит последовательно соединенные регистр 182, дешифратор 183 и логические элементы 184 И, ИЛИ, НЕ. Количество входов, включающих входы синхронизации, и количество выходов может меняться в зависимости от того, в каком блоке используется узел управления. Выходы узлов 58, 76, 85, 93, 104, 115, 120 соединяются с соответствующими управляющими входами всех других элементов, входящих в блоки. В состав внутреннего ПЗУ 21 подпрограмм входят дешифраторы, накопитель, регистр, блок шинных формирователей.

Второй блок 19 регистров может быть выполнен по схеме, аналогичной первому блоку 17 регистров. Примеры реализации устройства системной памяти 7, устройства буферной памяти 3 команд, устройства буферной памяти 2 данных, запоминающего устройства 4 признаков наличия информации постоянного запоминающего устройства 5, блока 21 постоянной памяти, порта 124 данных, порта 125 буфера команд, блока 126 управления буферной памятью команд, блока 127 управления памятью сегментов, порта 128 буфера данных, блока 130 управления памятью страниц, блока 131 центрального управления хорошо известны из литературы.

Выполнение программируемых логических матриц 119-1...119-3 и выполнение блока 121 приоритета раскрыто в известной литературе.

Работает вычислительная система следующим образом.

Процессор 1 посылает адрес очередной команды по шине 11 в устройство 3 и устройство 5, а также в устройство 6 управления буферной памяти, сопровождая этот адрес стробом. Отсутствие строба означает, что процессор считывает команды из блока 21 постоянной памяти. Сигналом, передаваемым по шине 12, процессор 1 указывает, что обращение выполняется к постоянному запоминающему устройству 5, а не в устройство 3 буферной памяти устройство команд. Устройство 6 управления буферными памятями проверяет наличие запрашиваемой команды в блоке 126 управления буферной памятью команд, если обращение осуществляется в устройство буферной памяти 3 команд, приписывает к адресу старшие разряды, определяющие номер блока, и осуществляет выдачу управляющих стробов из порта 125 буфера команд в устройство буферной памяти 3 команд или постоянное запоминающее устройство 5. Считанная команда поступает по шине 10 в процессор 1. В случае отсутствия запрашиваемой команды в устройстве 3 буферной памяти команд, устройство 6 управления буферными памятями сигнализирует об этом процессору 1 и делает запрос в устройство системной памяти 7 по шине 14. Сигнал процессору 1 формирует блок 131 центрального управления и выдает по шине 10. Запросы в устройство системной памяти 7 формирует блок 131 центрального управления. Так как процессор 1 работает с адресами команд в виде относительных индексов в пределах текущего программного сегмента кода, то при обращении в устройство системной памяти 7 происходит формирование полного физического адреса путем сложения базы программного сегмента и индексов. Смена базы программного сегмента осуществляется блоком 127 управления памятью сегментов при выполнении специальных команд межсегментных переходов. Процессор 1 на время запроса отключается от шин 8,9 и 10. При выполнении команд обращения в устройство буферной памяти 2 данных, процессор 1 выдает адрес числа по шине 8, в устройство 6 управления буферными памятями, сопровождая этот адрес стробом адреса. Порт 124 данных фиксирует полученный адрес и транслирует младшие разряды адреса через порт 128 буфера данных по шине 13 в устройство буферной памяти 2 данных и запоминающее устройство 4 признаков наличия информации. Параллельно с этим в блоке 129 управления буферной памятью данных проверяется факт присутствия данных по запрашиваемому адресу. В случае отсутствия данных, обращение в устройство буферной памяти 2 данных и запоминающее устройство 4 признаков наличия информации отменяется, устройство управления буферными памятями сигнализирует об этом процессору 1 и делает запрос в устройство системной памяти 7 по шине 14.

Процессор 1 на время запроса отключается от шин 8 и 9, обращение процесса 1 в устройство 2 буферной памяти данных осуществляется по математическим адресам. Поэтому перед обращением в устройство системной памяти 7 устройство 6 управления буферными памятями производит преобразование математического адреса в физический, используя специальную таблицу преобразования адресов, часть которых хранится в блоке 130 управления памятью страниц. Вся таблица расположена в устройстве системной памяти 7. Когда требуемая для преобразования строка таблицы отсутствует, устройство 6 управления буферными памятями в начале обращения в устройство системной памяти 7 за этой строкой, а затем уже производит преобразование адресов и повторное обращение в устройство системной памяти 7 за данными.

Данные, считываемые из устройства 2 буферной памяти данных, поступают в процессор 1 по шине 8. Тег данных, считанный из запоминающего устройства 4 признаков наличия информации, поступает в процессор 1 по шине 9.

Команды, поступающие в процессор 1, поступают в регистр 64 команд второго блока 18 сопряжения. Затем команды преобразуются в управляющие слова для блоков процессора в дешифраторе 65 команд. Блоки процессора 1 могут работать параллельно, причем одновременно могут выполняться несколько команд. Состав исполнительных блоков процессора 1 может быть различным. Изображенные на фиг. 2 блоки 22, 23 обработки целых и вещественных чисел достаточно традиционны и не требуют подробного описания. Особенностью является то, что оба блока могут одновременно выполнять операции сложения и вычитания над одними и теми же операндами. В качестве примера реализации блока 24 логической обработки на фиг. 8 показан блок, реализующий выделение и вставление поля бит произвольного размера в пределах 32-х разрядов. Рассмотрим, как осуществляется выделение поля. Операнд, из которого необходимо выделить поле, принимается в регистр 105. Операнд, в котором указывается начальная граница поля и количество бит в поле, принимается в регистр 1,6. На сдвигателе 110 производится сдвиг выделяемого поля к правому краю 32-разрядного слова, при этом в генераторе 112 маски формируется 32-разрядная заготовка из единиц в количестве, равном размеру выделяемого поля, прижатых к правому краю 32-разрядного слова.

Остальная часть маски заполняется нулями. В логическом элементе 111 маска и сдвинутый оператор логически умножаются и полученный результат записывается в регистр 113, а затем через шинные формирователи 114 выдается в информационную магистраль 50. При дешифрации команды формируется управляющее слово, которое разбито на фиксированные поля для каждого блока. В свою очередь каждое поле может иметь разряды, относящиеся к различным фазам выполнения команды. Команды по длительности выполнения могут включать от двух до четырех фаз. Во втором блоке 18 сопряжения организован конвейер выполняемых команд в виде регистров 66, 67, 68, 69 управляющего слова первого, второго, третьего и четвертого соответственно уровней. Выходы регистров, относящиеся к одноименным блокам, логически суммируются, в результате образуется текущее управляющее слово, поступающее в магистраль управления 51. Каждый из блоков процессора, в соответствии с кодом операции, постурпающим из управляющего слова, выполняет действия над операндами, считываемыми из первого блока 17 регистров. Результат операции также записывается в этот блок. Операнды, считываемые из первого блока 17 регистров на информационную магистраль 50, могут приниматься и обрабатываться всеми блоками процессора 1, результат же операции выдает только один блок. Так как в рассматриваемой вычислительной системе возможна динамика типов операндов, это допускает изначальную неопределенность в указании какому блоку необходимо выдавать результат операции. Поясним это на следующем примере. Команда арифметического сложения работает как с целыми так и с вещественными числами. Типы операндов могут быть сформированы в процессе выполнения команд, предшествующих команде арифметического сложения, поэтому определение того, с какимми операндами будет работать команда, осуществляется в момент их считывания из первого блока 17 регистров по тегам, поступающим по магистрали 52 контроля в блок контроля. Операнды, считанные из первого блока 17 регистров, как указывалось выше, обрабатываются параллельно в блоке 22 обработки целых чисел и блоке 23 обработки вещественных чисел. К моменту окончания операции блок 20 контроля сигнализирует о том, какому блоку необходимо записывать результат в первый блок 17 регистров. Помимо динамики типов в рассматриваемой вычислительной системе возможна динамика форматов. Это означает, что формат операндов, считываемых из первого блока 17 регистров может быть различным. В случае, если разноформатные операнды должны использоваться в арифметических операциях, требуется предварительное приведение их к формату, выданному в команде. Это, в свою очередь, может привести к преобразованию типа операнда, как, например, в случае перевода 64-разрядного целого числа в 32-разрядное. В системах, не имеющих тегированных данных, динамика форматов, как и динамика типов, в буквальном понимании невозможны, что обедняет возможности системы и усложняет программирование. Интерпретация работы с различными форматами и типами операндов требует также дополнительных затрат памяти под команды, выполняющие преобразование, что в конечном счете снижает производительность системы за счет роста процентов "промахов" при обращении в устройство 3 буферной памяти команд. С другой стороны, в системах с тегированными данными, реализующими динамику типов и форматов чисто аппаратными средствами, значительно растет сложность аппаратуры, что приводит к снижению ее надежности.

В рассматриваемой вычислительной системе использован комбинированный подход в решении задачи работы с динамикой типов и форматов. Анализ тегов операндов осуществляется аппаратурой блока 20 контроля.

В случае несовпадения форматов или типов, а также в случае срабатывания схем контроля правильности результата операции в исполнительных блоках, блок 20 контроля сигнализирует об этом второму блоку 18 сопряжения, блоку 21 постоянной памяти, первому блоку 17 регистров и второму блоку 19 регистров. Следствием этого является переключение второго блока 18 сопряжения на прием команд из блока 21 постоянной памяти. Результатом выполнения подпрограммы, записанной в блоке 21 постоянной памяти, будет то или иное преобразование типа или формата операндов, либо отработка исключительной ситуации, например, переполнения при арифметических операциях. В подпрограммах, записанных в блоке 2 постоянной памяти и постоянном запоминающем устройстве 5 используется тот же набор системы команд, что и в случае работы с устройством 3 буферной памяти команд. Это требует работы с внутренними регистрами процессора. Однако использование для этого первого блока 17 регистров исключало бы возможность корректного возврата к продолжению программы без предварительного сохранения содержимого первого блока 17 регистров в устройство 2 буферной памяти данных. Это приводило бы к существенному замедлению выполнения программ блока 21 постоянной памяти. Второй блок 19 регистров позволяет решить эту проблему. При работе с блоком 21 постоянной памяти все промежуточные результаты операций находятся в этом блоке. В системе команд имеются две команды, позволяющие осуществлять пересылки между первым блоком 17 регистров и вторым блоком 19 регистров. В начале выполнения подпрограммы происходит пересылка из первого блока 17 регистров требуемых операндов, а в конце подпрограммы из второго блока 19 регистров пересылается результат. В процессе выполнения подпрограммы возможны переходы в постоянное запоминающее устройство, где может находиться та часть подпрограммы, которая модифицируется для различных вычислительных систем, работающих с одним и тем же процессором 1. В момент перехода из основной программы к подпрограмме индексы выполняемых команд запоминаются в блоке 75 регистров индексов исполняемых команд. Это позволяет осуществить корректный возврат в основную программу после завершения подпрограммы.

Использование предлагаемой вычислительной системы обеспечивает, по сравнению с существующими системами, следующие преимущества:

1. Меньший объем и сложность аппаратуры, а как следствие, высокая надежность;

2. Обеспечивает повышение производительности и удобство работы программиста.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| УСТРОЙСТВО ДЛЯ ВЫЗОВА ПОДПРОГРАММ | 1990 |

|

RU2009538C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ И ОКРУГЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ | 1992 |

|

RU2018921C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| ОПТИЧЕСКИЙ МНОГОКАНАЛЬНЫЙ АССОЦИАТИВНЫЙ КОРРЕЛЯТОР | 1992 |

|

RU2037187C1 |

Изобретение относится к вычислительной технике. Целью изобретения является повышение быстродействия надежности за счет контроля типов и форматов операндов при трансляции в процессоре. Устройство содержит процессор, устройство буферной памяти данных, устройство буферной памяти команд, запоминающее устройство признаков наличия информации, постоянное запоминающее устройство, устройство управления буферными памятями, устройство системной памяти. Предлагаемая вычислительная система, разработанная на базе архитектуры, использующей сокращенный набор аппаратно-реализуемых простых команд, отрабатывает большинство исключительных ситуаций без прерывания процессора и выхода на процедуры операционной системы. Это осуществляется за счет перехода в такой режим, когда команды берутся не из устройства буферной памяти команд, а из блока постоянной памяти и постоянного запоминающего устройства. К исключительным ситуациям относятся, в частности, случаи обработки разноформатных и разнотипных операндов. Информация о типе и формате хранится в разрядах тегов операндов и позволяет автоматически определять алгоритм операции. 19 ил.

ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА, содержащая процессор, устройство системной памяти, устройство буферной памяти данных, устройство буферной памяти команд и устройство управления буферными памятями, причем первый информационный вход-выход процессора через магистраль адреса данных подключен к первому информационному входу-выходу устройства управления буферными памятями, к информационному входу-выходу устройства буферной памяти данных и к первому информационному входу-выходу устройства системной памяти, выход адреса процессора подключен к информационному входу устройства управления буферными памятями и к первому адресному входу устройства буферной памяти команд, информационный вход-выход которого через магистраль управления подключен к входу команд процессора и выходу устройства системной памяти, первый и второй выходы устройства управления буферными памятями подключены соответственно к управляющему входу устройства буферной памяти команд и адресному входу устройства буферной памяти данных, вход-выход режима устройства управления буферными памятями подключен к управляющему входу-выходу устройства системной памяти, при этом процессор содержит блок обработки целых чисел, блок обработки вещественных чисел, блок логической обработки, первый и второй блоки сопряжения, первый блок регистров, причем в процессоре первый информационный вход-выход подключен к адресно-числовому входу-выходу первого блока сопряжения, вход команд процессора подключен к первому информационному входу второго блока сопряжения, первый выход которого подключен к выходу адреса процессора, второй выход второго блока сопряжения через информационную магистраль подключен к первым информационным входам-выходам блока обработки целых чисел, блока обработки вещественных чисел, блока логической обработки, первого блока сопряжения и первого блока регистров, с первого по пятый выходы группы второго блока сопряжения подключены соответственно к управляющим входам блока обработки целых чисел, блока обработки вещественных чисел, блока логической обработки, первого блока сопряжения и к первому управляющему входу первого блока регистров, отличающаяся тем, что, с целью повышения быстродействия и надежности за счет контроля типов и форматов операндов при трансляции в процессоре, введены постоянное запоминающее устройство подпрограмм и запоминающее устройство признаков наличия информации, при этом выход управления буферной памятью процессора подключен к входу режима устройства управления буферными памятями, выход адреса процессора и первый выход устройства управления буферными памятями подключены соответственно к первому и второму адресным входам постоянного запоминающего устройства подпрограмм, выход которого через магистраль управления подключен к входу команд процессора, информационному входу-выходу устройства буферной памяти команд, третьему выходу устройства управления буферными памятями и выходу устройства системной памяти, второй выход устройства управления буферными памятями подключен к адресному входу запоминающего устройства признаков наличия информации, информационный вход-выход которого через магистраль признаков наличия информации подключен к второму информационному входу-выходу блока управления буферными памятями, второму информационному входу-выходу устройства системной памяти и второму информационному входу-выходу процессора, при этом процессор содержит второй блок регистров, блок контроля и блок постоянной памяти, причем в процессоре первый информационный вход-выход второго блока регистров через информационную магистраль подключен к первым информационным входам-выходам блока обработки целых чисел, блока обработки вещественных чисел, блока логической обработки, первого блока регистров, первого блока сопряжения и второму выходу второго блока сопряжения, шестой и седьмой выходы группы которого подключены соответственно к управляющему входу блока контроля и первому управляющему входу второго блока регистров, второй информационный вход-выход блока обработки целых чисел через магистраль контроля подключен к вторым информационным входам-выходам блока обработки вещественных чисел, блока логической обработки, первого и второго блоков регистров, первого блока сопряжения и информационному входу блока контроля, выход которого подключен к вторым управляющим входам первого и второго блоков регистров, управляющему входу второго блока сопряжения и входу считывания блока постоянной памяти, первый выход которого подключен к второму информационному входу второго блока сопряжения, первый выход которого подключен к адресному входу блока постоянной памяти, второй выход которого подключен к выходу управления буферной памятью процессора, второй информационный вход-выход которого подключен к третьему информационному входу-выходу первого блока сопряжения.

| Том Мануэль | |||

| Приспособление к зерновой сеялке для одновременного высева семян и гранулированных удобрений в одну борозду самостоятельными строчками | 1950 |

|

SU88000A1 |

| В сб | |||

| Электроника, т.61, N 9 (791), 1988, с.28-34. | |||

Авторы

Даты

1995-02-09—Публикация

1989-12-29—Подача