Предлагаемое изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих тактируемых запоминающих устройств большой емкости.

Известен дешифратор на КМДП транзисторах [а. с. №1113 853, СССР, G11C 8/00], содержащий управляющий вход, шину питания, шину нулевого потенциала, n входов, m выходов, полевые транзисторы первого и второго типа проводимости, соединенных в m n-входовых элементов ИЛИ-НЕ, один двухвходовой элемент И-НЕ, один инвертор и m элементов заряда.

Однако указанный дешифратор на КМДП транзисторах имеет высокий уровень помехи на своих выходах в выбранном режиме в виде напряжения высокого уровня на время переключения инвертора, двухвходового элемента И-НЕ и заряда узла выхода этого двухвходового элемента, к которому подключены затворы элементов заряда. Величина этого напряжения будет определяться напряжением источника питания и сопротивлением открытых параллельных транзисторов элемента ИЛИ-НЕ и транзистора элемента заряда. Время наличия этой помехи на выходе дешифратора на КМДП транзисторах может быть неопределенно большим, так как определяется нагрузочной способностью двухвходового элемента И-НЕ и нагрузкой на его выходе, которая может быть неопределенно большой, зависящей от сопротивления цепи соединения затворов элементов заряда и суммарной емкости этого узла. Присутствие этой помехи на выходах указанного дешифратора может привести к нарушению правильной работы устройств, для которых входными сигналами служат сигналы выходов дешифратора, что служит доказательством ненадежной работы дешифратора.

Кроме того, в этом дешифраторе через каждый невыбранный элемент ИЛИ-НЕ и соединенный с его выходом элемент заряда протекает ток потребления до момента полного закрытия транзисторов элемента заряда.

Ток потребления, протекающий через эти элементы, ужесточает режим их работы и приводит к возникновению паразитных эффектов схемы, что является прямым снижением надежности работы дешифратора на КМДП транзисторах.

Помимо этого, быстродействие указанного дешифратора определяется временем срабатывания инвертора, двухвходового элемента и заряда емкости узла, к которому подключены затворы элементов заряда. Так как число этих элементов может быть неопределенно большим, то и емкость этого узла может быть неопределенно высокой, а, следовательно, и быстродействие этой схемы - неопределенно низким.

Ко всему прочему, данный дешифратор содержит большее число транзисторов, так как увеличение числа адресных входов на один, требует в каждом элементе ИЛИ-НЕ дешифратора увеличения числа транзисторов на два.

Кроме того, известен дешифратор [патент №4401903, США, Н03К 19/094], являющийся прототипом предлагаемого изобретения и содержащий полевые транзисторы первого и второго типа проводимости, нулевой прямой А0, нулевой инверсный  и первые, вторые,..., n-ые прямые A1, A2,..., An и инверсные

и первые, вторые,..., n-ые прямые A1, A2,..., An и инверсные  ,

,  ,...,

,...,  адресные входы, вход выбора режима СЕ, выводы питания первого VDD и второго "ground" уровня напряжения, первый блок параллельно включенных n транзисторов T11-1÷Т11-n с каналом первого типа проводимости, стоки которых соединены между собой, истоки соединены между собой, а затворы соединены с соответствующими прямыми n-ми адресными входами A1, А2,..., An, второй блок параллельно включенных n транзисторов T21-1÷T21-n с каналом первого типа проводимости, стоки которых соединены между собой, истоки соединены между собой и подсоединены к истокам транзисторов первого блока параллельно включенных n транзисторов, а затворы соединены с соответствующими инверсными n-ми адресными входами

адресные входы, вход выбора режима СЕ, выводы питания первого VDD и второго "ground" уровня напряжения, первый блок параллельно включенных n транзисторов T11-1÷Т11-n с каналом первого типа проводимости, стоки которых соединены между собой, истоки соединены между собой, а затворы соединены с соответствующими прямыми n-ми адресными входами A1, А2,..., An, второй блок параллельно включенных n транзисторов T21-1÷T21-n с каналом первого типа проводимости, стоки которых соединены между собой, истоки соединены между собой и подсоединены к истокам транзисторов первого блока параллельно включенных n транзисторов, а затворы соединены с соответствующими инверсными n-ми адресными входами  ,

,  ,...,

,...,  , первый Т11-0 и второй T21-0 транзисторы с каналом первого типа проводимости, истоки которых соединены между собой и с истоками транзисторов первого и второго блоков параллельно включенных n транзисторов, затворы соединены, соответственно, с нулевым прямым и нулевым инверсным адресными входами, и сток первого транзистора, соединен со стоками транзисторов первого блока параллельно включенных n транзисторов, а сток второго транзистора - со стоками второго блока параллельно включенных n транзисторов, третий Т12 и четвертый T22 транзисторы с каналом второго типа проводимости, затворы которых соединены с входом выбора режима, истоки - с выводом питания первого уровня напряжения, а сток третьего транзистора - со стоком первого транзистора и со стоками транзисторов первого блока параллельно включенных n транзисторов, и сток четвертого транзистора - со стоком второго транзистора и со стоками второго блока параллельно включенных n транзисторов, пятый транзистор Т14 с каналом первого типа проводимости и шестой транзистор T15 с каналом второго типа проводимости, стоки которых соединены друг с другом, затворы соединены друг с другом, со стоками первого и третьего транзисторов и со стоками транзисторов первого блока параллельно включенных n транзисторов, исток пятого транзистора - со стоками второго и четвертого транзисторов и со стоками транзисторов второго блока параллельно включенных n транзисторов, а исток шестого транзистора соединен с выводом питания первого уровня напряжения, седьмой транзистор T16 с каналом второго типа проводимости, затвор которого соединен с входом выбора режима, исток - с выводом питания первого уровня напряжения, а сток - со стоками пятого и шестого транзисторов, восьмой транзистор Т24 с каналом первого типа проводимости и девятый транзистор Т25 с каналом второго типа проводимости, стоки которых соединены друг с другом, затворы соединены друг с другом, со стоками второго и четвертого транзисторов, со стоками транзисторов второго блока параллельно включенных n транзисторов и с истоком пятого транзистора, исток восьмого - со стоками первого и третьего транзисторов, со стоками первого блока параллельно включенных n транзисторов и с затворами пятого и шестого транзисторов, а исток девятого транзистора соединен с выводом питания первого уровня напряжения, десятый Т26 транзистор с каналом второго типа проводимости, затвор которого соединен с входом выбора режима, исток - с выводом питания первого уровня напряжения, а сток - со стоками восьмого и девятого транзисторов, одиннадцатый транзистор T13, затвор которого соединен с входом выбора режима, сток - с истоками первого и второго транзисторов и с истоками транзисторов первого и второго блоков параллельно включенных n транзисторов, а исток с выводом питания второго уровня напряжения, первый выходной буферный элемент IV1, вход которого соединен со стоками пятого, шестого и седьмого транзисторов, а выход является первым выходом дешифратора, второй выходной буферный элемент IV2, вход которого соединен со стоками восьмого, девятого и десятого транзисторов, а выход является вторым выходом дешифратора.

, первый Т11-0 и второй T21-0 транзисторы с каналом первого типа проводимости, истоки которых соединены между собой и с истоками транзисторов первого и второго блоков параллельно включенных n транзисторов, затворы соединены, соответственно, с нулевым прямым и нулевым инверсным адресными входами, и сток первого транзистора, соединен со стоками транзисторов первого блока параллельно включенных n транзисторов, а сток второго транзистора - со стоками второго блока параллельно включенных n транзисторов, третий Т12 и четвертый T22 транзисторы с каналом второго типа проводимости, затворы которых соединены с входом выбора режима, истоки - с выводом питания первого уровня напряжения, а сток третьего транзистора - со стоком первого транзистора и со стоками транзисторов первого блока параллельно включенных n транзисторов, и сток четвертого транзистора - со стоком второго транзистора и со стоками второго блока параллельно включенных n транзисторов, пятый транзистор Т14 с каналом первого типа проводимости и шестой транзистор T15 с каналом второго типа проводимости, стоки которых соединены друг с другом, затворы соединены друг с другом, со стоками первого и третьего транзисторов и со стоками транзисторов первого блока параллельно включенных n транзисторов, исток пятого транзистора - со стоками второго и четвертого транзисторов и со стоками транзисторов второго блока параллельно включенных n транзисторов, а исток шестого транзистора соединен с выводом питания первого уровня напряжения, седьмой транзистор T16 с каналом второго типа проводимости, затвор которого соединен с входом выбора режима, исток - с выводом питания первого уровня напряжения, а сток - со стоками пятого и шестого транзисторов, восьмой транзистор Т24 с каналом первого типа проводимости и девятый транзистор Т25 с каналом второго типа проводимости, стоки которых соединены друг с другом, затворы соединены друг с другом, со стоками второго и четвертого транзисторов, со стоками транзисторов второго блока параллельно включенных n транзисторов и с истоком пятого транзистора, исток восьмого - со стоками первого и третьего транзисторов, со стоками первого блока параллельно включенных n транзисторов и с затворами пятого и шестого транзисторов, а исток девятого транзистора соединен с выводом питания первого уровня напряжения, десятый Т26 транзистор с каналом второго типа проводимости, затвор которого соединен с входом выбора режима, исток - с выводом питания первого уровня напряжения, а сток - со стоками восьмого и девятого транзисторов, одиннадцатый транзистор T13, затвор которого соединен с входом выбора режима, сток - с истоками первого и второго транзисторов и с истоками транзисторов первого и второго блоков параллельно включенных n транзисторов, а исток с выводом питания второго уровня напряжения, первый выходной буферный элемент IV1, вход которого соединен со стоками пятого, шестого и седьмого транзисторов, а выход является первым выходом дешифратора, второй выходной буферный элемент IV2, вход которого соединен со стоками восьмого, девятого и десятого транзисторов, а выход является вторым выходом дешифратора.

Однако, указанный дешифратор в выбранном режиме имеет высокий уровень помехи, возникающей на одном из выходов WL, в виде импульса высокого уровня напряжения, когда оба выхода должны остаться в невыбранном состоянии. Данная помеха возникает, когда на адресные входы A1÷An и  подана такая комбинация уровней напряжений входных сигналов, что хотя бы один из них имеет напряжение высокого уровня в момент поступления сигнала СЕ высокого уровня напряжения.

подана такая комбинация уровней напряжений входных сигналов, что хотя бы один из них имеет напряжение высокого уровня в момент поступления сигнала СЕ высокого уровня напряжения.

Данная схема дешифратора допускает шунтирование узлов (N11) и (N12) на вывод питания второго уровня напряжения через открытый транзистор Т13 и через различное количество транзисторов первого и второго блоков параллельно включенных n транзисторов. Поэтому время разряда этих узлов из напряжения высокого уровня в напряжение низкого уровня будет различным, и величина этого различия будет определяться различием количества шунтирующих транзисторов в каждом блоке. Это позволяет напряжению низкого уровня, появившемуся раньше другого, поступить на вход выходного буферного элемента, например, через открытый транзистор Т14 (или Т24) до появления на его затворе отстающего напряжения низкого уровня, которое должно его закрыть и не допустить подобное проникновение. Так как величина этого отставания может быть неопределенно большой, выходной буферный элемент может переключиться и передать напряжение недостоверного уровня на выход WL1 (или WL2) дешифратора, что нарушает его правильное функционирование и, следовательно, правильное функционирование устройств, для которых входными сигналами служат выходные сигналы дешифратора. Тем самым нарушается надежность работы дешифратора. Например, если дешифратор используется в запоминающем устройстве, в котором адресные шины матрицы запоминающих элементов подсоединены к выходам дешифратора, может произойти одновременный выбор нескольких адресных шин, что, в свою очередь, приведет к сбою чтения (или записи) информации в этом запоминающем устройстве.

Кроме того, в указанной схеме дешифратора в цепи разряда между узлом входа первого (или второго) выходного буферного элемента и узлом N21 (или N11) включен только один транзистор Т14 (или T24), что допускает быстрое проникновение напряжения низкого уровня через этот открытый транзистор и усугубляет ситуацию возникновения импульса помехи.

Помимо этого, известный дешифратор содержит большее количество элементов при любом n>1 и требует большего количества коммутационных связей. Так как ни один физический объект не может обладать абсолютной надежностью, то использование при создании любого устройства большего количества компонентов и связей между ними снижает надежность работы этого устройства.

Все вышесказанное свидетельствует о недостаточной надежности этого дешифратора.

Кроме того, наличие двух блоков параллельно включенных n транзисторов увеличивает массогабаритные показатели дешифратора при любом n>1.

Задачей предлагаемого изобретения является повышение надежности дешифратора и снижение массогабаритных показателей.

Поставленная задача достигается тем, что в дешифратор, содержащий полевые транзисторы первого и второго типа проводимости, нулевой прямой, нулевой инверсный и первый, второй,..., n-ый адресные входы, вход выбора режима, выводы питания первого и второго уровня напряжения, блок параллельно включенных n транзисторов с каналом первого типа проводимости, стоки которых соединены между собой и истоки соединены между собой, а затворы соединены с соответствующими n-ми адресными входами, первый и второй транзисторы с каналом первого типа проводимости, истоки которых соединены между собой, затворы соединены соответственно с нулевым прямым и нулевым инверсным адресными входами и сток первого транзистора соединен со стоками транзисторов блока параллельно включенных n транзисторов, третий и четвертый транзисторы с каналом второго типа проводимости, затворы которых соединены с входом выбора режима, истоки - с выводом питания первого уровня напряжения, а сток третьего транзистора со стоком первого транзистора и со стоками транзисторов блока параллельно включенных n транзисторов, и сток четвертого транзистора - со стоком второго транзистора, пятый транзистор с каналом первого типа проводимости и шестой транзистор с каналом второго типа проводимости, стоки которых соединены друг с другом, затворы соединены друг с другом, со стоками первого и третьего транзисторов и со стоками транзисторов блока параллельно включенных n транзисторов, а исток шестого транзистора соединен с выводом питания первого уровня напряжения, седьмой транзистор с каналом второго типа проводимости, затвор которого соединен с входом выбора режима, исток - с выводом питания первого уровня напряжения, а сток - со стоками пятого и шестого транзисторов, восьмой транзистор с каналом первого типа проводимости и девятый транзистор с каналом второго типа проводимости, стоки которых соединены друг с другом, затворы соединены друг с другом и со стоками второго и четвертого транзисторов, а исток девятого транзистора соединен с выводом питания первого уровня напряжения, десятый транзистор с каналом второго типа проводимости, затвор которого соединен с входом выбора режима, исток - с выводом питания первого уровня напряжения, а сток - со стоками восьмого и девятого транзисторов, одиннадцатый транзистор с каналом первого типа проводимости, затвор которого соединен с входом выбора режима, первый выходной буферный элемент, вход которого соединен со стоками пятого, шестого и седьмого транзисторов, а выход является первым выходом дешифратора, второй выходной буферный элемент, вход которого соединен со стоками восьмого, девятого и десятого транзисторов, а выход является вторым выходом дешифратора, введен двенадцатый транзистор с каналом первого типа проводимости, затвор которого соединен с входом выбора режима, сток - с истоком восьмого транзистора, а исток - с затворами пятого и шестого транзисторов, со стоками первого и третьего транзисторов и со стоками транзисторов блока параллельно включенных n транзисторов, причем сток одиннадцатого транзистора соединен с истоком пятого транзистора, исток - с затворами восьмого и девятого транзисторов, со стоками второго и четвертого транзисторов и с истоками транзисторов блока параллельно включенных n транзисторов, а истоки первого и второго транзисторов соединены с выводом питания второго уровня напряжения.

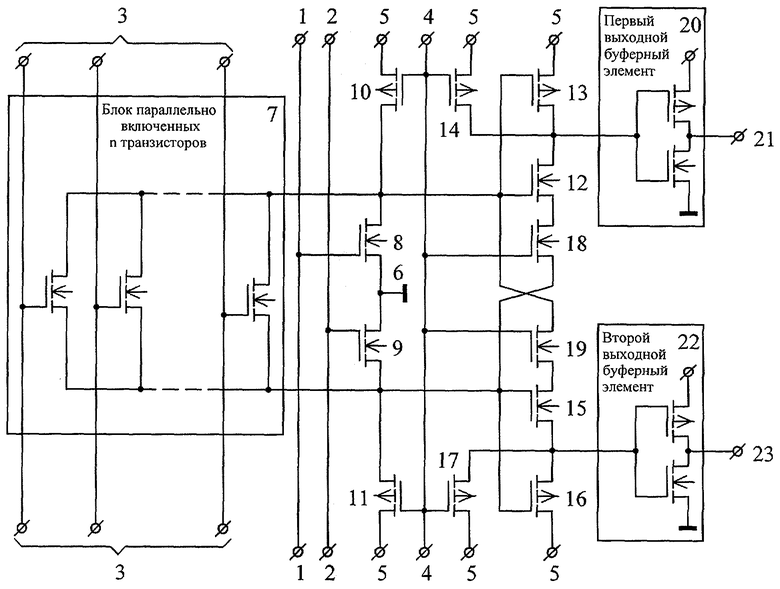

На чертеже приведен предлагаемый дешифратор, реализованный на КМОП транзисторах, в котором в качестве полевых транзисторов с каналом первого типа проводимости использованы N-канальные МОП транзисторы, а в качестве полевых транзисторов с каналом второго типа проводимости - Р-канальные МОП транзисторы, на выводы питания первого и второго уровней напряжения поданы напряжения, соответственно, высокого и низкого уровней, а выходные буферные элементы выполнены в виде инверторов на КМОП транзисторах.

Предлагаемый дешифратор содержит: полевые транзисторы первого и второго типа проводимости, нулевой прямой 1, нулевой инверсный 2 и первый, второй,..., n-ый 3 адресные входы, вход выбора режима 4, выводы питания первого 5 и второго 6 уровня напряжения, блок параллельно включенных n транзисторов 7 с каналом первого типа проводимости, стоки которых соединены между собой и истоки соединены между собой, а затворы соединены с соответствующими n-ми адресными входами 3, первый 8 и второй 9 транзисторы с каналом первого типа проводимости, истоки которых соединены с выводом питания второго уровня напряжения 6, затворы соединены соответственно с нулевым прямым 1 и нулевым инверсным 2 адресными входами и сток первого транзистора 8 соединен со стоками транзисторов блока параллельно включенных n транзисторов 7, а сток второго транзистора 9 - с истоками транзисторов блока параллельно включенных n транзисторов 7, третий 10 и четвертый 11 транзисторы с каналом второго типа проводимости, затворы которых соединены с входом выбора режима 4, истоки - с выводом питания первого уровня напряжения 5, а сток третьего транзистора 10 со стоком первого транзистора 8 и со стоками транзисторов блока параллельно включенных n транзисторов 7, и сток четвертого транзистора 11 - со стоком второго транзистора 9 и с истоками транзисторов блока параллельно включенных n транзисторов 7, пятый транзистор 12 с каналом первого типа проводимости и шестой транзистор 13 с каналом второго типа проводимости, стоки которых соединены друг с другом, затворы соединены друг с другом, со стоками первого 8 и третьего 10 транзисторов и со стоками транзисторов блока параллельно включенных n транзисторов 7, а исток шестого транзистора 13 соединен с выводом питания первого уровня напряжения 5, седьмой транзистор 14 с каналом второго типа проводимости, затвор которого соединен с входом выбора режима 4, исток - с выводом питания первого уровня напряжения 5, а сток - со стоками пятого 12 и шестого 13 транзисторов, восьмой транзистор 15 с каналом первого типа проводимости и девятый транзистор 16 с каналом второго типа проводимости, стоки которых соединены друг с другом, затворы соединены друг с другом, со стоками второго 9 и четвертого 11 транзисторов и с истоками транзисторов блока параллельно включенных n транзисторов 7, а исток девятого транзистора 16 соединен с выводом питания первого уровня напряжения 5, десятый транзистор 17 с каналом второго типа проводимости, затвор которого соединен с входом выбора режима 4, исток - с выводом питания первого уровня напряжения 5, а сток - со стоками восьмого 15 и девятого 16 транзисторов, одиннадцатый транзистор 18 с каналом первого типа проводимости, затвор которого соединен с входом выбора режима 4, сток - с истоком пятого транзистора 12, исток - с затворами восьмого 15 и девятого 16 транзисторов, со стоками второго 9 и четвертого 11 транзисторов и истоками транзисторов блока параллельно включенных п транзисторов 7, двенадцатый 19 транзисторы с каналом первого типа проводимости, затвор которого соединен с входом выбора режима 4, сток - с истоком восьмого транзистора 15, исток - с затворами пятого 12 и шестого 13 транзисторов, со стоками первого 8 и третьего 10 транзисторов и со стоками транзисторов блока параллельно включенных n транзисторов 7, первый выходной буферный элемент 20, вход которого соединен со стоками пятого 12, шестого 13 и седьмого 14 транзисторов, а выход является первым выходом 21 дешифратора, второй выходной буферный элемент 22, вход которого соединен со стоками восьмого 15, девятого 16 и десятого 17 транзисторов, а выход является вторым выходом 23 дешифратора.

Допускается другое выполнение выходных буферных элементов. Например, в виде инверсного буферного каскада построенного на нечетном количестве последовательно соединенных инверторов, в виде повторителя построенного на четном количестве последовательно соединенных инверторов или в виде низкоомного проводника, элемента памяти и т.д.

Дешифратор работает следующим образом.

В исходном состоянии, которому соответствует невыбранный режим, на входе выбора режима 4 и на адресных входах нулевом прямом 1 и нулевом инверсном 2 установлено напряжение низкого уровня. На адресных входах 3 блока 7 уровень напряжения может быть любым, от низкого до высокого, или даже третье состояние, т.е. состояние высокого сопротивления выхода. N-канальные МОП транзисторы 8, 9,18 и 19 закрыты, а Р-канальные МОП транзисторы 10, 11, 14 и 17 открыты напряжением низкого уровня, поступающим на их затворы. Через открытые транзисторы 10, 11, 14 и 17 в узлах, к которым подключены стоки этих транзисторов, установлено напряжение высокого уровня, которое поступает на входы выходных буферных элементов 20 и 21 и удерживает N-канальные МОП транзисторы 12 и 15 в открытом состоянии, а Р-канальные МОП транзисторы 13 и 16 в закрытом. В результате того, что на входах выходных буферных элементов 20 и 21 напряжение высокого уровня, на их выходах 21 и 23 установлено напряжение низкого уровня, что соответствует невыбранному состоянию выходов 21 и 23 дешифратора.

Для изменения режима работы дешифратора на выбранный режим необходимо на адресных входах 1, 2, 3 установить необходимую комбинацию уровней напряжений адресных сигналов и подать на вход выбора режима 4 напряжение высокого уровня.

Переключение выхода 21 дешифратора в состояние выбора, чему соответствует появление на нем напряжения высокого уровня, требует такой комбинации уровней напряжений адресных сигналов на адресных входах 1, 2 и 3, чтобы все N-канальные МОП транзисторы блока 7 и транзистор 8 были закрыты, а транзистор 9 - открыт. Так как на вход выбора режима 4 поступает напряжение высокого уровня, транзисторы 10, 11, 14 и 17 закрываются, а транзисторы 18 и 19 открываются. При этом транзистор 13 удерживается в закрытом состоянии, а транзистор 12 - в открытом емкостью узла, к которому подключены их затворы. В то же время узел, к которому подключены затворы транзисторов 15 и 16 и исток транзистора 18, через открытый транзистор 9, разряжается до напряжения низкого уровня и транзистор 15 закрывается, а транзистор 16 открывается. Напряжение высокого уровня, поступающее через открытый транзистор 16 на вход второго выходного буферного элемента 22, сохраняет на его выходе напряжение низкого уровня и выход 23 дешифратора остается в невыбранном состоянии. Одновременно напряжение низкого уровня, поступающее на исток транзистора 18, через открытые транзисторы 18 и 12, разряжает емкость узла, к которому подключен вход первого выходного буферного элемента 20, до напряжения низкого уровня. При этом первый выходной буферный элемент 20 переключается и на его выходе устанавливается напряжение высокого уровня, что соответствует выбранному состоянию первого выхода 21 дешифратора.

Переключение выхода 23 дешифратора в состояние выбора, чему соответствует появление на нем напряжения высокого уровня, требует такой комбинации уровней напряжений адресных сигналов на адресных входах 1, 2 и 3, чтобы все N-канальные МОП транзисторы блока 7 и транзистор 9 были закрыты, а транзистор 8 - открыт. Так как на вход выбора режима 4 поступает напряжение высокого уровня, транзисторы 10, 11, 14 и 17 закрываются, а транзисторы 18 и 19 открываются. При этом транзистор 16 удерживается в закрытом состоянии, а транзистор 15 - в открытом емкостью узла, к которому подключены их затворы. В то же время узел, к которому подключены затворы транзисторов 12 и 13 и исток транзистора 19, через открытый транзистор 8 разряжается до напряжения низкого уровня и транзистор 12 закрывается, а транзистор 13 открывается. Напряжение высокого уровня, поступающее через открытый транзистор 13 на вход первого выходного буферного элемента 20, сохраняет на его выходе напряжение низкого уровня и выход 21 дешифратора остается в невыбранном состоянии. Одновременно напряжение низкого уровня, поступающее на исток транзистора 19, через открытые транзисторы 19 и 15, разряжает емкость узла, к которому подключен вход второго выходного буферного элемента 22, до напряжения низкого уровня. При этом второй выходной буферный элемент 22 переключается и на его выходе устанавливается напряжение высокого уровня, что соответствует выбранному состоянию второго выхода 23 дешифратора.

Для реализации состояния дешифратора, в котором в выбранном режиме оба выхода и 21 и 23 остаются в невыбранном состоянии, то есть на них сохраняется напряжение низкого уровня, необходимо на адресных входах 1, 2 и 3 установить такую комбинацию уровней напряжений адресных сигналов, чтобы хотя бы один из транзисторов блока 7 и один из транзисторов 8 или 9 были открыты и подать на вход выбора режима 4 напряжение высокого уровня.

В случае, когда открыт транзистор 8 и, соответственно, транзистор 9 закрыт, реализация данного режима происходит следующим образом.

Как было сказано ранее, транзисторы 8 и один или n транзисторов блока 7 открыты напряжениями высокого уровня, поступающими на их затворы по соответствующим адресным входам 1 и 3. Так как на затвор транзистора 9 поступает напряжение дополняющего низкого уровня, то транзистор 9 закрыт этим напряжением. Напряжение высокого уровня, поступающее по входу выбора режима 4 на затворы транзисторов 10, 11, 14 и 17, закрывает эти транзисторы. Одновременно это же напряжение поступает на затворы транзисторов 18 и 19 и открывает их. При этом через открытый транзистор 8 емкость узла, к которому подсоединен его сток, разряжается до напряжения низкого уровня, которое, в свою очередь, поступает на стоки транзисторов блока 7, транзистора 10, затворы транзисторов 12 и 13 и исток транзистора 19. Это напряжение закрывает транзистор 12, открывает транзистор 13 и поступает через открытые транзисторы блока 7 и транзистор 19 на истоки транзисторов блока 7 и транзисторов 15 и 18, затворы транзисторов 15 и 16 и стоки транзисторов 9 и 11. При этом транзистор 15 закрывается, а транзистор 16 открывается. Поэтому напряжение высокого уровня через открытые транзисторы 13 и 16 поступает, соответственно, на входы выходных буферных элементов 20 и 22, тем самым, удерживая на их выходах напряжение низкого уровня, т.е. выходы 21 и 23 дешифратора сохраняются в невыбранном состоянии.

В другом случае, когда открыт транзистор 9 и транзистор 8 закрыт, на их затворы по адресным входам 2 и 1 поступают напряжения, соответственно, высокого и низкого уровней. Поэтому через открытый транзистор 9, узел, к которому подсоединен сток этого транзистора, разряжается до напряжения низкого уровня, которое, в свою очередь, поступает на истоки транзисторов блока 7, сток транзистора 11, затворы транзисторов 15 и 16 и исток транзистора 18. Это напряжение закрывает транзистор 15, открывает транзистор 16 и поступает через открытые транзисторы блока 7 и транзистор 18 на стоки транзисторов блока 7 и истоки транзисторов 12 и 19, затворы транзисторов 12 и 13 и стоки транзисторов 8 и 10. При этом транзистор 12 закрывается, а транзистор 13 открывается. Поэтому напряжение высокого уровня через открытые транзисторы 13 и 16 поступает, соответственно, на входы выходных буферных элементов 20 и 22, тем самым, удерживая на их выходах напряжение низкого уровня, т.е. выходы 21 и 23 дешифратора сохраняются в невыбранном состоянии.

Так как узлы схемы дешифратора, к которым подключены стоки транзисторов 8 и 10, затворы транзисторов 12 и 13, исток транзистора 19 и стоки транзисторов 9 и 11, затворы транзисторов 15 и 16 и исток транзистора 18, шунтируются одинаковым количеством транзисторов блока 7, то исключается возможность большого рассогласования времени разряда этих узлов, что повышает надежность дешифратора.

Кроме того, любой полевой транзистор, работающий в ключевом режиме, имеет конечное время пропускания сигнала через себя, величина которого зависит от характеристик этого транзистора. Поэтому размещение транзисторов 18 и 19 между истоками транзисторов 12 и 15 и узлами, к которым подключены стоки и истоки блока 7, вносит дополнительное препятствие проникновению импульсов помехи на входы выходных буферных элементов 20 и 22, что повышает надежность дешифратора.

Помимо этого, в предлагаемом дешифраторе используется только один блок параллельно включенных n транзисторов, вместо двух у прототипа, что уменьшает количество используемых элементов при любом n>1 для построения дешифратора и, следовательно, повышает надежность его работы и уменьшает его массогабаритные показатели.

Таким образом, в предлагаемом дешифраторе повышена надежность его работы и в то же время уменьшены его массогабаритные показатели.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ | 1991 |

|

RU2010361C1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2021 |

|

RU2771447C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2018 |

|

RU2679186C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2022 |

|

RU2787930C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2009 |

|

RU2408058C2 |

| ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКОГО УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2642416C1 |

| ВЫСОКОВОЛЬТНЫЙ ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2019 |

|

RU2702979C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих тактируемых запоминающих устройств большой емкости. Технический результат заключается в повышении надежности и уменьшении массогабаритных показателей. Дешифратор содержит полевые транзисторы первого и второго типа проводимости (8-19), нулевой прямой (1), нулевой инверсный (2) и первый, второй,..., n-ый (3) адресные входы, вход выбора режима (4), выводы питания первого (5) и второго (6) уровня напряжения, блок параллельно включенных n транзисторов (7) с каналом первого типа, затворы которых соединены с соответствующими n-ми входами (3), первый выходной буферный элемент (20), выход которого является первым выходом (21) дешифратора, второй выходной буферный элемент (22), выход которого является вторым выходом (23) дешифратора. 1 ил.

Дешифратор, содержащий полевые транзисторы первого и второго типа проводимости, нулевой прямой, нулевой инверсный и первый, второй,..., n-й адресные входы, вход выбора режима, выводы питания первого и второго уровня напряжения, блок параллельно включенных n транзисторов с каналом первого типа проводимости, стоки которых соединены между собой и истоки соединены между собой, а затворы соединены с соответствующими n-ми адресными входами, первый и второй транзисторы с каналом первого типа проводимости, истоки которых соединены между собой, затворы соединены соответственно с нулевым прямым и нулевым инверсным адресными входами, и сток первого транзистора соединен со стоками транзисторов блока параллельно включенных n транзисторов, третий и четвертый транзисторы с каналом второго типа проводимости, затворы которых соединены с входом выбора режима, истоки - с выводом питания первого уровня напряжения, а сток третьего транзистора - со стоком первого транзистора и со стоками транзисторов блока параллельно включенных n транзисторов, и сток четвертого транзистора - со стоком второго транзистора, пятый транзистор с каналом первого типа проводимости и шестой транзистор с каналом второго типа проводимости, стоки которых соединены друг с другом, затворы соединены друг с другом, со стоками первого и третьего транзисторов и со стоками транзисторов блока параллельно включенных n транзисторов, а исток шестого транзистора соединен с выводом питания первого уровня напряжения, седьмой транзистор с каналом второго типа проводимости, затвор которого соединен с входом выбора режима, исток - с выводом питания первого уровня напряжения, а сток - со стоками пятого и шестого транзисторов, восьмой транзистор с каналом первого типа проводимости и девятый транзистор с каналом второго типа проводимости, стоки которых соединены друг с другом, затворы соединены друг с другом и со стоками второго и четвертого транзисторов, а исток девятого транзистора соединен с выводом питания первого уровня напряжения, десятый транзистор с каналом второго типа проводимости, затвор которого соединен с входом выбора режима, исток - с выводом питания первого уровня напряжения, а сток - со стоками восьмого и девятого транзисторов, одиннадцатый транзистор с каналом первого типа проводимости, затвор которого соединен с входом выбора режима, первый выходной буферный элемент, вход которого соединен со стоками пятого, шестого и седьмого транзисторов, а выход является первым выходом дешифратора, второй выходной буферный элемент, вход которого соединен со стоками восьмого, девятого и десятого транзисторов, а выход является вторым выходом дешифратора, отличающийся тем, что в него введен двенадцатый транзистор с каналом первого типа проводимости, затвор которого соединен с входом выбора режима, сток - с истоком восьмого транзистора, а исток - с затворами пятого и шестого транзисторов, со стоками первого и третьего транзисторов и со стоками транзисторов блока параллельно включенных n транзисторов, причем сток одиннадцатого транзистора соединен с истоком пятого транзистора, исток - с затворами восьмого и девятого транзисторов, со стоками второго и четвертого транзисторов и с истоками транзисторов блока параллельно включенных n транзисторов, а истоки первого и второго транзисторов соединены с выводом питания второго уровня напряжения.

| US 4401903, 30.08.1983 | |||

| Дешифратор на КМДП-транзисторах | 1982 |

|

SU1113853A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| US 4446386, 01.05.1984 | |||

| US 4350905, 21.09.1982. | |||

Авторы

Даты

2007-09-27—Публикация

2005-12-02—Подача