иг

-5

Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для LU-разложения матриц | 1987 |

|

SU1509933A1 |

| Устройство решения систем логических уравнений | 2017 |

|

RU2654137C1 |

| Устройство обнаружения и коррекции ошибки модулярного кода | 2017 |

|

RU2653257C1 |

| Устройство поиска информации | 2017 |

|

RU2656736C1 |

| Устройство поиска информации | 2019 |

|

RU2724788C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Цифровой нелинейный корректор сигнала | 1982 |

|

SU1075423A1 |

| Устройство для анализа структурной характеристики показателя преломления атмосферы | 1991 |

|

SU1800426A1 |

| Устройство автоматической гамма-коррекции телевизионного сигнала | 1986 |

|

SU1345375A1 |

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

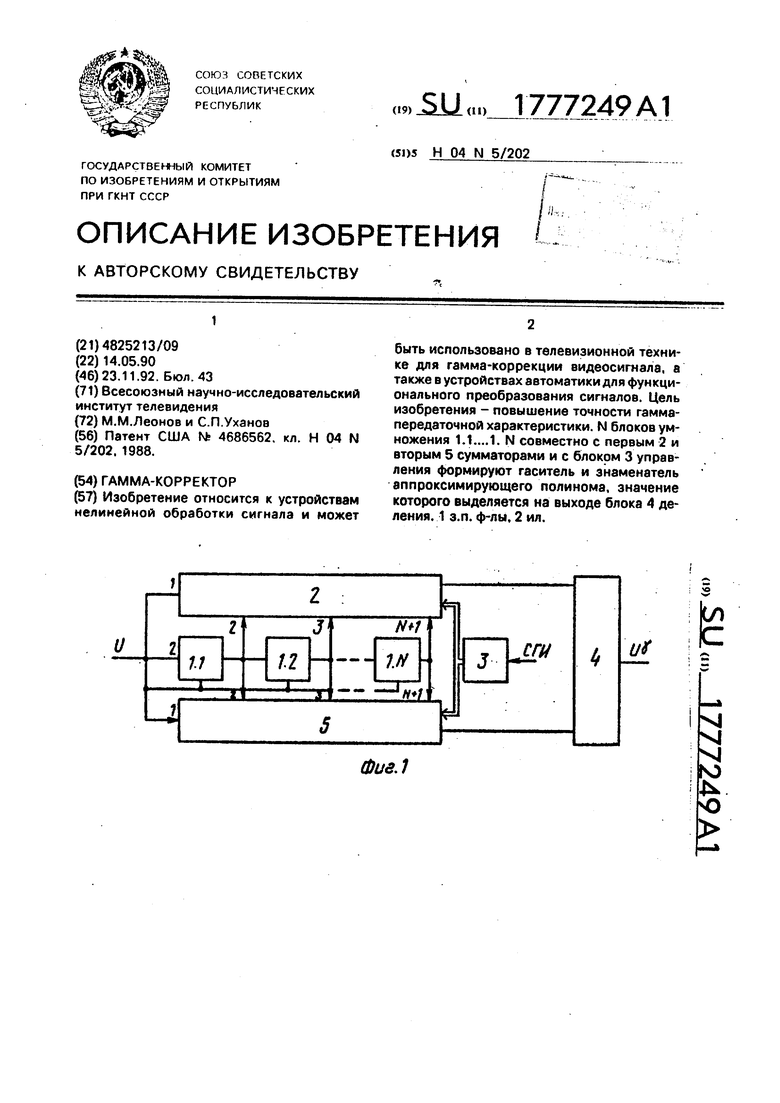

Изобретение относится к устройствам нелинейной обработки сигнала и может быть использовано в телевизионной технике для гамма-коррекции видеосигнала, а также в устройствах автоматики для функционального преобразования сигналов. Цель изобретения - повышение точности гамма- передаточной характеристики. N блоков умножения 1.1....1. N совместно с первым 2 и вторым 5 сумматорами и с блоком 3 управления формируют гаситель и знаменатель аппроксимирующего полинома, значение которого выделяется на выходе блока 4 деления. 1 з.п. ф-лы, 2 ил.

Фиг.1

Изобретение относится к устройствам нелинейной обработки сигнала и может быть использовано в телевизионной технике для гамма-коррекции видеосигнала, а также в устройствах автоматики для функционального преобразования сигналов,

Известно устройство гамма-корректора (заявка ЕПВ N0.086.958), содержащее устройство гамма-коррекции и устройство суммирования. Также известно устройство телевизионного гамма-корректора ЕПВ N 0.087.181), которое содержит шесть резисторов, дифференциальный усилитель, цепь обратной связи с нелинейной характеристикой. Общими недостатками этих устройств является малая точность и температурная нестабильность передаточной характеристики, а для первого устройства и сложность технической реализации устройства гамма- коррекции. Наиболее близким к предлагаемому по технической сущности является гамма-корректор (1), содержащий первую и вторую схему смешения, схему гамма-коррекции с фиксированной степенью схему изменения степени гамма-коррекции, схему фиксации, устройство выборки-хранения, операционный усилитель, процессор, блок памяти, дисплей и ЦАП.

Но данное устройство обладает следующими недостатками: для поддержания точностных качеств устройства требуется введение в видеосигнал дополнительных элементов, как то опознавательных импульсов на гасящих интервалах для поддержания стабильности гаммы и дополнительного пьедестала, величина которого изменяется в зависимости от показателя степени гаммы. Это позволяет улучшить характеристики в сравнении с подобными аналоговыми устройствами формирования у-передаточной характеристики. Но тем не менее, в данном устройстве остаются 3 источника нестабильности: устройство изменения степени гамма-коррекции, устройство стабили- зации уровня подставки, устройство отслеживания уровня вспомогательного импульса. Последние два устройства вследствие неидеальности и разброса параметров используемых в них операционных усилителей и температурного дрейфа имеют нестабильность до 2%. В устройстве изменения степени гамма-коррекции происходит накопление ошибок нестабильности от температурного дрейфа элементов, от неточности стабилизации уровня подставки и неточности отслеживания уровня вспомогательного импульса. В результате суммирования всех погрешностей общая ошибка может достигать Ч3% (в середине диапазона). К краям диапазона регулировки ошибка возрастает

еще в 2 раза. С учетом того, что неидеальность каналов RGB трехтрубочной камеры наиболее сильно ощущается в области темных участков изображения (Кус за счет гамма-коррекции до 6 раз), точности гамма-коррекции данной схемы недостаточно для высококачественной цветной передающей камеры, в особенности камеры ТВВЧ (телевидение высокой четкости).

0 Целью настоящего изобретения является повышение точности формирования гамма-передаточной характеристики.

Поставленная цель достигается за счет того, что в устройство, содержащее как и

5 прототип перемножитель и блок управления, введены N-1 блоки умножения, первый и второй сумматоры и блок деления, первый и второй входы первого блока умножения, а также первые входы N-1 блоков умножения

0 и первого и второго сумматоров соединены между собой и являются входом устройства, N-1 блоков умножения соединены последовательно, а их выходы соединены с соответствующими входами сумматора.

5 управляющие входы сумматора соединены с выходами блока управления, выходы первого и второго сумматоров соединены с соответствующими входами блока деления, выход которого является выходом устройст0 ва.

Совокупность указанных признаков, характеризующих предлагаемое решение не присуща ни одному из известных технических решений и является новой.

5 Введение N-1 блоков умножения, сумматоров и блока деления со связями между собой и другими блоками устройства, как описано выше, позволило повысить точность формирования и температурную ста0 бильность гамма передаточной характеристики за счет формирования ее полиномиальным способом..

Введение N-1 блоков умножения позволяет получить степенную функцию от вход5 ного сигнала с пиковой ошибкой не более 0,7-1% (Тимонтеев В.Н. и др. Аналоговые перемножители сигналов в радиоэлектронной аппаратуре, М.: Радио и связь, 1982, с. 39-72). Сумматор позволяет обеспечить точ0 ность суммирования 0,25% с неидентичностью между каналами до 0,1%. Если проводить дополнительную сортировку резисторов, задающих коэффициент суммиро- вания, то можно повысить точность

5 суммирования до 0,1%. Суммарная же точность предлагаемого устройства с учетом погрешностей не хуже 0,5-1 % во всем диапазоне изменения гамма-характеристики.

Это позволяет сделать вывод о том, что заявляемое техническое решение обладает

существенными отличиями по отношению к известному решению.

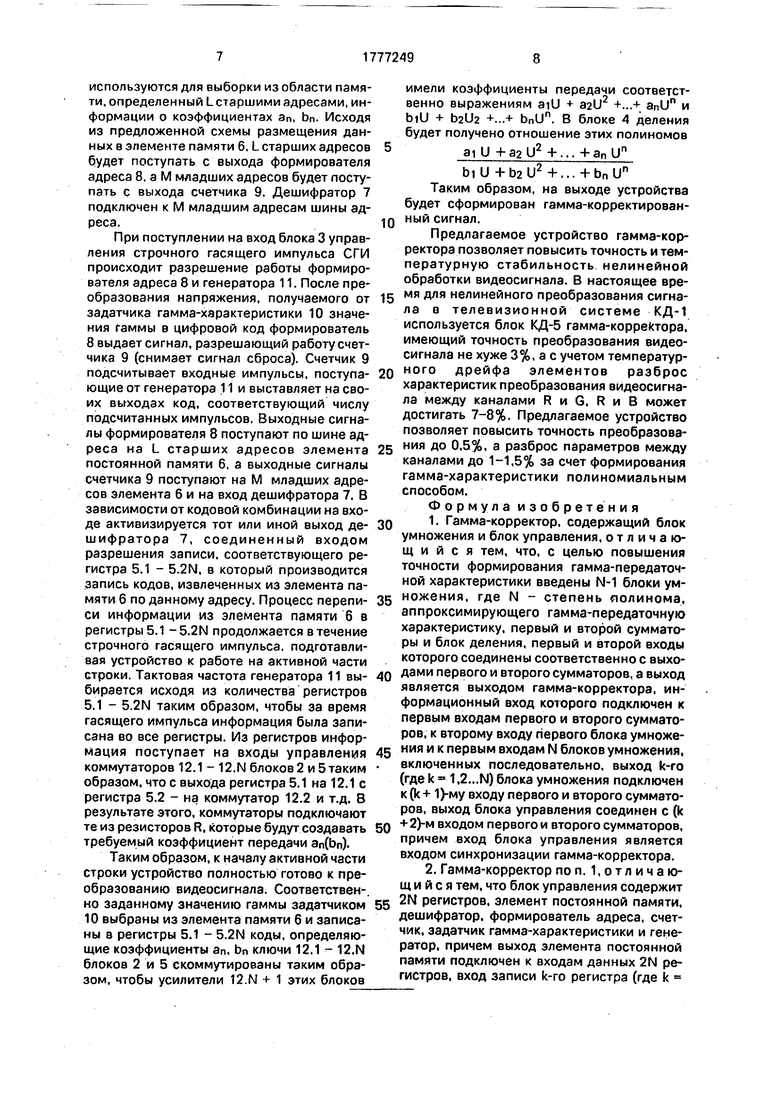

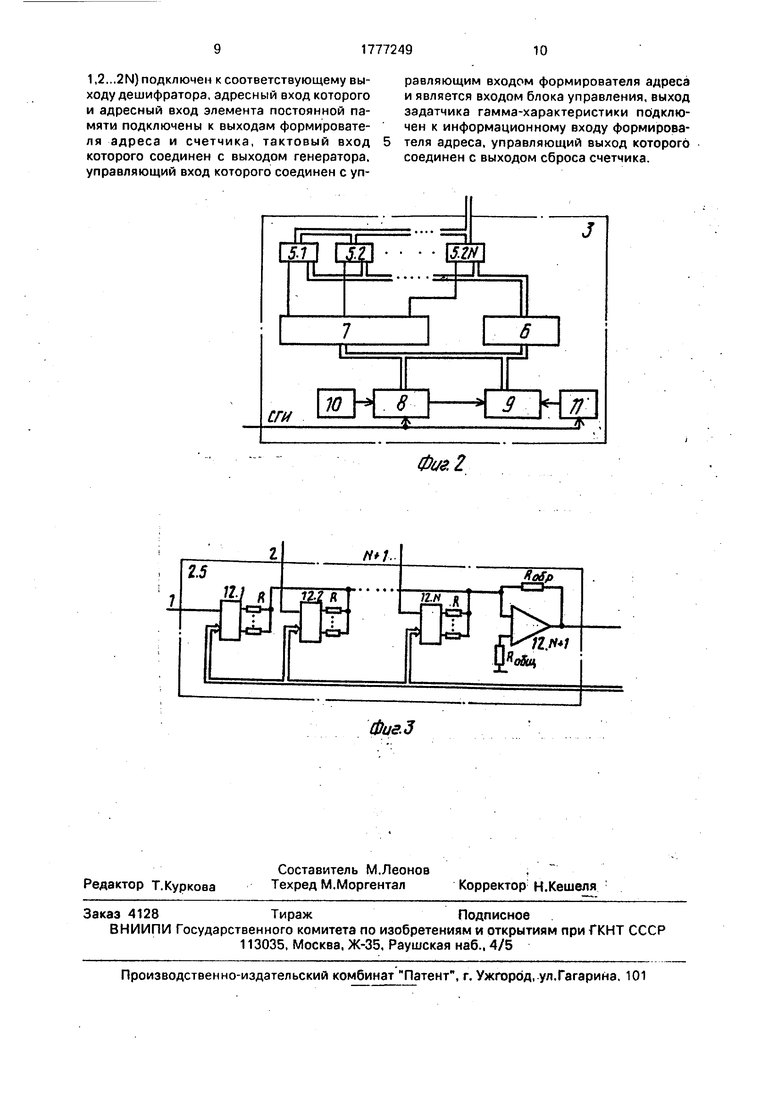

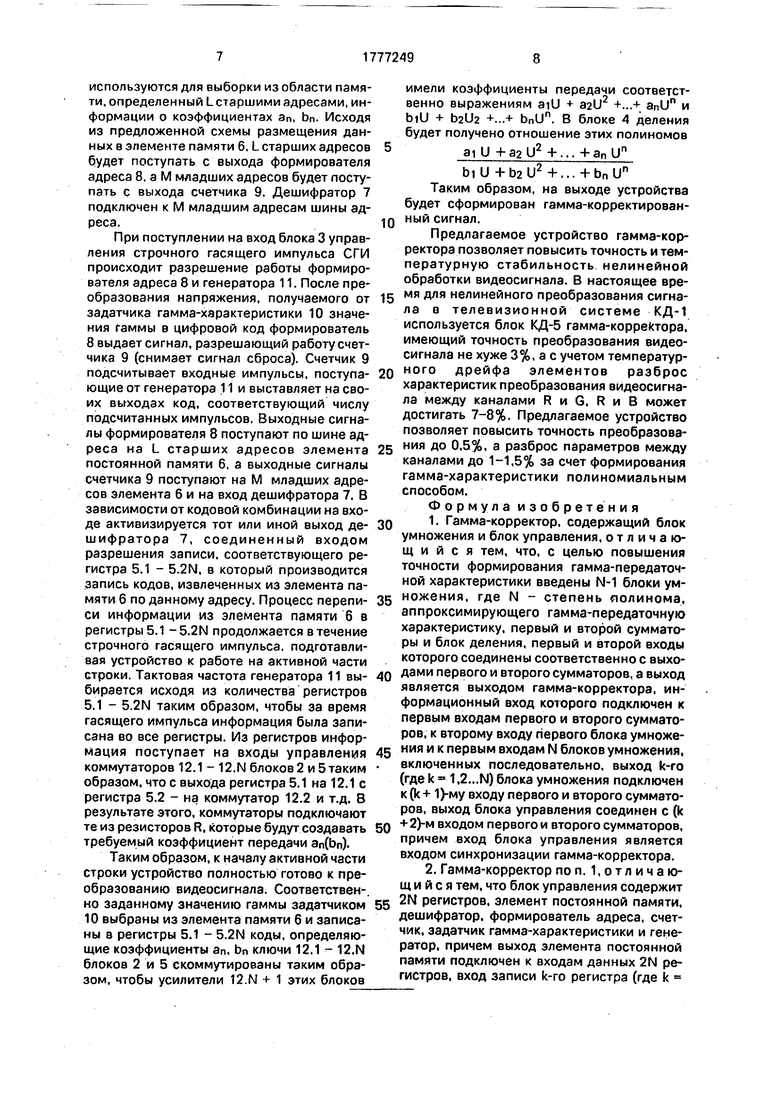

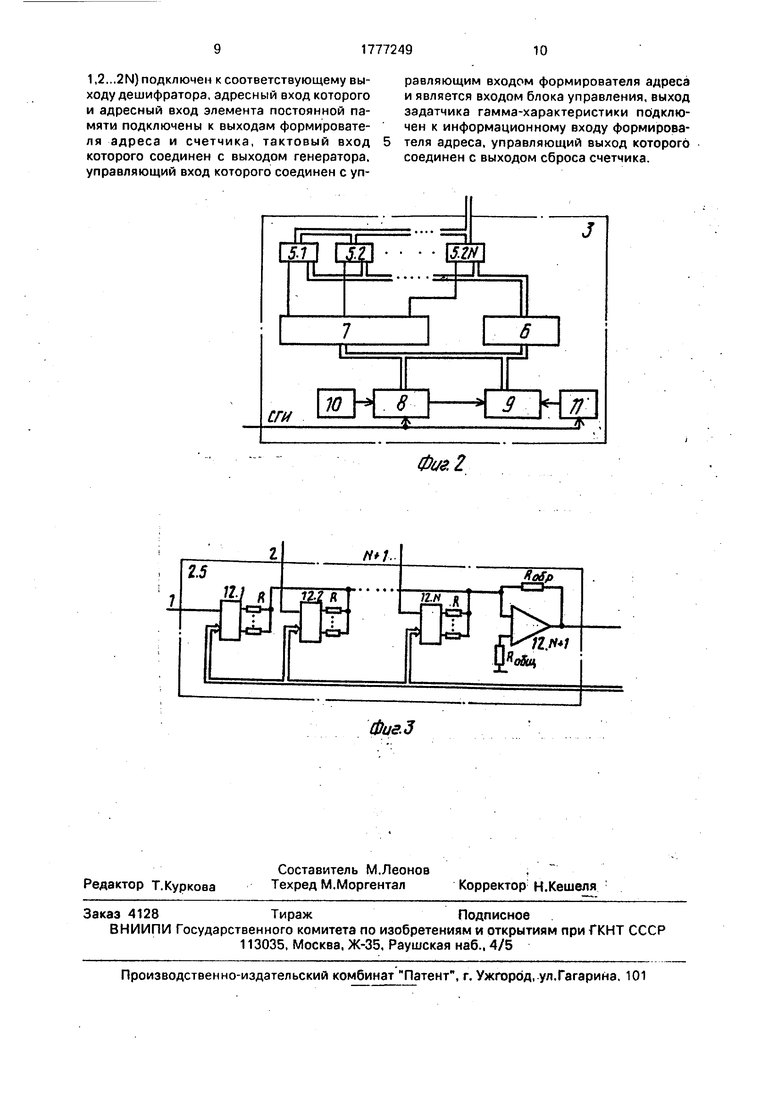

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - блок управления; на фиг, 3 - сумматор.

Гамма-корректор (фиг. 1) содержит N блоков умножения 1.1 -1.N, первый 2 и второй 5 сумматоры, блок 3 управления, блок 4 деления. При этом первый и второй входы первого блока умножения 1.1, а также первые входы блоков умножения 1.2 -1 .N и сумматоров 2, 5 соединены между собой и являются входом устройства, N - 1 блоков умножения 1.2 - 1.N соединены последовательно, а их выходы соединены с соответствующими входами сумматоров 2, 5, управляющие входы сумматоров 2 и 5 объединены между собой и соединены с выходами блока 3 управления, выходы сумматоров 2 и 5 соединены с соответствующими входами блока 4 деления, выход которого является выходом устройства. Блоки умножения 1.1 - 1.N представляют собой четырехквад- ратный аналоговый перемножитель.

Блок управления 3 (фиг. 2) содержит 2N резисторов 5.1 - 5.2N, элемент постоянной памяти 6, дешифратор 7, формирователь адреса 8. счетчик 9, задатчик гамма-характеристики 10 и генератор 11, причем выход элемента постоянной памяти 6 подключен к входам данных 2N регистров 5.1 - 5.2N, вход записи К-го регистра (где К 1, 2,... 2N) подключен к соответствующему выходу дешифратора 7, адресный вход которого и адресный вход элемента постоянной памяти б подключены к выходам формирователя адреса 8 и счетчика 9, тактовый выход которого соединен с выходом генератора 11, управляющий вход которого соединен с управляющим входом формирователя адреса 8 и является входом блока 3 управления, выход задатчика гамма характеристики 12 подключен к информационному входу формирователя адреса 8, управляющий выход которого соединен с выходом сброса счетчика 9.

Формирователь адреса гаммы может быть выполнен в виде АЦП.

Задатчик значения гаммы выполнен в виде потенциометра, задающего напряжения на аналоговом входе формирователя адреса гаммы.

Сумматор 2,5 (фиг. 3) содержит N коммутаторов 12.1 - 12.N, аналоговые входы которых являются входами блока 2(5), входы управления являются входами управления блока 2(5). а аналоговые выходы коммутаторов 12.1 - 12.N через К резисторов R соединены с инвертирующим входом операционного усилителя 12.N + 1. Между

инвертирующим входом усилителя i2.N + 1 и его выходом включены резисторы Ro6p. a неинвертирующий вход усилителя соединен с землей через резистор Яобщ. Выход

усилителя 12N + 1 является выходом блока.

В основу работы устройства положен

следующий принцип. Нелинейную кривую,

каковой является показательная функция,

можно аппроксимировать в общем случае

полиномом вида

х ai U +32 U2 +... +anUn

bit) +b2U2 +... +bnUn на который накладываются граничные условия вида X, U е 0,1 при U О X 0. при U 1 X 1. Для реализации данного устройства, вначале необходимо рассчитать коэффициенты ап и bn для аппроксимации функции X - U с различным показателем у Г1РИ

работе устройства эти коэффициенты хранятся в элементе памяти 6.

Степень полинома выбирается, исходя из требуемой точности аппроксимации показательной функции.

Работает устройство следующим образом.

На вход поступает видеосигнал U, из которого на перемножителях1.1 - 1.N формируются сигналы U, U2,...L)n. Сформированные сигналы поступают на соответствующие входы сумматоров 2.5 (фиг, 3), в которых с помощью коммутаторов 12,1 - 12.N и Усилителя 12N + 1 формируются сигналы aiU + aaU2 + ... + anUn; biU + 02

U2+...+bnUn. С помощью коммутаторов 12.1 -12.N блока 2 задаются коэффициенты ai ап. а с помощью коммутаторов 12.1 - 12.N блока 5 задаются коэффициенты bi-bn. Задание коэффициентов осуществляется путем коммутации резисторов R.

Сформированные в сумматорах 2 и 5 сигналы aiU + 32U2 +...+ anUn и biU + b2 U2+...+ bnUn поступают на входы блока деления, в котором осуществляется операция

Х aiU+a2U2+...+anUn

bi U -F-b.U2-K..-f-bnUn Рассмотрим работу блока 3 управления. Для этого надо пояснить способ размещения данных о коэффициентах ап и bn в элементе постоянной памяти 6. Пусть элемент 6 имеет К адресов. Тогда L старших адресов, определяемых из выражения С Ј2 , где С - количество стопов (фиксированных значений) гаммы (при значениях гаммы 0,3; 0,35;

0.4; 0,45; 0,5 L 3) будут определять области элемента постоянной памяти б, в которых хранится информация о коэффициентах an и Ьп. Оставшиеся М K-L младших адресов, определяемых из выражения 2N 2м и

используются для выборки из области памяти, определенный L старшими адресами, информации о коэффициентах ап, Ьл. Исходя из предложенной схемы размещения данных в элементе памяти 6, L старших адресов будет поступать с выхода формирователя адреса 8, а М младших адресов будет поступать с выхода счетчика 9. Дешифратор 7 подключен к М младшим адресам шины адреса.

При поступлении на вход блока 3 управления строчного гасящего импульса СГИ происходит разрешение работы формирователя адреса 8 и генератора 11. После преобразования напряжения, получаемого от задатчика гамма-характеристики 10 значения гаммы в цифровой код формирователь 8 выдает сигнал, разрешающий работу счетчика 9 (снимает сигнал сброса). Счетчик 9 подсчитывает входные импульсы, поступающие от генератора 11 и выставляет на своих выходах код, соответствующий числу подсчитанных импульсов. Выходные сигналы формирователя 8 поступают по шине адреса на L старших адресов элемента постоянной памяти 6, а выходные сигналы счетчика 9 поступают на М младших адресов элемента 6 и на вход дешифратора 7. В зависимости от кодовой комбинации на входе активизируется тот или иной выход дешифратора 7, соединенный входом разрешения записи, соответствующего регистра 5.1 - 5.2N. в который производится запись кодов, извлеченных из элемента памяти б поданному адресу. Процесс переписи информации из элемента памяти 6 в регистры 5.1 -5.2N продолжается в течение строчного гасящего импульса, подготавливая устройство к работе на активной части строки. Тактовая частота генератора 11 выбирается исходя из количества регистров 5.1 - 5.2N таким образом, чтобы за время гасящего импульса информация была записана во все регистры. Из регистров информация поступает на входы управления коммутаторов 12.1 - 12.N блоков 2 и 5 таким образом, что с выхода регистра 5.1 на 12.1 с регистра 5.2 - на коммутатор 12.2 и т.д. В результате этого, коммутаторы подключают те из резисторов R, которые будут создавать требуемый коэффициент передачи an(bn).

Таким образом, к началу активной части строки устройство полностью готово к преобразованию видеосигнала. Соответствен-, но заданному значению гаммы задатчиком 10 выбраны из элемента памяти б и записаны в регистры 5.1 - 5.2N коды, определяющие коэффициенты an, bn ключи 12.1 - 12.N блоков 2 и 5 скоммутированы таким образом, чтобы усилители 12.N + 1 этих блоков

имели коэффициенты передачи соответственно выражениям atU + a2ll2 +...+ anil и biU + D2U2 +...+ bnUn. В блоке 4 деления будет получено отношение этих полиномов

ai U +a2U2+...+anUn

biU +b2U2+... + bnUn Таким образом, на выходе устройства будет сформирован гамма-корректированный сигнал.

Предлагаемое устройство гамма-корректора позволяет повысить точность и температурную стабильность нелинейной обработки видеосигнала. В настоящее время для нелинейного преобразования сигнала в телевизионной системе КД-1 используется блок КД-5 гамма-корректора, имеющий точность преобразования видеосигнала не хуже 3%, а с учетом температурного дрейфа элементов разброс характеристик преобразования видеосигнала между каналами R и G, R и В может достигать 7-8%. Предлагаемое устройство позволяет повысить точность преобразования до 0,5%, а разброс параметров между каналами до 1-1,5% за счет формирования гамма-характеристики полиномиальным способом.

Формула изобретения

1- Гамма-корректор, содержащий блок умножения и блок управления, отличающийся тем, что, с целью повышения точности формирования гамма-передаточной характеристики введены N-1 блоки умножения, где N - степень полинома, аппроксимирующего гамма-передаточную характеристику, первый и второй сумматоры и блок деления, первый и второй входы которого соединены соответственно с выходами первого и второго сумматоров, а выход является выходом гамма-корректора, информационный вход которого подключен к первым входам первого и второго сумматоров, к второму входу первого блока умножения и к первым входам N блоков умножения, включенных последовательно, выход к-го (где k 1.2...N) блока умножения подключен к (k + 1)-му входу первого и второго сумматоров, выход блока управления соединен с (k

+ 2)-м входом первого и второго сумматоров, причем вход блока управления является входом синхронизации гамма-корректора.

2N регистров, элемент постоянной памяти, дешифратор, формирователь адреса, счетчик, задатчик гамма-характеристики и генератор, причем выход элемента постоянной памяти подключен к входам данных 2N регистров, вход записи k-ro регистра (где k

Фм2

Фиг.З

| Патент США № 4686562, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1992-11-23—Публикация

1990-05-14—Подача