Устройство относится к вычислительной технике и может быть использовано для контроля исполнения программ контролируемых устройств (системный контроллер, ЦВМ, микроЭВМ, ЭВМ и т. д. ).

Целью изобретения является расширение функциональных возможностей (повышение информативности, точности контроля, сокращения временных затрат на контроль) устройства для визуального контроля за счет обеспечения регистрации результатов контроля в виде информационного массива, за счет обеспечения соответствия регистрируемого адреса и данных фрагмета программы за интервал времени функционирования контролируемого устройства относительно многократно повторяющегося адреса, выбранного оператором.

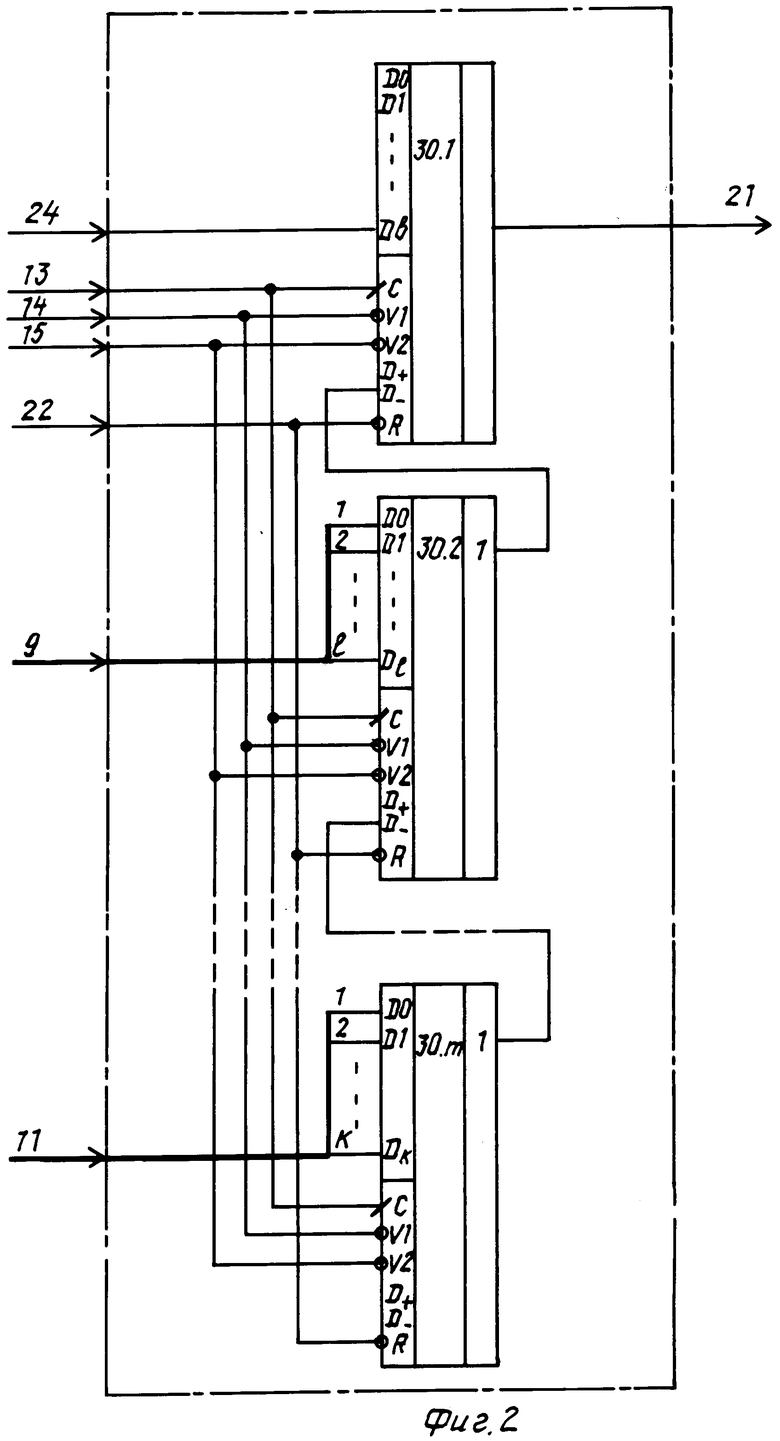

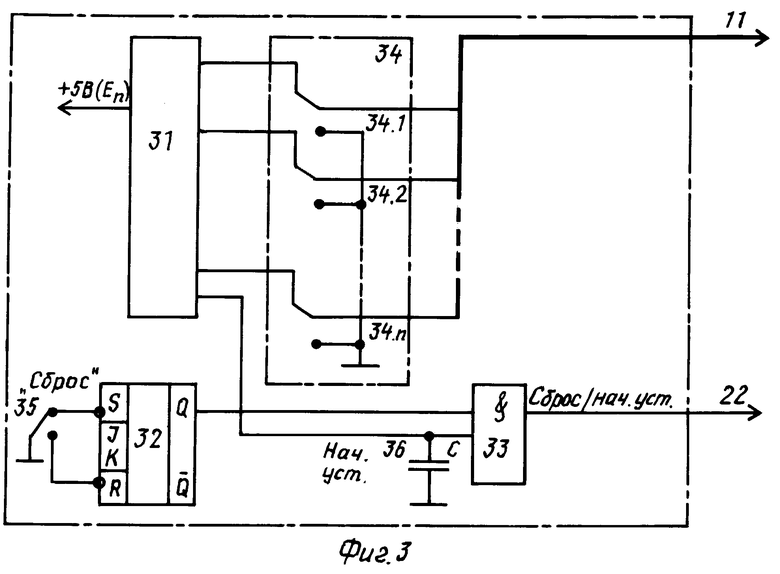

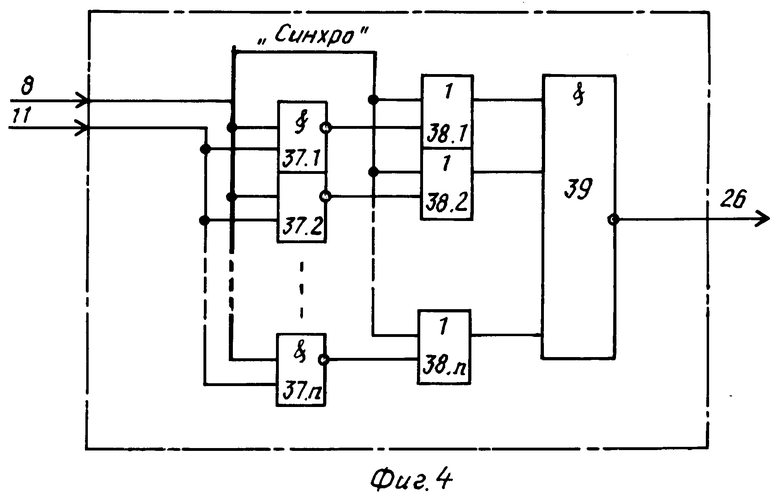

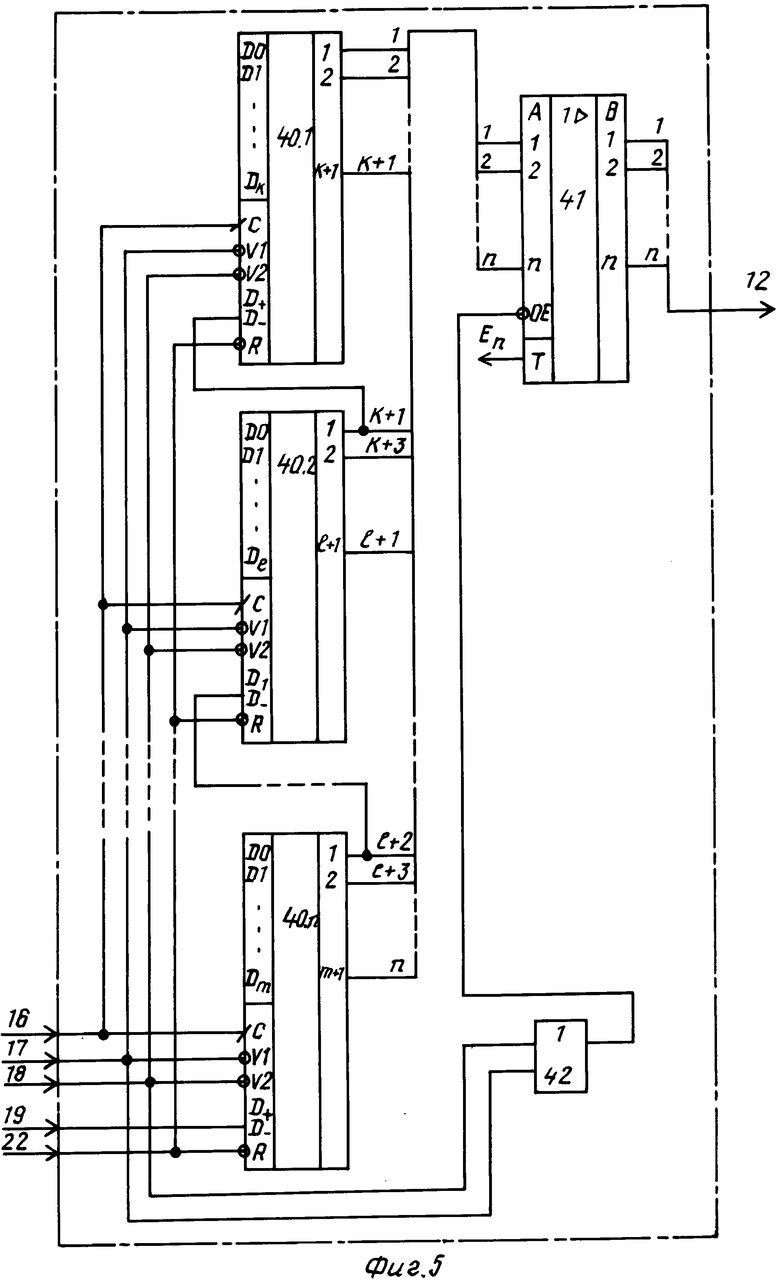

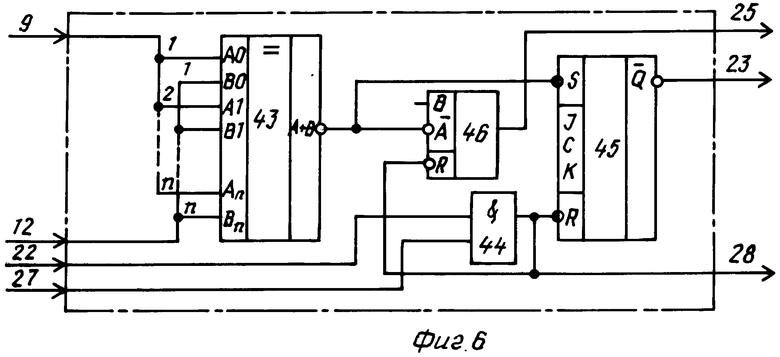

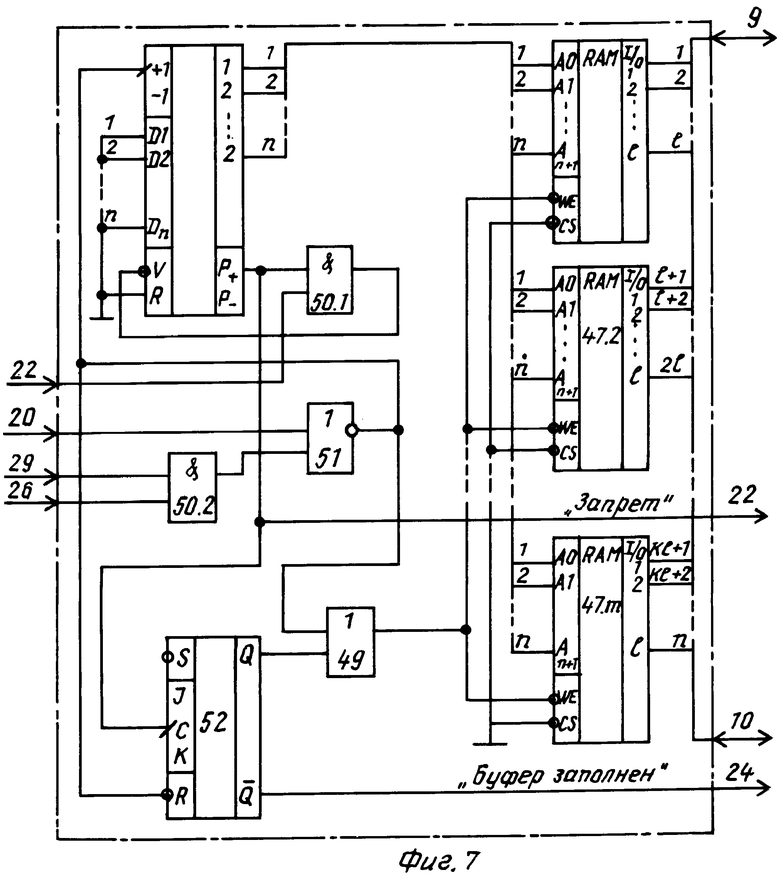

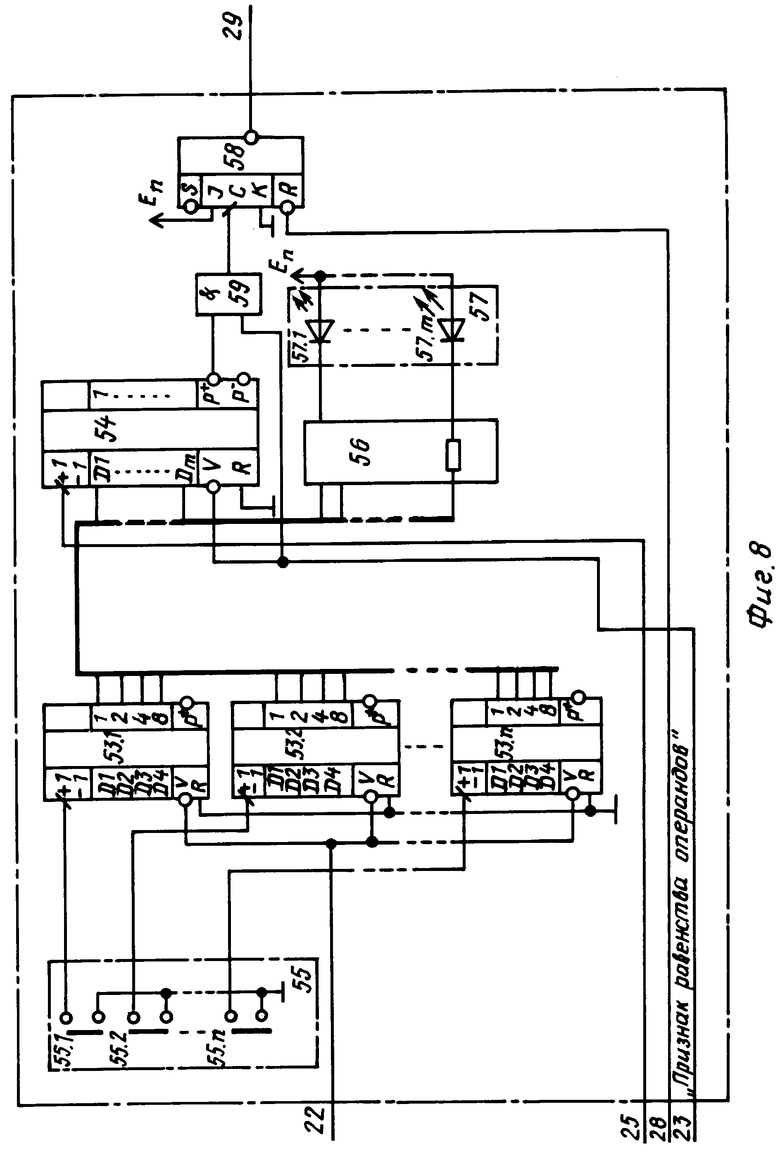

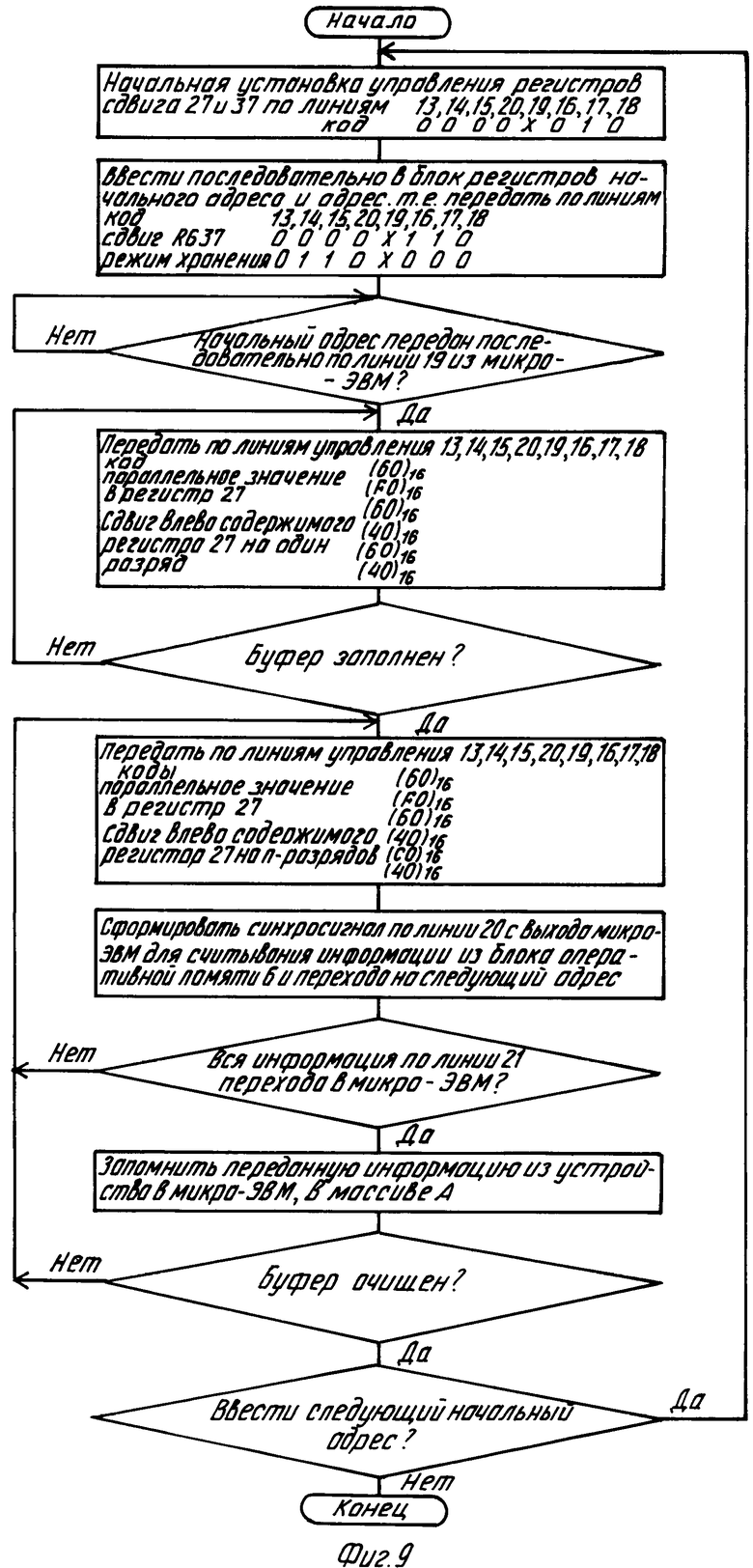

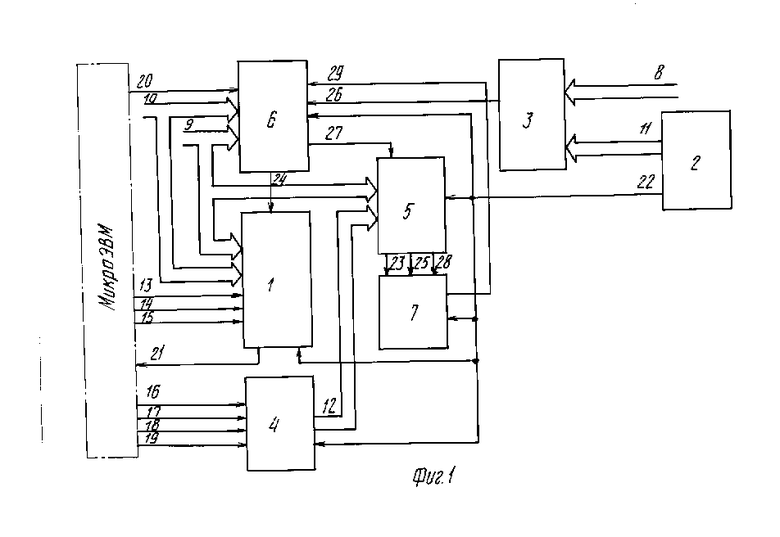

На фиг. 1 представлена структурная схема устройства для визуального контроля исполнения программ; на фиг. 2 - схема блока регистров текущего адреса и данных; на фиг. 3 - схема блока задания режимов; на фиг. 4 - схема блока мультиплексоров, на фиг. 5 - схема блока регистров начального адреса; на фиг. 6 - схема блока сравнения; на фиг. 7 - схема блока оперативной памяти; на фиг. 8 - схема блока выбора номера; на фиг. 9 - алгоритм совместной работы устройства с микроЭВМ и с контролируемым устройством.

Устройство для визуального контроля исполнения программ (фиг. 1) содержит блок 1 регистров текущего адреса и данных, блок 2 задания режимов, блок 3 мультиплексоров, блок 4 регистров начального адреса, блок 5 сравнения, блок 6 оперативной памяти, блок 7 выбора номера, группу входов 8 синхронизации и состояний, адресный вход 9, вход 10 данных, которые являются входами устройства для подключения к группе выходов синхронизации и состояний, к выходу адреса и данных контролируемого устройства (системный контроллер, ЦВМ, ЭВМ и т. д. ), группу выходов 11 блока 2, которая соединена с первой группой управляющих входов блока 3 мультиплексоров, группу информационных выходов 12 блока 4 регистров начального адреса, которая подключена к первой группе информационных входов блока 5 сравнения, первую и вторую группу входов-выходов блока 6 оперативной памяти, которая является входом адреса и данных устройства и выходом данных блока 6, причем первая группа выходов-входов подключена к первой группе информационных входов блока 1 регистров текущего адреса и данных и к второй группе информационных входов блока 5 сравнения, а вторая группа - к второй группе информационных входов блока 1 регистров текущего адреса и данных, группу входов управления режимов блока 1 регистров текущего адреса и данных, группу входов управления режимом блока 4 регистров начального адреса, первый тактовый вход блока 6 оперативной памяти, которые являются управляющими входами 13-20 устройства для подключения к соответствующим выходам управления микроЭВМ, информационный выход блока 1 регистров текущего адреса и данных, который является выходом 21 признака активности информации устройства для подключения к входу подтверждения наличия микроЭВМ, выход 22 начальной установки блока 2 задания режимов, который подключен к входам сброса блока 1 регистров текущего адреса и данных, блока 4 регистров начального адреса, к первому входу управления режимом блока 5 сравнения, блока 6 оперативной памяти и блока 7 выбора номера, второй вход управления режимом которого является первым выходом 23 равенства операндов блока 5 сравнения, причем первый выход 24 блока 6 оперативной памяти является выходом признака заполнения буфера для подключения к информационному входу блока 1 регистров текущего адреса и данных, второй выход блока 5 сравнения является выходом 25 для подключения к тактовому выходу блока 7 выбора номера, второй тактовый вход блока 6 оперативной памяти соединен с выходом 26 строба состояний блока 3 мультиплексоров, вход и вторая группа входов которого являются группой входов 8 синхронизации и состояний устройства для подключения к выходам синхронизации и состояний устройства, второй выход 27 блока 6 оперативной памяти является выходом признака заполнения буфера для подключения к второму входу управления режимом блока 5 сравнения, третий выход 28 которого является третьим входом управления режимом блока 7 выбора номера, выход 29 которого подключен к второму входу управления режимом блока 6 оперативной памяти.

Блок 1 регистров текущего адреса и данных (фиг. 2) содержит регистры 30 сдвига.

Блок 2 задания режимов (фиг. 3) содержит блок 31 регистров, RS-триггер 32, элемент И 33, переключатели 34, кнопочный переключатель 35, конденсатор 36.

Блок 3 мультиплексоров (фиг. 4) содержит элементы И 37, элементы ИЛИ 38, элемент И 39.

Блок 4 регистров начального адреса (фиг. 5) содержит регистры 40 сдвига, шинный формирователь 41, элемент ИЛИ 42.

Блок 5 сравнения (фиг. 6) содержит схему 43 сравнения, элемент И 44, RS-триггер 45, одновибратор 46.

Блок 6 оперативной памяти (фиг. 7) содержит элемент ОЗУ 47, счетчик 48, элемент ИЛИ 49, элементы И 50, элемент ИЛИ-НЕ 51, IK-триггер 52.

Блок 7 выбора номера (фиг. 8) содержит блок счетчиков 53 и 54 блок переключателей 55, блок резисторов 56, светодиоды 57, IK-триггер 58, элемент 2И 59.

Блок 1 регистров текущего адреса и данных предназначен для временного хранения в регистре 30 текущего адреса и данных, поступающих из блока 6 оперативной памяти через первую и вторую группы выходов-входов на первую и вторую группы информационных входов блока 1 для запоминания сигнала "Буфер заполнен" через выход 24 признака заполнения буфера блока 6 с оперативной памяти, через первую и вторую группы выходов-входов на первую группу информационных входов блока 1 для запоминания сигнала "Буфер заполнен" через выход 24 блока 6 на информационный вход блока 1, а также для формирования сигнала подтверждения в микроЭВМ, который поступает на вход 21 признака активности информации блока 1 с выхода регистра 30 в соответствии с алгоритмом (фиг. 9). Разрядность регистра 30 определяется разрядность адресных шин и шин данных контролируемого устройства, которые подключаются к адресному входу 9 и входу 10 данных устройства.

Блок 2 задания режимов предназначен для выбора состояний контролируемого устройства (выбор команды из ПЗУ, обращение к ПЗУ, ОЗУ, обращение к внешним устройствам) через переключатели 34, а также для формирования сигнала сброса, который поступает от кнопочного переключателя 35 через RS-триггер 32, и сигнала начальной установки от RC-цепочки блока 31 резисторов и конденсатора 36 и на выход 22 сброса (начальной установки по электропитанию), которые приводит в исходное состояние устройство.

Блок 3 мультиплексоров предназначен для формирования импульсов в моменты времени, определенные положением переключателей 34 блока 2 задания режимов.

Блок 4 регистров начального адреса предназначен для запоминания адреса, определяющего начало фрагмента программы, необходимого для просмотра программы оператором. Адрес заносится в регистр 40 и передается на выход в блок 5 сравнения через шинный формирователь 41 с помощью сигналов управления от микроЭВМ, которые поступают на входы 16, 17, 18, 19 управления режимом устройства в соответствии с алгоритмом (фиг. 9). Разрядность регистра 40 определяется разрядностью адресных шин контролируемого устройства, которые подключены к адресному входу 9 устройства.

Блок 5 сравнения предназначен для сравнения текущего адреса контролируемого устройства, который поступает на вторую группу информационных входов A схемы 43 сравнения через адресный вход устройства, и заданного адреса, который поступает на первую группу информационных входов B схемы 43 сравнения с информационного выхода 12 блока 4 регистров начального адреса. При сравнении адресов схема 43 сравнения выдает импульс на вход установки RS-триггера 45, сигнал с выхода которого передается на выход 23 равенства операндов блока 5 сравнения в блок 7 выбора номера, который разрешает проход тактовых сигналов с выхода 26 строба состояний блока 3 мультиплексоров в определенный момент.

Блок 6 оперативной памяти предназначен для запоминания фрагмента программы, которая запускается в контролируемом устройстве в реальном масштабе времени, т. е. текущей информации, поступаемой от контролируемого устройства через адресный вход 9 и вход 10 данных устройства на информационный вход-выход оперативной памяти 47.1 и 47. m в моменты, определяемые сигналами с выхода 26 строба состояний блока 3 мультиплексоров и с выхода 29 разрешения записи блока 7 выбора через элементы И 50.2 и ИЛИ-НЕ 51 а тактовый вход счетчика 48 для считывания занесенной текущей информации, поступаемой из блока 6 оперативной памяти через вход-выход оперативной памяти 47.1 и 47. m на первую и вторую группы информационных входов блока 1 регистров текущего адреса и данных в моменты, определяемые сигналом управления от микроЭВМ, в соответствии с алгоритмом (фиг. 9) через управляющий вход 20 устройства, а именно через элементы И 50.2, ИЛИ-НЕ 51 на тактовый вход счетчика 48 и через элеметы И 50.2, ИЛИ-НЕ 51 и ИЛИ 49 на вход разрешения записи-чтения оперативной памяти 47.1 и 47. m, а также для формирования сигнала "Буфер заполнен" с выхода переноса счетчика 48 через IK-триггер 52, поступаемый на первый выход признака заполнения буфера блока 6 оперативной памяти, и для формирования сигнала "Запрет", поступаемый с выхода переноса счетчика 48 через элемент И 50.1 на второй выход 27 блока 6 оперативной памяти. Разрядность оперативной памяти 47.1 и 47. m определяется разрядностью адресных шин и шин данных контролируемого устройства, которые подключаются к адресному входу 9 и входу 10 данных устройства.

Информационная емкость оперативной памяти 47.1 и 47. m определяется максимальным объемом памяти, необходимой для заполнения требуемого фрагмента программы.

Блок 1 регистров текущего адреса и данных представляет собой восьмиразрядные регистры сдвига типа К555ИР13.

Блок 4 регистров начального адреса представляет собой восьмиразрядные регистры сдвига типа К555ИР13 и восьмиразрядные шинные формирователи типа 580ВА86.

В качестве схемы 43 сравнения блока 5 сравнения могут быть использованы схемы сравнения типа 555СП1.

Оперативная память 47.1 и 47. m блока 6 оперативной памяти представляет собой ОЗУ статистического типа емкостью (например, 1К110) 132РУЗ, а в качестве счетчика 48 может быть использована микросхема типа 555ИЕ7 (четырехразрядный асинхронный счетчик).

В качестве схемы 46 может быть использован одновибратор 555АГЗ.

В блоке 7 выбора номера могут быть применены индикаторы 57 типа ЗЛСЗ41.

Устройство предназначено для визуального контроля исполнения программ контролируемого устройства, построенного на базе микропроцессоров К680ВМ80А, КР1821ВМ85А, КР180ВМ86, а также для контролируемых устройств, построенных на базе микропроцессорных комплектов 1802, 1804, 589 (см. Справочник. Цифровые и аналоговые интегральные микросхемы. / Под ред. С. В. Якубовского. : Радио и связь, 1990, разделы 3.2, 3.6, 3.7, 3.8).

Устройство работает следующим образом.

Для приведения устройства визуального контроля исполнения программ в исходное состояние на вход сброса блока 1 регистров текущего адреса и данных, блока 4 регистров начального адреса, блока 6 оперативной памяти, на первый вход сброса блока 5 сравнения и блока 6 оперативной памяти подается сигнал "Сброс + Начальная установка" с выхода 22 начальной установки блока 2 задания режимов, который формируется после включения электропитания устройства с выхода RC-цепочки 31, 36 или путем нажатия оператором кнопочного переключателя 35.

В результате регистры 30 и 40 сдвигы блоков 1 и 4 регистров текущего адреса и данных и регистров начального адреса устанавливаются в первоначальное состояние, на выходе IK-триггера 58 блока 7 выбора номера формируется сигнал запрета результирующей тактовой последовательности состояний, который поступает через выход 29 равенства операндов на первый вход элемента И 50.2 блока 6 оперативной памяти, на выходе IK-триггера 52 которого формируется сигнал разрешения записи, который по свертке ИЛИ 49 с сигналом с выхода элемента ИЛИ-НЕ 51 поступает на вход разрешения записи оперативной памяти 47, на инверсном выходе IK-триггера 52 блока формируется сигнал отсутствия "Заполнения буфера", который поступает на первый выход 24 признака заполнения буфера блока 6 оперативной памяти, на выходах счетчика 48 блока появляется начальный код адреса оперативной памяти 47, который формируется по сигналу начальной установки, поступающему на вход разрешения параллельной загрузки счетчика с выхода элемента И 50.1.

Устройство работает в двух режимах: в режиме записи фрагмента программы адреса, когда данные поступают в блок 6 оперативной памяти с выходов контролируемого устройства в реальном масштабе времени через адресный вход 9 и вход 10 данных устройства; в режиме считывания информации из блока 6 оперативной памяти в микроЭВМ с информационного выхода блока 1 регистров текущего адреса и данных через выход 21 подтверждения наличия сигнала устройства.

Первый и второй режимы выполняют совместно. Разделение этих режимов во времени решается аппаратурой устройства и сигналами управления, поступающими с выходов микроЭВМ на управляющие входы 13-20 устройства.

Управление блоками 1, 4, 6 регистров текущего адреса и данных, регистров начального адреса и оперативной памяти осуществляется от управляющих выходов микроЭВМ, которые подключены к управляющим входам 13-20 устройства в соответствии с алгоритмом, который представлен на фиг. 9.

Начальный адрес произвольного фрагмента программы подается последовательно на информационный вход для сдвига влево регистра 40 сдвига блока 4 регистров начального адреса через управляющий вход 19 устройства в сопровождении управляющих сигналов, поступающих на тактовый вход, первый и второй входы выбора режима регистра 40 через управляющие входы 16, 17, 18 устройства в соответствии с фиг. 9а. Начальный адрес запоминается в регистре 40 сдвига и передается при его переходе в режим хранения на выходе шинного формирователя 41 за счет формирования сигнала с выхода элемента ИЛИ 42, на первый и второй входы которого поступают сигналы разрешения с управляющих входов 17, 18 устройства. Начальный адрес с выхода 12 блока 4 регистров начального адреса поступает на первую группу информационных входов блока 5 сравнения, на вторую группу информационных входов которого передается текущий адрес с адресных выходов контролируемого устройства через адресный вход 9 устройства. При сравнении кодов адреса, присутствующих на первом и втором информационных входах схемы 43 сравнения, на ее выходе формируется сигнал, который поступает на вход установки RS-триггера 45 и инверсный вход одновибратора 46, вырабатывающего импульс по адресу определенной длительности. С выхода RS-триггера 45 через выход 23 равенства операндов и с выхода одновибратора 46 через выход 25 сигналы поступают соответственно на вход загрузки и тактовый вход счетчика 54 и переводят его в состояние подсчета n-многократно повторяющегося адреса, число повторений которого заранее выбрано оператором кнопочными переключателями 55, загружено в обратном коде в счетчик 54 через счетчик 53 и высвечено на индикаторах 57 через резисторную сборку 56. При подсчете n-адреса на выходе переноса счетчика 54 формируется признак переноса, который через элемент И 50.2 поступает на тактовый вход IK-триггера 58. С выхода последнего формируется признак разрешения записи, который через выход 29 блока 7 поступает на первый вход элемента И 50.2 и разрешает проход сигналов результирующей тактовой последовательности состояний. Эта последовательность поступает с выхода 26 блока 3 мультиплексоров, на вторую группу входов состояний и строба которого подаются сигналы с выхода состояний и с выхода синхронизации контролируемого устройства через группу входов 8 устройства.

Состояние процессора контролируемого устройства меняется с каждым его внутренним тактом. Следовательно, на второй группе входов состояний блока 3 мультиплексоров формируется последовательность импульсов, соответствующая определенным моментам работы контролируемого устройства (обращение за первым байтом, т. е. за командой из ПЗУ, обращение к оперативной памяти, обращение к оперативной памяти, обращение к внешним устройствам и т. д. ). Все сформированные последовательности состояний поступают на входы элементов 37.1 . . . 37. n блока 3 мультиплексора, однако на их выходы проходят лишь те, которые выбраны оператором при помощи переключателей 34.1 . . . 34n блока 2 задания режимов. После свертки по ИЛИ 38.1 . . . 38n с синхросигналом, поступающим на вход элементов ИЛИ 38.1 . . . 38n от контролируемого устройства, а затем после их свертки по И 39 результирующая тактовая последовательность поступает на выход 26 блока 3 мультиплексоров.

Адреса и данные текущего фрагмента программы поступают с выходов контролируемого устройства через адресный вход 9 и вход 10 данных устройств на первую и вторую группы входов-выходов блока 6 оперативной памяти.

Адреса и данные записываются в оперативную память 47.1 и 47. m результирующей тактовой последовательностью сигналов состояний с выхода 26 строба состояний, которая поступает на второй вход элемента И 50.2. Выход элемента И 50.2 подключен к первому входу элемента ИЛИ-НЕ 51, с выхода которого сигнал поступает через элемент ИЛИ 49 на вход разрешения записи в оперативную память 47 и одновременно этот сигнал поступает на тактовый вход счетчика 48, по положительному перепаду которого выбирается следующий адрес оперативной памяти 47 блока 6 оперативной памяти. После заполнения буфера оперативной памяти 47 информацией текущего фрагмента программы сигнал с выхода переноса счетчика 48 через элемент И 50.1 поступает на тактовый вход IK-триггера 52, с прямого выхода которого через элемент ИЛИ 49 формируется сигнал разрешения считывания с оперативной памяти 47 и с инверсного выхода которого формируется сигнал "Буфер заполнен". Последний поступает через выход 24 признака заполнения буфера блока 6 оперативной памяти на информационный вход блока 1 регистров текущего адреса и данных, с выхода 21 признака активности информации которого сигнал передается на вход подтверждения микроЭВМ в соответствии с алгоритмом на фиг. 9б.

По формировании сигнала "Буфер заполнен" осуществляется переход устройства в режим считывания информации в микроЭВМ.

По выходам управления микроЭВМ через входы 13, 14, 15 управления устройства передаются управляющие сигналы на тактовый вход выбора режима регистра 30 сдвига блока 1 регистров текущего адреса и данных и через вход на второй вход элемента ИЛИ 49, с выхода которого сигнал поступает на тактовый вход счетчика 48. Информация считывается с первой и второй групп выходов-входов блока 6 оперативной памяти в блок 1 регистров текущего адреса и данных, запоминается в регистре 30 сдвига и передается последовательно с его информационного выхода 21 на вход подтверждения микроЭВМ, где запоминается в определенном массиве A в соответствии с алгоритмом на фиг. 9в. С выхода управления микроЭВМ через управляющий вход 20 устройства на тактовый вход блока 6 оперативной памяти поступает сигнал, по положительному переносу которого с выхода счетчика 48 выбирается следующий адрес оперативной памяти 47, с первой и второй групп выходов-входов блока 6 оперативной памяти информация считывается как описано выше в соответствии с алгоритмом на фиг. 9в.

Информация, занесенная в массив A микроЭВМ, может быть рассмотрена с любого адреса фрагмента текущей программы как в прямом, так и в обратном направлении отсчета адреса начала и конца. Следовательно, нет необходимости в блоке регистров коничного адреса устройства для визуального контроля исполнения программы.

Технико-экономические преимущества заявляемого технического решения - расширение функциональных возможностей предложенного устройства за счет обеспечения сохранения произвольного фрагмента исследуемой программы, возможности многократного просмотра хода программы и контроля произвольной информации (в том числе адреса, данных) определяется совокупностью используемых в устройстве технических средств и новой организацией связей.

Заявляемое техническое решение обеспечивает сокращение затрат реального времени при контроле исполнения программ контролируемого устройства, в частности для НМЛЕС5740 со встроенным системным контроллером. Эффективность заявляемого технического решения вытекает из расчетных данных, подтверждающих сокращение затрат реального времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОТЛАДКИ МИКРОЭВМ | 1990 |

|

RU2015540C1 |

| УСТРОЙСТВО ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ КАНАЛА ВОСПРОИЗВЕДЕНИЯ АППАРАТУРЫ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ | 1991 |

|

RU2024968C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ КОМАНД УПРАВЛЕНИЯ ДВУХПОЗИЦИОННЫМИ ОБЪЕКТАМИ | 2002 |

|

RU2244344C2 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| ФОРМИРОВАТЕЛЬ КОМАНД УПРАВЛЕНИЯ | 2003 |

|

RU2244960C2 |

| Устройство для ввода информации | 1990 |

|

SU1702382A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для ввода информации | 1990 |

|

SU1698890A1 |

Устройство относится к вычислительной технике и может быть использовано для контроля исполнения программ микроЭВМ, контроллеров, персональных ЭВМ и ЭВМ. Цель изобретения состоит в расширении функциональных возможностей: повышения информативности, точности контроля, сокращения временных затрат на контроль. Для этого устройство содержит блок 1 регистров текущего адреса и данных, блок 2 задания режимов, блок 3 мультиплексоров, блок 4 регистров начального адреса, блок 5 сравнения, блок 6 оперативной памяти, блок 7 выбора номера и имеет группу входов состояний и синхронизации, адресный вход и вход данных, которые являются входами устройства для подключения соответственно к выходу синхронизации состояний, к выходу адреса и данных контролируемого устройства, первый тактовый вход блока оперативной памяти, группу входов управления режимом блока регистров текущего адреса и данных, группу входов управления режимом блока регистров начального адреса, которые являются управляющими входами устройства для подключения к соответствующим выходам управления режимом микроЭВМ. 9 ил.

УСТРОЙСТВО ДЛЯ ВИЗУАЛЬНОГО КОНТРОЛЯ ИСПОЛНЕНИЯ ПРОГРАММ, содержащее блок управления, блок регистров текущего адреса и данных, блок задания режимов, блок мультиплесоров, блок регистров начального адреса, блок сравнения, причем группа выходов блока задания режимов соединена с группой управляющих входов блока мультипликаторов, группа информационных выходов блока регистров начального адреса подключена к первой группе информационных входов блока сравнения, отличающееся тем, что, в устройство введены блок оперативной памяти, блок выбора номера адреса, причем первая и вторая группы входов-выходов блока оперативной памяти соединены с входами соответственно адреса и данных устройства для подключения к выходам адреса и данных контролируемого устройства, причем первая группа входов-выходов блока оперативной памяти подключена к первой группе информационных входов блока регистров текущего адреса и данных и к второй группе информационных входов блока сравнения, вторая группа входов-выходов блока оперативной памяти соединена с второй группой информационных входов блока регистров текущего адреса и данных, группа входов управления режимом которого, группа входов управления режимом блока регистров начального адреса, первый тактовый вход блока оперативной памяти подключены к соответствующим выходам блока управления, информационный вход блока регистров текущего адреса и данных соединен с входом признака, активности информации блока управления, выход начальной установки блока задания режимов подключен к входам сброса блока регистров текущего адреса и данных и блока регистров начального адреса, к первым входам управления режимом блока сравнения, блока оперативной памяти и блока выбора номера адреса, второй вход управления режимом которого соединен с первым выходом блока сравнения, выход признака заполнения буфера блока оперативной памяти подключен к информационному входу блока регистров текущего адреса и данных, второй выход блока сравнения подключен к тактовому входу блока выбора номера адреса, второй тактовый вход блока оперативной памяти соединен с выходом блока мультиплексоров, вторая группа входов которого является группой входов синхронизации состояний устройства для подключения к выходам синхронизации и состояний контролируемого устройства, выход признака запрета блока оперативной памяти подключен к второму входу управления режимом блока сравнения, третий выход которого соединен с третьим входом управления режимом блока выбора номера адреса, выход которого подключен к второму входу управления режимом блока оперативной памяти, причем блок выбора номера адреса содержит первый и второй счетчики, узел переключателей, узел индикаторов, JK-триггер, элемент И, первый вход которого и вход загрузки второго счетчика являются вторым входом управления режимом блока выбора номера адреса, второй вход элемента И соединен с выходом переноса второго счетчика, тактовый вход которого подключен к тактовому входу блока выбора номера адреса, информационные входы второго счетчика соединены с выходами первого счетчика и входами узла индикаторов, тактовые входы первого счетчика соединены с выходами узла переключателей, входы загрузки первого счетчика соединены с первым входом управления режимом блока выбора номера адреса, входы сброса первого и второго счетчика и K-вход JK-триггера соединены с шиной нулевого потенциала устройства, причем J-вход JK-триггера подключен к шине единичного потенциала устройства, вход сброса JK-триггера соединен с третьим входом управления режимом блока выбора номера адреса тактовый вход JK-триггера соединен с выходом элемента И, инверсный выход JK-триггера является выходом блока выбора номера адреса.

Авторы

Даты

1994-04-30—Публикация

1991-11-14—Подача