Изобретение относится к технике магнитной записи и может быть использовано контрольно-измерительной аппаратурой, а также во встроенных средствах диагностического контроля аппаратуры цифровой магнитной записи (АЦМЗ).

Устройство предназначено для качественной оценки работоспособности канала АЦМЗ.

Известно устройство для измерения колебаний скорости перемещения носителя магнитной записи, содержащее воспроизводящую магнитную головку, усилитель воспроизведения, формирователь, анализатор спектра, регистратор, компаратор, одновибратор и включенные последовательно элемент несовпадения, двухканальный преобразователь длительности импульса в напряжение и элемент объединения [1].

Однако устройство обладает недостаточно высокой точностью измерения электрическая схема его сложна и энергоемка, к тому же имеет узкие функциональные возможности (нет контроля воспроизводимых сигналов АЦМЗ).

Известно также устройство для контроля синхронизма воспроизведенных сигналов, содержащее шину псевдослучайного сигнала, первый сумматор, детектор псевдослучайной последовательности, детектор отсутствия ошибок, коммутатор, второй сумматор, первый регистр сдвига, триггер, выходную шину, шину тактового сигнала, дополнительный регистр сдвига, формирователь кода, регистр памяти, формирователи сбоя тактовых импульсов, каждый из которых состоит из последовательно соединенных сумматора, счетчика тактов и триггера, устройство содержит также выходные шины сигналов величины рассогласования и элементы ИЛИ [2].

Основным недостатком устройства являются узкие функциональные возможности (измеряет только величину рассогласования сигналов, осуществляет контроль синхронизма, но не "выявляет" источник возмущений рассогласованных сигналов), т.е. не позволяет качественно оценить работоспособность АЦМЗ

.

Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому устройству является устройство для измерения величины рассогласования сигналов воспроизведения с магнитной ленты, содержащее последовательно соединенные блок магнитных головок и усилитель воспроизведения, последовательно соединенные пеpвый счетчик и блок документирования, второй счетчик, вход которого соединен с входом первого счетчика, кроме того, устройство содержит последовательно соединенные кодер, коммутатор, блок формирования нормированного импульса, схему выделения измеряемого импульса, схему формирования импульса сброса и блок считывания, блок измерения временных интервалов, выходы которого подключены к вторым входам коммутатора и блока считывания, выход которого подключен к входу первого счетчика, а третий вход подключен к второму выходу схемы выделения измеряемого импульса, третий выход которой подсоединен к входу блока измерения временных интервалов, причем второй выход кодера подключен к входу блока магнитных головок, третий вход коммутатора подсоединен к выходу усилителя воспроизведения, а второй вход схемы выделения измеряемого импульса соединен с выходом коммутатора [3].

Недостатком этого устройства являются узкие функциональные возможности (недостаточная точность и информативность контроля, не позволяющее качественно оценить - проанализировать работоспособность контролируемого устройства) измеряет только величину рассогласования и только один тип контролируемых сигналов АЦМЗ подвержен контролю.

Целью предлагаемого изобретения является повышение точности и информативности контроля по независимым каналам относительно служебного управляющего сигнала.

Поставленная цель достигается тем, что в устройство для измерения величины рассогласования сигналов с магнитной ленты, содержащее блок коммутатора, первый блок формирователя, первый блок измерения временных интервалов, блок считывания, блок формирования импульса сброса, выход которого подключен ко входу сброса блока считывания, причем первый вход выбора режима блока коммутатора является входом управления устройства, первый информационный вход - информационным входом устройства, а первый выход - информационным входом устройства первого блока - формирователя, первый блок регистрации, введены второй блок формирователей, второй блок измерения временных интервалов, второй блок регистрации, блок выбора номера, блок синхронизации, блок выбора номера, блок синхронизации, блок системного управления и обработки микроЭВМ, причем второй и третий вход выбора режима блока коммутатора, первый вход выбора режима блока выбора номера, вход сброса блока формирования импульса сброса, вход выбора режима первого и второго блока формирователя, тактовый вход блока регистрации первого и второго кана лов, тактовый вход блока считывания являются группой входов управления устройства для подключения к соответствующим выходам управления микро-ЭВМ, а информационный выход блока считывания является выходом признака активности устройства для подключения ко входу подтверждения активности микро-ЭВМ, первый, второй и третий информационный вход блока коммутатора являются соответственно служебными и информационными входами устройства для подключения к контрольным и контролируемым входам контролируемого устройства, причем группа входов признака номера блока коммутатора подключена к группе выходов блока выбора номера, первый вход сброса которого соединен со входом блока считывания, с первым входом сброса блока коммутатора, со входом сброса первого и второго блока формирователей, первого и второго блока регистрации, а второй вход выбора режима блока выбора номера подключен к третьему выходу выбора режима блока коммутатора, к первому входу выбора режима блока синхронизации, первый тактовый вход блока выбора номера подключен к первому выходу блока синхронизации и к тактовому входу первого и второго формирователя, третий вход выбора режима блока выбора номера соединен со вторым выходом блока коммутатора и со входом выбора режима блока синхронизации, второй и третий выход которого подключен к тактовому входу первого и второго блока измерения временных интервалов соответственно, а четвертый и пятый выход являются группой контрольных выходов устройства, причем третий выход блока коммутатора является вторым тактовым входом блока выбора номера, второй вход признака сброса которого подключен к четвертому выходу блока коммутатора, пятый выход которого является информационным входом второго блока формирователя, а шестой и седьмой выходы которого подключены ко входу соответственно первого и второго блока формирователей, первый выход которого соединен со входом признака загрузки соответственно первого и второго блока измерения временных интервалов, группа выходов которых является информационной группой входов соответственно первого и второго блока регистрации, выход признака заполнения буфера которых подключен ко входу признака соответственно первого и второго блока формирователя и к группе входов признака заполнения буфера первого и второго каналов блока считывания, выход признака заполнения буфера двух каналов которого является вторым входом сброса блока коммутатора, первая и вторая группа информационных входов блока считывания подключена к группам выходов блока регистрации, вход признака записи которых соединен со вторым входом соответственно первого и второго блока формирователей, вход признака переноса которых является выходом соответственно первого и второго блока измерения временных интервалов, вход управления которых является третьим выходом первого и второго формирователей. Блок коммутатора содержит первый-пятый элемент НЕ, первый-четвертый элемент 2-2И-ИЛИ-НЕ, первый и второй одновибратор, первый-восьмой элемент 2 И, элемент 2 И-НЕ, первый-третий элемент 2 ИЛИ-НЕ, первый-четвертый элемент 2ИЛИ. Первый и второй блок формирователя содержит первый-третий одновибратор, D-триггер, элемент 2 ИЛИ, элемент 4И, элемент 2И-НЕ, элемент НЕ, резистор и конденсатор (элемент задержки). Первый и второй блок измерения временных интервалов содержит счетчик и шинный формирователь. Блок регистрации содержит IK-триггер, счетчик, элемент ОЗУ, первый и второй элемент 2 И, 2 ИЛИ и элемент НЕ. Блок считывания содержит мультиплексор, первый и второй счетчик, дешифратор, элемент ИЛИ и НЕ. Блок выбора номера содержит первый и второй счетчик, первый и второй IK-триггер, первый и второй элемент 2 И, элемент 2И-НЕ и НЕ, блок резисторов, индикаторы, переключатели. Блок синхронизации содержит счетчик, элемент 2 2И-ИЛИ-НЕ, элемент 2И, генератор тактовых импульсов. Блок формирования импульса сброса содержит элемент 2И-НЕ, резистор и конденсатор. Вход первого элемента НЕ и первый вход третьего элемента 2И блок коммутатора, вход второго элемента НЕ и третий вход первого элемента 2-2И-ИЛИ-НЕ, вход третьего элемента НЕ и третий вход второго элемента 2-2И-ИЛИ-НЕ которых являются первым третьим входом выбора режима блока коммутатора, вход четвертого элемента НЕ и четвертый вход первого элемента 2-2И-ИЛИ-НЕ, первый вход которого, первый вход первого элемента 2И являются соответственно первым-третьим входом управления блока коммутатора, первый вход второго элемента 2ИЛИ-НЕ, второй вход первого элемента 2И, первый вход третьего элемента 2ИЛИ-НЕ являются соответственно первым-третьим информационным входом блока коммутатора, а первый вход четвертого элемента 2И является первым входом сброса блока коммутатора для подключения к выходу элемента 2И-НЕ блока формирования импульса сброса, ко входу сброса первого IK-триггера, ко входу загрузки первого и n-входа первого счетчика блока выбора номера, к первому входу первого элемента 2И, ко входу сброса первого одновибратора и к первому входу элемента 4И первого и второго блока формирователя, ко входу сброса IK-триггера первого входа второго элемента 2И входа сброса первого и второго блока регистрации, ко входу второго элемента НЕ блока считывания, вход сброса первого и второго одновибратора блока коммутатора является вторым входом сброса блока коммутатора для подключения к выходу первого элемента НЕ блока считывания, первый вход второго элемента 2И и второй вход третьего элемента 2И, первый вход шестого элемента 2И, первый вход первого элемента 2ИЛИ-НЕ и четвертого элемента 2ИЛИ являются группой входов признака номера блока коммутатора для подключения соответственно к выходу второго IK-триггера, который соединен с первым входом элемента 2И-НЕ, к выходу второго элемента 2И и к инверсному выходу второго IK-триггера, который соединен со входом на уменьшение второго счетчика блока выбора номера, причем, выход первого элемента НЕ блока коммутатора подключен ко второму входу второго элемента 2И, шестого элемента 2И, к первому входу пятого элемента 2И и является вторым выходом блока для подключения к первому входу второго элемента 2И блока выбора номера и к первому входу элемента 2-2И-ИЛИ-НЕ блока синхронизации, причем выход второго элемента НЕ блока коммутации является вторым входом первого элемента 2-2И-ИЛИ-НЕ, а выход третьего элемента НЕ блока коммутации является вторым входом первого элемента 2 2И-ИЛИ-НЕ, а выход третьего элемента НЕ подключен к первому входу второго элемента 2-2И-ИЛИ-НЕ, выходы которых соединены с первым и вторым инверсным входом первого и второго одновибраторов, второй инверсный и первый вход которых подключен к шине нулевого и единичного потенциала, и соответственно ко входу пятого элемента НЕ, выход которого является третьим выходом блока для подключения к тактовому входу на увеличение второго счетчика блока выбора номера, причем выход четвертого элемента НЕ блока коммутатора является вторым входом элементов 2ИЛИ-НЕ, 2 ИЛИ, выходы которых соединены со вторым входом второго и третьего элемента 2ИЛИ-НЕ и первым входом седьмого и восьмого элемента 2И и соответственно со вторым входом пятого элемента 2И, выход которого является первым входом первого элемента ИЛИ, выход которого является шестым выходом блока коммутатора, а выход четвертого элемента 2ИЛИ является седьмым выходом блока коммутатора для подключения ко второму входу элемента 4И соответственно первого и второго блока формирователей, причем выходы первого и второго одновибраторов блока коммутатора соединены со вторым входом второго элемента 2-2И-ИЛИ-НЕ и соответственно с первым входом элемента 2И-НЕ, второй вход которого является выходом второго элемента 2И, а выход которого является вторым входом четвертого элемента 2И, выход которого является четвертым выходом блока коммутатора для подключения ко входу сброса второго IK-триггера блока выбора режима, причем выход первого элемента 2И блока коммутатора подключен к четвертому входу второго элемента 2-2И-ИЛИ-НЕ, ко второму входу седьмого и восьмого элемента 2И и к первому входу третьего элемента 2-2И-ИЛИ-НЕ, второй вход которого соединен с выходом третьего элемента 2И и подключен ко второму входу первого элемента 2 ИЛИ и ко второму входу четвертого элемента 2-2И-ИЛИ-НЕ, третий вход третьего элемента 2-2И-ИЛИ-НЕ соединен с выходом шестого элемента 2И и с третьим входом четвертого элемента 2-2И-ИЛИ-НЕ, первый и четвертый вход которого и четвертый вход третьего элемента 2-2И-ИЛИ-НЕ являются соответственно выходами третьего и второго элемента 2ИЛИ, первые выходы которых соединены соответственно с выходами третьего и второго элементов 2ИЛИ-НЕ, а вторые входы которых подключены соответственно к выходам восьмого и седьмого элемента 2И, причем выходы третьего и четвертого элемента 2-2И-ИЛИ-НЕ, являются первым и пятым выходом блока коммутатора для подключения ко второму инверсному и первому входу первого и второго одновибраторов соответственно первого и второго блока формирователей, причем первый и второй инверсный входы первого и второго одновибраторов соединены с шиной единичного и нулевого потенциала, а выходы подключены к первому и второму входу элемента 2ИЛИ, выход которого является первым входом элемента 2И-НЕ и входом данных D-триггера, тактовый вход которого является тактовым входом первого и второго блока формирователей для подключения к первому выходу счетчика блока синхронизации и который соединен со вторым входом элемента 2И-НЕ блока выбора номера, причем третий выход данных D-триггера первого и второго блока формирователей подключен к первому входу третьего одновибратора, второй инверсный вход которого подключен к нулевому потенциалу, а третий инверсный выход данных D-триггера является вторым входом элемента 2И-НЕ, выход которого подключен ко входу элемента НЕ и является третьим выходом первого и второго блока формирователей для подключения ко вход у признака управления шинного формирователя соответственно первого и второго блока измерения временных интервалов, причем выход третьего одновибратора первого и второго блока формирователей подключен к первому контакту резистора и конденсатора и к тактовому входу IK-триггера, а инверсный выход третьего одновибратора подключен к третьему входу элемента 4И, выход которого соединен с первым входом второго элемента 2И, выход которого является входом сброса IK-триггера, первый и второй информационный вход которого и второй контакт резистора и конденсатора подключены соответственно к единичному и нулевому потенциалу, а выход IK-триггера является первым выходом первого и второго блока формирователей для подключения ко входу признака загрузки счетчика первого и второго блока измерения временных интервалов, причем, выход элемента НЕ первого и второго блока формирователей является вторым входом блока для подключения к первому входу признака записи первого элемента 2И и первого и второго блока регистрации, второй вход элемента 2И подключен к инверсному выходу IK-триггера, который является выходом первого и второго блока регистрации для подключения к четвертому входу элемента 4И соответственно первого и второго блока формирователей и к первому и второму входу элемента 2ИЛИ-НЕ, причем первый вход элемента ИЛИ первого и второго блока регистрации является тактовым входом блока, второй вход элемента НЕ соединен с выходом первого элемента 2И-НЕ, а выход - со входом элемента НЕ, выход которого подключен к тактовому входу счетчика и к первому входу второго элемента 2ИЛИ, выход которого является входом признака - записи - чтения элемента ОЗУ, а второй вход которого соединен с выходом IK-триггера, К-вход которого подключен к единичному потенциалу, тактовый вход которого является выходом признака переноса счетчика и соединен со вторым входом второго элемента 2И, выход которого подключен ко входу загрузки по входу данных кодовой комбинации счетчика, группа выходов которого является группой адресных входов элемента ОЗУ, группа выходов которого представляет собой группу выходов и группу информационных входов соответственно первого и второго блока регистрации для подключения ко входам мультиплексора блока считывания и соответственно к выходу шинного формирователя первого и второго блока измерения временных интервалов, группа входов которого соединена с группой выходов счетчика, группа входов данных которого подключена к нулевому потенциалу, причем выход элемента 2ИЛИ-НЕ блока считывания подключен ко входу элемента НЕ и к первому входу мультиплексора, группа выходов которого является информационным выходом блока считывания, а первая и вторая группа признака управления которого является группой выходов соответственно первого счетчика и дешифратора, первый инверсный и второй вход управления которого соединен с третьим выходом второго счетчика, а второй инверсный и первый вход которого подключены к шине нулевого потенциала, причем первый и второй выходы счетчика подключены к первому и второму информационным входам дешифратора, тактовый вход которого соединен со вторым выходом первого счетчика, тактовый вход которого является информационным выходом блока считывания, вход данных которого представляет собой определенную кодовую комбинацию, а вход сброса второго счетчика является выходом второго элемента НЕ, причем выход генератора блока синхронизации соединен с тактовым входом счетчика, с первым контактом переключателя, со вторым входом элемента 2-2И-ИЛИ-НЕ и является вторым выходом блока, а выход второго элемента 2-2И-ИЛИ-НЕ является третьим выходом блока для подключения к тактовому входу счетчика соответственно второго и первого блока измерения временных интервалов, третий вход элемента 2-2И-ИЛИ-НЕ подключен к первому входу выбора режима блока коммутатора, а четвертый вход соединен с выходом элемента 2И, первый вход которого соединен со вторым контактом переключателя, второй вход которого соединен с третьим контактом переключателя, четвертый контакт которого соединен с первым выходом счетчика, второй и третий выходы которого являются группой контрольных точек блока синхронизации, причем вторые контакты кнопочных переключателей блока выбора номера подключены к нулевому потенциалу, а вторые - соответственно к тактовым входам на уменьшение первого счетчика, группы выходов которого являются группами первых контактов блока резисторов и группами входов данных второго счетчика, вход признака загрузки которого соединен с первым входом первого элемента 2И и с выходом элемента НЕ, вход которого является первым входом выбора режима блока выбора номера, выход признака переноса второго счетчика которого является вторым входом элемента 2И, выход которого соединен с тактовым входом второго IK-триггера, а тактовый вход первого IK-триггера соединен с выходом элемента 2И-НЕ, причем входы К первого и второго IK-триггеров подключены к нулевому потенциалу, а выход первого соединен со вторым входом второго элемента 2И, причем группа вторых контактов блока резисторов подключена к группе первых контактов индикаторов, группа вторых контактов соединена с единичным потенциалом, причем первый вход элемента 2И-НЕ блока формирования импульсов сброса является входом сброса блока, а второй вход соединен с первым контактом резистора и конденсатора, вторые контакты которых подключены соответственно к единичному и нулевому потенциалу.

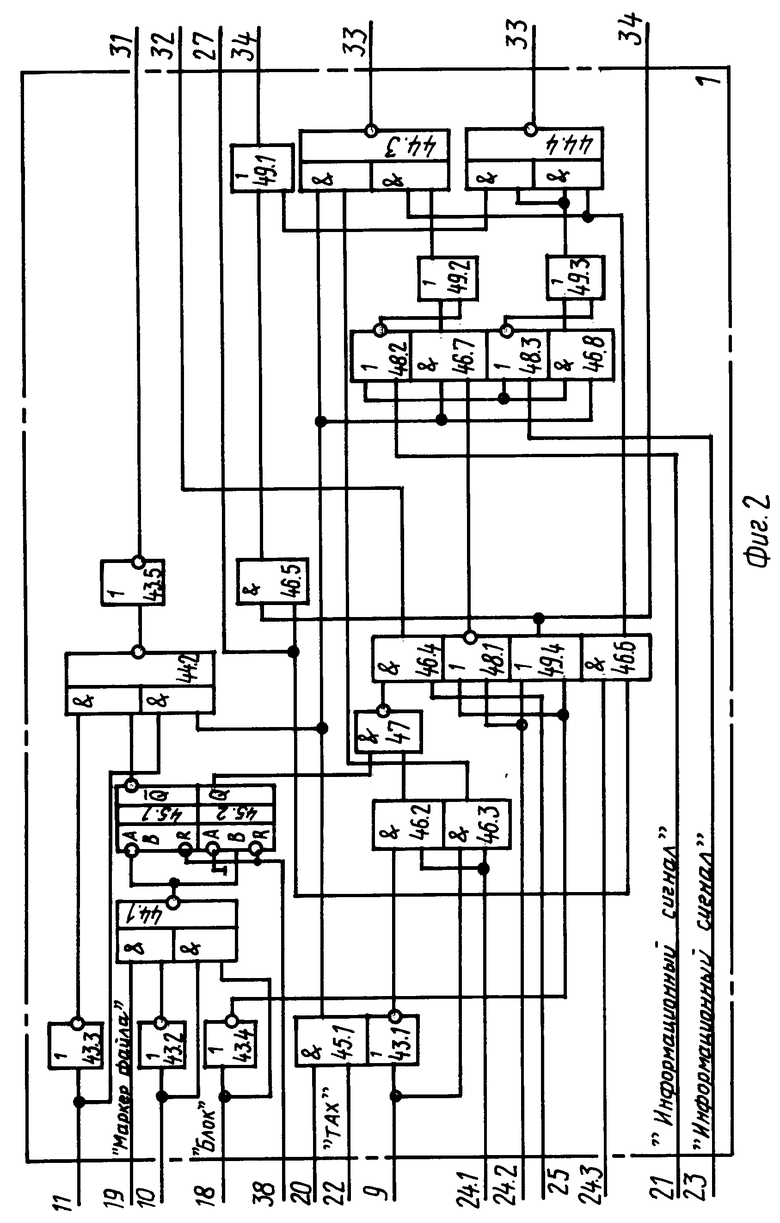

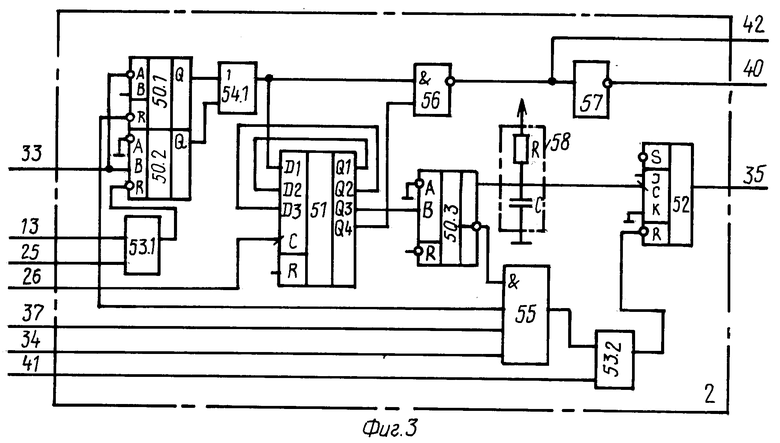

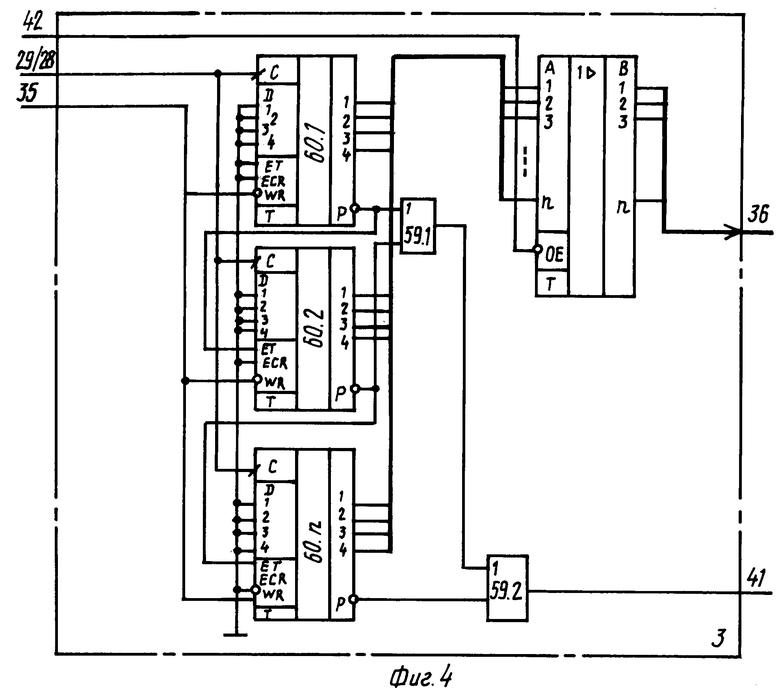

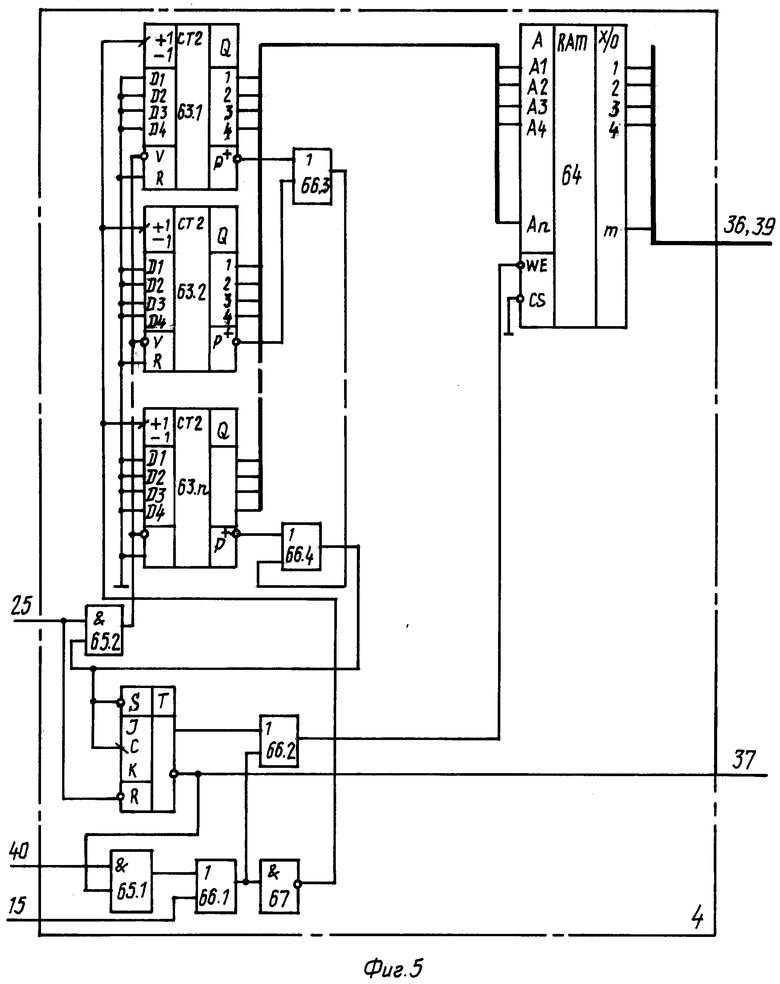

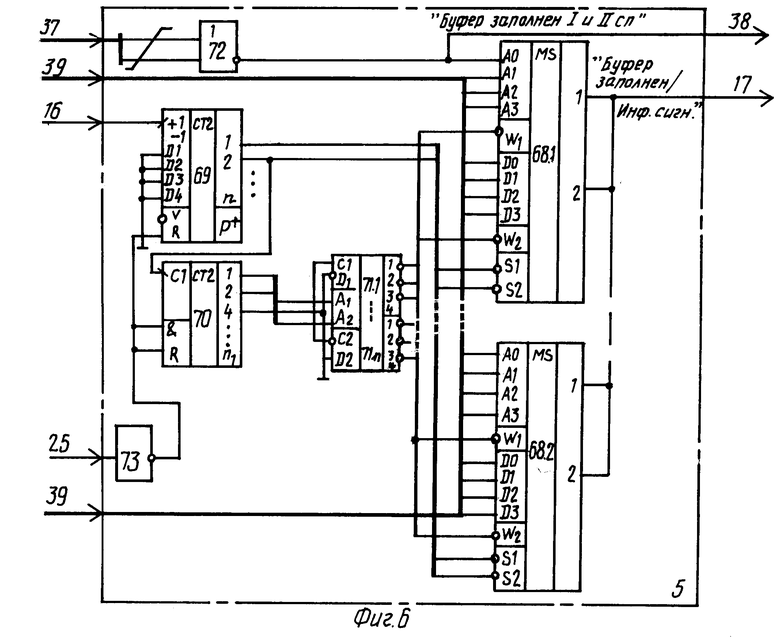

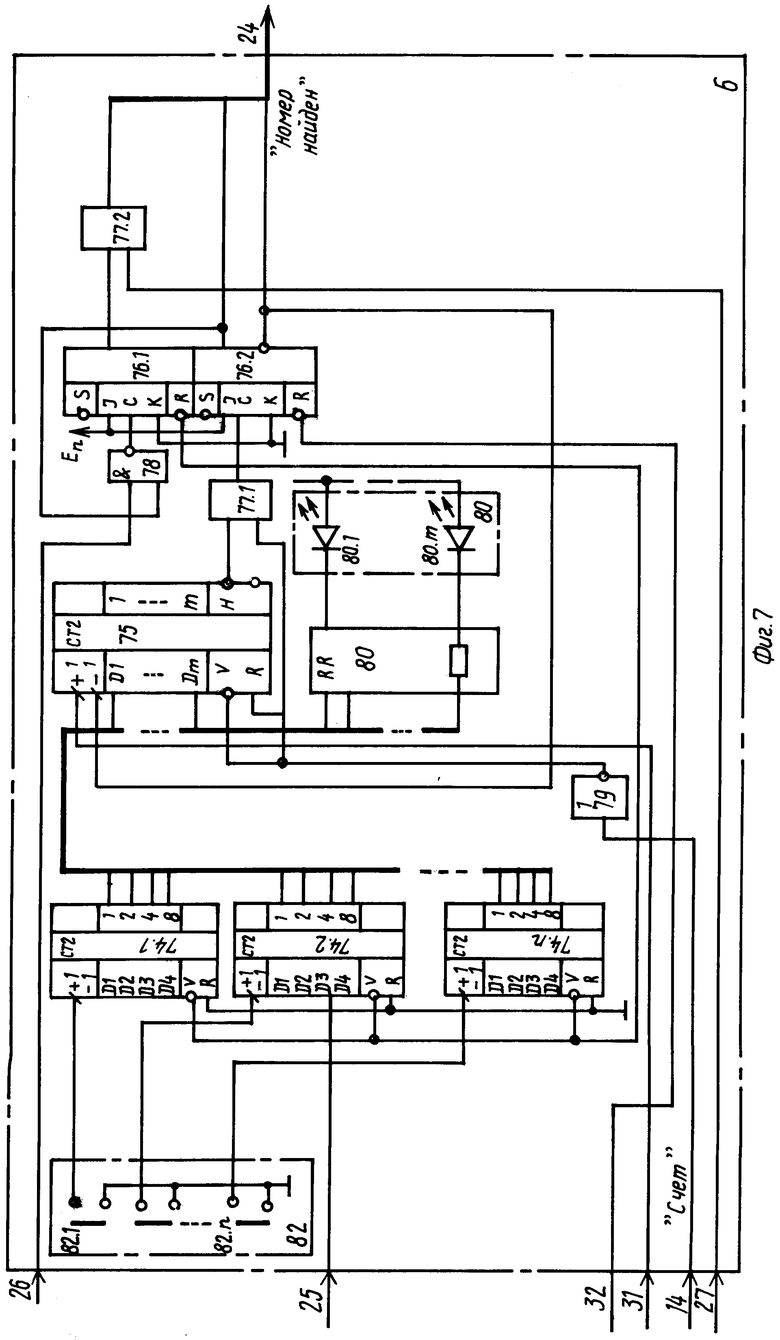

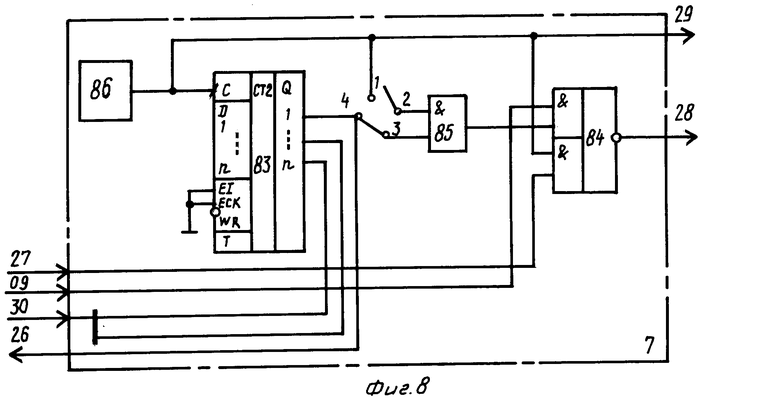

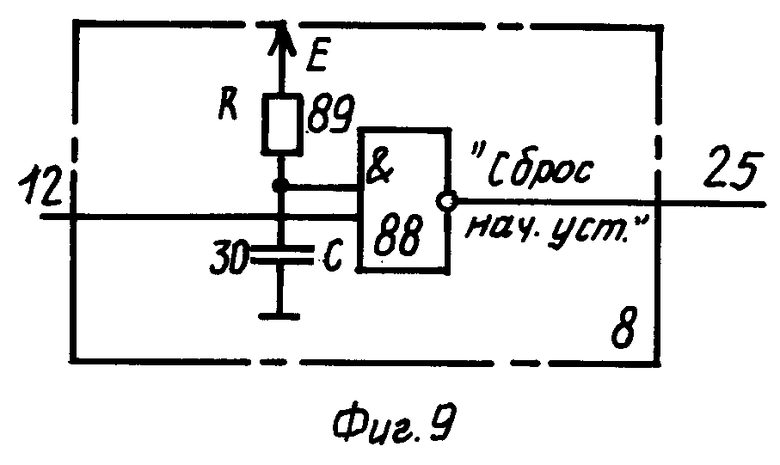

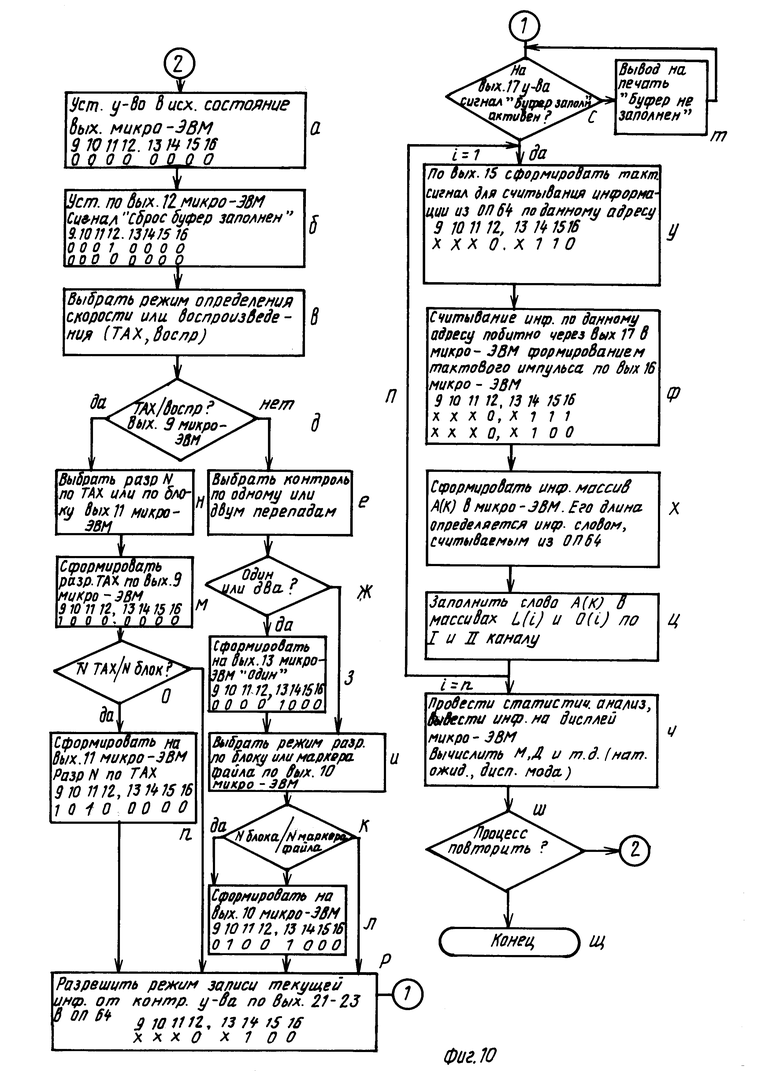

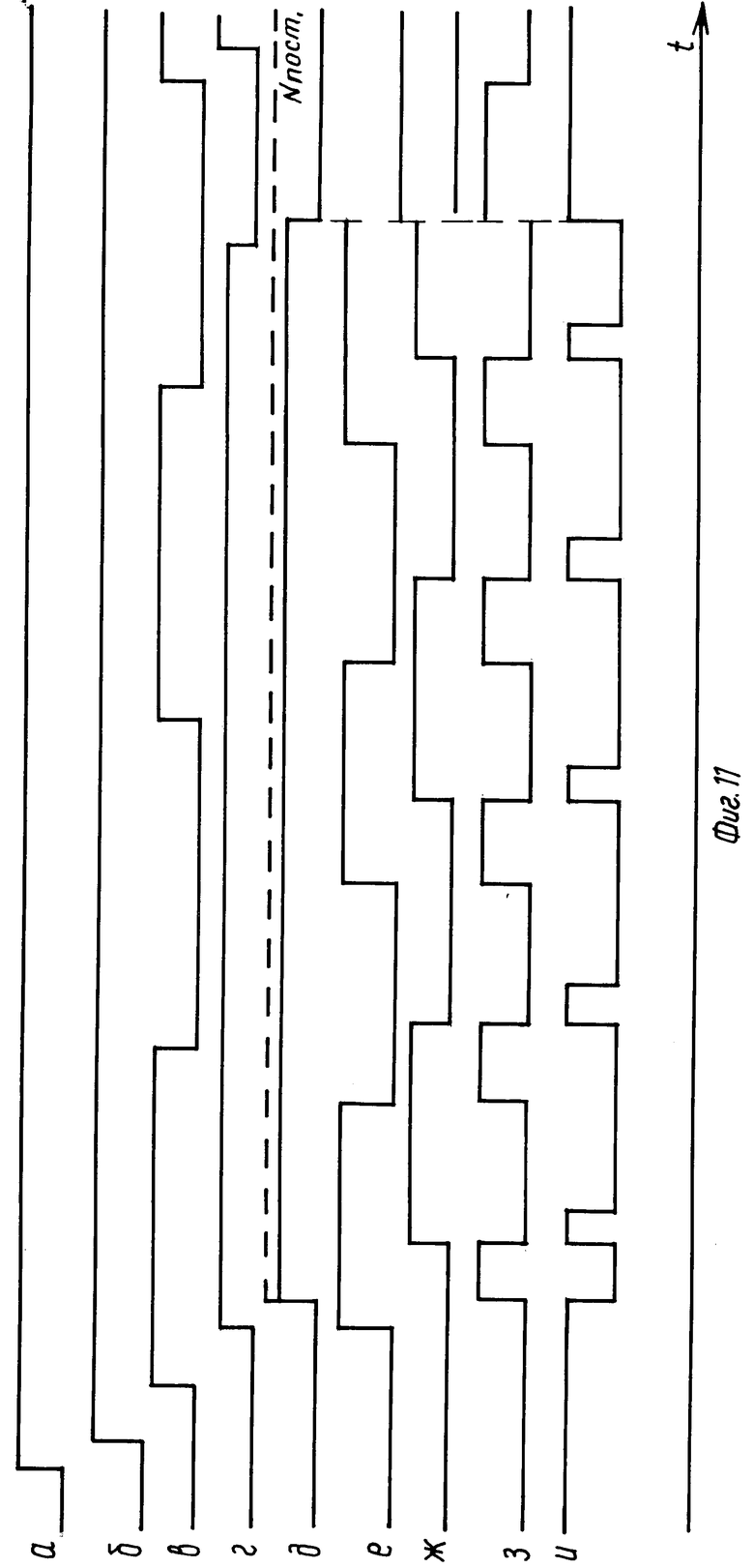

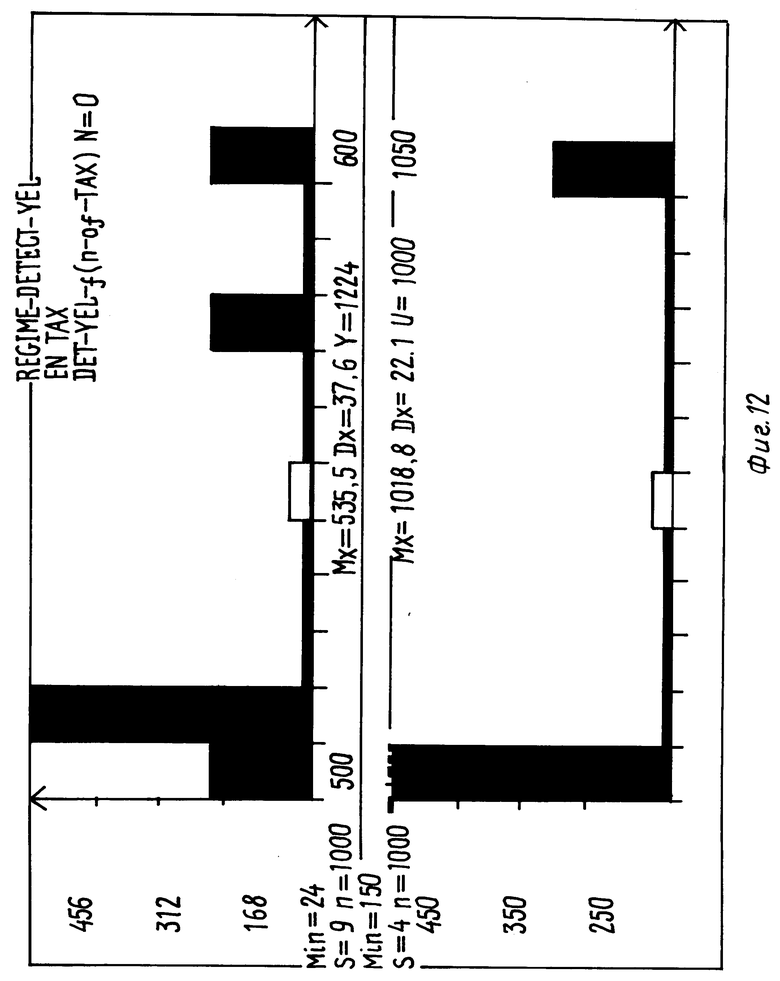

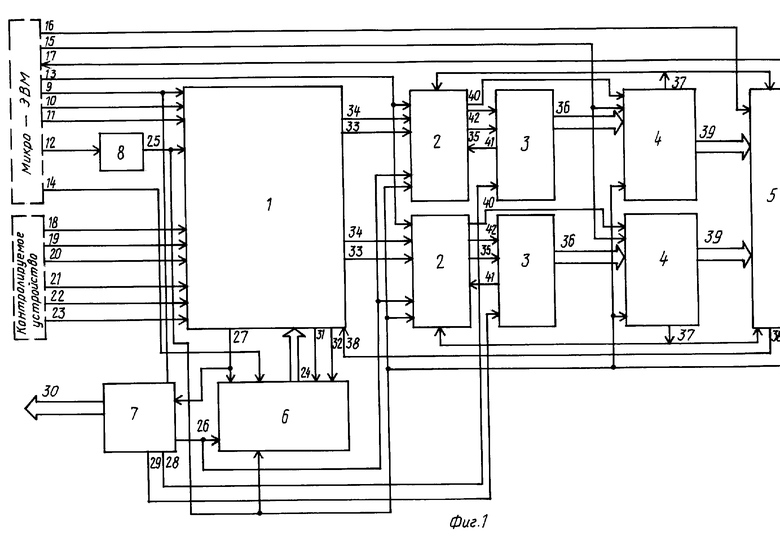

На фиг.1 представлена структурная схема устройства для диагностического контроля канала воспроизведения АЦМЗ; на фиг.2 - схема блока коммутатора; на фиг. 3 - схема первого и второго блока формирователей; на фиг.4 - схема первого и второго блока измерения временных интервалов; на фиг.5 - схема первого и второго блока регистратора; на фиг.6 - счет схема блока считывания; на фиг.7 - схема блока выбора номера; на фиг.8 - схема блока синхронизации; на фиг.9 - схема формирования импульса сброса; на фиг.10 - алгоритм совместной работы устройства с микро-ЭВМ и с контролируемым устройством; на фиг. 11 - временная диаграмма работы устройства; на фиг.12 - фрагмент распечатки статистического анализа по двум независимым каналам.

Устройство диагностического контроля канала воспроизведения АЦМЗ (см. фиг. 1) содержит блок 1 коммутатора, первый и второй блок 2 формирователей, первый и второй блок 3 измерения временных интервалов, первый и второй блок 4 регистратора, блок 5 считывания, блок 6 выбора номера, блок 7 синхронизации, блок 8 формирования импульса сброса и имеет первый 9, второй 10 и третий 11 вход выбора режима блока 1, вход 12 сброса блока 8, вход 13 выбора режима первого и второго блока 2, первый вход 14 выбора режима блока 6, тактовый вход 15 первого и второго блока 4, тактовый вход 16 блока 5, которые являются управляющими входами 13-16 устройства для подключения к соответствующим выходам управления микро-ЭВМ, а информационный выход 17 блока 5, который является выходом признака активности информации устройства, подключен ко входу подтверждения признака микро-ЭВМ, первый 18, второй 19, третий 20 вход управления и первый 21, второй 22, третий 23 информационный входы блока 1, которые являются соответственно служебными входами 18-20 и информационными входами 21-23 устройства, подключены к контрольным и контролирующим выходам контролируемого устройства, причем, группа входов признака номера 24 блока 1 соединена с группой выходов блока 6, первый вход сброса 25 которого соединен с входом сброса блока 5, с первым входом сброса блока 1, со входом сброса первого и второго блоков 2 и 4 и с выходом блока 8. Первый тактовый вход 26 блока 6 соединен с первым выходом блока 7 и с тактовым входом первого и второго блока 2, второй вход 27 выбора режима блока 6 подключен ко второму выходу блока 1, и со вторым входом выбора режима блока 7 второй 28 и третий 29 выходы которого подключены к тактовому первого и второго блока 3 соответственно, четвертый и пятый выход которого являются группой 30 контрольных выходов устройства, причем третий выход блока 1 является вторым тактовым входом 31 блока 6, второй вход 32 признака сброса которого подключены к четвертому выходу блока 1, первый и пятый выходы которого являются соответственно информационными входами 33 первого и второго блоков 2, а шестой и седьмой выходы которого подключены ко входам 34 соответственно первого и второго блока 2, первый выход которых соединен со входом 35 признака загрузки соответственно первого второго блока 3, группа выходов которых является информационной группой входов 36 первого и второго блока 4, выходы 37 признака заполнения буфера которых подключен ко входу признака соответственно первого и второго блока 2 и к группе входов признака заполнения буфера первого и второго каналов блока 5, выход признака заполнения буфера двух каналов которого является вторым входом 38 сброса блока 1, первая и вторая группа информационных входов блока 5 подключена к группам выходов 39 блоков 4, вход признака записи которых соединен с вторым выходом 40 соответственно первого и второго блока 2, вход признака переноса которых является выходом 41 соответственно первого и второго блока 3, вход управления 42 которых является третьим выходом первого и второго блока 2.

Блок 1 коммутатора (см. фиг.2) содержит элемент НЕ 43, элемент 2 2И-ИЛИ-НЕ 44, одновибратор 45, элемент 2И 46, элемент 2И-НЕ 47, элемент 2ИЛИ-НЕ 48, элемент 2ИЛИ 49.

Блок формирователя 2 (см. фиг.3) содержит одновибратор 50, D-триггер 51, IK-триггер 52, элемент 2И 53, 2ИЛИ 54, элемент 4И 55, элемент 2И-НЕ 56, элемент НЕ 57, элемент задержки 58, состоящий из резистора и конденсатора.

Блок измерения временных интервалов 3 (см. фиг.4) содержит элемент ИЛИ 59, счетчик 60, шинный формирователь 61.

Блок регистрации 4 (см. фиг. 5) содержит IK-триггер 62, счетчик 63, элемент ОЗУ 64, элемент 2И 65, элемент 2 ИЛИ 66, элемент НЕ 67.

Блок считывания 5 (см. фиг.6) содержит мультиплексор 68, счетчик 69 и 70, дешифратор 71, элемент ИЛИ 72, элемент НЕ 73.

Блок выбора номера 6 (см. фиг.7) содержит счетчик 74 и 75, IK-триггер 76, элемент 2И 77, элемент 2И-НЕ 78, элемент НЕ 79, блок резисторов 80, индикаторы 81, кнопочные переключатели 82.

Блок синхронизации 7 (см. фиг.8) содержит счетчик 83, элемент 2И-ИЛИ-НЕ 84, элемент 2И 85, генератор тактовых импульсов 86; переключатель 87.

Блок формирования импульса сброса 8 (см. фиг.9) содержит элемент 2И-НЕ 88, резистор 89, конденсатор 90.

Блок 1 коммутатора предназначен для выбора одной из комбинаций режимов, поступающих по первому-третьему входу 9-11 выбора режима (РАЗР, ТАХ, НОМЕРА БЛОКА, ФАЙЛА) от микро-ЭВМ в соответствии с алгоритмом (фиг.10), для задания управления по признакам (БЛОК, МАРКЕР, ФАЙЛА, ДВИЖЕНИЕ), по первому-третьему входу 18-20 управления блока с целью коммутации сигналов (ТАХ, ВОСПРОИЗВОДИМЫЕ ДАН С МЛ и СИНХРО), формируемых в контролируемом устройстве (в канале воспроизведения АЦМЗ) и поступающих на первый-третий 21-23 информационные входы блока и далее в первый и второй блока 2 формирователей.

Первый и второй блок 2 формирователя нормированного импульса предназначен для формирования управляющих сигналов, поступаемых с первого 35, третьего 42 и второго 40 выходов блока соответственно на вход признака загрузки и управления первого и второго блока 3 измерения временных интервалов, и на вход признака записи первого и второго блока 4 регистрации в соответствии с временной диаграммой (см. фиг.11).

Первый и второй блок 3 измерения временных интервалов предназначен для подсчета периода следования импульсов информационных сигналов, поступаемых от контролируемого устройства по независимым каналам 33 с первого и второго блоков 3 относительно служебного сигнала 34 и 13, формируемых под управлением контрольных сигналов АЦМЗ и микро-ЭВМ в соответствии с алгоритмом (см. фиг.10).

Первый и второй блок 4 регистрации предназначен для запоминания информационного массива, сформированного из величин измеряемых временных интервалов контролируемых сигналов, поступающих из первого и второго блоков 3 по независимым каналам 36 в режиме записи, в моменты, определяемые сигналами с выхода 40 первого и второго блока 2 формирователей в соответствии с временной диаграммой (см. фиг.11).

Блок 5 считывания предназначен для считывания информационного массива, занесенного в режиме записи в ОЗУ 64 первого и второго блока 4, в микро-ЭВМ, под ее управлением через выход 17 блока в режиме считывания после формирования признака заполнения буфера.

Блок 6 выбора номера предназначен для выбора номера признака (с какого номера блока, файла или ТАХ начинать процесс записи) с помощью кнопочных переключателей 82, с последующим его нанесением в обратном коде через счетчик 74 и в счетчик 75 с одновременным отображением номера на индикаторах 81, для нахождения номера в процессе работы контролируемого устройства под управлением микро-ЭВМ, а также для формирования группы 24 сигналов признака номера, поступаемых в блок 1 коммутатора.

Блок 7 синхронизации предназначен для формирования сигналов тактирования, поступаемых с выходов 28 и 29 соответственно на тактовый вход первого и второго блока измерения временных интервалов, а также для формирования текстируемых сигналов, представляемых собой контрольную группу 30 блока. Выбор признака режима (воспроизведения или ТАХ) осуществляется с помощью переключателя 87.

Блок 8 формирования импульса сброса предназначен для формирования сигнала начальной установки устройства в исходное состояние и сброса под управлением микроЭВМ через вход сброса в соответствии с алгоритмом (см. фиг. 10).

В качестве одновибратора 50 блока 2 формирователя предлагается использовать микросхему 155АГЗ, а D-триггера - 531ТМ8.

В качестве счетчика 60 блока 3 может быть использовано микросхема 531ИЕ17.

Оперативная память 64 первого и второго блока 4 регистрации представляет собой ОЗУ статического типа (например, емкостью 1К4Х10) 132РУ8, а в качестве счетчика 63 может быть использована микросхема типа 555ИЕ7 (четырехразрядный асинхронный счетчик).

Мультиплексор 68 блока 5 считывания представляет собой микросхему 555КП12, а счетчиками 69 и 70 могут быть микросхемы 555ИЕ7 и ИЕ5.

В качестве счетчика 74 и 75 блока 6 выбора номера может быть использована микросхема 555ИЕ7, а в качестве индикаторов - светодиоды типа ЗЛС341Б.

В качестве счетчика 83 блока 7 синхронизации может быть использована микросхема типа 531ИЕ17, а в качестве генератора любой кварцевый генератор, совместный с TTL или кварцевый генератор Пирса на полевом транзисторе с частотой генерации до 50 МГц (Электронные схемы, 1300 примеров, под ред. Р. Графа, Москва "Мир", 1989 г.).

Устройство работает следующим образом.

Для приведения устройства диагностического контроля канала воспроизведения АЦМЗ в исходное состояние на первый вход сброса блока 1, на вход сброса первого и второго блоков 2 и 4, 5, на первый вход сброса блока 6 подается сигнал "Сброс + Начальная установка" с выхода 25 блока 8, который формируется после включения электропитания или же под управлением микро-ЭВМ с выхода 12 в соответствии с алгоритмом (см. фиг.10).

В результате одновибраторы 50 первого и второго блока 2, IK-триггеры 62 первого и второго блока 4, счетчик 70 и IK-триггер 76.1 блока 6 устанавливаются в исходное состояние, на выходах IK-триггера 62 формируется сигнал "Разрешение записи" в ОЗУ 64, разрешение на счет через элементы 65.1, 66.1 и 67 счетчика 63, и сигнал отсутствия "Буфер заполнен", который через элементы 55 и 53.2, и вход сброса IK-триггера 52 первого и второго блоков 2 запрещает счет счетчика 60 первого и второго блоков 3 и переводит его в состоянии загрузки нулевой кодовой комбинацией. Кроме того, на выходе IK-триггера 76.1 блока 6 устанавливается уровень отсутствия признака номера, который запрещает проход информации от контролируемого устройства по независимым каналам через элементы 44.3 и 44.4 блока 1.

Устройство работает в двух режимах:

- в режиме записи контролируемая информация от контролируемого устройства в реальном масштабе времени поступает через элементы 44.3 и 44.4 блока 1 по двум независимым каналам в первый и второй блок 2 соответственно для формирования нормированных импульсов 40 и 43 и 35. С помощью сигнала 35, поступающего на вход признака загрузки счетчика 60 первого и второго блоков 3 осуществляется подсчет величины измеряемого импульса тактовыми импульсами, формируемыми с выходов 28 и 29 блока 7 синхронизации, а с помощью сигналов 40 и 42 осуществляется запись этой величины через шинный формирователь 61 в ОП 64 первого и второго блока 4 по соответствующему адресу:

- в режиме считывания информации из ОЗУ 64 первого и второго блоков 4 считывается одновременно с двух каналов через мультиплексор 68 блока 5 в микро-ЭВМ на вход 17, под ее управлением по линиям 15 и 16.

Разделение этих режимов по времени решается аппаратурой устройства и управлением микро-ЭВМ в соответствии с алгоритмом (см. фиг.10).

Устройство многофункциональное и позволяет создавать информационные массивы относительно служебного сигнала с последующим статистическим анализом в микро-ЭВМ. В качестве служебного сигнала может быть следующие признаки от контролируемого устройства: "Блок", "Маркер файла", ТАХ совместно с сигналом "Движение". В зависимости от управляющей комбинации выбора режима по линиям 9-11 от микро-ЭВМ информационный массив может заноситься в ОП 64 относительно любого номера ТАХ, блока, маркера файла. Устройство обладает следующими основными функциями: определения колебаний к скорости МН; в режиме воспроизведения (определение фазовых и частотных сдвигов при вхождении в синхронизм систем синхронизации АЦМЗ и проверке ее работоспособности в процессе слежения воспроизводимой информации, с последующим статистическим анализом; определение характера воспроизводимой информации, считываемой с любых двух дорожек МН по независимым каналам); разрешения конфликтной ситуации при выходе из строя отдельных узлов АЦМЗ (тракт перемещения МП или канал воспроизведения АЦМЗ). Выявление источника возмущения осуществляется в режиме определения колебаний скорости МН в тракте его перемещения статистическим анализом величин измеряемых импульсов, поступаемых от контролируемого устройства по линиям 21, 23 признак "Информационный сигнал" и 22 признак - "ТАХ".

Управление устройством диагностического контроля канала воспроизведения осуществляется по управляющим выходам 9-16 микро-ЭВМ в соответствии с алгоритмом (см. фиг.10).

Режим записи информации, поступаемой с контрольных выходов 21-24 контролируемого устройства происходит согласно временной диаграмме (см. фиг. 11), а режим считывания информации из ОЗУ 64 в микроЭВМ по выходу 17 в соответствии с алгоритмом фиг.10.

Программная установка устройства диагностического контроля осуществляется передачей всех нулей - (0 с выходов 9-16 микро-ЭВМ (фиг.10а). Для блокировки сигнала 16 "Буфер 16 заполнен" на вых. 17, а также для приведения устройства в исходное состояние по выходу 12 формируется сигнал "Сброс буфер заполнен" который, поступая через элемент 2И 88 фиг.8 блока 8 сбрасывает IK-триггеры 62 по входу 25 первого и второго блока 4 фиг.5. В результате на 17 выходе через элемент 2ИЛИ 72 и в первый вход мультиплексора 68 блока 5 считывания формируется признак отсутствия заполнения буфера и установка блоков 2, 4, 5, 6 в исходное состояние в соответствии с фиг.106 (последовательная передача кодовой комбинации с выходов 9-16 1

с выходов 9-16 микро-ЭВМ (фиг.10а). Для блокировки сигнала 16 "Буфер 16 заполнен" на вых. 17, а также для приведения устройства в исходное состояние по выходу 12 формируется сигнал "Сброс буфер заполнен" который, поступая через элемент 2И 88 фиг.8 блока 8 сбрасывает IK-триггеры 62 по входу 25 первого и второго блока 4 фиг.5. В результате на 17 выходе через элемент 2ИЛИ 72 и в первый вход мультиплексора 68 блока 5 считывания формируется признак отсутствия заполнения буфера и установка блоков 2, 4, 5, 6 в исходное состояние в соответствии с фиг.106 (последовательная передача кодовой комбинации с выходов 9-16 1 0

0 . Далее оператор через микро-ЭВМ осуществляет выбор функционального режима (определения скорости фиг.10 вг или воспроизведения - фиг.10вд). В случае определения скорости по вых. 9-16 передается кодовая комбинация (4

. Далее оператор через микро-ЭВМ осуществляет выбор функционального режима (определения скорости фиг.10 вг или воспроизведения - фиг.10вд). В случае определения скорости по вых. 9-16 передается кодовая комбинация (4 фиг. 10м. Затем оператором через микро-ЭВМ задается дополнительная информация в зависимости от функционального режима (см. фиг.10 г-н или фиг.10 дл). С помощью кнопочных переключателей 82 выбирается номер признака (блок, ТАХ, маркер файла) относительно которого начинается процесс формирования информационного массива по двум независимым каналам из величин измеряемых интервалов контролируемых сигналов. Т. е. оператор, последовательным нажатием кнопок 82 блока 6 фиг. 7 устанавливает номер признака в обратном коде в счетчике 74.1-74. п, который заносится по информационным входам в счетчик 75.1-75.п и там запоминается до формирования сигнала "Счет" под управлением микро-ЭВМ (фиг.14) в соответствии с алгоритмом (фиг.10р). Номер признака с выхода счетчика 74.1-74.в отображается на индикаторах 81 через резисторную сборку 80 блока 6 фиг.7. Кроме того, в исходном состоянии на выходах IK-триггеров 76.1 и 76.2 отсутствует признак "Номер найден" (группа признаков 24 блока 6 фиг. 7), который осуществляет блокировку контрольных сигналов, поступаемых с выходов 21-23 через элементы 2И 46.1 и элементы 2ИЛИ 46.2, 48.3 на первый, четвертый вход элемента 2-2И-ИЛИ-НЕ 44.3 и 44.4 блока 1 коммутатора фиг.2 устанавливает в состояние сброса через второй вход элемента 4И 55 и первый вход элемента 2И 53.2 IK-триггера 52 первого и второго блока 2. Выходы IK-триггеров в свою очередь переводят счетчик 60 первого и второго блоков 3 фиг.4 в состояние загрузки нулевой кодовой комбинации по информационному входу.

фиг. 10м. Затем оператором через микро-ЭВМ задается дополнительная информация в зависимости от функционального режима (см. фиг.10 г-н или фиг.10 дл). С помощью кнопочных переключателей 82 выбирается номер признака (блок, ТАХ, маркер файла) относительно которого начинается процесс формирования информационного массива по двум независимым каналам из величин измеряемых интервалов контролируемых сигналов. Т. е. оператор, последовательным нажатием кнопок 82 блока 6 фиг. 7 устанавливает номер признака в обратном коде в счетчике 74.1-74. п, который заносится по информационным входам в счетчик 75.1-75.п и там запоминается до формирования сигнала "Счет" под управлением микро-ЭВМ (фиг.14) в соответствии с алгоритмом (фиг.10р). Номер признака с выхода счетчика 74.1-74.в отображается на индикаторах 81 через резисторную сборку 80 блока 6 фиг.7. Кроме того, в исходном состоянии на выходах IK-триггеров 76.1 и 76.2 отсутствует признак "Номер найден" (группа признаков 24 блока 6 фиг. 7), который осуществляет блокировку контрольных сигналов, поступаемых с выходов 21-23 через элементы 2И 46.1 и элементы 2ИЛИ 46.2, 48.3 на первый, четвертый вход элемента 2-2И-ИЛИ-НЕ 44.3 и 44.4 блока 1 коммутатора фиг.2 устанавливает в состояние сброса через второй вход элемента 4И 55 и первый вход элемента 2И 53.2 IK-триггера 52 первого и второго блока 2. Выходы IK-триггеров в свою очередь переводят счетчик 60 первого и второго блоков 3 фиг.4 в состояние загрузки нулевой кодовой комбинации по информационному входу.

После формирования микро-ЭВМ по вых.14 сигнала "Счет" фиг.10р счетчик 75.1-75.п блока 6 фиг.7 переходит в состояние счетного режима. Сигналы признака с вых.18-20 контролируемого устройства преобразуются в нормированные сигналы через одновибраторы 45.1 и 45.2, элемент 2И 46.1 и 2-2И-ИЛИ-НЕ 44.2 блока 1 фиг.2, которые поступают на тактовый вход счетчика 75 блока 6 фиг. 7. При формировании переноса с выхода счетчика 75 IK-триггера 76.1 и 76.2 через элемент 2И 77.1 переходят в состояние активности признака "Номер найден", который передается через группу 24 выходов блока 6 на первый и второй вход элементов 46.2 и 46.3, на первый вход элемента 2И 46.6 на первые входы элементов 2 ИЛИ 48.1 и 49.4 блока 1 фиг.2. В результате на втором-третьем входах элемента 2-2И-ИЛИ-НЕ 44.3 и 44.4 формируется сигнал разрешения на прохождение информационных сигналов от контролируемого устройства и разрешение на измерение величины временных интервалов по входу 34 первого и второго блоков - формирователей 2.

Режим записи в ОЗУ 64 блока 4 фиг.5 осуществляется в соответствии с временной диаграммой фиг.11. Фиг.11а соответствует заданию функционального режима разрешения воспроизведения по блоку (вых.9, 10), а фиг.11б,в,г соответствуют признакам движения. ТАХ, блока (выходов 20, 22, 18). На фиг.11л отражен процесс формирования признака "Номер найден" (вых. IK-триггеров 76.1 и 76.2 блока 6). На фиг.11е показан информационный выход контролируемого устройства по двум каналам (вых.21-23).

Информационные сигналы по двум независимым каналам в режиме записи поступают из блока 1 на инверсный и прямой входы одновибраторов 50.1 и 50.2 первого и второго блоков 2. На D-триггере формируется сдвиг фиг.11ж для организации нормированного импульса записи через элемент 2И 56 и НЕ 57, через элемент 2И 65.11, 2 ИЛИ 66.1, НЕ 67, 2ИЛИ 65.2 в ОЗУ 64 первого и второго блока 4 фиг.11з. С выхода D-триггера 51 первого и второго блоков 3 сдвинутый на несколько тактов сигнал (тактирование идет от блока синхронизации по входу 26 блока) поступает на одновибратор 50.3 и далее, через элемент задержки 58 (стандартная RC-цепочка) и через элемент 4И 55, 2И 53.2 на тактовый вход и соответственно вход сброса К-триггера 52 с целью создания нормированного импульса загрузки нулевой кодовой комбинации по синхроимпульсу счетчика 60 первого и второго блоков 3 фиг.11и. Величина измеряемого импульса через шинный формирователь 61, просчитанных синхроимпульсов (выходы 29 и 28 блока синхронизации 7), поступаемого на тактовый вход соответственно первого и второго блоков 3, записывается последовательно по адресу, выбираемого счетчиком 63 первого и второго блока 4. В результате, в ОЗУ 64 создается информационный массив по двум независимым каналам.

Переход в режим чтения информационного массива из ОЗУ 64 осуществляется в соответствии с опросом микро-ЭВМ признака "Буфер заполнен" по вых.17 устройства фиг. 10с, т. Сигнал "Буфер заполнен I и II каналов" формируется независимо друг от друга путем активности переноса с выходов счетчика 63 первого и второго блоков 4 фиг.5. Признак переноса переводит ОЗУ 64 в режим чтения через IK-триггер 62, через элемент 2ИЛИ 66.2 блокирует IK-триггеры 52 первого и второго блока 2 и одновибраторы 45.1 и 45.2 блока 1.

Процесс считывания информации из ОЗУ осуществляется в соответствии с фиг. 10у-ш под управлением микро-ЭВМ с его выходов 15-16. По выходу 15 микро-ЭВМ формирует тактовый сигнал, который поступает на счетный вход счетчика 63 через элементы 2ИЛИ 66.1 и НЕ 67. На входе управления элемента ОЗУ 64 установлен признак чтения с выхода IK-триггера, который взводится по переполнению счетчика 62 в режиме записи информации в ОЗУ 64 первого и второго блока 4. В результате на информационном выходе счетчика 63 устанавливается соответствующий адрес, который поступает на адресный вход ОП 64, по которому выбирается информационное слово, которое в свою очередь передается в виде первой и второй информационной группы 39 на информационный вход мультиплексоров 68 блока 5. Считывание слова побитно по выбранному адресу осуществляется под управлением микро-ЭВМ по выходу 16 фиг.10ф. Тактовый импульс поступает на счетный вход счетчика НЕ 7 69, информационные выходы которого, один из которых подключен к счетному входу НЕ 5 70, и выходы дешифратора 71 блока 5 осуществляют управление мультиплексором 68 при последовательном побитном считывании информации на вых.17 в микроЭВМ. Информация, занесенная в массив А фиг.10х микро-ЭВМ разбивается программистом на массивы L( ) и O(

) и O( ) соответствующие первому и второму каналам. Далее программно решаются проблемы статистического анализа и оценки работоспособности устройства, в том числе выявление источника возмущения рассогласования сигналов по двум каналам, фиг.10ч и фрагмент распечатки фиг.12 с подсчетом M(x), D(х), моды, медианы и т.д. В программе предусмотрен повторный запуск относительно другого служебного сигнала и любого произвольного номера (переход 2 фиг.10ш). Если нет такой необходимости, то осуществляется переход на окончание процесса работы с микро-ЭВМ и контролируемым устройством фиг.10ш.

) соответствующие первому и второму каналам. Далее программно решаются проблемы статистического анализа и оценки работоспособности устройства, в том числе выявление источника возмущения рассогласования сигналов по двум каналам, фиг.10ч и фрагмент распечатки фиг.12 с подсчетом M(x), D(х), моды, медианы и т.д. В программе предусмотрен повторный запуск относительно другого служебного сигнала и любого произвольного номера (переход 2 фиг.10ш). Если нет такой необходимости, то осуществляется переход на окончание процесса работы с микро-ЭВМ и контролируемым устройством фиг.10ш.

Технико-экономические преимущества заявляемого технического решения расширение функциональных возможностей предложенного устройства (а именно: повышения точности контроля измеряемых величин, с их представлением в цифровом виде, сигналов, поступающих в виде любой кодовой комбинации как непрерывно, так и дискретно (поблочно), повышения информативности с последующей статистической обработкой, в микро-ЭВМ, за счет обеспечения регистрации величин измеряемых временных интервалов контролируемых сигналов по независимым каналам относительно служебного сигнала с определенным номером определяется совокупностью используемых в устройстве технических средств и новой организацией связей.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ПРОБНИК | 1991 |

|

RU2041473C1 |

| УСТРОЙСТВО ДЛЯ ВИЗУАЛЬНОГО КОНТРОЛЯ ИСПОЛНЕНИЯ ПРОГРАММ | 1991 |

|

RU2012044C1 |

| Устройство для индицирования текущего времени | 1989 |

|

SU1661719A1 |

| Полевая телеметрическая сейсмическая станция | 1986 |

|

SU1327031A2 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1748283A1 |

| Устройство для сортировки информации | 1988 |

|

SU1501039A1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

Изобретение относится к технике магнитной записи и может быть использовано контрольно-измерительной аппаратурой, а также во встроенных средствах диагностического контроля аппаратуры цифровой магнитной записи. Целью изобретения является повышение точности контроля по независимым каналам относительно служебного управляющего сигнала. Сущность изобретения: устройство диагностического контроля канала воспроизведения аппаратуры цифровой магнитной записи содержит 1 блок (1) коммутатора, 2 блока (2) формирователей, 2 блока (3) измерения временных интервалов, 2 блока (4) регистратора, 1 блок (5) считывания, 1 блок (6) выбора номера. 1 блок (7) синхронизации, 1 блок (8) формирования импульса сброса, 4 управляющих входа (13-16) устройства, связанные с блоком системного управления и обработки, например, микроЭВМ. 12 ил.

УСТРОЙСТВО ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ КАНАЛА ВОСПРОИЗВЕДЕНИЯ АППАРАТУРЫ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ, содержащее блок считывания, блок коммутатора, первый вход выбора режима которого и первый информационный вход являются соответственно управляющим и информационным входами устройства, первый блок формирователей, информационный вход которого соединен с первым информационным выходом блока коммутатора, первый блок измерения временных интервалов, блок формирования импульса сброса, выход которого подключен к входу сброса блока считывания, первый блок регистрации, отличающееся тем, что, с целью повышения точности и информативности контроля по независимым каналам относительно служебного управляющего сигнала, в него введены второй блок формирователей, второй блок измерения временных интервалов, второй блок регистрации, блок выбора номера, блок синхронизации и блок системного управления и обработки блок считывания выполнен двухканальным, а блок коммутатора выполнен с вторым и третьим входами выбора режима, блок формирования импульса сброса - с входом сброса, первый блок формирователей - с входом выбора режима, которые совместно с первым входом выбора режима блока выбора номера, входом выбора режима второго блока формирователей, соединенного с входом выбора режима первого блока формирователей, тактовыми входами блоков регистрации и блока считывания, первым входом выбора режима блока коммутатора, подключенным к первому входу выбора режима блока синхронизации являются группой управляющих входов устройства, связанных с соответствующими управляющими выходами блока системного управления и обработки, вход подтверждения инициализации которого соединен с информационным выходом блока считывания, первый, второй и третий управляющие входы, первый, второй и третий информационные входы блока коммутатора являются соответственно группами служебных и информационных входов устройства, связанных с контролируемым каналом воспроизведения аппаратуры цифровой магнитной записи, блок коммутатора выполнен с группой входов признака номера, подключенной к группе входов признака номера блока выбора номера, вход сброса которого соединен с входом сброса блока считывания, с первым входом сброса блока коммутатора, с входами сброса первого и второго блоков формирователей, первого и второго блоков регистрации, первый тактовый вход - с первым выходом блока синхронизации и с тактовыми входами первого и второго блоков формирователей, второй вход выбора режима - с вторым выходом блока коммутатора и с вторым входом выбора режима блока синхронизации, второй и третий выходы которого подключены к тактовым входам соответственно первого и второго блоков измерения временных интервалов, а четвертый и пятый выходы являются группой контрольных выходов устройства, третий выход блока коммутатора подключен к второму тактовому входу блока выбора номера, вход признака сброса которого соединен с четвертым выходом блока коммутатора, пятый информационный выход которого соединен с информационным входом второго блока формирователей, а шестой и седьмой выходы - служебными входами соответственно первого и второго блоков формирователей, первые выходы которых соединены с входами признаков загрузки соответственно первого и второго блоков измерения временных интервалов, группы информационных выходов которых подключены к группам информационных входов соответственно первого и второго блоков регистрации, выходы признаков буферного заполнения которых подключены к входам признаков соответственно первого и второго блоков формирователей и к группам входов признака буферного заполнения первого и второго каналов блока считывания, выход признаков буферного заполнения которых соединен с вторым входом сброса блока коммутатора, первая и вторая группы информационных входов блока считывания подключены к группам информационных выходов соответствующих блоков регистрации, выход признака записи которых соединен с вторыми выходами соответственно первого и второго блоков формирователей, входы признаков переноса которых подключены к выходам соответственно первого и второго блоков измерения временных интервалов, входы управления которых соединены с третьими выходами соответственно первого и второго блоков формирователей, при этом блок синхронизации выполнен в виде счетчика, генератора тактовых импульсов, элемента 2 - 2И - ИЛИ - НЕ, элемента И и переключателя, выход тактового генератора соединен с тактовым входом счетчика, через первую группу переключателя - с одним входом элемента И, с третьим входом элемента 2 - 2И - ИЛИ - НЕ и является третьим выходом блока синхронизации, первый выход счетчика через вторую группу переключателя соединен с другим входом элемента И является первым выходом блока синхронизации, четвертым и пятым выходами которого являются третий и четвертый выходы счетчика, выход элемента И подключен к второму входу элемента 2 - 2И - ИЛИ - НЕ, первый и четвертый входы которого являются соответственно первым и вторым входами выбора режима, а выход - вторым выходом блока синхронизации, блок выбора номера содержит два счетчика, два JK-триггера , два элемента И, элемент И - НЕ, элемент НЕ, блок резисторов, индикатора и переключатель через соответствующие контактные группы которого тактовые входы первого счетчика связаны с шиной нулевого потенциала, группы выходов которого соединены через соответствующие резисторы блока резисторов с соответствующими индикаторами и подключены к группе входов данных второго счетчика, вход признака загрузки которого подключен к одному входу первого элемента И и к выходу элемента НЕ, вход которого является первым входом выбора режима блока выбора номера, выход признака переноса второго счетчика соединен с другим входом первого элемента И, выход которого подключен к тактовому входу второго JK-триггера, тактовый вход первого JK-триггера подключен к выходу элемента И - НЕ, один вход которого соединен с прямым выходом второго JK-триггера, а другой вход является первым тактовым входом блока выбора номера, K-входы и J-входы JK-триггеров подключены к шинам нулевого и единичного потенциалов соответственно, прямой выход первого JK-триггера соединен с одним входом второго элемента И, другой вход которого является вторым входом выбора режима блока выбора номера, инверсный выход второго JK-триггера подключен к вычитающему тактовому входу второго счетчика, суммирующий тактовый вход которого является вторым тактовым входом блока выбора номера, выходом признака сброса которого является вход сброса второго JK-триггера, входом сброса - входы разрешения сброса первого счетчика, входы сброса которого соединены с шиной нулевого потенциала, а группой выходов признака номера - прямой и инверсный выходы второго JK-триггера и выход второго элемента И, блок коммутатора содержит пять элементов НЕ, четыре элемента 2 - 2И - ИЛИ - НЕ, два одновибратора, восемь элементов 2И, элемент 2И - НЕ, три элемента 2ИЛИ - НЕ, четыре элемента 2 ИЛИ, вход первого элемента НЕ и первый вход третьего элемента 2И, вход второго элемента НЕ и третий вход первого элемента 2 - 2И - ИЛИ - НЕ, вход третьего элемента НЕ и третий вход второго элемента 2 - 2И - ИЛИ - НЕ являются соответственно первым, вторым и третьим входами выбора режима блока коммутатора, вход четвертого элемента НЕ и четвертый вход первого элемента 2 - 2И - ИЛИ - НЕ, первый вход первого элемента 2 - 2И - ИЛИ - НЕ, первый вход первого элемента 2И являются соответственно первым, вторым и третьим управляющими входами блока коммутатора, первый вход второго элемента 2ИЛИ - НЕ, второй вход первого элемента 2И, первый вход третьего элемента 2ИЛИ - НЕ являются соответственно первым, вторым и третьим информационными входами блока коммутатора, первый вход четвертого элемента 2И является первым входом сброса блока коммутатора входы сброса первого и второго одновибраторов являются вторым входом сброса блока коммутатора, первый вход второго элемента 2И и второй вход третьего элемента 2И, первый вход шестого элемента 2И, первый вход первого элемента 2ИЛИ - НЕ и четвертого элемента 2ИЛИ являются группой входов признака номера блока коммутатора, выход первого элемента НЕ подключен ко второму входу второго элемента 2И, шестого элемента 2И, к первому входу пятого элемента 2И и является вторым выходом блока коммутатора выход второго элемента НЕ соединен с вторым входом первого элемента 2 - 2И - ИЛИ - НЕ, а выход третьего элемента НЕ подключен к первому входу второго элемента 2 - 2И - ИЛИ - НЕ, выходы которых соединены с первым и вторым инверсными входами первого и второго одновибраторов, второй инверсный и первый входы которых подключены соответственно шине нулевого и единичного потенциала и к входу пятого элемента НЕ, выход которого является третьим выходом блока коммутатора, выход четвертого элемента НЕ соединен с вторым и входами элементов 2ИЛИ - НЕ, 2 ИЛИ, выходы которых соединены с вторыми входами второго и третьего элементов 2ИЛИ - НЕ и первыми входами седьмого и восьмого элементов 2И, и соответственно с вторым входом пятого элемента И, выход которого подключен к первому входу первого элемента ИЛИ , выход которого является шестым выходом блока коммутатора, а выход четвертого элемента 2ИЛИ является седьмым выходом блока коммутатора, выходы первого и второго одновибраторов соединены со вторым входом второго элемента 2 - 2И - ИЛИ - НЕ и соответственно с первым входом элемента 2И - НЕ, второй вход которого подключен к выходу второго элемента 2И, а выход соединен с вторым входом четвертого элемента 2И, выход которого является четвертым выходом блока коммутатора, выход первого элемента 2И подключен к четвертому входу второго элемента 2 - 2И - ИЛИ - НЕ, к вторым входам седьмого и восьмого элементов 2И и к первому входу третьего элемента 2 - 2И - ИЛИ - НЕ, второй вход которого соединен с выходом третьего элемента 2И, подключен к второму входу первого элемента 2 ИЛИ и к второму входу четвертого элемента 2 - 2И - ИЛИ - НЕ, третий вход третьего элемента 2 - 2И - ИЛИ - НЕ соединен с выходом шестого элемента 2И и с третьим входом четвертого элемента 2 - 2И - ИЛИ - НЕ, первый и четвертый входы которого и четвертый вход третьего элемента 2 2И - ИЛИ - НЕ соединены соответственно с выходами третьего и второго элементов 2ИЛИ, первые выходы которых подключены соответственно к выходам третьего и второго элементов 2ИЛИ - НЕ, а вторые входы - соответственно к выходам восьмого и седьмого элементов 2И, выходы третьего и четвертого элементов 2 - 2И - ИЛИ - НЕ являются первым и пятым выходами блока коммутатора, каждый блок формирователей содержит три одновибратора, D-триггер, JK-триггер, элемент ИЛИ, три элемента И, элемент И - НЕ, элемент НЕ, резистор и конденсатор, первый инверсный и второй входы первого и второго одновибраторов являются информационным входом блока формирователей, вход сброса второго одновибратора соединен с выходом первого элемента И, два входа которого являются входом выбора режима и входом сброса блока формирователей, вход первый и второй инверсный входы первого и второго одновибраторов соединены с шинами единичного и нулевого потенциалов, а выходы подключены через элемент ИЛИ к одному входу элемента И - НЕ и входу данных D-триггера, тактовый вход которого является тактовым входом блока формирователей, третий выход данных D-триггера подключен к первому входу третьего одновибратора, второй инверсный вход которого подключен к шине нулевого потенциала третий инверсный выход данных D-триггера соединен с другим входом элемента И - НЕ, выход которого подключен ко входу элемента НЕ и является третьим выходом блока формирователей прямой выход третьего одновибратора подключен к объединенным выводам резистора и конденсатора и к тактовому входу JK-триггера, инверсный выход - к первому входу третьего элемента И, выход которого соединен через второй элемент И с входом сброса JK-триггера, первый и второй информационные входы которого и другие выводы резистора и конденсатора подключены соответственно к шинам единичного и нулевого потенциалов, выход JK-триггера является первым выходом блока формирователей, выход элемента НЕ является вторым выходом блока формирователей, входом признака переноса, входом признака и служебным входом которого являются другой вход второго элемента И и второй, третий входы третьего элемента И соответственно, четвертый вход которого соединен с входом сброса первого одновибратора, каждый блок измерения временных интервалов выполнен в виде счетчика и шинного формирователя, группа входов которого соединена с группой выходов счетчика, группа входов данных которого подключена к шине нулевого потенциала, выходы переноса являются выходом признака переноса блока измерения временных интервалов, группой информационных выходов которого является группа выходов шинного формирователя, входом управления - вход признака управления шинного формирователя, входом признака загрузки - вход записи-чтения счетчика, а тактовым входом - тактовый вход счетчика, каждый блок регистрации содержит JK-триггер, счетчик, элемент оперативного запоминающего устройства, два элемента И, два элемента ИЛИ и элемент НЕ, входы данных счетчика соединены с шиной нулевого потенциала, к которой подключены J- и K-входы JK-триггера, тактовый вход которого связан с выходом признака переноса счетчика и соединен с одним входом первого элемента И, выход которого подключен к входу загрузки по входу данных кодовой комбинации счетчика, группа выходов которого соединена с группой адресных входов элемента оперативного запоминающего устройства, вход признака записи чтения которого соединен через первый элемент ИЛИ с прямым выходом JK-триггера, а группа выходов является группами информационных входов и выходов блока регистрации, выходом признака буферного заполнения которого является инверсный выход JK-триггера, подключенный через второй элемент И, второй элемент ИЛИ, выход которого соединен с другим входом первого элемента ИЛИ, и элемент НЕ к суммирующему тактовому входу счетчика, а вход сброса JK-триггера подключен к другому входу первого элемента И и является входом сброса блока регистрации, входом признака записи, тактовым входом и выходом признака буферного заполнения которого являются соответственно другой вход второго элемента И, другой вход второго элемента ИЛИ и инверсный выход JK-триггера, блок считывания содержит мультиплексор, два счетчика, дешифратор, элемент ИЛИ - НЕ и элемент НЕ, выход элемента ИЛИ - НЕ подключен к первому входу мультиплексора и является выходом признака буферного заполнения блока считывания, первой и второй группами информационных входов которого являются группы соответствующих информационных входов мультиплексора, группа выходов которого является информационным выходом блока считывания, группой входов признака буферного заполнения первого и второго каналов которого являются соответствующие входы элемента ИЛИ - НЕ, входы данных первого счетчика соединены с шиной нулевого потенциала, вход сброса соединен с входом сброса второго счетчика и выходом элемента НЕ, вход которого является входом сброса блока считывания, тактовым входом которого является суммирующий тактовый вход первого счетчика, выходы которого связаны с входами установки мультиплексора, а второй выход подключен к тактовому входу второго счетчика, первый и второй выходы которого подключены к первому и второму информационным входам соответственно дешифратора, первый инверсный и второй входы управления которого соединены с третьим выходом второго счетчика, а второй инверсный и первый входы подключены к шине нулевого потенциала, а выходы соединены с соответствующими входами групп признаков управления мультиплексора, блок формирования импульса сброса выполнен в виде элемента И - НЕ, резистора и конденсатора, включенных последовательно между шинами единичного и нулевого потенциалов, другие соединенные между собой выводы резистора и конденсатора подключены к одному выводу элемента И - НЕ, другой вход и выход которого являются соответственно входом сброса и выходом блока формирования импульса сброса.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для измерения величины рассогласования сигналов воспроизведения с магнитной ленты | 1980 |

|

SU928402A1 |

Авторы

Даты

1994-12-15—Публикация

1991-11-14—Подача