Изобретение относится к радиотехнике и может быть использовано в широкополосных системах спутниковой связи и навигации, в частности в бортовой аппаратуре спутниковых навигационных систем, типа НАВСТАР.

Целью изобретения является сокращение времени поиска псевдошумовых сигналов.

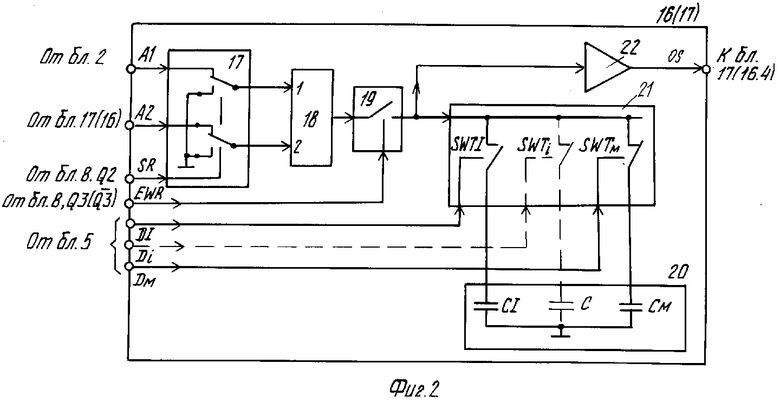

На фиг. 1 представлена структурная электрическая схема устройства поиска псевдошумовых сигналов; на фиг. 2 - вариант выполнения накопителя и дополнительного накопителя.

Устройство поиска псевдошумовых сигналов содержит синхронный детектор 1, когерентный интегратор 2, накопитель 3, компаратор 4, распределитель 5 селекторных стробов, формирователь 6 опорного кода, генератор 7 тактовых импульсов, формирователь 8 селекторных стробов, дополнительный накопитель 9 и блок управления 10. В состав когерентного интегратора входят регистр сдвига 11, блок амплитудного детектирования 12, первый и второй запоминающие блоки 13 и 14 и блоки интегрирования синфазного и квадратурного сигналов 15 и 16, а накопитель 3 и дополнительный накопитель 9 выполнены идентично на переключающих конденсаторах и содержат коммутатор 17, сумматор 18, ключ 19, блок запоминающих конденсаторов 20, блок ключей 21 и усилитель 22 с неразрушающим считыванием.

Устройство поиска псевдошумовых сигналов работает следующим образом.

На сигнальный вход синхронного детектора 1 поступает псевдошумовой радиосигнал Sω(t), где он подвергается преобразованию с понижением частоты в синфазную SJ(t) и квадратурную SQ(t) составляющие, которые поступают на сигнальные входы запоминающих блоков 13 и 14 на переключаемых конденсаторах синфазного и квадратурного сигналов, входящих в состав когерентного интегратора 2. Результирующие псевдошумовые видеосигналы синфазной SJ(t) и квадратурной SQ(t) составляющих описываются равенством

SJ(t)=  xk(t)cos(Δωt+Ф);

xk(t)cos(Δωt+Ф);

SQ(t)=  xk(t)sin(Δωt+Ф), (1) где Δω и Φ - рассогласование по угловой частоте и по фазе между передатчиком и приемником.

xk(t)sin(Δωt+Ф), (1) где Δω и Φ - рассогласование по угловой частоте и по фазе между передатчиком и приемником.

xk= Dk CmP(t-[m-1] Tc)

CmP(t-[m-1] Tc)

Затем сигналы SJ(t) и SQ(t) в когерентном интеграторе 2 подвергаются согласованной фильтрации в соответствующих корреляторах. В процессе корреляционной обработки в когерентном интеграторе 2 вычисляется взаимная корреляционная функция между отсчетами входных сигналов SJ(t), SQ(t) и бинарной последовательностью опорного ПС-кода.

Блоки, участвующие в корреляционной обработке синфазного сигнала (блоки 5, 11, 13 и 15) и квадратурного сигнала (блоки 5, 11, 14 и 16) по структуре идентичны и во времени работают синхронно. В связи с этим их функционирование можно описать на примере обработки ("свертки") синфазного сигнала.

Синфазная SJ(t) составляющая сигнала Sω (t) в аналоговой форме поступает на сигнальный вход запоминающего блока 13 на переключающих конденсаторах, где этот сигнал с тактовой частотой 1/2 fопдискретизируется и запоминается в виде зарядовых пакетов в соответствующих емкостях.

На выходах распределителя 5 селекторных стробов формируются адресные стробы, которые поступают последовательно во времени на входы запоминающего блока 13. Работа распределителя 5 синхронизируется под воздействием тактовых сигналов, поступающих с выхода генератора 7 на его С-вход.

Под воздействием стробов происходит последовательный заряд соответствующих запоминающих емкостей в запоминающем блоке 13, т. е. используется принцип памяти дискретных значений сигнала с последовательной адресацией. При этом через период МТс все М аналоговых величин дискретизированных сигналов с помощью усилителей с неразрушающим считыванием поступают на выходы запоминающего блока 13.

Эти сигналы далее поступают на группу входов блока интегрирования 15 синфазного сигнала, на другую группу входов которого поступают текущие данные опорного ПС-кода с выходов регистра сдвига 11 с весами ± 1. Таким образом "загрузка" каждой конкретной ячейки памяти запоминающего блока 13 на коммутируемых конденсаторах происходит последовательно во времени один раз за период Т = МТс.

Управляется процесс загрузки сигналами от распределителя 5 селекторных стробов. При этом последовательно включаются ячейки памяти, куда вводятся соответствующие значения зарядов и хранятся эти заряды в течение периода Т = МТс. В блоке интегрирования 15 в каждом элементарном интервале Тс все М считанных зарядов (копий) соответствующих ячеек перемешиваются под воздействием управляющих двоичных сигналов опорного ПС-кода, поступающего по М шинам с выходов регистра сдвига 11. Вводится опорный ПС-код в регистр сдвига 11 последовательно с выхода формирователя 6 опорного кода. Отсчеты входного сигнала SJ(t) записываются в запоминающем блоке 13 также последовательно в прямом направлении (первый отсчет - в первую ячейку, второй - во вторую и т. д. ) В этой связи для упрощения процесса определения временного положения принимаемого сигнала относительно опорного ПС-кода последний представляют в обращенном виде, когда в последовательности символов опорного ПС-кода формируется первым символом М-го значения, а последним - символ 1-го значения. Например, если прямая последовательность ПС-кода описывается полиномом вида

Gп= 1+x5+x9, то в обращенном виде этот полином описывает выражение

Gоб= 1+x4+x9, т. е. для m последовательности обращенный ПС-код рассчитывается по правилу: из числа разрядов последнего члена полинома вычитается предпоследний член. В данном случае 9-5 = 4, следовательно Х5 заменяют на член Х4 и т. д.

Таким образом в запоминающем блоке 13 нет передачи зарядов от ячейки к ячейке и, следовательно, нет большого рассеяния полезного сигнала.

По аналогии параллельно во времени работает коррелятор квадратурного канала (блоки 5, 6, 14 и 16).

Поэлементно "взвешенные" на положительных и отрицательных суммирующих шинах сигналы в блоке интегрирования 15 поступают на устройство суммирования, на выходе которого формируются в каждом периоде Тс опорного ПС-кода суммарные сигналы положительной или отрицательной полярности.

Эти сигналы с выходов блоков интегрирования 15 и 16 поступают на соответствующие входы блока амплитудного детектирования 12. Эти сигналы преобразуются в однополярные сигналы поэлементной свертки синфазной RJ(nTc) и квадратурной RQ(nTc) составляющих и на выходе блока амплитудного детектирования формируется результирующий сигнал поэлементной свертки, который описывается выражением

y(t)=  C

C x*(t-[k-1] Tc), где X*(t) - квадратурный сигнал, образованный из суммы RJ(nTc) и RQ(nTc).

x*(t-[k-1] Tc), где X*(t) - квадратурный сигнал, образованный из суммы RJ(nTc) и RQ(nTc).

Сигналы поэлементной свертки y(t) с периодом МТс с выхода блока амплитудного детектирования, являющегося выходом когерентного интегратора 2, поступают на сигнальные входы накопителя 3 и дополнительного накопителя 9, которые работают поочередно через период МТс в двух режимах, например в нечетных (на соответствующем выходе формирователя 8 - единичный сигнал) периодах Т = МТс дополнительный накопитель 9 работает в режиме "последовательное суммирование - запись - считывание", а накопитель 3 в этот период работает в режиме "последовательное считывание". В четные периоды дополнительный накопитель 9 работает в режиме "последовательное считывание", а накопитель 3 - в режиме "последовательное суммирование - запись - считывание". После окончания режима накопления через t = r МТс оба накопителя 3 и 9 переводятся в исходное состояние.

Процесс накопления начинается в момент tо. Пусть в момент t2единичный уровень с прямого выхода и нулевой уровень с инверсного выхода формирователя 8 поступают на входы "Разрешение записи" накопителей 3 и 9. При этом в накопителе 9 коммутатор 17 подключает выход сумматора 18 к шине ввод-вывод блока ключей 21, а в накопителе 3 в этот момент выход коммутатора 17 отключен от шины ввод-вывод блока ключей 21. В этом режиме последовательно во времени на управляющие входы блока ключей 21 накопителей 3 и 9 поступают М селекторных стробов, под воздействием которых одновременно срабатывают ключи одного номера в накопителях 3 и 9 и подключают соответствующие конденсаторы блока запоминающих конденсаторов 20 к шине ввод-вывод.

Поскольку в накопителе 3 коммутатор 17 разомкнут, то сигнал с i-го конденсатора блока запоминающих конденсаторов 20 поступает на вход усилителя 22 неразрушающего считывания, с выхода которого сигнал передается по цепи обратной связи на второй сигнальный вход накопителя 3, а в нем - на вход сумматора 18, в котором происходит суммирование текущего сигнала Yi,j(t) когерентного интегратора 2 и результирующего сигнала  (t), накопленного в предыдущих j-1 периодах МТс j = 1,2, . . . , j-1. На выходе сумматора 18 в j-ом периоде МТс формируется результирующий сигнал поэлементной свертки

(t), накопленного в предыдущих j-1 периодах МТс j = 1,2, . . . , j-1. На выходе сумматора 18 в j-ом периоде МТс формируется результирующий сигнал поэлементной свертки  (t).

(t).

Сумматор 18 имеет малое выходное сопротивление, например на его выходе подключен эмиттерный повторитель. Поэтому величина заряда на i-ом конденсаторе блока запоминающих конденсаторов 20 будет с высокой точностью повторять сигнал на выходе сумматора 18. В следующем четном периоде МТс переводится в режим "последовательное считывание" накопитель 9, а накопитель 3 переключается в режим "последовательное суммирование - считывание - запись". При этом в накопителе 3 на соответствующем i-ом конденсаторе запоминается результирующий сигнал

yi,j+1+ (t)=

(t)=  (t)

(t)

Таким образом циклы записи и считывания повторяются r раз. Результирующие М сигналов  (t) считываются из накопителя 3 (в принципе из любого) путем последовательной во времени передачи результирующих

(t) считываются из накопителя 3 (в принципе из любого) путем последовательной во времени передачи результирующих  (t) сигналов на сигнальный вход компаратора 4. Сигналы

(t) сигналов на сигнальный вход компаратора 4. Сигналы  (t) поэлементно с периодом Тс сравниваются с пороговыми значениями сигналов, поступающих извне на второй вход компаратора 4. Пороговые значения сигналов обычно соответствуют требуемым вероятностям правильного обнаружения и ложной тревоги. Через период Т = Тс Мr на выходе компаратора 4 формируется в цифровом виде двоичный код числа, определяющий временное положение ПС-кода входного сигнала относительно опорного ПС-кода данного устройства. Компаратор 4 устанавливается в исходное состояние фронтом импульса, формируемого на втором выходе генератора 7.

(t) поэлементно с периодом Тс сравниваются с пороговыми значениями сигналов, поступающих извне на второй вход компаратора 4. Пороговые значения сигналов обычно соответствуют требуемым вероятностям правильного обнаружения и ложной тревоги. Через период Т = Тс Мr на выходе компаратора 4 формируется в цифровом виде двоичный код числа, определяющий временное положение ПС-кода входного сигнала относительно опорного ПС-кода данного устройства. Компаратор 4 устанавливается в исходное состояние фронтом импульса, формируемого на втором выходе генератора 7.

Данные о параметрах опорного кода вводятся из блока управления и запоминаются в формирователе 6, на синхронизирующий вход которого поступают импульсы с выхода генератора 7, под воздействием которых осуществляется формирование опорного ПС-кода. В момент t2 формирователь 6 устанавливается в исходное состояние и на его выходе формируется 1-й символ обращенного ПС-кода, который характеризуется тем, что на его первой позиции формируется последний М-й символ опорного ПС-кода, затем через период Тс на второй позиции формируется значение (М-1)-го символа и т. д. На последней М-й позиции формируется 1-й символ опорного ПС-кода. При изменении вида опорного ПС-кода на информационный вход формирователя в цифровой форме поступает сигнал, который запоминается и коммутирует цепи обратной связи.

Блок управления 10 информацию о данных числа накопления r передает с выхода на вход формирователя 8, данные о разрядности М - на вход генератора 7, данные о виде обратных связей опорного ПС-кода - на вход формирователя 6 опорного кода.

Использование: в радиотехнике, в частности в широкополосных системах спутниковой связи и навигации. Сущность изобретения: устройство поиска псевдошумовых сигналов содержит синхронный детектор, когерентный интегратор, накопитель, компаратор, распределитель селекторных стробов, формирователь опорного кода, генератор тактовых импульсов, формирователь селекторных стробов, дополнительный накопитель и блок управления. Цель изобретения - сокращение времени поиска псевдошумовых радиосигналов. 1 з. п. ф-лы, 2 ил.

Авторы

Даты

1994-04-30—Публикация

1990-06-25—Подача