Изобретение относится к автоматике и цифровой вычислительной технике и может найти применение при построении управляющих и вычислительных систем высокой производительности, в том числе систем с массовым параллелизмом, а также подсистем дискретного управления многоуровневых интеллектуальных автоматизированных систем управления (АСУ) технологическими и робототехническими комплексами, где требуется точное согласование моментов инициализации и завершения асинхронно протекающих процессов.

Известно микропрограммное устройство управления, содержащее блок постоянной памяти, блок формирования адреса микрокоманд, регистр адреса следующей микрокоманды, регистр микроопераций, регистр формата микрокоманды, регистр начала микропрограмм, регистр состояния параллельных участков, триггер управления, генератор импульсов, элемент ИЛИ, блок элементов ИЛИ, первый и второй элементы И, первый и второй блоки элементов И, группу элементов И, одновибратор, первый, второй и третий элементы задержки (а. с. СССР N 1647566, кл. G 06 F 9/22, опубл. 07.05.91, БИ N 17).

Недостатком данного устройства является значительное число внешних выводов, используемых для организации взаимодействия с другими аналогичными устройствами (приема и выдачи адресов передачи управления), и, как следствие, резко ограниченная наращиваемость формируемых на его основе управляющих систем и, соответственно, узкая область применения устройства.

Наиболее близким к предлагаемому устройству по технической сущности является микропрограммное устройство для управления обменом управляющей информации в распределенной системе, включающее блок памяти микропрограмм, регистры адреса, микрокоманд и приема, буферный запоминающий блок, блок регистров, коммутаторы адреса, выходной и микрокоманд, генератор констант, схему сравнения, мультиплексор логических условий, генератор тактовых импульсов, триггер запуска, элемент задержки, с первого по третий элементы И, первый и второй блоки элементов И, с первого по четвертый элементы ИЛИ и одновибратор (а.с СССР, N 1325477 кл. G 06 F 9/22, опубл. 23.07.87, БИ N 27).

Недостатком указанного устройства является узкая область применения, обусловленная отсутствием средств синхронизации завершения параллельных ветвей (участков) микропрограмм, закрепленных за различными модулями управляющих систем, формируемых на его основе. Отсутствие возможности синхронизации завершения параллельных участков может привести к возникновению некорректных режимов функционирования, например, к одновременному (параллельному) выполнению несовместимых операций при реализации параллельных алгоритмов управления.

Технической задачей изобретения является расширение области применения устройства на основе организации возможности синхронизации завершения произвольных групп параллельных участков микропрограмм.

Техническая задача решается тем, что модуль микроконтроллерной сети, содержащий блок памяти микропрограмм, регистры адреса и микрокоманд, мультиплексор логических условий, генератор констант, триггер запуска, первую схему сравнения, первый генератор тактовых импульсов, первый буферный запоминающий блок, коммутатор адреса, первый выходной коммутатор, с первого по третий элементы И, с первого по четвертый элементы ИЛИ, первый элемент задержки и первый одновибратор, причем вход генератора констант является входом настройки модуля, а выход соединен с первым входом первой схемы сравнения, выход первого выходного коммутатора соединен с выходом управления синхронизацией модуля, выход первого элемента ИЛИ подключен к первому входу первого элемента И, выход второго элемента ИЛИ соединен с входом установки триггера запуска, прямой выход которого соединен с входом первого генератора тактовых импульсов, первый выход которого соединен с входом синхронизации регистра адреса, а второй выход подключен к входу синхронизации регистра микрокоманд, выходы кода логического условия и модифицируемого разряда адреса которого подключены к адресному и первому информационному входам мультиплексора логических условий соответственно, второй информационный вход которого является входом логических условий модуля, выход мультиплексора логических условий в объединении с выходом немодифицируемой части адреса регистра микрокоманд соединен с первым информационным входом коммутатора адреса, выход которого подключен к информационному входу регистра адреса, выход которого соединен с адресным входом блока памяти микропрограмм, выход которого соединен с информационным входом регистра микрокоманд, выход метки конца операции которого подключен к первому и второму управляющим входам коммутатора адреса, дополнительно включает второй буферный запоминающий блок, второй генератор тактовых импульсов, вторую схему сравнения, регистр-счетчик событий, второй выходной коммутатор, триггеры переключения каналов, управления синхронизацией и блокировки, триггер, с четвертого по четырнадцатый элементы И, с пятого по седьмой элементы ИЛИ, элемент ИЛИ-НЕ, второй и третий одновибраторы, с второго по пятый элементы задержки, причем выход метки управления синхронизацией регистра микрокоманд соединен с первыми входами второго и третьего элементов И и с первым входом третьего элемента ИЛИ, выход которого подключен к первому входу четвертого элемента И, выход которого подключен к входу сброса триггера запуска, выход метки конца участка регистра микрокоманд соединен с первыми входами пятого и шестого элементов И, с третьим и четвертым управляющими входами коммутатора адреса, с вторым входом третьего элемента ИЛИ, с входом установки триггера блокировки, а также с первым входом четвертого элемента ИЛИ, выход которого подключен к пятому управляющему входу коммутатора адреса, второй информационный вход которого является входом кода операции модуля, выход метки передачи управления регистра микрокоманд соединен с третьим входом третьего элемента ИЛИ, с первым входом седьмого элемента И и с первым управляющим входом второго выходного коммутатора, выход которого в объединении с выходом пятого элемента ИЛИ образуют выход передачи управления модуля, выход управляющей информации регистра микрокоманд включает выход номера точки синхронизации и выход количества ожидаемых событий и подключен к первым информационным входам первого и второго выходных коммутаторов, выход номера точки синхронизации регистра микрокоманд соединен с первым входом второй схемы сравнения, выход которой подключен к второму входу шестого элемента И и к второму входу третьего элемента И, третий вход которого подключен к выходу элемента ИЛИ-НЕ, выход третьего элемента И соединен с первым (инверсным) входом восьмого элемента И и с первым входом девятого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом первого одновибратора, выход метки конца операции регистра микрокоманд соединен с выходом конца операции модуля, с четвертым входом третьего элемента ИЛИ, с вторым входом четвертого элемента ИЛИ и с вторым входом пятого элемента И, третий вход которого является входом пуска модуля, выход пятого элемента И соединен с третьим входом второго элемента ИЛИ, второй выход первого генератора тактовых импульсов подключен к входу второго одновибратора, выход которого подключен к второму входу четвертого элемента И и к второму входу второго элемента И, выход которого соединен с входом установки триггера управления синхронизацией, прямой выход которого подключен к первому управляющему входу первого выходного коммутатора, к первому входу десятого элемента И и к первому входу одиннадцатого элемента И, выход которого соединен с входом установки триггера, счетный вход которого подключен к инверсному выходу триггера управления синхронизацией, прямой выход триггера соединен с первым входом двенадцатого элемента И, выход которого подключен к входу сброса триггера управления синхронизацией, первый выход второго генератора тактовых импульсов подключен к второму входу седьмого элемента И, к второму входу одиннадцатого элемента И, к входу установки триггера переключения каналов и к второму входу десятого элемента И, выход которого соединен с первым входом шестого элемента ИЛИ, выход которого подключен к выходу управления синхронизацией модуля, второй выход второго генератора тактовых импульсов соединен с первым входом тринадцатого элемента И, с вторым входом двенадцатого элемента И, с входом сброса триггера переключения каналов и с вторым входом первого элемента И, выход которого подключен к второму входу шестого элемента ИЛИ и к входу первого элемента задержки, выход которого соединен с входами синхронизации сдвига и разрешения сдвига первого буферного запоминающего блока, выход которого соединен с вторым информационным входом первого выходного коммутатора и с входами первого элемента ИЛИ, выход которого подключен к второму управляющему входу первого выходного коммутатора, третий и четвертый управляющие входы которого соединены с инверсным и прямым выходами триггера переключения каналов соответственно, вход управления синхронизацией модуля образован входом номера точки синхронизации, входом количества ожидаемых событий и линией синхронизации, вход номера точки синхронизации модуля соединен с вторым входом второй схемы сравнения и в объединении с выходом регистра-счетчика событий подключен к информационному входу первого буферного запоминающего блока, вход синхронизации записи которого соединен с выходом восьмого элемента И, вход количества ожидаемых событий модуля соединен с входами элемента ИЛИ-НЕ и с информационным входом регистра-счетчика событий, линия синхронизации входа управления синхронизацией модуля подключена к входу второго элемента задержки, выход которого подключен к входу синхронизации регистра-счетчика событий, к второму входу девятого элемента И и к входу третьего одновибратора, выход которого соединен с вторым (прямым) входом восьмого элемента И и с третьим входом шестого элемента И, четвертый вход которого соединен с прямым выходом триггера блокировки, выход шестого элемента И подключен к счетным входам триггера блокировки и регистра-счетчика событий, прямой и инверсный выходы триггера переключения каналов соединены соответственно с вторым и третьим управляющими входами второго выходного коммутатора, вход приема управления модуля образован входом номера модуля, входом адреса приема управления и линией синхронизации, вход адреса приема управления модуля соединен с третьим информационным входом коммутатора адреса и в объединении с входом номера модуля устройства подключен к информационному входу второго буферного запоминающего блока, выход которого подключен к второму информационному входу второго выходного коммутатора и к входам седьмого элемента ИЛИ, выход которого соединен с четвертым управляющим входом второго выходного коммутатора и с вторым входом тринадцатого элемента И, выход которого подключен к первому входу пятого элемента ИЛИ и к входу третьего элемента задержки, выход которого соединен с входами синхронизации сдвига и разрешения сдвига второго буферного запоминающего блока, вход синхронизации записи которого подключен к выходу четырнадцатого элемента И, первый (прямой) вход которого соединен с выходом четвертого элемента задержки, вход которого соединен с линией синхронизации входа приема управления модуля, вход номера модуля устройства подключен к второму входу первой схемы сравнения, выход которой соединен с вторым (инверсным) входом четырнадцатого элемента И, с входом первого одновибратора, а также с шестым управляющим входом коммутатора адреса, выход седьмого элемента И подключен к второму входу пятого элемента ИЛИ и к входу пятого элемента задержки, выход которого соединен с четвертым входом второго элемента ИЛИ, выход микроопераций регистра микрокоманд является выходом микроопераций модуля.

Сущность предлагаемого изобретения состоит в следующем.

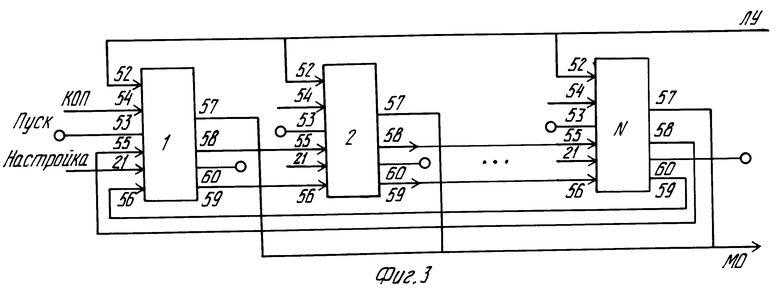

Предлагаемое устройство совместно с другими идентичными устройствами (модулями) объединяется в кольцевую структуру, называемую микроконтроллерной сетью (МКС) и предназначенную для управления сложными объектами (комплексами взаимосвязанных объектов), предполагающими параллельное и асинхронное протекание во времени множества процессов (например, коллективами процессорных элементов в многопроцессорных вычислительных системах).

Каждый модуль МКС выполняется в виде СБИС с внутренней перепрограммируемой памятью микропрограмм и обеспечивает возможности: управления последовательным процессом, инициализации процессов в других аналогичных устройствах, а также синхронизации их завершения путем передачи специальных управляющих микрокоманд (сообщений). Для идентификации различных модулей МКС им присваиваются логические номера 1,2,...,N. Тип (номер) выполняемой операции определяется кодом операции (КОП), который представляет собой адрес первой микрокоманды начального участка соответствующей микропрограммы и формируется устройством управления верхнего уровня (УУВУ), например, центральным процессором.

При управлении параллельными или последовательными процессами модули МКС вырабатывают последовательности микрокоманд, порядок следования которых задается значениями сигналов логических условий, поступающих от объекта управления (снимаемых с соответствующих датчиков или вырабатываемых специальными схемами формирования признаков). В процессе реализации участков микропрограмм модули сети могут инициировать выполнение участков микропрограмм другими модулями путем передачи этим модулям соответствующих начальных адресов.

Инициализация параллельных или последовательных участков микропрограмм (передача управления) осуществляется следующим образом.

Модуль Мi формирует управляющую микрокоманду S, которая включает номер инициализируемого модуля k и соответствующий начальный адрес (адрес инициализации) Апу. Микрокоманда S передается модулю Мi+1, где подвергается анализу, который заключается в сопоставлении номера приемника сообщения k с номером данного модуля (i+1), Если указанные номера совпадают, то модуль Мi+1 начинает выполнение участка микропрограммы с поступившего адреса Апу иначе микрокоманда S транслируется на выход модуля Мi+1 и передается следующему модулю МКС Мi+2, где вновь подвергается анализу. Аналогично микрокоманда S передается следующему в кольцевой структуре сети модулю и ретранслируется вплоть до совпадения номера k с номером одного из модулей МКС,

Для реализации режима синхронизации завершения группы P параллельных участков микропрограмм, закрепленных за модулями  ,

,  , одному из перечисленных модулей присваивается статус ведущего (например, ведущим считается модуль

, одному из перечисленных модулей присваивается статус ведущего (например, ведущим считается модуль  , остальные рассматриваются как ведомые. В качестве ключевой информации при синхронизации параллельных участков используется номер точки (вершины) слияния (синхронизации) этих участков Tr, а также число участков Wr0 (количество ожидаемых событий), завершающихся в точке Tr.

, остальные рассматриваются как ведомые. В качестве ключевой информации при синхронизации параллельных участков используется номер точки (вершины) слияния (синхронизации) этих участков Tr, а также число участков Wr0 (количество ожидаемых событий), завершающихся в точке Tr.

Ведущий модуль Mq, завершая выполнение соответствующего участка микропрограммы, переходит в режим управления синхронизацией, а остальные (ведомые) модули - в состояние активного ожидания. В режиме управления синхронизацией модуль Mq вырабатывает управляющую микрокоманду Zr, содержащую номер точки слияния Tr и количество ожидаемых событий Wr=Wr0-1 (параллельный участок, выполняемый модулем Mq, не учитывается). Данная микрокоманда последовательно передается модулям Мq+1, Мq+2,..., Мj,... и по мере прохождения через каждый из указанных модулей подвергается анализу и, возможно, модификации. Если очередной модуль МКС Мj выполняет некоторый участок микропрограммы (и, соответственно, не находится в состоянии ожидания) или завершил реализацию параллельного участка в точке слияния Tf≠Tr, то микрокоманда Zr без изменений транслируется следующему модулю (Мj+1), в противном случае перед выдачей микрокоманды модулю Мj+1 количество ожидаемых событий Wr уменьшается на единицу. Аналогичным образом рассматриваемая микрокоманда проходит через все модули сети и, поскольку МКС обладает кольцевой структурой, появляется на входе ведущего модуля Мq.

Модуль Мq анализирует микрокоманды, поступающие на его вход, и при обнаружении микрокоманды Zr (возвращающейся на его вход по кольцу) осуществляет опрос состояния поля количества ожидаемых событий Wr. В случае, если для поступившей микрокоманды Zr, Wr > 0, т.е. среди контролируемых параллельных участков существуют незавершенные, модуль Мq продолжает функционировать в режиме управления синхронизацией и ретранслирует микрокоманду Zr на выход для реализации повторного опроса. Если для поступившей микрокоманды имеет место Wr= 0, т.е. все параллельные участки, сходящиеся к точке слияния Тr, завершены, то модуль Mq выходит из режима управления синхронизацией и возобновляет выполнение закрепленного за ним участка микропрограммы. Ведомые модули впоследствии выходят из состояния ожидания по мере поступления на их входы управляющих микрокоманд передачи управления S.

Для обеспечения приемлемого быстродействия МКС передача управляющих микрокоманд типа S (передачи управления) и типа Z (управления синхронизацией) производится по различным - независимым и параллельно функционирующим - каналам.

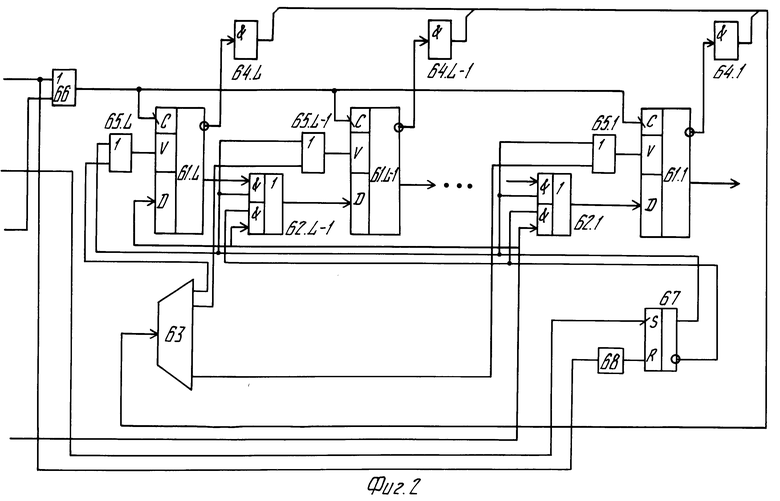

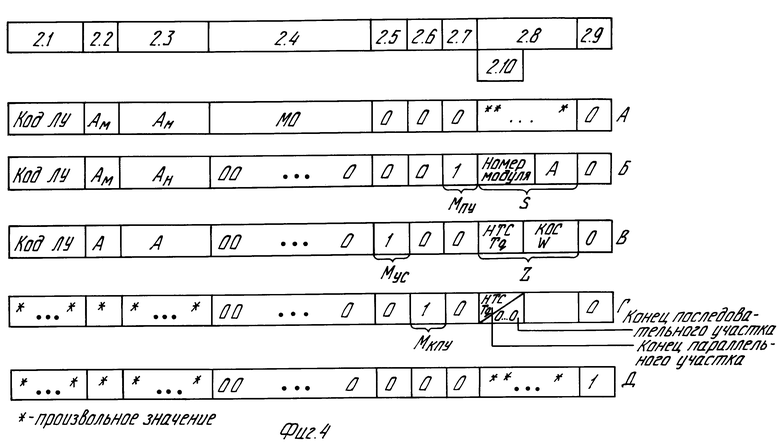

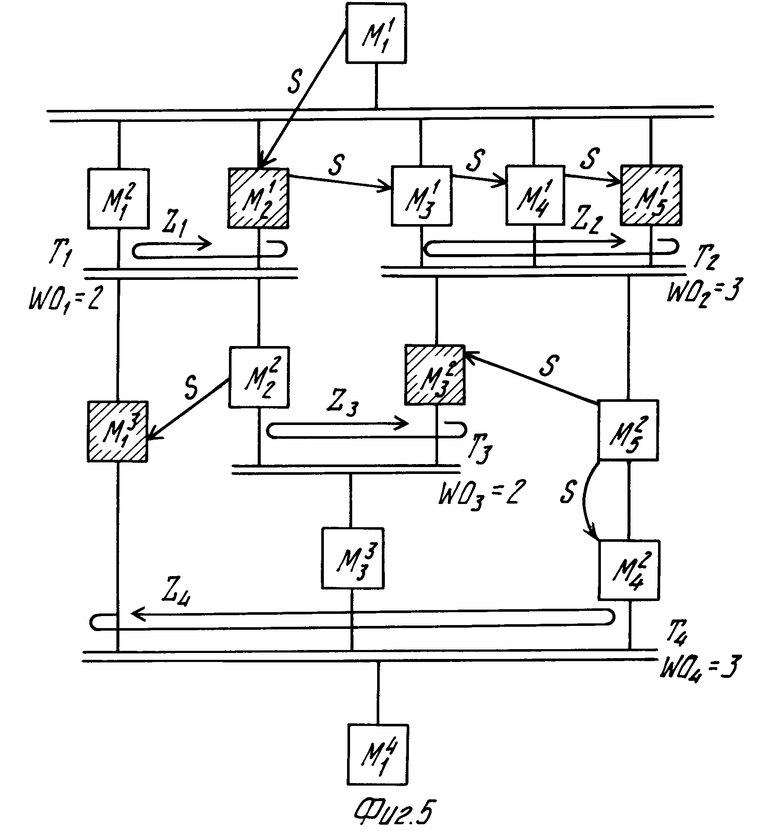

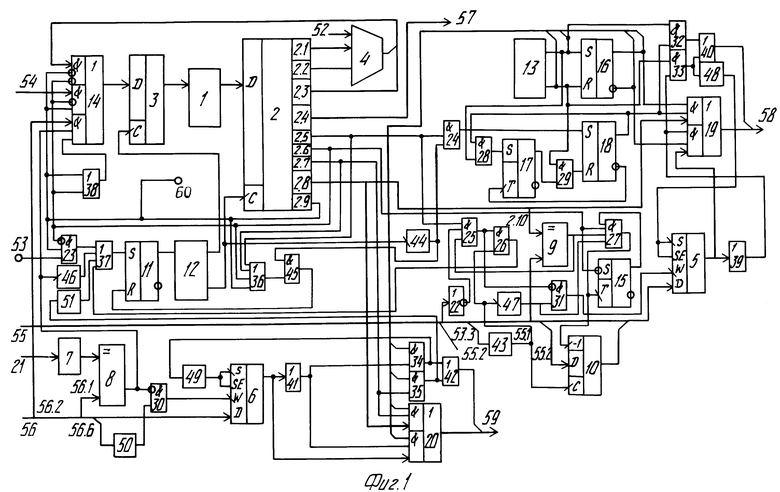

Сущность предлагаемого изобретения поясняется чертежами, где на фиг. 1 представлена функциональная схема модуля микроконтроллерной сети, на фиг. 2 - функциональная схема буферного запоминающего блока, на фиг. 3 - структурная схема кольцевой микроконтроллерной сети, на фиг. 4 - форматы микрокоманд, реализуемых устройством, а на фиг. 5 дан пример реализации параллельного алгоритма управления микроконтроллерной сетью, состоящей из пяти однотипных устройств.

Модуль микроконтроллерной сети (фиг. 1) содержит блок 1 памяти микропрограмм, регистр 2 микрокоманд, регистр 3 адреса, мультиплексор 4 логических условий, первый буферный запоминающий блок 5, генератор 7 констант, первую схему 8 сравнения, триггер 11 запуска, первый генератор 12 тактовых импульсов, коммутатор 14 адреса, первый выходной коммутатор 19, второй 24, третий 25 и первый 33 элементы И, третий 36, второй 37, четвертый 38 и первый 39 элементы ИЛИ, первый одновибратор 46 и первый элемент 48 задержки, причем вход генератора 7 констант является входом 21 настройки модуля, а выход соединен с первым входом схемы 8 сравнения, выход коммутатора 19 соединен с выходом 58 управления синхронизацией модуля, выход элемента ИЛИ 39 подключен к первому входу элемента И 33, выход элемента ИЛИ 37 соединен с входом установки триггера 11 запуска, прямой выход которого соединен с входом генератора 12 тактовых импульсов, первый выход которого соединен с входом синхронизации регистра 3 адреса, а второй выход подключен к входу синхронизации регистра 2 микрокоманд, выходы 2.1 кода логического условия (ЛУ) и 2.2 модифицируемого разряда адреса (Ам) которого подключены к адресному и первому информационному входам мультиплексора 4 логических условий соответственно, второй информационный вход которого является входом 52 логических условий модуля, выход мультиплексора 4 логических условий в объединении с выходом 2,3 немодифицируемой части адреса (Ан) регистра 2 микрокоманд соединен с первым информационным входом коммутатора 14 адреса, выход которого подключен к информационному входу регистра 3 адреса, выход которого соединен с адресным входом блока 1 памяти микропрограмм, выход которого соединен с информационным входом регистра 2 микрокоманд, выход 2,9 метки конца операции которого подключен к первому и второму управляющим входам коммутатора 14 адреса, а также дополнительное включенные второй буферный запоминающий блок 6, вторую схему 9 сравнения, регистр-счетчик 10 событий, второй генератор 13 тактовых импульсов, триггеры 15 блокировки и 16 переключения каналов, триггер 17, триггер 18 управления синхронизацией, второй выходной коммутатор 20, элемент ИЛИ-НЕ 22, пятый 23, девятый 26, шестой 27, одиннадцатый 28, двенадцатый 29, четырнадцатый 30, восьмой 31, десятый 32, тринадцатый 34, седьмой 35 и четвертый 45 элементы И, шестой 40, седьмой 41 и пятый 42 элементы ИЛИ, второй 44 и третий 47 одновибраторы, второй 43, третий 49, четвертый 50 и пятый 51 элементы задержки, причем выход 2.5 метки управления синхронизацией регистра 2 микрокоманд соединен с первыми входами элементов И 24, 25 и с первым входом элемента ИЛИ 36, выход которого подключен к первому входу элемента И 45, выход которого подключен к входу сброса триггера 11 запуска, выход 2.6 метки конца участка регистра 2 микрокоманд соединен с первыми входами элементов И 23, 27, с третьим и четвертым управляющими входами коммутатора 14 адреса, с вторым входом элемента ИЛИ 36, с входом установки триггера 15 блокировки, а также с первым входом элемента ИЛИ 38, выход которого подключен к пятому управляющему входу коммутатора 14 адреса, второй информационный вход которого является входом 54 кода операции модуля, выход 2.7 метки передачи управления регистра 2 микрокоманд соединен с третьим входом элемента ИЛИ 36, с первым входом элемента И 35 и с первым управляющим входом коммутатора 20, выход которого в объединении с выходом элемента ИЛИ 42 образуют выход 59 передачи управления модуля, выход 2.8 управляющей информации регистра 2 микрокоманд включает выход 2.10 номера точки синхронизации и выход количества ожидаемых событий и подключен к первым информационным входам выходных коммутаторов 19, 20, выход 2.10 номера точки синхронизации регистра 2 микрокоманд соединен с первым входом схемы 9 сравнения, выход которой подключен к второму входу элемента И 27 и к второму входу элемента И 25, третий вход которого подключен к выходу элемента ИЛИ-НЕ 22, выход элемента И 25 соединен с первым (инверсным) входом элемента И 31 и с первым входом элемента И 26, выход которого подключен к первому входу элемента ИЛИ 37, второй вход которого соединен с выходом одновибратора 46, выход 2,9 метки конца операции регистра 2 микрокоманд соединен с выходом 60 конца операции модуля, с четвертым входом элемента ИЛИ 36, с вторым входом элемента ИЛИ 38 и с вторым входом элемента И 23, третий вход которого является входом 53 пуска модуля, выход элемента И 23 соединен с третьим входом элемента ИЛИ 37, второй выход генератора 12 тактовых импульсов подключен к входу одновибратора 44, выход которого подключен к второму входу элемента И 45 и к второму входу элемента И 24, выход которого соединен с входом установки триггера 18 управления синхронизацией, прямой выход которого подключен к первому управляющему входу коммутатора 19, к первому входу элемента И 32 и к первому входу элемента И 28, выход которого соединен с входом установки триггера 17, счетный вход которого подключен к инверсному выходу триггера 18 управления синхронизацией, прямой выход триггера 17 соединен с первым входом элемента И 29, выход которого подключен к входу сброса триггера 18 управления синхронизацией, первый выход генератора 13 тактовых импульсов подключен к второму входу элемента И 35, к второму входу элемента И 28, к входу установки триггера 16 переключения каналов и к второму входу элемента И 32, выход которого соединен с первым входом элемента ИЛИ 40, выход которого подключен к выходу 58 управления синхронизацией модуля, второй выход генератора 13 тактовых импульсов соединен с первым входом элемента И 34, с вторым входом элемента И 29, с входом сброса триггера 16 переключения каналов и с вторым входом элемента И 33, выход которого подключен к второму входу элемента ИЛИ 40 и к входу элемента 48 задержки, выход которого соединен с входами синхронизации сдвига (S) и разрешения сдвига (SE) буферного запоминающего блока 5, выход которого соединен с вторым информационным входом коммутатора 19 и с входами элемента ИЛИ 39, выход которого подключен к второму управляющему входу коммутатора 19, третий и четвертый управляющие входы которого соединены с инверсным и прямым выходами триггера 16 переключения каналов соответственно, вход 55 управления синхронизацией модуля образован входом 55.1 номера точки синхронизации, входом 55.2 количества ожидаемых событий и линией 55.3 синхронизации, вход 55.1 номера точки синхронизации модуля соединен с вторым входом схемы 9 сравнения и в объединении с выходом регистра-счетчика 10 событий подключен к информационному входу буферного запоминающего блока 5, вход синхронизации записи (W) которого соединен с выходом элемента И 31, вход 55.2 количества ожидаемых событий модуля соединен с входами элемента ИЛИ-НЕ 22 и с информационным входом регистра-счетчика 10 событий, линия 55.3 синхронизации входа 55 управления синхронизацией модуля подключена к входу элемента 43 задержки, выход которого подключен к входу синхронизации регистра-счетчика 10 событий, к второму входу элемента И 26 и к входу одновибратора 47, выход которого соединен с вторым (прямым) входом элемента И 31 и с третьим входом элемента И 27, четвертый вход которого соединен с прямым выходом триггера 15 блокировки, выход элемента И 27 подключен к счетным входам триггера 15 блокировки и регистра-счетчика 10 событий, прямой и инверсный выходы триггера 16 переключения каналов соединены соответственно с вторым и третьим управляющими входами коммутатора 20, вход 56 приема управления модуля образован входом 56.1 номера модуля, входом 56.2 адреса приема управления и линией 56.3 синхронизации, вход 56.2 адреса приема управления модуля соединен с третьим информационным входом коммутатора 14 адреса и в объединении с входом 56.1 номера модуля устройства подключен к информационному входу буферного запоминающего блока 6, выход которого подключен к второму информационному входу коммутатора 20 и к входам элемента ИЛИ 41, выход которого соединен с четвертым управляющим входом коммутатора 20 и с вторым входом элемента И 34, выход которого подключен к первому входу элемента ИЛИ 42 и к входу элемента 49 задержки, выход которого соединен с входами синхронизации сдвига (S) и разрешения сдвига (SE) буферного запоминающего блока 6, вход синхронизации записи (W) которого подключен к выходу элемента И 30, первый (прямой) вход которого соединен с выходом элемента 50 задержки, вход которого соединен с линией 56.3 синхронизации входа 56 приема управления модуля, вход 56.1 номера модуля устройства подключен к второму входу схемы 8 сравнения, выход которой соединен с вторым (инверсным) входом элемента И 30, с входом одновибратора 46, а также с шестым управляющим входом коммутатора 14 адреса, выход элемента И 35 подключен к второму входу элемента ИЛИ 42 и к входу элемента 51 задержки, выход которого соединен с четвертым входом элемента ИЛИ 37, выход 2.4 микроопераций (МО) регистра 2 микрокоманд является выходом 57 микроопераций модуля.

Буферный запоминающий блок 5 (6) (фиг. 2) предназначен для приема, временного хранения и выдачи управляющих сообщений (микрокоманд) типа Z (S) в порядке поступления и содержит группу регистров 61.1-61.L (где L - максимальная длина очереди сообщений в блоке), группу коммутаторов 62.1-62.L-1, дешифратор 63, группу элементов И 64.1-64.L, группу элементов ИЛИ 65.1-65.L, элемент ИЛИ 66, триггер 67 и элемент 68 задержки, причем вход синхронизации сдвига (S) блока подключен к входу элемента 68 задержки, выход которого соединен с входом сброса триггера 67, вход синхронизации сдвига блока подключен к первому входу элемента ИЛИ 66, второй вход которого подключен к входу синхронизации записи (W) блока, выход элемента ИЛИ 66 подключен к входам синхронизации регистров 61.1-61.L, инверсные выходы которых подключены к входам элементов И 64.1-64. L соответственно, выходы которых соединены с входом дешифратора 63, выходы с первого по L-й которого подключены к первым входам элементов ИЛИ 65.1-65.L соответственно, выходы которых подключены к входам разрешения (V-входам) регистров 61.1-61. L соответственно, прямые выходы регистров 61.2-61.L соединены с первыми информационными входами коммутаторов 62.1-62. L-1 соответственно, а прямой выход регистра 61.1 является выходом блока, вход разрешения сдвига (SE) которого соединен с входом установки триггера 67, прямой выход которого подключен к первым управляющим входам коммутаторов 62.1-62.L-1 и к вторым входам элементов ИЛИ 65.1-65.L, инверсный выход триггера 67 соединен с вторыми управляющими входами коммутаторов 62.1-62. L-1, вторые информационные входы которых и информационный вход регистра 61.L соединены с информационным входом (D) блока, выходы коммутаторов 62.1-62.L-1 соединены с информационными входами регистров 61.1-61.L-1 соответственно.

Блок 1 памяти микропрограмм предназначен для постоянного хранения и выдачи микрокоманд, входящих в различные участки микропрограмм, закрепленные за текущим модулем.

Регистр 2 микрокоманд служит для приема и фиксации микрокоманд, считываемых из блока 1 памяти микропрограмм, на время их обработки, а регистр 3 адреса - для фиксации исполнительного адреса следующей микрокоманды реализуемого участка микропрограммы, кода очередной операции или адреса приема управления.

Мультиплексор 4 логических условий предназначен для опроса значений логических условий, образующихся на входе 52 логических условий модуля, и модификации значения младшего разряда адреса следующей микрокоманды в точках ветвления микропрограмм.

Генератор 7 констант предназначен для формирования кода логического номера (идентификатора) модуля.

Схема 8 сравнения служит для сравнения кода логического номера текущего модуля с кодами приемников управляющих микрокоманд типа S и формирования сигнала приема/ретрансляции, определяющего либо прием микрокоманды текущим модулем, либо транзитную передачу микрокоманды на выход 59 передачи управления модуля.

Схема 9 сравнения предназначена для сравнения кода номера точки синхронизации, соответствующей выполненному участку микропрограммы, с кодами номеров точек синхронизации микрокоманд типа Z, поступающих на вход 55 управления синхронизацией модуля, и используется как при функционировании модуля в режиме ведомого, так и при работе в режиме ведущего.

Регистр-счетчик 10 событий предназначен для временного хранения и модификации кодов количества ожидаемых событий микрокоманд управления синхронизацией Z при работе модуля в режиме ведомого.

Генератор 12 тактовых импульсов служит для формирования двух непересекающихся во времени импульсных последовательностей t1 и t2 синхронизирующих процесс считывания микрокоманд.

Генератор 13 тактовых импульсов служит для формирования двух сдвинутых друг относительно друга импульсных последовательностей П1 и П2, синхронизирующих процессы выдачи и приема управляющих микрокоманд S и Z (для обеспечения устойчивой работы устройства и исключения повторной выдачи микрокоманд типа S частоты следования тактовых импульсов F1 и F2, вырабатываемых соответственно генератором 12 и генератором 13, должны удовлетворять соотношению F1 > F2.

Коммутатор 14 адреса предназначен для передачи кода адреса следующей микрокоманды на информационный вход регистра 3 адреса с одного из трех возможных направлений: с выхода 2.3 регистра 2 микрокоманд и выхода мультиплексора 4 логических условий, с входа 54 кода операции или с входа 56 приема управления модуля.

Триггер 11 запуска предназначен для управления работой генератора 12.

Триггер 15 блокировки служит для блокировки процесса модификации кодов количества ожидаемых событий при многократном прохождении одних и тех же управляющих микрокоманд типа Z.

Коммутатор 19 обеспечивает передачу микрокоманд управления синхронизацией Z, формируемых текущим модулем, и микрокоманд Z, поступающих на вход 55 модуля, на единый выход 58 управления синхронизацией модуля.

Коммутатор 20 обеспечивает передачу микрокоманд типа S, формируемых текущим модулем, и микрокоманд типа S, поступающих с входа 56 приема управления модуля и фиксируемых в буферном запоминающем блоке 6, на единый выход 59 передачи управления модуля.

Триггер 16 переключения каналов используется для управления коммутаторами 19 и 20 (обеспечивает попеременную активизацию первых и вторых информационных входов коммутаторов 19 и 20).

Триггеры 17 и 18 в объединении с элементами И 24, 28, 29 и одновибратором 44 предназначены для управления процессом выдачи управляющих микрокоманд типа Z на выход 58 модуля.

Элемент ИЛИ-НЕ 22 служит для формирования сигнала, определяющего состояние поля количества ожидаемых событий микрокоманд Z, поступающих на вход 55 при работе модуля в режиме ведущего.

Элемент И 23, одновибратор 46, элемент И 35 и элемент И 26 служат для формирования сигналов запуска модуля соответственно при инициализации модуля со стороны УУВУ, при передаче управления от другого аналогичного модуля, при окончании процесса выдачи управляющих микрокоманд типа S и при завершении опрашиваемых модулем параллельных участков микропрограммы и совместно с элементом ИЛИ 37 предназначены для управления запуском генератора 12 (переключения в единичное состояние триггера 11 запуска).

Элемент И 25 служит для формирования сигнала, подтверждающего окончание требуемых параллельных участков микропрограммы,

Элемент И 27 служит для управления прохождением импульсов модификации кодов количества ожидаемых событий, вырабатываемых одновибратором 47, на счетный вход регистра-счетчика 10 событий и управления переключением триггера 15 блокировки.

Элементы И 30 и 31 предназначены для блокировки записи управляющих микрокоманд S и Z, поступающих соответственно с входов 56 и 55 модуля, в буферные запоминающие блоки 6 и 5 соответственно.

Группы, первая из которых образована элементами И 32, 33 и элементом ИЛИ 40, а вторая - элементами И 34, 35 и элементом ИЛИ 42, служат для управления выдачей импульсов синхронизации приема управляющих микрокоманд Z и S соответственно,

Элемент ИЛИ 36 совместно с элементом И 45 и одновибратором 44 используется для формирования сигнала отключения генератора 12 тактовых импульсов (сброса триггера 11 запуска).

Элемент ИЛИ 38 служит для формирования сигнала управления коммутатором 14 адреса при ожидании модулем передачи управления со стороны другого аналогичного устройства.

Элементы ИЛИ 39 и 41 служат для формирования сигналов, характеризующих состояния буферных запоминающих блоков 5 и 6 соответственно, а элементы задержки 48 и 49 - для задержки поступления импульсов сдвига очередей буферных запоминающих блоков 5 и 6 соответственно при выдаче сообщений на время приема сообщений следующим модулем МКС.

Элементы 50 и 43 задержки введены для согласования моментов появления импульсов синхронизации приема управляющих микрокоманд S и Z с моментами установления микрокоманд на входах 56 и 55 модуля соответственно, а элемент 51 задержки введен для задержки поступления импульса запуска модуля (после выдачи микрокоманды передачи управления S) на вход установки триггера 11 на время присутствия единичного уровня сигнала на его входе сброса.

Работу предлагаемого устройства поясним примером функционирования кольцевой микроконтроллерной сети (фиг. 3) при реализации параллельного алгоритма управления.

Учитывая идентичность модулей, образующих МКС, работу сети рассмотрим на примере функционирования одного из модулей, например, модуля Мi.

Первоначально регистры 61.1-61. L и триггеры 67 буферных запоминающих блоков 5 и 6 (фиг. 2), триггер 11 запуска (фиг. 1), триггеры 17 и 18 находятся в состоянии логического нуля, триггер 15 - в состоянии логической единицы, состояние регистра 3 адреса, регистра-счетчика 10 событий и триггера 16 не определено (произвольно), а все разряды регистра 2 микрокоманд, кроме разряда 2.9 метки конца операции (Мко), который установлен в единичное состояние, находятся в состоянии логического нуля, поэтому генератор 12 тактовых импульсов выключен, элемент И 23 открыт, коммутатор 14 адреса настроен на прием информации с входа 54 кода операции модуля, а на выходах элементов ИЛИ 39, 41 присутствуют сигналы логического нуля, индицирующие отсутствие управляющих сообщений в буферных запоминающих блоках 5 и 6 соответственно. Генератор 13 тактовых импульсов не имеет специального управляющего входа и поэтому постоянно вырабатывает две распределенные во времени последовательности синхроимпульсов П1 и П2; на выходе генератора 7 констант присутствует код логического номера модуля (цепи приведения элементов устройства в исходное состояние на фиг. 1 и 2 для упрощения условно не показаны),

Функционирование МКС начинается с момента подачи на вход 54 одного из ее модулей кода выполняемой операции. Код операции формируется УУВУ и поступает на вход 54 модуля, за которым закреплен начальный последовательный участок соответствующей микропрограммы, допустим, модуля Мi. Одновременно на вход 53 модуля подается импульс "Пуск". Код операции поступает на второй информационный вход коммутатора 14 адреса и, так как на его втором и четвертом управляющих входах присутствуют разрешающие сигналы (соответственно "1" и "О"), проходит на информационный вход регистра 3 адреса микрокоманды. Импульс "Пуск" проходит на выход элемента И 23, через элемент ИЛИ 37 передается на вход установки триггера 11 запуска и переключает его в единичное состояние. Единичный сигнал с прямого выхода триггера 11 поступает на вход генератора 12 и разрешает формирование на его выходах импульсных последовательностей t1 и t2.

По переднему фронту первого тактового импульса t1 с первого выхода генератора 12 код операции фиксируется в регистре 3 и поступает на адресный вход блока 1 памяти микропрограмм, на выходе которого через некоторое время появляется первая микрокоманда выполняемой микропрограммы. По переднему фронту импульса t2, поступающего на вход синхронизации регистра 2 с второго выхода генератора 12, считанная микрокоманда заносится в регистр 2 микрокоманд и появляется на его выходе, а задний фронт импульса t2 возбуждает импульс на выходе одновибратора 44. Дальнейший ход работы устройства определяется форматом считанной микрокоманды (фиг. 4).

Случай 1. Если считанная микрокоманда имеет формат А, то на выходах 2.5-2.7 и 2.9 регистра 2 микрокоманд устанавливается нулевой уровень сигнала, состояние выхода 2.8 становится неопределенным и, соответственно, на выходе элемента ИЛИ 36 формируется нулевой сигнал, а коммутатор 14 адреса настраивается на прием информации с его первого информационного входа. Нулевой сигнал с выхода элемента ИЛИ 36 блокирует элемент И 45, запрещая тем самым сброс триггера 11 запуска; нулевой сигнал с выхода 2.5 регистра 2 блокирует элементы И 24, 25; нулевой сигнал с выхода 2.6 регистра 2 подтверждает исходное (единичное) состояние триггера 15 и формирует нулевой уровень сигнала на выходе элемента И 27, а нулевой сигнал с выхода 2.7 регистра 2 обусловливает блокировку элемента И 35 и первого информационного входа коммутатора 20. Операционная часть микрокоманды с выхода 2.4 регистра 2 микрокоманд передается на выход 57 модуля для возбуждения требуемых микроопераций.

Одновременно осуществляется формирование исполнительного адреса следующей микрокоманды.

Код логического условия с выхода 2.1 и модифицируемый разряд адреса с выхода 2.2 регистра 2 микрокоманд поступают соответственно на адресный и первый информационный входы мультиплексора 4 логических условий. Если код опрашиваемого логического условия не является нулевым, то на выход мультиплексора 4 передается сигнал с соответствующего разряда входа 52 логических условий модуля, в противном случае (т.е. если код логического условия является нулевым) на выход мультиплексора 4 поступает исходное значение младшего разряда адреса с выхода 2.2 регистра 2. Таким образом, на выходе мультиплексора 4 образуется модифицированное значение младшего разряда адреса, которое в объединении с немодифицируемой (старшей) частью адреса с выхода 2.3 регистра 2 определяет исполнительный адрес следующей микрокоманды. Сформированный исполнительный адрес поступает на первый информационный вход коммутатора 14 адреса.

Так как на первом и третьем управляющих входах коммутатора 14 присутствуют нулевые сигналы, поступающие соответственно с выходов 2.9 и 2.6 регистра 2, исполнительный адрес следующей микрокоманды передается на информационный вход регистра 3 адреса. В момент появления на входе синхронизации регистра 3 очередного тактового импульса t1 адрес следующей микрокоманды заносится в регистр 3 и адресует блок 1 памяти микропрограмм, обеспечивая считывание очередной микрокоманды. Далее модуль приступает к выполнению считанной микрокоманды и функционирует аналогично ранее рассмотренному,

Случай 2. Если считанная микрокоманда имеет формат Б (фиг. 4), то модуль переходит в режим передачи управления другому аналогичному модулю МКС или инициализации параллельного участка микропрограммы. На выходах 2.4-2.6 и 2.9 регистра 2 микрокоманд устанавливается нулевой уровень сигнала, а на выходе 2.7 формируется единичный сигнал - метка передачи управления (Мпу). Номер модуля, которому передается управление (р), и адрес передачи управления (Апу) с выхода 2.8 управляющей информации регистра 2 микрокоманд (управляющая микрокоманда типа S) поступают на первый информационный вход коммутатора 20, а метка передачи управления подается на третий вход элемента ИЛИ 36 и первый вход элемента И 35, а также на первый управляющий вход коммутатора 20.

Единичный сигнал, образующийся на выходе элемента ИЛИ 36, открывает элемент И 45 и импульс, формируемый одновибратором 44, через элемент И 45 проходит на вход сброса триггера 11 запуска. Триггер 11 переключается в нулевое состояние, и нулевой сигнал с его прямого выхода запрещает работу генератора 12: модуль временно переходит в состояние ожидания.

Очередной импульс П1 с первого выхода генератора 13 переключает триггер 16 в единичное состояние и единичный сигнал с прямого выхода триггера 16 поступает на второй управляющий вход коммутатора 20, обеспечивая выдачу управляющей микрокоманды S передачи управления на выход 59 передачи управления модуля, при этом нулевой сигнал с инверсного выхода триггера 16 блокирует второй информационный вход коммутатора 20. Одновременно импульс П1 через открытый элемент И 35 и элемент ИЛИ 42 поступает на выход 59 модуля и обеспечивает синхронизацию приема выдаваемой микрокоманды S следующим аналогичным модулем МКС, Этот же импульс с выхода элемента И 35 через элемент 51 задержки и элемент ИЛИ 37 подается на вход установки триггера 11 запуска и возвращает его в единичное состояние (необходимость блокировки генератора 12 на время выдачи управляющих микрокоманд S вызвана возможностью смены информации на выходе 2.8 регистра 2 до появления очередного импульса П1, поскольку F1 > F2).

Код опрашиваемого логического условия с выхода 2.1 и модифицируемый разряд адреса с выхода 2.2 регистра 2 поступают соответственно на адресный и первый информационный входы мультиплексора 4 и формируют на его выходе новое значение младшего разряда адреса. Значение с выхода мультиплексора 4 в объединении с немодифицируемыми разрядами адреса с выхода 2.3 регистра 2 образует исполнительный адрес очередной микрокоманды. Этот адрес через коммутатор 14 передается на информационный вход регистра 3. Единичный сигнал с прямого выхода триггера 11 включает генератор 12 и текущий модуль возобновляет выполнение микропрограммы с адреса, сформированного на информационном входе регистра 3.

Случай 3. Если считанная микрокоманда имеет формат В (фиг. 4), то модуль Мi получает статус ведущего и переходит в режим управления синхронизацией завершения группы параллельных участков, закрепленных за другими модулями. На выходах 2.4, 2.6, 2.7 и 2.9 регистра 2 микрокоманд устанавливается нулевой уровень сигнала, на выходе 2.5 появляется единичный сигнал - метка управления синхронизацией (Мус), а на выходе 2.8 управляющей информации формируется код номера точки синхронизации (НТС) Тq и код соответствующего количества ожидаемых событий (КОС) (завершаемых параллельных участков) Wq, образующие микрокоманду управления синхронизацией Zq.

Код НТС с выхода 2.8 (2.10) регистра 2 поступает на первый вход схемы 9 сравнения и, кроме того, совместно с кодом КОС подается на первый информационный вход коммутатора 19. Единичная метка Мус с выхода 2.5 регистра 2 поступает на первые входы элемента И 24, элемента И 25 (на втором входе которого находится нулевой (запрещающий) сигнал несовпадения с выхода схемы 9 сравнения) и элемента ИЛИ 36. Аналогично ранее рассмотренному единичный сигнал, образующийся на выходе элемента ИЛИ 36, открывает элемент И 45 и импульс, формируемый одновибратором 44, через элемент И 45 проходит на вход сброса триггера 11. Триггер 11 переключается в нулевое состояние и тем самым запрещает работу генератора 12: модуль переходит в состояние ожидания.

Одновременно импульс с выхода одновибратора 44 через открытый элемент И 24 проходит на вход установки триггера 18 управления синхронизацией и переводит его в единичное состояние. Единичный сигнал с прямого выхода триггера 18 поступает на первый управляющий вход коммутатора 19, открывает элемент И 32 и, кроме того, подается на первый вход элемента И 28. Очередной импульс П1 с первого выхода генератора 13 переключает триггер 16 в единичное состояние и одновременно с единичным сигналом, образующимся на его прямом выходе и поступающим на четвертый управляющий вход коммутатора 19, подается на второй вход элемента И 32. Появление единичных сигналов на первом и четвертом управляющих входах коммутатора 19 при одновременной блокировке его третьего управляющего входа нулевым сигналом с инверсного выхода триггера 16 обусловливает передачу управляющей микрокоманды Zq с первого информационного входа коммутатора 19 на выход 58 управления синхронизацией модуля. В свою очередь импульс П1 проходит через элемент И 32, элемент ИЛИ 40, поступает на выход 58 модуля и обеспечивает прием вырабатываемой микрокоманды Zq модулем Мi+1.

Одновременно импульс П1 через открытый элемент И 28 проходит на вход установки триггера 17 и переводит его в единичное состояние. Единичный сигнал с прямого выхода триггера 17 поступает на первый вход элемента И 29. Импульс П2 с второго выхода генератора 13 через открытый элемент И 29 передается на вход сброса триггера 18 и возвращает его в состояние логического нуля. Нулевой сигнал с прямого выхода триггера 18 блокирует элементы И 32 и 28 и, поступая также на первый управляющий вход коммутатора 19, отключает выход 2.8 управляющей информации регистра 2 микрокоманд от выхода 58 управления синхронизацией модуля. В то же время положительный перепад уровня сигнала, возникающий на инверсном выходе триггера 18, переключает триггер 17 в исходное (нулевое) состояние и нулевой сигнал с прямого выхода триггера 17 блокирует элемент И 29. Поступление импульсов П1 и П2 на входы триггеров 17 и 18 прекращается.

Микрокоманды управления синхронизацией, вырабатываемые аналогичным образом другими модулями МКС, поступают на вход 55 модуля и размещаются в буферном запоминающем блоке 5 (ход обработки микрокоманд Z перед размещением в блоке 5 детально рассмотрен ниже). Первая из поступивших микрокоманд с выхода блока 5 подается на второй информационный вход коммутатора 19 и, кроме того, формирует единичный сигнал на выходе элемента ИЛИ 39. Очередной импульс П2 с второго выхода генератора 13 возвращает триггер 16 в нулевое состояние. Нулевой сигнал с прямого выхода триггера 16 блокирует первый, а единичный сигнал с инверсного выхода открывает второй информационный вход коммутатора 19. Единичный сигнал с выхода элемента ИЛИ 39 поступает на второй управляющий вход коммутатора 19, и управляющая микрокоманда с выхода блока 5 через коммутатор 19 ретранслируется на выход 58 модуля. Одновременно этот же сигнал подается на первый вход элемента И 33. Импульс П2 через открытый элемент И 33, элемент ИЛИ 40 поступает на выход 58 модуля и обеспечивает прием ретранслируемой микрокоманды следующим модулем сети.

Одновременно импульс П2 с выхода элемента И 33 через элемент 48 задержки подается на входы сдвига и разрешения сдвига блока 5 и задним фронтом осуществляет сдвиг существующей очереди управляющих микрокоманд (функционирование блока 5 детально рассматривается на примере работы идентичного блока 6 и приводится ниже),

Случай 4. Если считанная микрокоманда имеет формат Г (фиг. 4), то модуль Мi завершает выполнение соответствующего параллельного или последовательного участка микропрограммы и переходит в состояние активного ожидания. На выходах 2.4, 2.5, 2.7 и 2.9 регистра 2 микрокоманд формируется нулевой уровень сигнала, на выходе 2.6 устанавливается единичный сигнал - метка конца параллельного/последовательного участка (Мкпу), состояние выходов 2.1-2.3 становится неопределенным, а на выходе 2.8 (2.10) регистра 2 появляется код номера точки синхронизации Tq, завершающей выполненный участок микропрограммы, - для параллельного и нулевой код - для последовательного участка. Единичный сигнал Мкпу с выхода 2.6 регистра 2 через элемент ИЛИ 36 поступает на первый вход элемента И 45. Импульс с выхода одновибратора 44 через элемент И 45 поступает на вход сброса триггера 11 запуска, переводит его в нулевое состояние и тем самым выключает генератор 12. Одновременно метка Мкпу с выхода 2.6 регистра 2 поступает на первый вход элемента И 27, разрешает переключение триггера 15, блокирует элемент И 23 и, поступая также на третий, четвертый и пятый управляющие входы коммутатора 14 адреса, настраивает его на прием информации (адреса при передаче управления на данный модуль) с входа 56 приема управления модуля.

Очередная микрокоманда управления синхронизацией Zt (выработанная модулем Мk) в сопровождении импульса синхронизации появляется на входе 55 модуля; код КОС Wt поступает на информационный вход регистра-счетчика 10 и входы элемента ИЛИ-НЕ 22, а код HTC Tt подается на второй вход схемы 9 сравнения и сопоставляется с кодом Tq, поступающим с выхода 2.10 регистра 2. Импульс синхронизации, сопровождающий микрокоманду Zt, с входа (линии) 55.3 модуля поступает на вход элемента 43 задержки и со сдвигом во времени появляется на его выходе. С выхода элемента 43 импульс синхронизации подается на вход синхронизации регистра-счетчика 10 событий и передним фронтом фиксирует в нем поступивший код Wt.

В случае совпадения кодов HTC Тq и Тt на выходе схемы 9 появляется единичный сигнал, который поступает на второй вход элемента И 27. Так как на выходе 2.5 регистра 2 микрокоманд присутствует сигнал логического нуля, нулевой сигнал с выхода элемента И 25 блокирует элемент И 26, не допуская переключение триггера 11 в единичное состояние, и, кроме того, открывает элемент И 31.

Импульс с выхода элемента 43 задержки подается на вход одновибратора 47 и задним фронтом возбуждает на его выходе импульс v. Импульс v с выхода одновибратора 47 поступает на третий вход элемента И 27 и, так как на четвертом входе этого элемента присутствует единичный (разрешающий) сигнал с прямого выхода триггера 15, проходит на его выход. С выхода элемента И 27 импульс v поступает на счетный вход регистра-счетчика 10 и передним фронтом инициирует операцию обратного счета: код Wt уменьшается на единицу. Одновременно импульс v появляется на входе синхронизации триггера 15 и задним фронтом переключает его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 15 блокирует элемент И 27, запрещая прохождение очередного импульса v, и, таким образом, не позволяет модулю Мi повторно модифицировать поле КОС этой же микрокоманды Zt при ее очередном появлении на входе 55 модуля (данная блокировка необходима, когда в силу существенного рассогласования моментов окончания различных параллельных участков одни и те же управляющие микрокоманды могут многократно транслироваться по кольцу МКС).

При несовпадении кодов HTC Tq и Tt на втором входе элемента И 27 формируется запрещающий (нулевой) сигнал, импульс v с выхода одновибратора 47 не проходит через элемент И 27 и, таким образом, код Wt, размещенный в регистре-счетчике 10, остается неизменным. Аналогично код Wt не модифицируется, если текущий модуль продолжает выполнение микропрограммы и нулевой сигнал с выхода 2.6 блокирует элемент И 27.

Модифицированный код Wt с выхода регистра-счетчика 10 в объединении с кодом HTC Tt с входа 55.1 модуля поступает на информационный вход буферного запоминающего блока 5. Одновременно импульс v с выхода одновибратора 47 через открытый элемент И 31 поступает на W-вход блока 5 и обеспечивает фиксацию микрокоманды Zt для передачи следующему модулю МКС.

Случай 5. Если считанная микрокоманда имеет формат Д (фиг. 4), то на выходах 2.4-2.7 регистра 2 формируется нулевой уровень сигнала, на выходе 2.9 появляется единичный сигнал - метка конца операции (Мко), а состояние остальных выходов становится неопределенным. Метка Мко с выхода 2.9 регистра 2 через элемент ИЛИ 36 проходит на первый вход элемента И 45. Импульс с выхода одновибратора 44 проходит через элемент И 45 и переводит триггер 11 в нулевое состояние, выключая тем самым генератор 12. В тоже время метка Мко поступает на первый и второй, а также через элемент ИЛИ 38 - на пятый управляющие входы коммутатора 14 и настраивает коммутатор 14 либо на прием кода операции с входа 54 модуля, либо на прием адреса передачи управления с входа 56.2 модуля. Одновременно метка Мко поступает на выход 60 конца операции модуля и сообщает УУВУ о завершении выполнения текущей и готовности МКС к реализации очередной операции.

Рассмотрим работу модуля в режиме приема и анализа микрокоманд передачи управления типа S.

Микрокоманда передачи управления S, выработанная модулем Мi, последовательно транслируется по кольцу МКС и в некоторый момент поступает на вход 56 приема управления модуля Mi+h. Номер приемника управления p, содержащийся в адресной части поступающей микрокоманды, подается на второй вход схемы 8 сравнения и сравнивается с номером текущего модуля Mi+h, формируемым на выходе генератора 7 констант, а адрес передачи управления Апу передается на третий информационный вход коммутатора 14 адреса. Одновременно микрокоманда S подается на информационный вход буферного запоминающего блока 6.

При совпадении номера p с номером текущего модуля Mi+h на выходе схемы 8 сравнения устанавливается единичный уровень сигнала. Единичный сигнал с выхода схемы 8 сравнения передается на шестой управляющий вход коммутатора 14, на вход одновибратора 46 и блокирует элемент И 30. Так как хотя бы на одном из входов элемента ИЛИ 38 имеется единичный сигнал (т.е. рассматриваемый модуль завершил выполнение какого-либо участка микропрограммы или операции в целом), что является условием правильности работы МКС и обеспечивается наличием средств синхронизации завершения параллельных участков, на пятом управляющем входе коммутатора 14 также присутствует единичный сигнал, поэтому Апу через коммутатор 14 поступает на информационный вход регистра 3 адреса. Одновременно положительный перепад уровня сигнала, возникающий на входе одновибратора 46, возбуждает на его выходе импульс, который через элемент ИЛИ 37 поступает на вход установки триггера 11, переключает его в единичное состояние и, таким образом, запускает генератор 12. Первый тактовый импульс t1 с первого выхода генератора 12 подается на вход синхронизации регистра 3 и обеспечивает фиксацию поступившего на его информационный вход адреса Апу. Модуль Мi+h начинает выполнение микропрограммы с адреса Апу.

В дальнейшем работа устройства по реализации микропрограммы ничем не отличается от функционирования модуля Мi при выполнении начального последовательного участка микропрограммы.

В то же время импульс синхронизации, сопровождающий поступившую микрокоманду S с линии 56.3 синхронизации подается на вход элемента 50 задержки, спустя заданное время появляется на его выходе и поступает на первый вход элемента И 30. Так как элемент И 30 заблокирован единичным сигналом совпадения с выхода схемы 8 сравнения, импульс синхронизации не проходит на его выход, а следовательно, и на вход синхронизации записи W буферного запоминающего блока 6. Таким образом, запись поступившей микрокоманды в блок 6 с целью дальнейшей передачи не производится.

Если совпадение номера p и номера модуля Mi+h не происходит, то на выходе схемы 8 сравнения сохраняется нулевой уровень сигнала. Импульс синхронизации с линии 56.3 модуля через элемент 50 задержки и открытый элемент И 30 проходит на вход синхронизации записи W буферного запоминающего блока 6 и обеспечивает прием поступившей микрокоманды S для передачи следующему модулю сети Mi+h+1; состояние текущего модуля остается неизменным.

Микрокоманда (управляющее сообщение) S с информационного входа буферного запоминающего блока 6 (фиг. 2) передается на информационный вход регистра 61. L и на вторые информационные входы коммутаторов 62.1-62.L-1. Так как триггер 67 находится в состоянии логического нуля, единичный сигнал с его инверсного выхода поступает на вторые управляющие входы коммутаторов 62.1-62. L-1 и обеспечивает передачу управляющей микрокоманды на информационные входы регистров 61.1-61. L-1, в то время как нулевой сигнал с его прямого выхода блокирует поступление на выходы коммутаторов 62.1-62.L-1 информации с их первых информационных входов. Сигналы с инверсных выходов регистров 61.1-61.L поступают на входы элементов И 64.1-64.L соответственно и формируют на их выходах код, характеризующий текущее состояние очереди управляющих микрокоманд в блоке.

Пусть в регистрах 61.1-61.k (k<L) зафиксированы ранее поступившие микрокоманды, а остальные регистры находятся соответственно в состоянии логического нуля. Так как на инверсных выходах каждого из регистров 61.1-61.k присутствует по крайней мере по одному нулевому сигналу, а на инверсных выходах регистров 61. k+1-61.L установлены единичные сигналы на выходах элементов И 64.1-64. L образуется код  . Этот код поступает на вход дешифратора 63 и возбуждает единичный сигнал на его (k+1)-м выходе. Указанный сигнал через элемент ИЛИ 65.k+1 передается на V-вход регистра 61. k+1, разрешая тем самым прием информации в данный регистр.

. Этот код поступает на вход дешифратора 63 и возбуждает единичный сигнал на его (k+1)-м выходе. Указанный сигнал через элемент ИЛИ 65.k+1 передается на V-вход регистра 61. k+1, разрешая тем самым прием информации в данный регистр.

Импульс с входа синхронизации записи блока через элемент ИЛИ 66 поступает на входы синхронизации регистров 61.1-61.L и задним фронтом фиксирует управляющую микрокоманду S в регистре 61.k+1. Так как на V-входах остальных регистров 61.1-61. k, 61.k+2-61.L сохраняется запрещающий (нулевой) уровень сигнала, их состояние остается неизменным.

После фиксации микрокоманды S в регистре 61.k+1 на выходе элемента И 64. k+1 появляется нулевой сигнал, который в объединении с сигналами с выходов элементов И 64.1-64.k,64.k+2-64.L поступает на вход дешифратора 63 и возбуждает единичный сигнал на его следующем, т.е. (k+2)-м, выходе. Аналогичным образом очередная управляющая микрокоманда S записывается в регистр 61.k+2 и т.д.

Считывание управляющих микрокоманд из буферного запоминающего блока 6 производится в порядке их поступления.

Микрокоманда S, размеченная в регистре 61.1, появляется на выходе блока и передается (фиг. 1) на входы элемента ИЛИ 41 и второй информационный вход коммутатора 20. Единичный сигнал, образующийся на выходе элемента ИЛИ 41, подается на второй вход элемента И 34 и четвертый управляющий вход коммутатора 20. Очередной импульс П2 с второго выхода генератора 15 переключает триггер 16 в нулевое состояние и одновременно с единичным сигналом с его инверсного выхода, поступающим на третий управляющий вход коммутатора 20, подается на первый вход элемента И 34. Управляющая микрокоманда с выхода блока 6 через открытый коммутатор 20 проходит на выход 59 передачи управления модуля и передается на вход 56 следующего модуля МКС, а импульс П2 проходит через открытый элемент И 34, элемент ИЛИ 42 и синхронизирует прием выдаваемой микрокоманды. Одновременно с выхода элемента И 34 импульс П2 поступает на вход элемента 49 задержки и со сдвигом во времени подается на входы разрешения и синхронизации сдвига буферного запоминающего блока 6.

Импульс с входа разрешения сдвига блока 6 (фиг. 2) поступает на вход установки триггера 67 и переключает его в единичное состояние. Единичный сигнал с прямого выхода триггера 67 подается на первые управляющие входы коммутаторов 62.1-62.L-1 и обеспечивает передачу информации с прямых выходов регистров 61.2-61.L на информационные входы регистров 61.1-61.L-1 соответственно. Этот же сигнал через элементы ИЛИ 65.1-65.L проходит на V-входы регистров 61.1-61. L и разрешает запись информации во все указанные регистры. В то же время импульс с входа синхронизации сдвига (S) блока поступает на вход элемента 68 задержки и, кроме того, через элемент ИЛИ 66 передается на входы синхронизации регистров 61.1-61.L. Так как на V-входах регистров 61.1-61.L находятся разрешающие сигналы, по заднему фронту импульса информация из регистров 61. L-61.2 переписывается в регистры 61.L-1-61.1, а в регистр 61.L заносится нулевой код. Состояние регистра 61.k становится нулевым, на выходе элемента И 64.k формируется единичный сигнал, а управляющая микрокоманда S, ранее размещавшаяся в регистре 61.2, появляется на выходе блока. Импульс с выхода элемента 68 задержки спустя заданное время (время сдвига очереди) поступает на вход сброса триггера 67 и возвращает его в нулевое состояние.

Если после сдвига очереди состояние регистра 61.1 становится нулевым, то на выходе элемента ИЛИ 41 (фиг. 1) устанавливается нулевой сигнал. Этот сигнал блокирует элемент И 34 и предотвращает распространение импульса П2 на выход 59 передачи управления модуля и на вход элемента 49 задержки. Процесс выдачи управляющих микрокоманд на выход 59 модуля приостанавливается. С поступлением в блок 6 очередной управляющей микрокоманды транзитная передача микрокоманд на выход 59 модуля возобновляется.

Рассмотрим работу ведущего модуля Mi в режиме анализа микрокоманд управления синхронизацией.

Микрокоманда управления синхронизацией Zq вырабатываемая модулем Мi, последовательно передается модулям Мi+1, Мi+2,..., Мi+h, которые по мере завершения закрепленных за ними параллельных участков микропрограммы либо уменьшают соответствующий код Wq, либо оставляют поступающую микрокоманду Zq без модификации (см. случай 4). Микрокоманда управления синхронизацией последовательно проходит через все модули сети и вновь поступает на вход 55 управления синхронизацией ведущего модуля Mi.

Код НТС Tq появляющейся микрокоманды Zq с входа 55.1 поступает на второй вход схемы 9 сравнения и сопоставляется с кодом НТС, сформированным на выходе 2.10 регистра 2. Так как последний представляет собой код НТС Tq (см. случай 3), на выходе схемы 9 сравнения образуется единичный сигнал совпадения, который передается на второй вход элемента И 25, на первый вход которого поступает единичная метка Мус с выхода 2.5 регистра 2. Одновременно код КОС Wq поступившей микрокоманды Zq с входа 55.2 модуля подается на входы элемента ИЛИ-НЕ 22, а импульс синхронизации, сопровождающий микрокоманду, с линии 55.3 синхронизации поступает на вход элемента 43 задержки и, спустя заданное время, появляется на его выходе.

Если Wq > 0, т.е. среди опрашиваемых параллельных участков существуют незавершенные, на выходе элемента ИЛИ-НЕ 22 образуется нулевой сигнал. Нулевой сигнал с выхода элемента 22 через элемент И 25 проходит на первый вход элемента И 31, а также блокирует элемент И 26, По переднему фронту импульса с выхода элемента 43 код Wq заносится в регистр-счетчик 10 событий и в объединении с кодом НТС с входа 55.1 модуля поступает на информационный вход блока 5, а задний фронт импульса возбуждает импульс v аналогичной формы на выходе одновибратора 47. Одновременно импульс с выхода элемента 43 подается на второй вход элемента И 26, однако так как последний заблокирован нулевым сигналом с выхода элемента И 25, на его выходе сохраняется нулевой уровень сигнала, триггер 11 остается в нулевом состоянии и по-прежнему блокирует работу генератора 12. В то же время импульс v с выхода одновибратора 47 через открытый элемент И 31 проходит на W-вход блока 5 и обеспечивает запись микрокоманды Zq в блок 5 для повторной выдачи следующему модулю МКС и опроса состояния оставшихся участков микропрограммы. Так как элемент И 27 заблокирован нулевым сигналом с выхода 2.6 регистра 2, импульс v не проходит на выход элемента 27 и, таким образом, микрокоманда Zq (код Wq) передается на вход блока 5 без изменений.

Если Wq= 0, т.е. все сходящиеся к точке Tq параллельные участки завершены, то на выходе элемента ИЛИ-НЕ 22 образуется единичный сигнал, который через открытый элемент И 25 поступает на первый вход элемента И 26 и, кроме того, блокирует элемент И 31. Импульс синхронизации с выхода элемента 43 через открытый элемент И 26, а также элемент ИЛИ 37 проходит на вход установки триггера 11, переводит его в единичное состояние и тем самым запускает генератор 12. В то же время импульс v, вырабатываемый одновибратором 47, не проходит на выход элемента И 31, а следовательно, и на W-вход блока 5; таким образом, запись поступившей микрокоманды в блок 5 не производится. Первый тактовый импульс t1, образующийся на первом выходе генератора 12, фиксирует ранее сформированный адрес следующей микрокоманды в регистре 3. Модуль Мi выходит из состояния ожидания и возобновляет выполнение микропрограммы с записанного в регистр 3 адреса.

В дальнейшем работа модуля ничем не отличается от рассмотренного ранее его функционирования при реализации начального последовательного участка микропрограммы.

Сразу же после синхронизации параллельных участков в точке Tq модуль Мi может перейти в любой из возможных режимов функционирования, в том числе и в режим управления синхронизацией очередной группы параллельных участков.

Функционирование микроконтроллерной сети, построенной на базе предлагаемого устройства, поясним на примере работы сети, состоящей из пяти модулей, при реализации алгоритма управления, приведенного на фиг. 5, где использованы следующие обозначения: Т1, Т2, Т3, Т4 - точки (вершины) синхронизации, а WO1 , WO2, WO3 и WO4 - количества ожидаемых событий, т.е. параллельных участков, сходящихся к точкам Т1, Т2, Т3 и Т4 соответственно. В обозначениях M , где Qi - общее число параллельных и последовательных участков, закрепленных за модулем Мi,

, где Qi - общее число параллельных и последовательных участков, закрепленных за модулем Мi,  . Штриховкой на фиг. 5 выделены параллельные участки, сопоставленные ведущим модулям, а стрелками показаны условные направления передачи микрокоманд типов S и Z.

. Штриховкой на фиг. 5 выделены параллельные участки, сопоставленные ведущим модулям, а стрелками показаны условные направления передачи микрокоманд типов S и Z.

Первоначально модуль М1 (после поступления КОП от УУВУ) реализует последовательный участок M

Модуль М2, завершая реализацию параллельного участка M

Аналогичным образом осуществляется выполнение и синхронизация завершения других участков микропрограммы. Функционирование МКС прекращается, когда модуль М1 завершает выполнение последнего последовательного участка M

Таким образом, предлагаемое устройство обеспечивает возможность построения на его основе систем, обладающих более широкими функциональными возможностями, чем системы, реализуемые на базе прототипа, что существенно расширяет область применения устройства. Наличие и использование средств синхронизации окончания произвольных групп параллельно выполняемых участков исключает возможность одновременной реализации несовместимых операций (микрокоманд), например участков M

Максимальное число синхронизируемых параллельных участков, сходящихся к единой точке слияния Тm определяется разрядностью n регистра-счетчика 10 событий (фиг. 1) и соответствующего поля в формате управляющих микрокоманд и равно Dmax= 2n-1. Для большинства возможных применений устройства достаточными являются значения n=6-8 (63-255 параллельных участков).

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| МОДУЛЬ СИСТЕМЫ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2145434C1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2146064C1 |

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1999 |

|

RU2168198C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

Изобретение относится к автоматике и вычислительной технике. Применяется при построении высокопроизводительных управляющих и вычислительных систем. Устройство содержит блок памяти микропрограмм, регистры адреса и микрокоманд, мультиплексор логических условий, генератор констант, триггер запуска, первую схему сравнения, первый генератор тактовых импульсов, первый буферный запоминающий блок, коммутатор адреса, первый выходной коммутатор, с первого по третий элементы И, с первого по четвертый элементы ИЛИ, первый элемент задержки и первый одновибратор, регистр-счетчик событий, второй буферный запоминающий блок, второй генератор тактовых импульсов, второй выходной коммутатор, вторую схему сравнения, триггеры переключения каналов, управления синхронизацией и блокировки, элемент ИЛИ-НЕ, триггер, с четвертого по четырнадцатый элементы И, с пятого по седьмой элементы ИЛИ, второй и третий одновибраторы и четыре элемента задержки. 5 ил.

Модуль микроконтроллерной сети, содержащий блок памяти микропрограмм, регистры адреса и микрокоманд, мультиплексор логических условий, генератор констант, триггер запуска, первую схему сравнения, первый генератор тактовых импульсов, первый буферный запоминающий блок, коммутатор адреса, первый выходной коммутатор, с первого по третий элементы И, с первого по четвертый элементы ИЛИ, первый элемент задержки и первый одновибратор, причем вход генератора констант является входом настройки модуля, а выход соединен с первым входом первой схемы сравнения, выход первого выходного коммутатора соединен с выходом управления синхронизацией модуля, выход первого элемента ИЛИ подключен к первому входу первого элемента И, выход второго элемента ИЛИ соединен с входом установки триггера запуска, прямой выход которого соединен с входом первого генератора тактовых импульсов, первый выход которого соединен с входом синхронизации регистра адреса, а второй выход подключен к входу синхронизации регистра микрокоманд, выходы кода логического условия и модифицируемого разряда адреса которого подключены к адресному и первому информационному входам мультиплексора логических условий соответственно, второй информационный вход которого является входом логических условий модуля, выход мультиплексора логических условий в объединении с выходом немодифицируемой части адреса регистра микрокоманд соединен с первым информационным входом коммутатора адреса, выход которого подключен к информационному входу регистра адреса, выход которого соединен с адресным входом блока памяти микропрограмм, выход которого соединен с информационным входом регистра микрокоманд, выход метки конца операции которого подключен к первому и второму управляющим входам коммутатора адреса, отличающийся тем, что в него дополнительно введены второй буферный запоминающий блок, второй генератор тактовых импульсов, вторая схема сравнения, регистр-счетчик событий, второй выходной коммутатор, триггеры переключения каналов, управления синхронизацией и блокировки, триггер, с четвертого по четырнадцатый элементы И, с пятого по седьмой элементы ИЛИ, элемент ИЛИ - НЕ, второй и третий одновибраторы, с второго по пятый элементы задержки, причем выход метки управления синхронизацией регистра микрокоманд соединен с первыми входами второго и третьего элементов И и с первым входом третьего элемента ИЛИ, выход которого подключен к первому входу четвертого элемента И, выход которого подключен к входу сброса триггера запуска, выход метки конца участка регистра микрокоманд соединен с первыми входами пятого и шестого элементов И, с третьим и четвертым управляющими входами коммутатора адреса, с вторым входом третьего элемента ИЛИ, с входом установки триггера блокировки, а также с первым входом четвертого элемента ИЛИ, выход которого подключен к пятому управляющему входу коммутатора адреса, второй информационный вход которого является входом кода операции модуля, выход метки передачи управления регистра микрокоманд соединен с третьим входом третьего элемента ИЛИ, с первым входом седьмого элемента И и с первым управляющим входом второго выходного коммутатора, выход которого в объединении в выходом пятого элемента ИЛИ образуют выход передачи управления модуля, выход управляющей информации регистра микрокоманд включает выход номера точки синхронизации и выход количества ожидаемых событий и подключен к первым информационным входам первого и второго выходных коммутаторов, выход номера точки синхронизации регистра микрокоманд соединен с первым входом второй схемы сравнения, выход которой подключен к второму входу шестого элемента И и к второму входу третьего элемента И, третий вход которого подключен к выходу элемента ИЛИ - НЕ, выход третьего элемента И соединен с первым (инверсным) входом восьмого элемента И и с первым входом девятого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом первого одновибратора, выход метки конца операции регистра микрокоманд соединен с выходом конца операции модуля, с четвертым входом третьего элемента ИЛИ, с вторым входом четвертого элемента ИЛИ и с вторым входом пятого элемента И, третий вход которого является входом пуска модуля, выход пятого элемента И соединен с третьим входом второго элемента ИЛИ, второй выход первого генератора тактовых импульсов подключен к входу второго одновибратора, выход которого подключен к второму входу четвертого элемента И и к второму входу второго элемента И, выход которого соединен с входом установки триггера управления синхронизацией, прямой выход которого подключен к первому управляющему входу первого выходного коммутатора, к первому входу десятого элемента И и к первому входу одиннадцатого элемента И, выход которого соединен с входом установки триггера, счетный вход которого подключен к инверсному выходу триггера управления синхронизацией, прямой выход триггера соединен с первым входом двенадцатого элемента И, выход которого подключен к входу сброса триггера управления синхронизацией, первый выход второго генератора тактовых импульсов подключен к второму входу седьмого элемента И, к второму входу одиннадцатого элемента И, к входу установки триггера переключения каналов и к второму входу десятого элемента И, выход которого соединен с первым входом шестого элемента ИЛИ, выход которого подключен к выходу управления синхронизацией модуля, второй выход второго генератора тактовых импульсов соединен с первым входом тринадцатого элемента И, с вторым входом двенадцатого элемента И, с входом сброса триггера переключения каналов и с вторым входом первого элемента И, выход которого подключен к второму входу шестого элемента ИЛИ и к входу первого элемента задержки, выход которого соединен с входами синхронизации сдвига и разрешения сдвига первого буферного запоминающего блока, выход которого соединен с вторым информационным входом первого выходного коммутатора и с входами первого элемента ИЛИ, выход которого подключен к второму управляющему входу первого выходного коммутатора, третий и четвертый управляющие входы которого соединены с инверсным и прямым выходами триггера переключения каналов соответственно, вход управления синхронизацией модуля образован входом номера точки синхронизации, входом количества ожидаемых событий и линией синхронизации, вход номера точки синхронизации модуля соединен с вторым входом второй схемы сравнения и в объединении с выходом регистра-счетчика событий подключен к информационному входу первого буферного запоминающего блока, вход синхронизации записи которого соединен с выходом восьмого элемента И, вход количества ожидаемых событий модуля соединен с входами элемента ИЛИ - НЕ и с информационным входом регистра-счетчика событий, линия синхронизации входа управления синхронизацией модуля подключена к входу второго элемента задержки, выход которого подключен к входу синхронизации регистра-счетчика событий, к второму входу девятого элемента И и к входу третьего одновибратора, выход которого соединен с вторым (прямым) входом восьмого элемента И и с третьим входом шестого элемента И, четвертый вход которого соединен с прямым выходом триггера блокировки, выход шестого элемента И подключен к счетным входам триггера блокировки и регистра-счетчика событий, прямой и инверсный выходы триггера переключения каналов соединены соответственно с вторым и третьим управляющими входами второго выходного коммутатора, вход приема управления модуля образован входом номера модуля, входом адреса приема управления и линией синхронизации, вход адреса приема управления модуля соединен с третьим информационным входом коммутатора адреса и в объединении с входом номера модуля устройства подключен к информационному входу второго буферного запоминающего блока, выход которого подключен к второму информационному входу второго выходного коммутатора и к входам седьмого элемента ИЛИ, выход которого соединен с четвертым управляющим входом второго выходного коммутатора и с вторым входом тринадцатого элемента И, выход которого подключен к первому входу пятого элемента ИЛИ и к входу третьего элемента задержки, выход которого соединен с входами синхронизации сдвига и разрешения сдвига второго буферного запоминающего блока, вход синхронизации записи которого подключен к выходу четырнадцатого элемента И, первый (прямой) вход которого соединен с выходом четвертого элемента задержки, вход которого соединен с линией синхронизации входа приема управления модуля, вход номера модуля устройства подключен к второму входу первой схемы сравнения, выход которой соединен с вторым (инверсным) входом четырнадцатого элемента И, с входом первого одновибратора, а также с шестым управляющим входом коммутатора адреса, выход седьмого элемента И подключен к второму входу пятого элемента ИЛИ и к входу пятого элемента задержки, выход которого соединен с четвертым входом второго элемента ИЛИ, выход микроопераций регистра микрокоманд является выходом микроопераций модуля.

| WO, заявка, 86/04700, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| DE, заявка, 4026871, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| DE, заявка, 3009121, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 1647566, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 1325477, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-05-27—Публикация

1997-03-20—Подача