Изобретение относится к радиотехнике и может быть использовано для автоматического измерения в дискретных каналах связи характеристик группирования ошибок с цифровой индикацией.

Известны устройства для контроля качества каналов связи, позволяющие учитывать эффект группирования ошибок .

Принцип действия устройств по авт. св. СССР N 856023 и N 926777 заключается в том, что в специальный счетчик записывается число, при этом импульсы ошибок, поступающие из блока выявления ошибок, уменьшают содержимое счетчика. При обнулении счетчика вырабатывается сигнал на обработку результатов измерения характеристик группирования ошибок.

Недостатком подобных схем является низкая точность измерения, поскольку емкость счетчика выбирается эмпирически путем усреднения результатов измерения длительности групп ошибок за продолжительный период.

Наиболее близким по технической сущности и достигаемому результату является устройство для контроля качества дискретного канала связи .

Устройство содержит блок согласования, блок выявления ошибок, первую схему И, элементы задержки, схему ИЛИ, схему НЕ, вторую схему И, счетчик одиночных ошибок, датчик сигналов сброса, блок управления, триггер, третью схему И, счетчик смежных ошибок, счетчик числа групп ошибок, первый и второй блоки деления, первый и второй дешифраторы, блоки ключей, блок индикации .

Использование данного устройства возможно для оперативной оценки качества дискретных каналов и в качестве датчика для повышения достоверности информации в адаптивных линиях связи.

Однако область его применения ограничена измерением характеристик группирования только смежных (т.е. следующих друг за другом подряд) ошибок.

Целью изобретения является повышение точности оценки характеристик группирования ошибок в дискретных каналах связи с изменяющимися во времени параметрами, в которых для повышения достоверности информации применяется адаптивное управление длиной помехозащитного кода в зависимости от длительности пакетов (групп) ошибок в принимаемой информации. При этом под пакетом ошибок часто понимается группа ошибочно принятых единичных элементов, отделенных друг от друга не менее чем Iзбезошибочными элементами дискретного сигнала. В соответствии с рекомендациями МККТТ обычно выбирают Lз=10 . Изобретение позволяет измерять характеристики группирования ошибок при указанном более широком относительно использованного в определении группы (пакета) ошибок.

Цель достигается тем, что в устройство для оценки качества дискретного канала связи, содержащее блок согласования, блок выявления ошибок, счетчик общего числа ошибок, счетчик числа пакетов ошибок, счетчик длины пакета ошибок, датчик сигналов сброса, блок управления, первый и второй блоки деления, первый и второй дешифраторы, первый и второй блоки ключей, блок индикации введены счетчик ошибок в пакете и блок анализа пакетов ошибок, состоящий из первой и второй схем НЕ, первого и второго триггера, первой, второй, третьей и четвертой схем И, схемы И-НЕ, первого и второго счетчиков, элемента задержки, первой и второй схем ИЛИ, при этом вход первой схемы НЕ, соединенный с вторыми входами схемы И-НЕ и второй схемы И и являющийся первым входом блока анализа пакетов ошибок, соединен с выходом блока выявления ошибок и счетным входом счетчика общего числа ошибок, выход первой схемы НЕ соединен с тактовым входом первого триггера и входом параллельной записи первого счетчика, выход которого соединен с входом сброса первого триггера, прямой выход которого соединен с первыми входами первой и второй схем И и входом установки второго триггера, а инверсный выход соединен с первым входом схемы И-НЕ, выход которой соединен с входом параллельной записи второго счетчика, на вторые входы первой и третьей схем И, соединенные с входом датчика сигнала сброса и являющиеся вторым входом блока анализа пакетов ошибок, поступают импульсы тактовой синхронизации, выход первой схемы И соединен с входами вычитания первого и второго счетчиков соответственно, выход второго счетчика соединен с входом второй схемы НЕ, выход которой соединен с первым входом четвертой схемы И, а инверсный выход является первым выходом блока анализа пакетов ошибок и соединен со счетным входом счетчика числа пакетов ошибок, первым входом первой схемы ИЛИ и входом элемента задержки, выход которого соединен с вторым входом первой схемы ИЛИ, выход которой соединен с первым входом третьей схемы И, выход которой является вторым выходом блока анализа пакетов ошибок и соединен со счетным входом счетчика длины пакета ошибок и вторым входом четвертой схемы И, выход которой соединен с первым входом второй схемы ИЛИ, второй вход которой соединен с выходом второй схемы И, а выход является третьим выходом блока анализа пакетов ошибок и соединен со счетным входом счетчика ошибок в пакете, выход которого соединен с первым сигнальным входом второго блока деления, второй сигнальный вход которого соединен с выходом счетчика общего числа ошибок, выход счетчика длины пакета ошибок соединен с первым сигнальным входом первого блока деления, второй сигнальный вход которого соединен с выходом счетчика числа пакетов ошибок, выход датчика сигнала сброса соединен с входами сброса счетчиков общего числа ошибок, числа пакетов ошибок, длины пакета ошибок, ошибок в пакете, а также с входом блока управления.

Анализ существенных отличий по источникам патентной и научно-технической информации показал, что в известных устройствах для контроля качества каналов нет такой совокупности перечисленных элементов, соединенных в описанной последовательности, позволяющих реализовать цель, достигаемую предложенным устройством, что позволяет сделать вывод о соответствии данного технического решения критерию "существенные отличия".

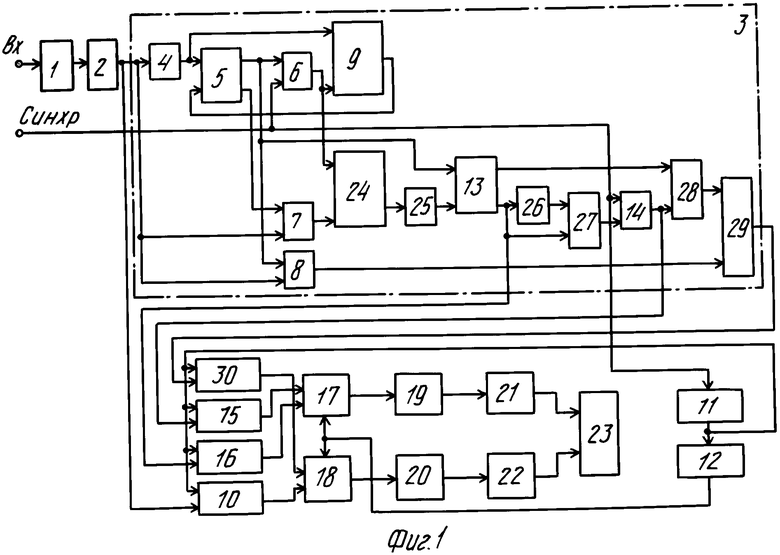

На фиг. 1 изображена структурная схема предложенного устройства.

Устройство содержит блок 1 согласования, блок 2 выявления ошибок, блок 3 анализа пакетов ошибок, состоящий из первой схемы НЕ 4, первого триггера 5, первой схемы И 6, схемы И-НЕ 7, второй схемы И 8, первого счетчика 9, второго триггера 13, третьей схемы И 14, второго счетчика 24, второй схемы НЕ 25, элемента 26 задержки, первой схемы ИЛИ 27, четвертой схемы И 28 и второй схемы ИЛИ 29, счетчик общего числа ошибок 10, датчик сигнала сброса 11, блок управления 12, счетчик длины пакета ошибок 15, счетчик числа пакетов ошибок 16, первый и второй блоки деления 17 и 18 соответственно, первый и второй дешифраторы 19 и 20 соответственно, первый и второй блоки ключей 21 и 22 соответственно, блок индикации 23, счетчик ошибок в пакете 30.

Причем входом устройства является вход блока 1 согласования, выход которого соединен с входом блока 2 выявления ошибок, выход которого соединен с входом блока 2 выявления ошибок, выход которого соединен с входом первой схемы НЕ 4, соединенным с вторыми входами схемы И-НЕ 7 и второй схемы И 8 и являющимся первым входом блока 3 анализа пакетов ошибок, а также со счетным входом счетчика 10 общего числа ошибок, выход первой схемы НЕ 4 соединен с тактовым входом первого триггера 5 и входом параллельной записи первого счетчика 9, выход которого соединен со входом сброса первого триггера 5, прямой выход которого соединен с первыми входами первой схемы И 6 и второй схемы И 8, а также со входом установки второго триггера 13, а инверсный выход триггера 5 соединен с первым входом схемы И-НЕ 7, выход которой соединен с входом параллельной записи второго счетчика 24, на вторые входы схем И 6 и И 14, соединенные с входом датчика 11 сигнала сброса и являющиеся вторым входом блока 3 анализа пакетов ошибок, поступают импульсы тактовой синхронизации.

Выход первой схемы И 6 соединен с входами вычитания первого и второго счетчиков 9 и 24 соответственно, выход второго счетчика 24 соединен с входом второй схемы НЕ 25, выход которой соединен с тактовым входом второго триггера 13, прямой выход которого соединен с первым входом четвертой схемы И 28, а инверсный выход является первым выходом блока 3 анализа пакетов ошибок и соединен со счетным входом счетчика 16 числа пакетов ошибок, первым входом первой схемы ИЛИ 27 и входом элемента 26 задержки, выход которого соединен с вторым входом первой схемы ИЛИ 27, выход которой соединен с первым входом третьей схемы И 14, выход которой является вторым выходом блока 3 анализа пакетов ошибок и соединен со счетным входом счетчика 15 длины пакета ошибок и вторым входом четвертой схемы И 28, выход которой соединен с первым входом второй схемы ИЛИ 29, второй вход которой соединен с выходом второй схемы И 8, а выход является третьим выходом блока 3 анализа пакетов ошибок и соединен со счетным входом счетчика 30 ошибок в пакете, выход которого соединен с первым сигнальным входом второго блока 18 деления, второй сигнальный вход которого соединен с выходом счетчика 10 общего числа ошибок.

Выход счетчика 15 длины пакета ошибок соединен с первым сигнальным входом первого блока 17 деления, второй сигнальный вход которого соединен с выходом счетчика 16 числа пакетов ошибок, выход датчика 11 сигнала сброса соединен с входами сброса счетчика 10 общего числа ошибок счетчика 16 числа пакетов ошибок, счетчика 15 длины пакета ошибок, счетчика 30 ошибок в пакете, а также с входом блока 12 управления, выход которого соединен с управляющими входами блоков 17, 18 деления, выходы которых через дешифраторы 19, 20 соответственно и блоки 21 и 22 ключей соответственно соединены с входами блока 23 индикации.

Все введенные блоки стандартные .

Блок 1 предназначен для преобразования уровней сигнала, поступающего с выхода дискретного канала, в необходимые для срабатывания цифровых схем логические уровни и состоит из буферного каскада, выполненного на ОУ К553УД2 и оптотранзисторного ключа АОТ11ОА .

Блок 2 предназначен для выявления ошибок в принимаемой информации с использованием тестовых, кодовых или косвенных методов и может быть реализован аппаратно на цифровых микросхемах или программно с использованием микропроцессорного контроллера.

Блоки 4-8, 10, 13-16, 25-30 реализованы на стандартных ИМС серии К555 .

Счетчики 9, 24 представляют собой стандартные двоичные реверсивные счетчики с входами параллельной загрузки серии К555, причем изменяя логические уровни на этих входах, т.е. изменяя значение L3, можно модифицировать критерий определения пакета ошибок, что позволяет с помощью предложенного устройства контролировать параметры группирования как смежных ошибок (когда L3=1), так и ошибок, разделенных L≅L3безошибочными интервалами.

Датчик 11 сигналов сброса представляет собой счетчик с переменной емкостью, реализованный на ИМС серии К555, при этом изменяя емкость счетчика, можно менять продолжительность сеанса контроля канала.

Блок 12 предназначен для формирования сигнала управления блоками деления и представляет собой триггер серии К555.

Операции вычисления коэффициента группирования и средней длительности групп ошибок (блоки 17, 18 деления), а также отображения результатов вычисления (дешифраторы 19, 20, блоки 21, 22 ключей, блок 23 индикации) осуществляются с помощью стандартной микроЭВМ "Электроника Д3-28" .

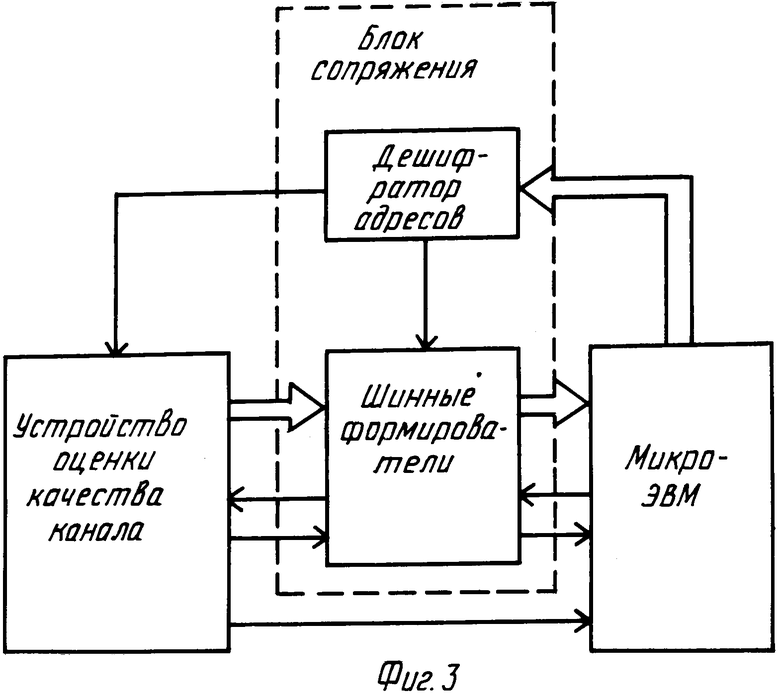

Блок сопряжения с микроЭВМ (на схеме не указан) построен согласно алгоритму ввода-вывода микроЭВМ Д2-28. Использован принцип работы с запросом на прерывание программы.

Блок-схема устройства сопряжения приведена на фиг. 3.

Устройство работает следующим образом. По окончании сеанса измерений блок 12 управления из устройства контроля качества дискретного канала формирует сигнал "Запрос на прерывание", который поступает в микроЭВМ. После этого микроЭВМ на шине управления формирует адреса периферийных устройств, которые декодируются дешифратором адреса. Сигналы с последнего поступают на устройство контроля качества и шинные формирователи. Данные со счетчиков через шинные формирователи поступают на шину ввода. Ввод информации производится по сигналам "ВВ" и "СИП", причем сигнал "ВВ" формируется в микроЭВМ, а сигнал "СИП" - в устройстве сопряжения. Блок сопряжения реализован на ИМС серии К155 и шинных формирователях К589АП26 .

Устройство для контроля качества дискретных каналов работает следующим образом.

Сигналы из дискретного канала через блок 1 согласования поступают на блок 2, который выделяет ошибки. При обнаружении ошибки на выходе блока 2 вырабатывается импульс, который поступает на счетчик 10 общего числа ошибок, где эти импульсы накапливаются. Одновременно эти импульсы поступают на блок анализа пакетов ошибок 3. Если ошибка будет одиночной (т.е. интервал между соседними импульсами ошибок превышает величину L3тактов, выбираемую в соответствии с критерием определения пакета ошибок ), то на выходах блока 3 импульсов не будет. В случае появления пакета ошибок (с интервалом между ошибками в пределах пакета менее L3) на первом выходе блока 3 появится импульс, сигнализирующий об обнаружении пакета ошибок. Эти импульсы на интервале анализа накапливаются счетчиком 16 числа пакетов ошибок. Количество импульсов на втором выходе блока 3 будет соответствовать длине обнаруженного пакета (в тактах) и будет фиксироваться счетчиком 15 длины пакета ошибок. Количество импульсов на третьем выходе блока 3 будет соответствовать количеству ошибок в обнаруженном пакете и будет подсчитываться счетчиком 30 ошибок в пакете.

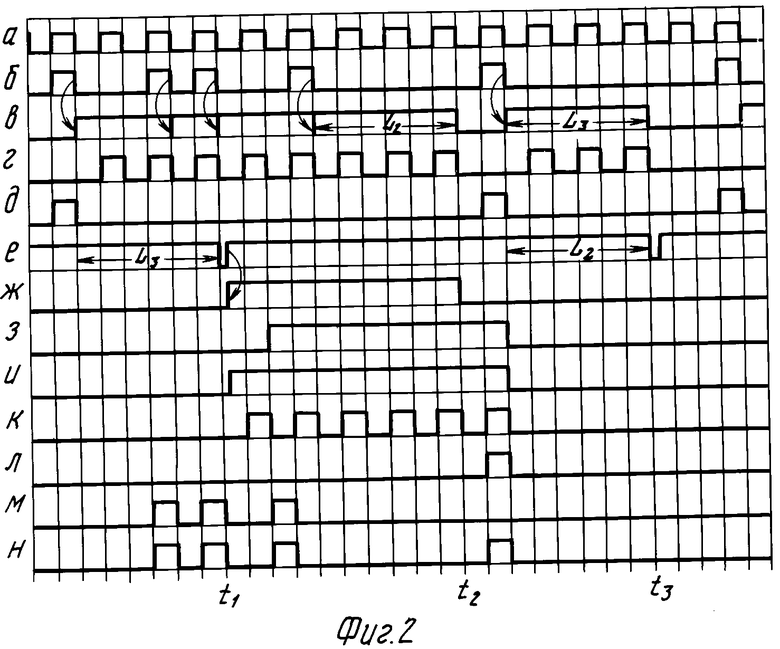

Принцип работы блока 3 анализа пакетов ошибок поясняют временные диаграммы на фиг. 2 (диаграммы показаны для L3=3). Первый импульс ошибки с выхода блока 2 выявления ошибок (эпюра б) поступает через схему И-НЕ 7 на вход параллельной записи счетчика 24 (эпюра д), записывая в него двоичный код числа L3, и через первую схему НЕ 4 - на тактовый вход первого триггера 5, переводя его в единичное состояние по прямому выходу (эпюра в), и одновременно на вход параллельной записи счетчика 9, записывая в него двоичный код числа L3. Уровень логической единицы с прямого выхода триггера 5 (эпюра в) снимает блокировку по входу установки второго триггера 13, разрешает прохождение через схему совпадения И 8 импульсов ошибок с выхода блока 2, следующих за первым с интервалом L<L3 (эпюра м), а также прохождение через схему И 6 импульсов тактовой синхронизации (эпюра а) на вход вычитания счетчиков 9 и 24 (эпюра г), под воздействием которых значение записанного в счетчиках 9 и 24 двоичного кода последовательно уменьшается от L3 до нуля.

Если очередной импульс ошибки с выхода схемы НЕ 4 поступил через интервал L<L3, то этим импульсом в первый счетчик 9 по входу параллельной записи повторно записывается двоичный код числа L3, и декремент кода счетчика 9 начинается вновь со значения L3 (момент времени t1 на диаграммах фиг. 2). Если же импульс ошибки поступит через интервал L≥L3 (моменты времени t2 или t3 на диаграммах фиг. 2), то значение кода в счетчике 9 достигнет нулевого, и импульс с выхода счетчика поступит на вход сброса первого триггера 5, возвращая его в состояние "0" по прямому выходу (эпюра в). Уровень логического нуля с прямого выхода триггера 5 блокирует по первому входу схему совпадения И 8 и по входу установки триггер 13, устанавливая его в "нулевое" состояние по инверсному выходу. При достижении нулевого значения двоичного кода в счетчике 24 импульс с его выхода через вторую схему НЕ 25 (эпюра е) поступает на тактовый вход второго триггера 13 и, если на входе установки триггера присутствует уровень логической единицы (момент времени t1 на временных диаграммах фиг. 2), переводит его в единичное состояние по инверсному выходу (эпюра ж), что соответствует обнаружению пакета ошибок.

Если в момент поступления на тактовый вход триггера 13 импульса с выхода схемы НЕ 25 на входе установки триггера присутствует уровень логического нуля, то триггер 13 остается в прежнем "нулевом" состоянии по инверсному выходу (момент времени t3 на диаграммах фиг. 2). Сигнал с инверсного выхода триггера 13, который служит первым выходом блока 3 анализа пакетов ошибок, поступает на первый вход схемы ИЛИ 27 (эпюра ж) и через элемент задержки 26 на второй вход схемы ИЛИ 27 (эпюра з), с выхода которой импульс положительной полярности поступает на первый вход схемы совпадения И 14 (эпюра и), с выхода которой, являющегося вторым выходом блока 3 анализа пакетов ошибок, число импульсов тактовой синхронизации, равное длине пакета ошибок, поступает на второй вход схемы И 28 (эпюра к), на первый вход которой подается сигнал с прямого выхода триггера 13. Выделенный схемой И 28 импульс (эпюра л), поступающий на первый вход схемы ИЛИ 29, добавляется в ней с последовательностью импульсов с выхода схемы совпадения И 8 (эпюра м), образуя на выходе схемы ИЛИ 29, являющемся третьим выходом блока 3 анализа пакетов ошибок, последовательность с числом импульсов, равным количеству ошибок в обнаруженном пакете (эпюра н).

По окончании интервала анализа датчик 11 вырабатывает сигнал, по которому считывается информация со счетчиков 10, 15, 16 и 30, одновременно подготавливая их к новому сеансу измерений. Одновременно сигнал с датчика 11 подается на блок управления 12, который формирует сигнал управления блоками 17 и 18 деления. В блоке 17 происходит деление двоичного кода, поступившего со счетчика 15 длины пакета ошибок, на двоичный код, поступивший со счетчика 16 числа пакетов ошибок, а в блоке 18 происходит деление двоичного кода, поступившего со счетчика 30 ошибок в пакете, на двоичный код, поступивший со счетчика 10 общего числа ошибок. Результаты деления через соответствующие дешифраторы 19, 20 и далее через блоки ключей 21, 22 поступают на индикатор 23, на котором отображаются значение показателя группирования ошибок, а также значение средней длительности группы ошибок.

По сравнению с известными устройствами предложенное устройство позволяет получить выигрыш в оперативности вычисления показателя группирования ошибок и средней длительности группы ошибок, а также повысить точность оценки качества за счет вычисления средней длительности группы ошибок, оно также позволяет расширить область применения за счет вычисления параметров группирования ошибок при определении окончании пакета ошибок по критерию L3 безошибочных интервалов.

Использование предлагаемого устройства возможно как для визуальной оперативной оценки качества дискретных каналов, так и в адаптивных системах повышения достоверности за счет вариации кодов и скорости передачи при изменении показателей группирования ошибок: коэффициента группирования и средней длительности групп ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля качества дискретного канала связи | 1984 |

|

SU1225022A1 |

| Устройство для контроля качества канала связи | 1979 |

|

SU856023A1 |

| Устройство для измерения показателя группирования ошибок в дискретном канале связи | 1982 |

|

SU1016845A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Генератор потока ошибок | 1979 |

|

SU855968A1 |

| Устройство для контроля канала связи с переменными параметрами | 1980 |

|

SU924882A1 |

| Устройство для контроля качестваКАНАлОВ СВязи | 1979 |

|

SU794743A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2216869C1 |

| Устройство для контроля качества канала связи | 1990 |

|

SU1830186A3 |

| Устройство для контроля качества канала связи | 1990 |

|

SU1716610A2 |

Использование: автоматическое измерение в дискретных каналах связи характеристик группирования, ошибок с цифровой индикацией. Сущность изобретения: устройство содержит блок согласования 1, блок выявления ошибок 2, блок анализа пакета ошибок 3, четыре счетчика 10, 15, 16, 30, два блока деления 17, 18, два шифратора 19, 20, два блока ключей 21, 22, блок индикации 23, датчик 11, блок управления 12. Цель - повышение точности при оценке качества дискретных каналов связи с переменными параметрами при более широком определении пакета ошибок достигается за счет введения счетчика 30 ошибок в пакете и блока анализа пакетов ошибок 3, выполненного определенным образом. 3 ил.

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА ДИСКРЕТНОГО КАНАЛА СВЯЗИ, содержащее последовательно соединенные блок согласования и блок выявления ошибок, выход которого соединен со счетным входом счетчика общего числа ошибок, выход которого соединен с вторым сигнальным входом второго блока деления, а вход сброса объединен с выходом датчика сигналов сброса и входом блока управления, выход которого соединен с входами управления первого и второго блоков деления, выходы которых соединены соответственно с входами первого и второго дешифраторов, выходы которых соединены соответственно с входами первого и второго блоков ключей, выходы которых соединены с первым и вторым входами блока индикации, объединенные по входам сброса счетчик длины пакета ошибок и счетчик числа пакетов ошибок, выход которого соединен с вторым сигнальным входом первого блока деления, отличающееся тем, что введены счетчик ошибок в пакете и блок анализа пакетов ошибок, состоящий из первого и второго элементов НЕ, первого и второго триггеров, первого, второго, третьего и четвертого элементов И, элемента И - НЕ, первого и второго счетчиков, элемента задержки, первого и второго элементов ИЛИ, при этом вход первого элемента НЕ, соединенный с вторыми входами элемента И - НЕ и второго элемента И и являющийся первым входом блока анализа пакетов ошибок, соединен с выходом блока выявления ошибок и счетным входом счетчика общего числа ошибок, выход первого элемента НЕ соединен с тактовым входом первого триггера и входом параллельной записи первого счетчика, выход которого соединен с входом сброса первого триггера, прямой выход которого соединен с первыми входами первого и второго элементов И, и входом установки второго триггера, а инверсный выход соединен с первым входом элемента И - НЕ, выход которого соединен с входом параллельной записи второго счетчика, вторые входы первого и третьего элементов И, соединенные с входом датчика сигнала сброса и являющиеся вторым входом блока анализа пакетов ошибок, являются входом импульсов тактовой синхронизации, выход первого элемента И соединен с входами вычитания первого и второго счетчиков соответственно, выход второго счетчика соединен с входом второго элемента НЕ, выход которого соединен с тактовым входом второго триггера, прямой выход которого соединен с первым входом четвертого элемента И, а инверсный выход является первым выходом блока анализа пакетов ошибок и соединен со счетным входом счетчика числа пакетов ошибок, первым входом первого элемента ИЛИ и входом элемента задержки, выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, выход которого является вторым выходом блока анализа пакетов ошибок и соединен со счетным входом счетчика длины пакета ошибок и вторым входом четвертого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй выход которого соединен с выходом второго элемента И, а выход является третьим выходом блока анализа пакетов ошибок и соединен со счетным входом счетчика ошибок в пакете, выход которого соединен с первым сигнальным входом второго блока деления, второй сигнальный вход которого соединен с выходом счетчика общего числа ошибок, выход счетчика длины пакета ошибок соединен с первым сигнальным входом первого блока деления, второй сигнальный вход которого соединен с выходом счетчика числа пакетов ошибок, выход датчика сигнала сброса соединен с входами сброса счетчиков общего числа ошибок, числа пакетов ошибок, длины пакетов ошибок, ошибок в пакете, а также с входом блока управления.

| Устройство для контроля качества дискретного канала связи | 1984 |

|

SU1225022A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-07-30—Публикация

1991-11-18—Подача