Изобретение относится к цифровой вычислительной технике и может быть использовано при построении средств коммутации специализированных мультипроцессорных вычислительных систем, отказоустойчивых дискретных микроконтроллерных сетей, а также средств параллельного обмена информацией в измерительных системах.

Известна ячейка матричного коммутатора, содержащая с первой по шестую схемы сравнения, первый и второй шифраторы, регистр, с первого по четвертый элементы И, с первого по четвертый шинные формирователи [2].

Недостатком данной ячейки является невозможность построения на ее основе структур, обеспечивающих взаимодействие удаленных абонентов путем передачи сообщения через промежуточные (транзитные) ячейки.

Наиболее близким к предлагаемому устройству по технической сущности является модуль матричного коммутатора, реализующий возможность полносвязного взаимодействия и содержащий с первого по третий блоки организации очередей сообщений, регистр идентификатора модуля, блок анализа очередей сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, первый и второй элементы сравнения, первый и второй дешифраторы, элемент И [1].

Недостатками этого устройства являются невозможность построения на его основе структур, обеспечивающих реализацию множества различных маршрутов доставки сообщений для каждой пары взаимодействующих модулей, и ограниченная наращиваемость этих структур.

Технической задачей изобретения является расширение функциональных возможностей устройства.

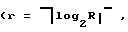

Техническая задача решается тем, что модуль матричного коммутатора, содержащий с первого по третий блоки организации очереди сообщения (БООС), мультиплексор, блок анализа очередей сообщения (БАОС), регистр, дешифратор, блок синхронизации, триггер, первый элемент И, дополнительно включает блок перепрограммируемой постоянной памяти (блок ретрансляции сообщений), коммутатор, с второго по восьмой элементы И, с первого по четвертый элементы ИЛИ, причем группа n+1 (где n - разрядность передаваемых сообщений) входов первого БООС подключена к первой входной шине, объединяющей первую n-разрядную входную информационную шину устройства и первый вход синхронизации приема сообщений устройства; группа n+1 входов второго БООС подключена к второй входной шине, объединяющей вторую n-разрядную входную информационную шину устройства, на старшей (n-й) линии которой постоянно присутствует потенциал логического нуля, и вторую линию синхронизации приема сообщения, которая подключена к выходу второго элемента И; группа n+1 входов третьего БООС подключена к третьей входной шине, объединяющей третью n-разрядную входную информационную шину устройства, на старшей (n-й) линии которой постоянно присутствует потенциал логического нуля, и третью линию синхронизации приема сообщений, которая подключена к выходу третьего элемента И; первые входы второго и третьего элементов И являются соответственно первым и вторым входами разрешения приема сообщений устройства, а вторые входы - соответственно вторым и третьим входами синхронизации приема сообщения устройства; первые группы n выходов БООС с первого по третий подключены к соответствующим группам информационных входов мультиплексора, а вторые группы k+1 (где k - максимальная длина очередей сообщений) выходов - к соответствующим группам входов БАОС, группа информационных выходов которого подключена к адресным входам мультиплексора и к входам дешифратора, первый - третий выходы которого подключены к входам опроса соответствующих БООС; управляющий выход БАОС подключен к первому (инверсному) входу первого элемента И и к входу установки (S) триггера, прямой выход которого соединен с входом разрешения блока синхронизации; первый выход блока синхронизации подключен к входу синхронизации регистра, второй выход - к входам сдвига БООС с первого по третий, а третий выход - к второму (прямому) входу первого элемента И, к третьему входу пятого элемента И и к второму входу шестого элемента И; выход первого элемента И соединен с входом сброса (R) триггера; выходы мультиплексора соединены с информационными входами регистра, первая группа (поле данных) q (где q - разрядность поля данных сообщения) выходов которого подключена к первой - третьей выходным шинам данных устройства, вторая группа (поле признака ретрансляции) r (где r =┐log2R┌, R - емкость памяти блока ретрансляции сообщений) выходов - к входам первого элемента ИЛИ, к адресным входам блока ретрансляции сообщений и к первой группе входов коммутатора, третья группа (поле маршрутного кода) h (где h - максимальная длина участка маршрута) выходов - к входам второго элемента ИЛИ и к второй группе входов коммутатора, а выход кода принимающего канала подключен к первому входу седьмого элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ; на входе "Выбор кристалла" (CS) блока ретрансляции сообщений постоянно присутствует разрешающий (единичный) сигнал, а группа r+h выходов (поля признака ретрансляции и маршрутного кода) подключена к третьей группе входов коммутатора, выходы которого подключены к первой и второй шинам маршрутного кода устройства, которые в объединении с второй и третьей выходными шинами данных устройства соответственно образуют вторую и третью (n-1)-разрядные выходные информационные шины устройства; выход первого элемента ИЛИ подключен к первому входу четвертого элемента И и к первому входу пятого элемента И; выход второго элемента ИЛИ подключен к второму (инверсному) входу четвертого элемента И, к второму входу пятого элемента И, к второму входу третьего элемента ИЛИ, к второму входу седьмого элемента И и к первому входу коммутатора; выход четвертого элемента И подключен к первому входу третьего элемента ИЛИ, к первому входу восьмого элемента И к второму входу коммутатора; второй вход восьмого элемента И соединен с выходом кода принимающего канала блока ретрансляции сообщений, а выход - с вторым входом четвертого элемента ИЛИ, выход которого подключен к первому и второму выходам кода принимающего канала устройства; выход третьего элемента ИЛИ подключен к первому входу шестого элемента И, выход которого подключен к второму и третьему выходам синхронизации приема сообщений устройства; выход пятого элемента И является первым выходом синхронизации приема сообщений устройства и в объединении с первой выходной шиной данных устройств образует первую (q+1)-разрядную выходную информационную шину устройства.

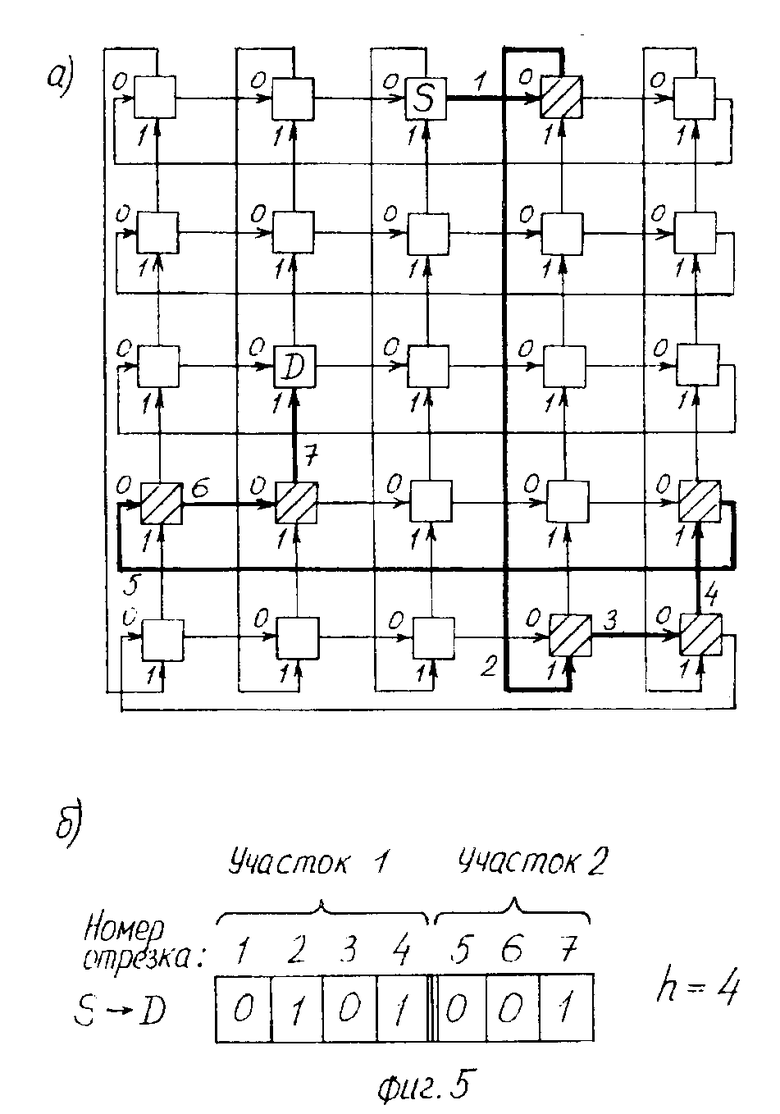

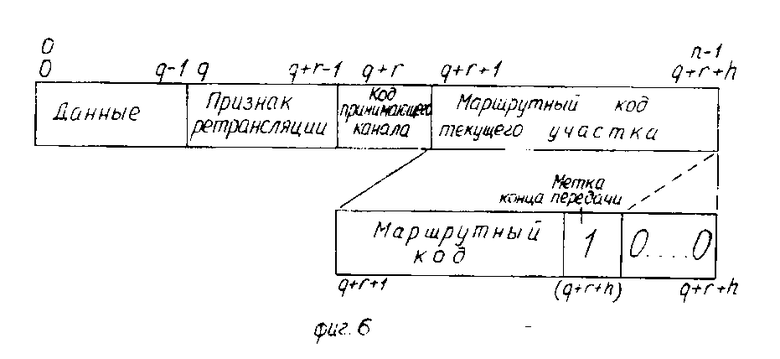

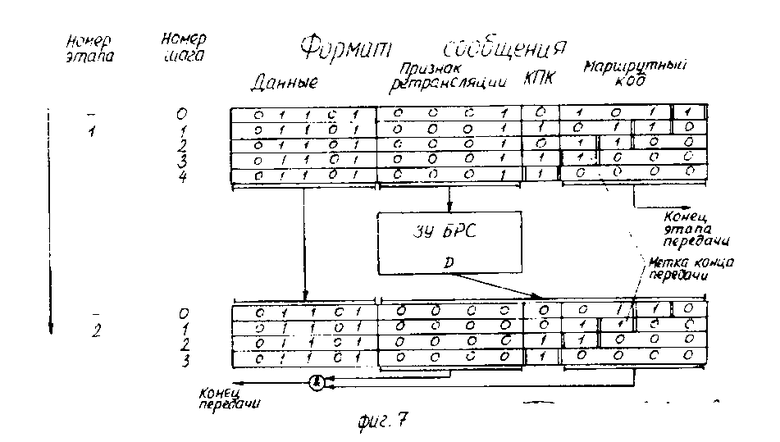

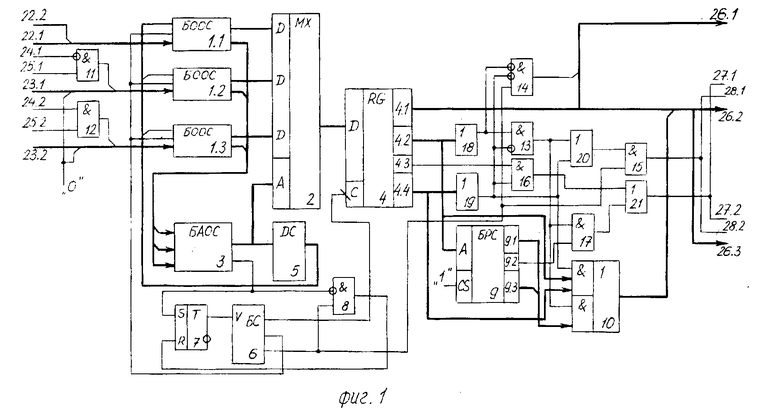

На фиг. 1 изображена схема модуля матричного коммутатора; на фиг. 2 - схема блока организации очередей сообщений; на фиг. 3 - схема блока анализа очередей сообщений; на фиг. 4 - пример матричного коммутатора размерностью 5 х 5 с указанием возможных маршрутов передачи сообщений и способа их кодирования; на фиг. 5 - пример матричного коммутатора размерностью 5 х 5 и способ представления маршрута большой длины при ограниченной разрядности сообщения: на фиг. 6 - обобщенный формат сообщения: на фиг. 7 - диаграмма, отображающая процесс изменения адресной части сообщения при его передаче по назначенному маршруту.

Модуль матричного коммутатора содержит с первого по третий блоки организации очередей сообщения (БООС) 1.1-1.3, мультиплексор 2, блок анализа очередей сообщений (БАОС) 3, регистр 4 (включающий поле данных 4.1 разрядностью q, поле признака ретрансляции 4.2 разрядностью r, одноразрядное поле 4.3 кода принимающего канала и поле маршрутного кода 4.4), дешифратор 5, блок синхронизации 6, триггер 7, первый элемент И 8, а также дополнительно введенные перепрограммируемое постоянное запоминающее устройство - блок ретрансляции сообщений 9 (БРС), коммутатор 10, с второго по восьмой элементы И 11-17, с первого по четвертый элементы ИЛИ 18-21, причем группа n+1, входов БООС 1.1 подключена к первой входной шине, объединяющей первую n-разрядную входную информационную шину устройства 22.1 и первый вход синхронизации приема сообщений устройства 22.2; группа n+1 входов БООС 1.2 подключена к второй входной шине, объединяющей вторую n-разрядную входную информационную шину устройства 23.1, на старшей (n-й) линии которой постоянно присутствует потенциал логического нуля, и вторую линию синхронизации приема сообщений, которая подключена к выходу второго элемента И 11; группа n+1 входов БООС 1.3 подключена к третьей входной шине, объединяющей третью n-разрядную входную информационную шину устройства 23.2, на старшей (n-й) линии которой постоянно присутствует потенциал логического нуля, и третью линию синхронизации приема сообщений, которая подключена к выходу третьего элемента И 12; первые входы второго и третьего элементов И являются соответственно первым 24.1 и вторым 24.2 входами разрешения приема сообщений устройства, а вторые входы - соответственно вторым 25.1 и третьим 25.2 входами синхронизации приема сообщений устройства; первые группы n выходов БООС 1.1-1.3 подключены к соответствующим группам информационных входов мультиплексора 2, а вторые группы k+1 выходов - к соответствующим группам входов БАОС 3, группа информационных выходов которого подключена к адресным входам мультиплексора 2 и к входам дешифратора 5, первый - третий выходы которого подключены к входам опроса соответствующих БООС; управляющий выход БАОС 3 подключен к первому (инверсному) входу первого элемента И 8 и к входу установки (S) триггера 7, прямой выход которого соединен с входом разрешения блока синхронизации 6; первый выход блока синхронизации подключен к входу синхронизации регистра 4, второй выход - к входам сдвига БООС 1.1.-1.3, а третий выход - к второму (прямому) входу первого элемента И 8, к третьему входу пятого элемента И 14 и к второму входу шестого элемента И 15; выход первого элемента И 8 соединен с входом сброса (R) триггера 7; выходы мультиплексора 2 соединены с информационными входами регистра 4, первая группа 4.1 (поле данных) q выходов которого подключена к первой - третьей выходным шинам данных устройства, вторая группа 4.2 (поле признака ретрансляции) r выходов - к входам первого элемента ИЛИ 18, к адресным входам блока ретрансляции сообщений 9 и к первой группе входов коммутатора 10, третья группа 4.4 (поле маршрутного кода) h выходов - к входам второго элемента ИЛИ 19 и к второй группе входов коммутатора 10, а выход 4.3 кода принимающего канала подключен к первому входу седьмого элемента И 16, выход которого соединен с первым входом четвертого элемента ИЛИ 21; на входе "Выбор кристалла" (CS) блока ретрансляции сообщений 9 постоянно присутствует разрешающий (единичный) сигнал, а группа r+h выходов (поля признака ретрансляции 9.1 и маршрутного кода 9.3) подключена к третьей группе входов коммутатора 10, выходы которого подключены к первой и второй шинам маршрутного кода устройства, которые в объединении с второй и третьей выходными шинами данных устройства соответственно образуют вторую 26.2 и третью 26.3 (n-1)-разрядные выходные информационные шины устройства; выход первого элемента ИЛИ 18 подключен к первому входу четвертого элемента И 13 и к первому входу пятого элемента И 14; выход второго элемента ИЛИ 19 подключен к второму (инверсному) входу четвертого элемента И 13, к второму входу пятого элемента И 14, к второму входу третьего элемента ИЛИ 20, к второму входу седьмого элемента И 16 и к первому входу коммутатора 10; выход четвертого элемента И 13 подключен к первому входу третьего элемента ИЛИ 20, к первому входу восьмого элемента И 17 и к второму входу коммутатора 10; второй вход восьмого элемента И 17 соединен с выходом 9.2 кода принимающего канала блока ретрансляции сообщений 9, а выход - с вторым входом четвертого элемента ИЛИ 21, выход которого подключен к первому 27.1 и второму 27.2 выходам кода принимающего канала устройства; выход третьего элемента ИЛИ 20 подключен к первому входу шестого элемента И 15, выход которого подключен к второму 28.1 и третьему 28.2 выходам синхронизации приема сообщений устройства; выход пятого элемента И 14 является первым выходом синхронизации приема сообщений устройства и в объединении с первой выходной шиной данных устройства образует первую (q+1)-разрядную выходную информационную шину устройства 26.1

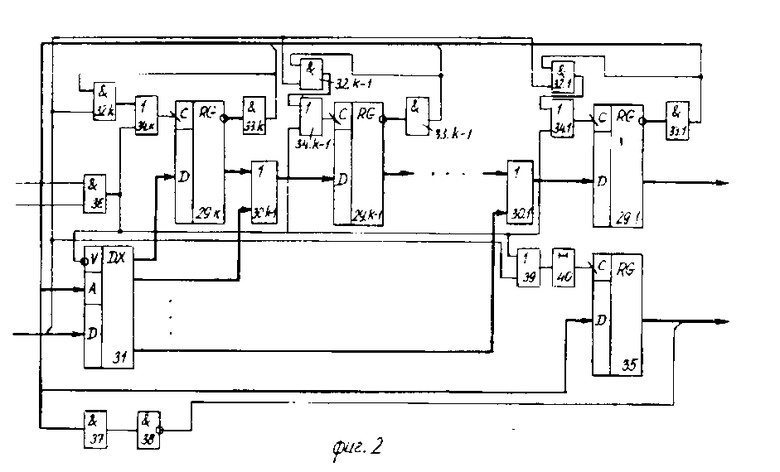

Блок организации очереди сообщений (БООС) (фиг. 2) предназначен для приема, хранения и выдачи сообщений в порядке их поступления и включает группу регистров 29.1-29. k, группу блоков элементов ИЛИ 30.1-30.k-1, демультиплексор 31, первую группу элементов И 32.1-32.k, вторую группу элементов И 33.1-33. k, группу элементов ИЛИ 34.1-34.k, регистр длины очереди 35, первый элемент И 36, второй элемент И 37, элемент НЕ 38, элемент ИЛИ 39, элемент задержки 40, причем информационные входы демультиплексора подключены к n входам группы входов БООС, а группа выходов с второй по k-ю к вторым группам входом блоков элементов ИЛИ с (k-1)-го по первый, соответственно, первая группа выходов - к информационным входам k-го регистра; прямые выходы регистров с второго по k-й подключены к первым группам входов блоков элементов ИЛИ с первого по (k-1)-й, соответственно, а прямые выходы первого регистра образуют первую группу n выходов БООС; выходы блоков элементов ИЛИ с первого по (k-1)-й соединены с информационными входами регистров с первого по (k-1)-й, соответственно; инверсные выходы регистра с первого по k-й подключены к входам элементов И второй группы с первого по k-й, соответственно, выходы которых подключены к адресным входам демультиплексора, к первым входам элементов И первой группы с первого по k-й, соответственно, к информационным входам регистра длины очереди и к входам второго элемента И, выход которого соединен с входом элемента НЕ, выход которого в объединении с выходами регистра длины очереди образует вторую группу k+1 выходов БООС; первый вход группы входов БООС подключен к вторым входам элементов И первой группы и к второму входу элемента ИЛИ, выход которого соединен с входом элемента задержки, выход которого подключен к входу синхронизации регистра длины очереди; первый и второй входы первого элемента И являются соответственно входами опроса и сдвига БООС, а выход подключен к управляющему входу демультиплексора, к первому входу элемента ИЛИ и к вторым входам элементов ИЛИ с первого по k-й, первые входы которых соединены с выходами соответствующих элементов И первой группы, а выходы - с входами синхронизации регистров с первого по k-й, соответственно.

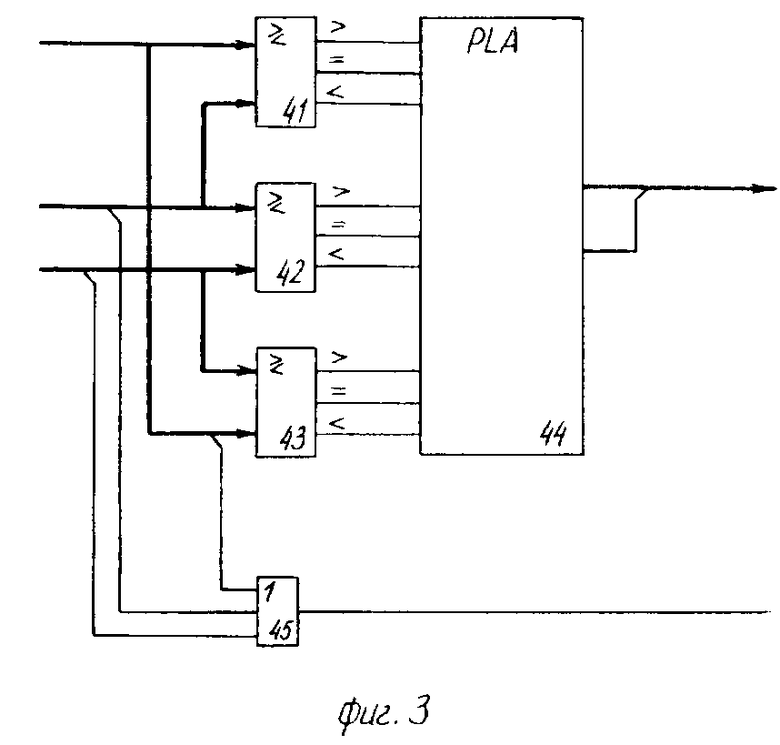

Блок анализа очередей сообщений (БАОС) (фиг. 3) предназначен для определения соотношения длин очередей сообщения в различных БООС и формирования кода БООС, содержащего наибольшее число сообщений, и включает с первой по третью схемы сравнения 41-43, узел постоянной памяти 44 и элемент ИЛИ 45, причем первая и вторая группы входов первой схемы сравнения подключены к k входам первой и второй групп входов БАОС, соответственно, первая и вторая группы входов второй схемы сравнения подключены к k входам второй и третьей групп входов БАОС, соответственно БАОС, соответственно, первая и вторая группы входов третьей схемы сравнения подключены к k входам третьей и первой групп входов БАОС, соответственно; выходы схем сравнения с первой по третью подключены к входам узла постоянной памяти, выходы которого являются информационными выходами БАОС; входы элемента ИЛИ с первого по третий подключены к (k-1)-м входам соответствующих групп входов БАОС, а выход является управляющим выходом БАОС.

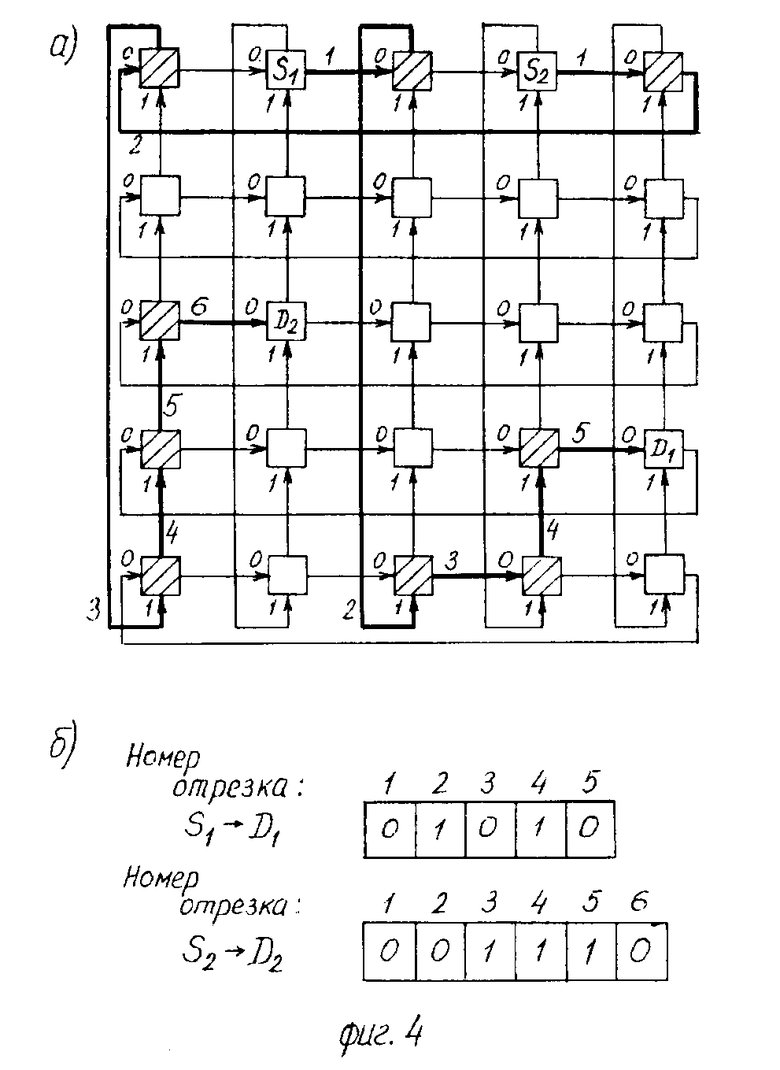

Коммутатор состоит из множества однотипных программируемых модулей, объединенных в матричную структуру. Каждый модуль соединяется с двумя соседними модулями по входу и с двумя модулями по выходу, что обеспечивает возможность передачи сообщений четырьмя различными способами (фиг. 4); слева-вверх, слева-направо, снизу-вверх и снизу-направо. Так как строки и столбцы коммутатора организованы в виде кольцевых структур, имеется потенциальная возможность взаимодействия любой пары модулей.

При построении коммутационных структур на базе прототипа каждому модулю присваивается идентификатор, определяющий его расположение в пределах коммутационного поля. В случае необходимости передачи сообщения, например, модулю А. В. (где А - номер строки; B - номер столбца коммутатора, содержащих этот модуль; "." - символ конкатенации) номер данного модуля указывается в адресном поле сообщения и однозначно определяет маршрут его передачи. Наличие единственно возможного маршрута для каждой пары взаимодействующих модулей в ряде случаев не позволяет установить оптимальное (квазиоптимальное) распределение потоков сообщений в пределах коммутационного поля. Невозможность последнего приводит к росту длин очередей в отдельных модулях, что неизбежно ведет к увеличению времени доставки сообщений и может вызвать блокировку некоторых каналов. Другим аспектом является ограничение числа возможных обменных взаимодействий при наличии в пределах коммутационного поля отказавших или дефектных модулей. Последнее нередко имеет место, например, в матричных СБИС-процессорах.

В предлагаемом устройстве для идентификации адресата (приемника сообщения) используется так называемый маршрутный код. Для построения этого кода выполняются следующие действия. Входные каналы каждого модуля коммутатора помечаются ортогональными одноразрядными кодами ("0" либо "1"), поддержка которых обеспечивается на аппаратном уровне. Для определенности левым входным каналам присваивается код "0", а нижним - код "1". Аппаратная поддержка указанных кодов реализуется путем использования различных активных уровней сигнала для первого 24.1 и второго 24.2 входов разрешения приема сообщения устройства (фиг. 1). Выходы 27.1 (27.2) кода принимающего канала каждого модуля подключаются к входам 24.1 (24.2) или 24.2 (24.1) разрешения приема сообщения, а выходы 28.1 (28.2) - к входам 25.1 (25.2) синхронизации приема сообщений соседних модулей. С целью обеспечения правильности работы коммутатора при комплексировании модулей вводится следующее ограничение: выходы каждого модуля подключаются к разноименным входным каналам соседних модулей (фиг. 4).

Передача сообщений в пределах коммутационного поля осуществляется по заранее известным маршрутам, которые определяются для каждой реализуемой задачи с учетом минимизации времени доставки сообщений, исключением блокировок и обходом дефектных (отказавших) модулей. Каждый маршрут представляется в виде упорядоченного множества элементарных (транзитных) отрезков, число которых определяет длину маршрута. Каждый отрезок соответствует передаче сообщения между двумя соседними модулями (шагу передачи). Например, маршрут S1__→D1 выделенный на фиг. 4а жирной линией, имеет длину 5, т.е. состоит из пяти отрезков и, следовательно, порождает 5 шагов передачи (фиг. 4б). Передача сообщения на каждом шаге производится одновременно в двух направлениях, одно из которых рассматривается как запрещенное. Ограничение на способ комплексирования модулей, введенное ранее, позволяет однозначно задеть требуемый маршрут путем кодирования разрешенных направлений передачи для каждого элементарного отрезка. Последовательность получаемых кодов представляет собой маршрутный код приемника сообщений. Примеры кодирования маршрутов, выделенных на фиг. 4а жирными линиями, представлены на фиг. 4б. Значение f-го разряда маршрутного кода определяет разрешенное направление передачи для f-го шага и соответствует коду входного канала того из соседних модулей, который должен принимать сообщение согласно реализуемому маршруту.

Так как максимальная длина маршрутов заранее не известна, разрядность поля маршрутного кода сообщения принимается равной h (фиксируется), а те маршруты, длина m которых превышает h, разбиваются на  транзитных участков, число которых практически ничем не ограничено. Для каждого участка определяется соответствующий ему маршрутный код. Объединение (конкатенация) маршрутных кодов всех участков определяет код исходного маршрута. Каждому участку маршрута ставится в соответствие этап передачи сообщения. Пример маршрута, содержащего два участка при h=4, приведен на фиг. 5а, а соответствующий ему код - на фиг. 5б.

транзитных участков, число которых практически ничем не ограничено. Для каждого участка определяется соответствующий ему маршрутный код. Объединение (конкатенация) маршрутных кодов всех участков определяет код исходного маршрута. Каждому участку маршрута ставится в соответствие этап передачи сообщения. Пример маршрута, содержащего два участка при h=4, приведен на фиг. 5а, а соответствующий ему код - на фиг. 5б.

С целью поддержки многоэтапных маршрутов в устройстве введено перепрограммируемое постоянное запоминающее устройство, образующее блок ретрансляции сообщений 9 (ППЗУ БРС). В ППЗУ БРС g-го модуля в ячейках с ненулевыми адресами размещаются коды участков тех маршрутов, которые проходят через данный модуль и соответствующие участки которых завершаются именно g-м модулем. Обращение к требуемой ячейке ППЗУ БРС осуществляется по адресу (признаку ретрансляции), который указывается в формате сообщения при необходимости его ретрансляции. Так как число участков, образующих маршрут, заранее не фиксировано, вместе с маршрутным кодом очередного ((S+1)-го) участка из ППЗУ БРС 9 соответствующего транзитного модуля извлекается новый признак ретрансляции. По этому признаку определяется маршрутный код (S+2)-го участка и т.д. до тех пор, пока не будет достигнут последний участок маршрута.

Так как через каждый модуль коммутатора в среднем проходит небольшое число маршрутов, соответствующие участки которых завершаются именно этим модулем, требуемая емкость ППЗУ БРС является незначительной (16 или 32 слова). Таким образом, при фиксированной разрядности передаваемых сообщений и небольших дополнительных аппаратурных затратах реализуется практически неограниченная наращиваемость коммутатора, что принципиально недостижимо в прототипе, где максимальное число модулей в строке (столбце) коммутатора ограничено разрядностью регистра идентификатора модуля и элементов сравнения.

С учетом вышесказанного для передаваемых сообщений установлен формат, приведенный на фиг. 6 и включающий следующие поля:

поле данных;

поле признака ретрансляции;

одноразрядное поле кода принимающего канала (КПК);

поле маршрутного кода реализуемого транзитного участка.

В поле КПК на каждом шаге передачи сообщения присутствует соответствующий код разрешенного направления, что обеспечивает реализацию требуемого маршрута и организуется путем сдвига поля маршрутного кода (по мере передачи сообщения) влево с переносом содержимого его крайнего слева разряда в поле КПК и введением в крайний справа разряд нуля. Признаком завершения очередного этапа передачи сообщения является нулевое состояние поля маршрутного кода. Так как этот код может содержать только нули (что соответствует передаче сообщения по строке), справа от его последнего разряда устанавливается единичная метка конца передачи МКП=1, а оставшиеся (справа от метки) незадействованные разряды заполняются нуляи (фиг. 6). В момент завершения очередного этапа введенная метка поступает в поле КПК, а в поле маршрутного кода содержатся нули. Признаком завершения передачи сообщения является нулевое состояние как поля маршрутного кода, так и поля признака ретрансляции. Формат слов, находящихся в ячейках ППЗУ БРС 9, аналогичен приведенному на фиг. 6 формату сообщения и отличается от последнего только отсутствием поля данных.

Пример реализации маршрута, показанного на фиг. 5а жирной линией, отображен в виде диаграммы, которая представлена на фиг. 7, где для определенности установлено q=5, r=4, h-4.

Модуль матричного коммутатора работает следующим образом. В исходном состоянии регистры 29.1-29.k и 35 БООС 1.1.-1.3 содержат нулевые коды, триггер 7 и регистр 4 находятся в нулевом состоянии (цепи начальной установки на фиг. 1 и фиг. 2 условно не показаны), поэтому блок синхронизации 6 выключен, а на выходах элементов И 33.1-33.k БООС 1.1-1.3 присутствуют сигналы логической единицы, что обусловливает наличие низкого уровня сигнала на выходах элементов НЕ 38 БООС 1.1-1.3. Сигналы логического нуля с выходов последних поступают на (k+1)-е выходы второй группы выходов БООС 1.1-1.3 и далее на соответствующие входы элемента ИЛИ 45 БАОС 3, на выходе которого появляется сигнал логического нуля.

Очередное сообщение с одной из входных информационных шин устройства (например с шины 22.1) в сопровождении импульса синхронизации на соответствующем входе синхронизации приема (22.2) поступает на информационные входы соответствующего БООС (1.1). Так как на адресных входах демультиплексора 31 присутствует код 11..1, сообщение с информационных входов БООС поступает на k-ю группу выходов демультиплексора 31, затем через блок элементов ИЛИ 30.1 - на информационные входы регистра 29.1 и записывается в этом регистре по заднему фронту импульса синхронизации приема, который поступает на входы синхронизации регистров 29.1-29.k через элементы И 32.1-32.k и элементы ИЛИ 34.1-34. k. Элементы И 32.1-32.k оказываются открытыми для указанного импульса, так как на их первых входах присутствуют единичные сигналы с выходов соответствующих элементов И 33.1-33.k. Одновременно импульс синхронизации приема поступает на второй вход элемента ИЛИ 39 и далее на вход элемента задержки 40. С выхода элемента задержки 40 данный импульс подается на синхронизирующий вход регистра 35 длины очереди и своим задним фронтом фиксирует в этом регистре новый установившийся код длины очереди 11... 10 с выходов элементов И 33.1-33.k. В то же время на выходе элемента И 37 появляется нулевой уровень сигнала, в связи с чем на выходе элемента НЕ 38 появляется сигнал логической единицы, который поступает на (k+1)-й выход второй группы выходов БООС, сигнализируя тем самым о наличии сообщения.

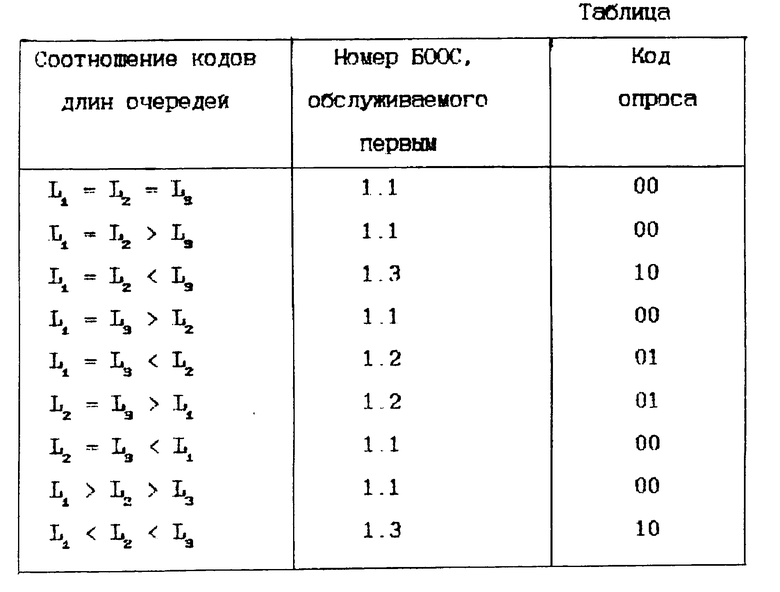

Код длины очереди сообщений с выходов регистра 35 поступает на первые входы первой 41 и вторые входы третьей 43 схем сравнения БАОС 3. На выходах схем сравнения 41-43 образуется код, определяемой соотношением длин очередей сообщения в БООС 1.1-1.3 в соответствии с таблицей (где L1, L2, L3 - коды длин очередей соответственно в БООС 1.1, 1.2 и 1.3). Сформированный код поступает на входы узла постоянной памяти 44, на выходе которого появляется двоичный код номера БООС, содержащего наибольшее число сообщений (в данном случае это БООС 1.1 и код "00").

Одновременно сигнал логической единицы с выхода элемента НЕ 38 БООС 1.1 поступает на первый вход элемента ИЛИ 45, проходит на управляющий выход БАОС 3 и затем подается на вход установки (S) триггера 7, переключая последний в единичное состояние. Единичный сигнал с прямого выхода триггера 7 включает блок синхронизации 6 и последний начинает вырабатывать три распределенные во времени последовательности тактовых импульсов τ1, τ2, τ3.

Код номера опрашиваемого БООС ("00") с информационных выходов БАОС 3 поступает на адресные входы мультиплексора 2 и на входы дешифратора 5. На информационные входы регистра 4 поступает сообщение из регистра 29.1 БООС 1.1. Это сообщение фиксируется в регистре 4 по заднему фронту импульса τ1. Одновременно соответствующие разряды унитарного кода выбранного БООС ("001") с выходов дешифратора 5 поступает на входы опроса БООС 1.1-1.3. Очередной тактовый импульс τ2 с второго выхода блока синхронизации поступает на входы сдвига БООС 1.1-1.3, проходит на выход элемента И 36 БООС 1.1 и, поступая далее через элементы ИЛИ 34.1-34.k на входы синхронизации регистров 29.1-29. k, обеспечивает сдвиг очереди сообщений в БООС 1.1. Этот же сигнал осуществляет управление демультиплексором 31 БООС 1.1 и к моменту сдвига информации обеспечивает наличие нулевых уровней сигнала на всех группах выходов демультиплексора 31. Кроме того, указанный импульс поступает на первый вход элемента ИЛИ 39, а затем на вход элемента задержки 40, задерживается последним на время τ, достаточное для установления нового кода длины очереди, и обеспечивает фиксацию указанного кода с выходов элементов И 33.1-33. k в регистре 35.

В случае наличия (после сдвига) сообщений хотя бы в одном регистре БООС 1.1, 1.2 или 1.3 триггер 7 остается в единичном состоянии, так как на управляющем выходе БАОС 3 присутствует единичный сигнал, обусловленный наличием единичного сигнала на выходе элемента НЕ 38 по крайней мере одного БООС, и устройство продолжает функционировать рассмотренным выше способом. В противном случае на выходе элемента ИЛИ 45 БАОС 3 устанавливается сигнал логического нуля, который с управляющего выхода БАОС 3 поступает на инверсный вход элементов И 8. Очередной тактовый импульс τ3 с третьего выхода блока 6 синхронизации, поступая через открытый элемент И 8 на вход сброса (R) триггера 7, устанавливает последний в нулевое состояние. Нулевой сигнал с прямого выхода триггера 7 выключает блок синхронизации 6.

После определения соотношения длин очередей БАОС 3, выбора одного из БООС 1.f (f=1, 2, 3) и записи сообщения из регистра 29.1 выбранного БООС в регистр 4 параллельно со сдвигом очереди выполняется анализ содержимого служебных полей сообщения, от результатов которого зависит ход дальнейшей работы устройства.

Возможны три различных режима работы устройства при передаче сообщения соседнему модулю: транзитная передача, транзитная передача с ретрансляцией и передача сообщения собственному операционному устройству (устройству, которое обслуживается данным модулем коммутатора).

Рассмотрим последовательно работу устройства в трех указанных режимах:

1. Сообщение, поступившее в регистр 4, имеет хотя бы одну единицу в поле маршрутного кода 4.4 (содержимое поля 4.2 признака ретрансляции безразлично). На выходе элемента ИЛИ 19 появляется сигнал логической единицы, который одновременно поступает на вторые входы элемента И 13, элемента И 14, элемента И 16, элемента ИЛИ 20 и на первый вход коммутатора 10. Единичный сигнал с выхода элемента ИЛИ 20 поступает на первый вход элемента И 15, а нулевой сигнал с выхода элемента И 13 - на первый вход элемента И 17, а также на второй вход коммутатора 10. Так как на первом входе коммутатора 10 присутствует единичный сигнал, а второй вход заблокирован нулевым сигналом с выхода элемента И 13, на его выходы поступает содержимое полей 4.2 и 4.4 регистра 4. Код принимающего канала поступает с выхода 4.3 регистра 4 через открытый элемент И 16 и элемент ИЛИ 21, на втором входе которого имеется низкий уровень сигнала, на первый 27.1 и второй 27.2 выходы кода принимающего канала устройства, а данные с выходов 4.1 регистра 4 передаются одновременно на первую, вторую и третью выходные шины данных устройства.

После затухания переходных процессов в выходных каналах устройства на третий вход элемента И 14 и второй вход элемента И 15 с третьего выхода блока синхронизации 6 поступает очередной тактовый импульс τ3. Этот импульс проходит через открытый элемент И 15 на второй 28.1 и третий 28.2 выходы синхронизации приема сообщений устройства, обеспечивая прием сообщения с выходной информационной шины 26.2 (26.3) устройства тем из соседних модулей, у которого на первом входе элемента И 11 (12) присутствует разрешающий сигнал. Последний поступает с выхода кода принимающего канала 27.1 (27.2) передающего модуля. В то же время собственного операционное устройство модуля игнорирует данное сообщение, так как на втором входе элементов И 14 присутствует запрещающий сигнал и импульс τ3 не проходит на выход указанного элемента.

Сдвиг маршрутного кода по мере передачи сообщения осуществляется путем исключения линии кода принимающего канала из выходных шин устройства на f-м шаге передачи и принудительного введения нуля в крайний справа разряд непосредственно при записи сообщения в БООС очередного модуля, т.е. реализуется монтажным средствами, не требуя дополнительных аппаратурных затрат (фиг. 1).

2. Сообщение, поступившее в регистр 4, содержит нулевой код в поле 4.4 маршрутного кода и ненулевой признак ретрансляции в поле 4.2, что соответствует завершению s-го этапа передачи сообщения и говорит о необходимости обращения к ППЗУ БРС 9 для определения новых маршрутного кода и признака ретрансляции. Признак ретрансляции с выходов 4.2 регистра 4 поступает на адресный вход БРС 9, на входы элемента ИЛИ 18 и на правую группу входов коммутатора 10. Слово, считанное из ППЗУ БРС 9, поступает на третью группу входов коммутатора 10. На выходе элемента ИЛИ 18 формируется единичный, а на выходе элемента ИЛИ 19 нулевой сигнал. На выходах элемента И 14 и элемента И 16 устанавливаются нулевые уровни сигнала. Так как на первом входе элемента И 13 присутствует единичный сигнал, а на втором входе - нулевой, на выходе этого элемента появляется сигнал логической единицы, который поступает на первый вход элемента ИЛИ 20 и далее на первый вход элемента И 15. Одновременно единичный сигнал с выхода элемента И 13 поступает на первый вход элемента И 17 и второй вход коммутатора 10. Код принимающего канала с выхода 9.2 ППЗУ БРС 9 через открытый элемент И 17 и элемент ИЛИ 21 передается на первый 27.1 и второй 27.2 выходы кода принимающего канала устройства, настраивая тем самым один из соседних модулей на прием сообщения. Так как на первом входе коммутатора 10 присутствует нулевой, а на втором - единичный уровень сигнала, слово с выходов 9.1 и 9.3 ППЗУ БРС 9 вместе с данными поля 4.1 поступает на вторую 26.2 и третью 26.3 выходные информационные шины устройства. Таким образом на выходных шинах устройства устанавливается сообщение с модифицированными служебными полями, что обеспечивает возможность реализации следующего этапа передачи. Очередной тактовый импульс τ3, поступает через открытый элемент И 15 на второй 28.1 и третий 28.2 выходы синхронизации приема сообщения устройства, обеспечивает прием сообщения следующим модулем.

3. Поля 4.2. и 4.4 поступившего сообщения содержат нулевую информацию. В этом случае на выходах элемента ИЛИ 18 и элемента ИЛИ 19 появляются нулевые сигналы, которые блокируют элементы И 13 и 16, а нулевые сигналы с выходов последних и элемента ИЛИ 19 обусловливают наличие сигналов логического нуля на выходах элемента И 17, элемента И 15 и на выходах коммутатора 10. В то же время на первом и втором входах элемента И 14 появляются разрешающие (нулевые) сигналы и очередной тактовый импульс τ3 с третьего выхода блока синхронизации 6 проходит на первый выход синхронизации приема сообщений устройства, обеспечивая прием поля данных 4.1 сообщения собственным операционным устройством данного модуля. Так как элемент И 15 заблокирован нулевым сигналом на его первом входе, импульс τ3 не поступает на выход этого элемента, а значит и на выходы синхронизации приема сообщений устройства 28.1 и 28.2, запрещая прием сообщения соседним модулям.

Таким образом, предлагаемое устройство обеспечивает возможность построения на его основе коммутационных структур, позволяющих производить статическую адаптацию маршрутов передачи сообщений и обладающих практически неограниченной наращиваемостью при фиксированной длине сообщения. Наличие указанных свойств является весьма важным при построении систем, функционирующих в реальном масштабе времени и/или в условиях гибкого производства (например, систем логического управления гибкими технологическими и робототехническими комплексами), где набор решаемых задач ограничен, но может изменяться при необходимости расширения функциональных возможностей или частичного перепрофилирования системы. Включение новых задач и организация взаимодействия соответствующих им процессов обеспечивается вложением этих задач в систему, кодированием маршрутов передачи сообщения и добавлением в ППЗУ БРС 9 некоторых модулей новой информации. При этом логическая структура имеющихся задач не изменяется и поэтому не требуется перепрограмирование соответствующих им маршрутов.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2110831C1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1999 |

|

RU2168204C1 |

| МОДУЛЬ ДЛЯ ПЕРЕДАЧИ И ВЕЩАНИЯ СООБЩЕНИЙ В МАТРИЧНОМ КОММУТАТОРЕ | 2003 |

|

RU2249848C2 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ, ПРЕДНАЗНАЧЕННЫЙ ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ, ОБМЕНА СООБЩЕНИЯМИ И ОРГАНИЗАЦИИ ВЕЩАТЕЛЬНЫХ РЕЖИМОВ ОБМЕНА СООБЩЕНИЯМИ | 2000 |

|

RU2178584C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2166793C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАРШРУТА СООБЩЕНИЯ | 2000 |

|

RU2175144C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении средств коммутации специализированных мультипроцессорных вычислительных систем, микроконтроллерных сетей и средств параллельного обмена информацией в измерительных системах. Изобретение позволяет расширить функциональные возможности устройства. С помощью устройств возможно построение на его основе коммутационных структур, позволяющих производить статическую адаптацию маршрутов передачи сообщений. Коммутационные структуры обладают наращиваемостью при фиксированной длине сообщения. В модуль, содержащий с первого по третий блоки организации очередей сообщений, мультиплексор, блок анализа очередей сообщения, регистр, дешифратор, блок синхронизации, триггер, первый элемент И, введены блок ретрансляции сообщений, с второго по восьмой элементы И, с первого по четвертый элементы ИЛИ. Устройство обеспечивает связь любого из трех входных каналов с любым из трех выходных. Прием сообщений из различных входных каналов осуществляется одновременно. 1 табл. 7 ил.

Модуль матричного коммутатора, содержащий с первого по третий блоки организации очередей сообщений, мультиплексор, блок анализа очередей сообщений, регистр, дешифратор, блок синхронизации, триггер, первый элемент И, причем прямой выход триггера соединен с входом разрешения блока синхронизации, первые группы n выходов (n - разрядность передаваемых сообщений) блоков организации очередей сообщений с первого по третий подключены к соответствующим группам информационных входов мультиплексора, выходы которого соединены с информационными входами регистра, вторые группы k + 1 выходов (k - максимальная длина очередей сообщений) блоков организации очередей сообщений с первого по третий соединены с соответствующими группами входов блока анализа очередей сообщений, группа информационных выходов которого подключена к адресным входам мультиплексора и к входам дешифратора, выходы с первого по третий которого подключены к входам опроса блоков организации очередей сообщений с первого по третий соответственно, входы сдвига которых соединены с вторым выходом блока синхронизации, управляющий выход блока анализа очередей сообщений подключен к входу установки S триггера и первому (инверсному) входу первого элемента И, выход которого соединен с входом сброса R триггера, третий выход блока синхронизации подключен к второму (прямому) входу первого элемента И, отличающийся тем, что в него дополнительно включены блок ретрансляции сообщений, коммутатор, с второго по восьмой элементы И, с первого по четвертый элементы ИЛИ, причем группа n + 1 входов первого блока организации очередей сообщений подключена к первой входной шине, объединяющей первую n-разрядную входную информационную шину устройства и первый вход синхронизации приема сообщений устройства, группа n + 1 входов второго блока организации очередей сообщений подключена к второй входной шине, объединяющую вторую n-разрядную входную информационную шину устройства, на старшей (n-й) линии которой постоянно присутствует потенциал логического нуля, и вторую линию синхронизации приема сообщений, которая подключена к выходу второго элемента И, группа n + 1 входов третьего блока организации очередей сообщений подключена к третьей входной шине, объединяющей третью n-разрядную входную информационную шину устройства, на старшей (n-й) линии которой постоянно присутствует потенциал логического нуля, и третью линию синхронизации приема сообщений, которая подключена к выходу третьего элемента И, первые входы второго и третьего элементов И являются соответственно первым и вторым входами разрешения приема сообщений устройства, вторые входы второго и третьего элементов И являются соответственно вторым и третьим входами синхронизации приема сообщений устройства, первый выход блока синхронизации соединен с входом синхронизации регистра, третий выход блока синхронизации подключен к третьему входу пятого элемента И и к второму входу шестого элемента И, первая группа (поле данных) q выходов регистра (где q - разрядность поля данных сообщения) подключена к первой, второй и третьей выходным шинам данных устройства, вторая группа (поле признака ретрансляции) r выходов регистра  R - максимальное число слов блока ретрансляции сообщений,

R - максимальное число слов блока ретрансляции сообщений,  - ближайшее целое число, не меньшее a) соединена с входами первого элемента ИЛИ, адресными входами блока ретрансляции сообщений и с первой группой входов коммутатора, третья группа (поле маршрутного кода) h выходов регистра (h - максимальная длина участка маршрута) подключена к входам второго элемента ИЛИ и к второй группе входов коммутатора, выход кода принимающего канала регистра соединен с первым входом седьмого элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, на входе "выбор кристалла" блока ретрансляции сообщений постоянно присутствует разрешающий (единичный) сигнал, группа r + h выходов (поля признака ретрансляции и маршрутного кода) блока ретрансляции сообщений подключена к третьей группе входов коммутатора, выходы которого подключены к первой и второй шинам маршрутного кода устройства, которые в объединении с второй и третьей выходными шинами данных устройства соответственно образуют вторую и третью (n - 1)-разрядные выходные информационные шины устройства, выход первого элемента ИЛИ подключен к первому входу четвертого элемента И и к первому входу пятого элемента И, выход второго элемента ИЛИ подключен к второму входу четвертого элемента И, к второму входу пятого элемента И, к второму входу третьего элемента ИЛИ, к второму входу седьмого элемента И и к первому входу коммутатора, выход четвертого элемента И подключен к первому входу третьего элемента ИЛИ, к первому входу восьмого элемента И и к второму входу коммутатора, второй вход восьмого элемента И соединен с выходом кода принимающего канала блока ретрансляции сообщений, выход восьмого элемента И подключен к второму входу четвертого элемента ИЛИ, выход которого подключен к первому и второму выходам кода принимающего канала устройства, выход третьего элемента ИЛИ подключен к первому входу шестого элемента И, выход которого подключен к второму и третьему выходам синхронизации приема сообщений устройства, выход пятого элемента И является первым выходом синхронизации приема сообщений устройства и в объединении с первой выходной шиной данных устройства образует первую (q + 1) - разрядную выходную информационную шину устройства.

- ближайшее целое число, не меньшее a) соединена с входами первого элемента ИЛИ, адресными входами блока ретрансляции сообщений и с первой группой входов коммутатора, третья группа (поле маршрутного кода) h выходов регистра (h - максимальная длина участка маршрута) подключена к входам второго элемента ИЛИ и к второй группе входов коммутатора, выход кода принимающего канала регистра соединен с первым входом седьмого элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, на входе "выбор кристалла" блока ретрансляции сообщений постоянно присутствует разрешающий (единичный) сигнал, группа r + h выходов (поля признака ретрансляции и маршрутного кода) блока ретрансляции сообщений подключена к третьей группе входов коммутатора, выходы которого подключены к первой и второй шинам маршрутного кода устройства, которые в объединении с второй и третьей выходными шинами данных устройства соответственно образуют вторую и третью (n - 1)-разрядные выходные информационные шины устройства, выход первого элемента ИЛИ подключен к первому входу четвертого элемента И и к первому входу пятого элемента И, выход второго элемента ИЛИ подключен к второму входу четвертого элемента И, к второму входу пятого элемента И, к второму входу третьего элемента ИЛИ, к второму входу седьмого элемента И и к первому входу коммутатора, выход четвертого элемента И подключен к первому входу третьего элемента ИЛИ, к первому входу восьмого элемента И и к второму входу коммутатора, второй вход восьмого элемента И соединен с выходом кода принимающего канала блока ретрансляции сообщений, выход восьмого элемента И подключен к второму входу четвертого элемента ИЛИ, выход которого подключен к первому и второму выходам кода принимающего канала устройства, выход третьего элемента ИЛИ подключен к первому входу шестого элемента И, выход которого подключен к второму и третьему выходам синхронизации приема сообщений устройства, выход пятого элемента И является первым выходом синхронизации приема сообщений устройства и в объединении с первой выходной шиной данных устройства образует первую (q + 1) - разрядную выходную информационную шину устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| SU, авторское свидетельство, 1575167, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| SU, ав торское свидетельство, 1783510, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| SU, авторское с видетельство, 1462279, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| SU, авторское свидетельст во, 1499469, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-07-27—Публикация

1996-04-24—Подача