Изобретение относится к электросвязи и может быть использовано в устройствах передачи и коммутации цифровых систем связи.

Целью изобретения является повышение достоверности передачи информации путем динамического перехода с одной скорости выдачи информации на другую и динамического согласования полосы асинхронизации для каждого канала индивидуально.

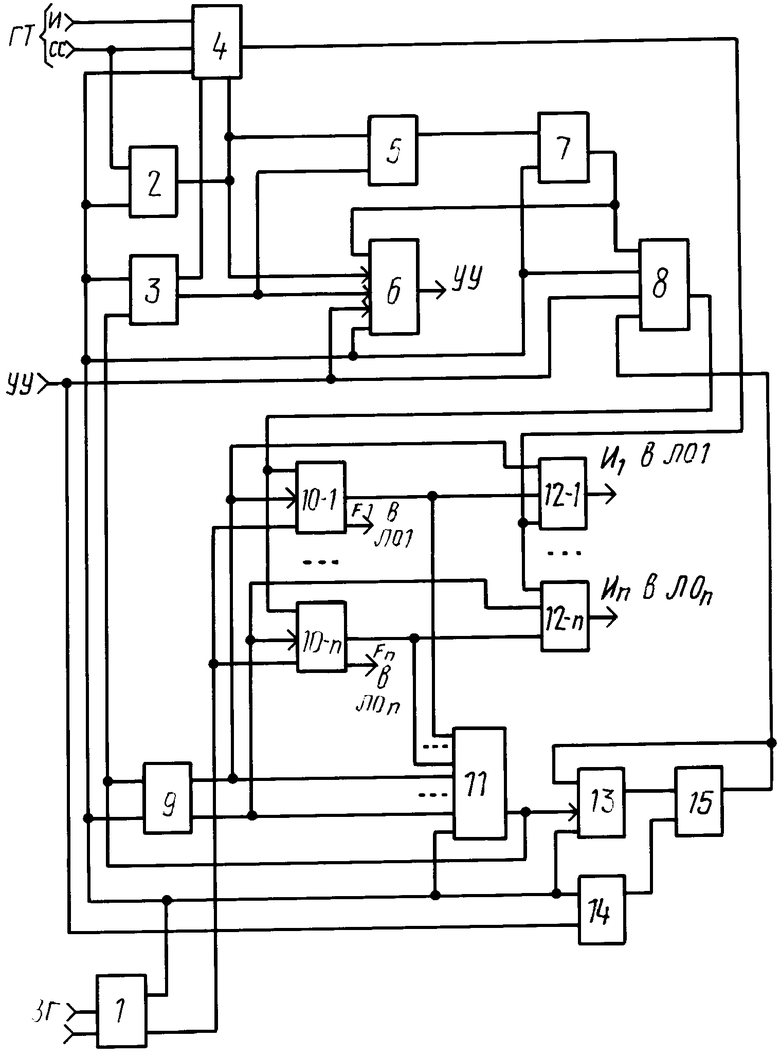

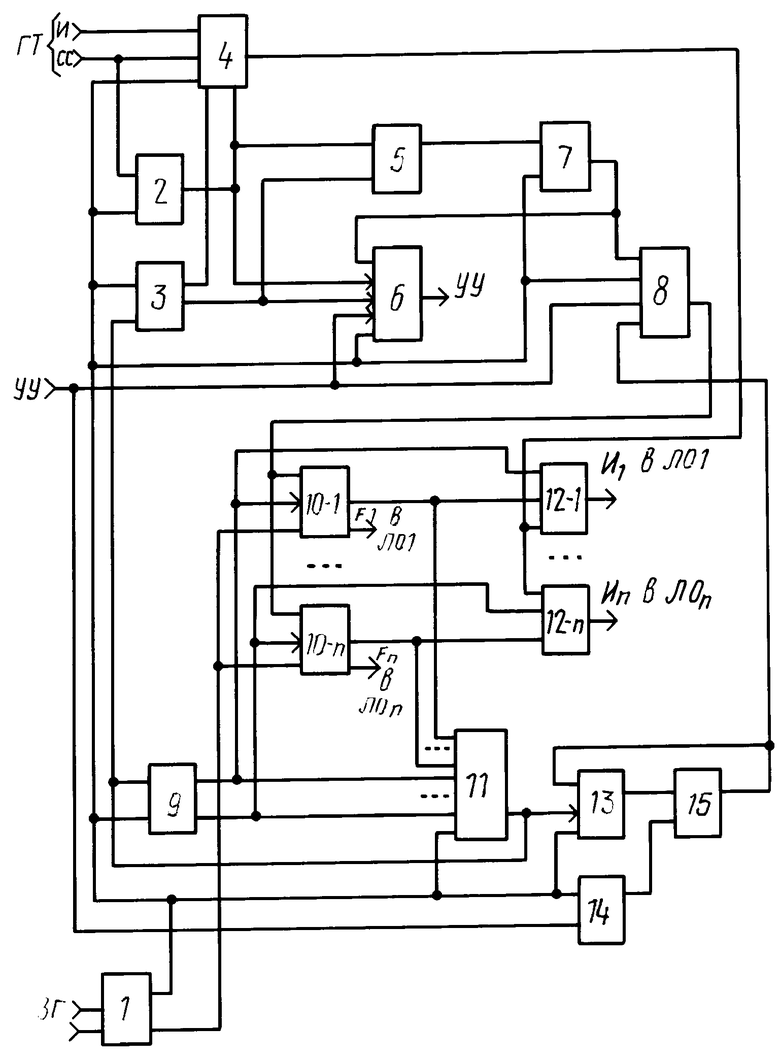

На чертеже представлена структурная электрическая схема устройства сопряжения асинхронных разноскоростных дискретных сигналов.

Устройство содержит счетчик 1, блок 2 записи, блок 3 чтения, блок 4 эластичной памяти, блок 5 формирования сигнала рассогласования, блок 6 интерфейса, блок 7 памяти сигнала рассогласования, блок 8 управления коэффициентом деления, дешифратор 9, n делителей 10-1 - 10-n частоты, блок 11 блокировки, n регистров 12-1 - 12-n, блоки 13 и 14 формирования шага коррекции и коэффициента коррекции и блок 15 сравнения.

Устройство сопряжения асинхронных разноскоростных дискретных сигналов работает следующим образом.

Групповой тракт (ГТ) использует синхронный побитный принцип формирования, когда каждой входящей линии связи в ГТ отводится свой канальный интервал (КИ): первой линии - первый КИ и т.д. Из-за асинхронного сопряжения ГТ с входными линиями поступающие сигналы передаются с сигналами сопровождения (СС) параллельно. Для передачи входного сигнала без потерь скорость КИ в ГТ должна быть на 1 - 4% выше скорости входного сигнала, поэтому один и тот же информационный бит в КИ и ГТ может передаваться многократно. При значении СС = 1 происходит первая передача бита. При повторных передачах того же бита СС = 0.

При приеме сигналов из ГТ устройство производит синхронные разуплотнения, поэтому оно не имеет внутренних блокировок и число КИ в ГТ n равно числу исходящих линий связи n. Поступающая информация в первом КИ ГТ выдается в первую исходящую линию и т.д. Для синхронизации работы устройства в ГТ на счетчик 1 поступают цикловая частота fц и высокая частота f, кратная несущей частоте fo ГТ и частотам выдачи информации в исходящие линии. Частота цикла fц синхронизирует работы входящего ГТ и устройства, устанавливая счетчик 1 циклически в нулевое состояние. Частота f поступает в делители 10-1 - 10-n.

Частоту fo, поступающую на счетный вход счетчика 1, получают путем деления частоты f. Счетчик 1 циклически вырабатывает адреса КИ ГТ с первого по n и соответственно адреса исходящих линий с первого по n. Число разрядов счетчика 1, используемых в качестве адресов, равно logn. Адреса со счетчика 1 и частота fо поступают в блоки 2, 3, 4, 6, 7, 8, 9, 11, 13 и 14, которые содержат ОЗУ. В перечисленных блоках устройства каждому КИ ГТ и соответственно каждой нисходящей линии отводится ячейка ОЗУ, определяемая адресом счетчика 1, а в блоках 4 и 8 - зона ОЗУ. Блоки работают в режиме чтения и записи, причем в такт t1, соответствующий положительному полупериоду частоты fo, производится чтение в ОЗУ, в такт t2, соответствующий отрицательному полупериоду частоты fо, - запись в ОЗУ.

В блоке 4 для каждого КИ ГТ и соответствующей исходящей линии отводится зона в n ячеек, которая разделена на четыре области: первая область - от 0 до К ячеек, вторая область - от К до  ячеек, третья область - от

ячеек, третья область - от  до l-К ячеек, четвертая область - от l-К до l ячеек, где К <

до l-К ячеек, четвертая область - от l-К до l ячеек, где К <  .

.

Величина l ограничивается объемом оборудования устройства и временем задержки сигнала в устройстве. Величина К зависит от числа переприемов на сети. Оптимальное значение параметров l и К при шести переприемах равно 16 и 4. При смещении заполнения зоны от  до К и от

до К и от  до l-К вторая и третья области используются как эластичная память. При этом информация считывается из зоны в исходящую линию на номинальной частоте Fном.

до l-К вторая и третья области используются как эластичная память. При этом информация считывается из зоны в исходящую линию на номинальной частоте Fном.

Полоса синхронизации устройства (ΔFу') в этом случае определяется из выражения

ΔFу'=Fном Кгу, (1) где Кгу - коэффициент нестабильности задающего генератора.

По достижении точек заполнения зоны К или l-К включается частота выдачи Fмин или Fмакс соответственно, отличающаяся от частоты выдачи Fном на величину ΔFу, т.е. на величину полосы синхронизации:

ΔFу= (Fном-Fмин)=(Fном-Fмакс), (2) вторая и третья области используются в этом случае как области подстройки.

Частоты выдачи определяются из выражений

Fном=  (3); Fмин=

(3); Fмин=  (4);

(4);

Fмакс=  (5), где Кдном - номинальный коэффициент деления;

(5), где Кдном - номинальный коэффициент деления;

Кдмин - минимальный коэффициент деления;

Кдмакс - максимальный коэффициент деления.

Для достоверной передачи информации полоса синхронизации устройства должна удовлетворять условиям по приему сигналов ΔFу.прм> Δ Fловх(6) и по передаче ΔFу< ΔFло (7).

Условие достоверного приема информации устройством (6) выполняется автоматически, так как скорость канала выше скорости входного потока не менее чем на 1-4%.

Для регулирования полосы синхронизации устройства по передаче ΔFувводится коэффициент коррекции (Кк), так как регулирование ΔFуизменением f и Кд исходя из выражений 2, 4, 5 нереализуемо для широкого набора скоростей выдачи. Для устройства полоса синхронизации зависит от Кд и Кк при f=const, т.е. ΔFу= ϕ (Кд, Кк).

После синхронизации устройства определяется из выражения

ΔF ,, (8) где ΔКд=|Кдном-Кдмин|= |Кдном-Кдмакс| .

,, (8) где ΔКд=|Кдном-Кдмин|= |Кдном-Кдмакс| .

Максимальное значение Кк определяют из выражения ,, откуда

,, откуда

.

.

Коэффициент коррекции показывает число выдаваемых битов информации d, из которых d-1 бит выдается на частоте Fном, а один бит - на частоте Fмакс или Fмин. Поэтому, увеличивая число Кк или соответственно число d, пропорционально уменьшают полосу ΔFу2 согласно выражению (8), выполняя условие (7). Обычно при подстройке во второй и третьей областях частоту синхронизации расширяют в 5 - 10 раз по сравнению с полосой ΔFу1, т.е. ΔFу2=(5-10) ΔFу1.

Для этого текущий коэффициент коррекции делают равным

Ккмакс=(5-10)Кк.

Первая и четвертая области в ОЗУ блока 4 используют как буферные области для устранения фазовых флуктуаций входного сигнала и как области подстройки полосы синхронизации ΔFу при переприемах сигнала на станциях. Полоса синхронизации входного потока может быть равна либо ΔFвх1 ≈ ΔFу1, либо ΔFвх2 ≈ ΔFу2. Если входной поток имеет полосу синхронизации ΔFвх1 ≈ ΔFу1, то при включении в устройство ΔFу2заполнение ОЗУ в блоке 4 всегда смещается в точке l/2 и перезаполнение ОЗУ не происходит, так как ΔFу2> ΔFвх1. Если входной поток имеет полосу синхронизации ΔFвх2, равную ΔFу2, то при включении в устройство ΔFу2 заполнение ОЗУ в блоке 4 находится в районе точки К либо l-К до тех пор, пока полоса синхронизации входного потока не станет равной ΔFвх1 ΔFу1, после чего заполнение ОЗУ в блоке смещается к точке l/2. Когда полоса асинхронизации входного потока равна ΔFвх2 ≈ ΔFу2, может наблюдаться смещение заполнения ОЗУ в блоке 4 от точки К к точке 0 либо от точки l-К к l. Для устранения данного смещения коэффициент коррекции в устройстве Кк постепенно либо уменьшают, либо увеличивают, тем самым расширяют либо сужают полосу синхронизации в устройстве ΔFу2, что означает соответственно увеличение либо уменьшение скорости считывания информации из ОЗУ блока 4, выполняя при этом условие ΔFло> ΔFу2.

При предельных значениях скорости считывания из ОЗУ блока 4 и скорости прихода информации в ОЗУ блока 4 время предельной скорости прихода информации в 5-10 раз меньше, чем время сползания заполнения ОЗУ блока 4 к точкам 0 и l при равенстве первой, второй, третьей и четвертой зон в ОЗУ блока 4. Далее следует уменьшение скорости прихода до номинальной, т.е. переход на полосу ΔFвх1 ≈ ΔFу1, и заполнение зоны в ОЗУ блока 4 смещается к точке l/2. Переполнение ОЗУ блока 4 не происходит.

Для заполнения ячеек памяти в зонах блока 4 служат блок 2 записи и блок 3 чтения, в которых для каждого КИ ГТ и каждой исходящей линии отводятся ячейки памяти, разрядность которых равна logl. В ячейках памяти блока 2 и блока 3 фиксируется последний адрес ячейки зоны блока 4, куда произошла запись информации из ГТ и откуда произошло считывание информации в исходящие линии соответственно. Запись информации и считывание информации производятся последовательно, последняя ячейка памяти сменяется первой, первая - второй и т.д.

По j-му адресу счетчика 1 в такт t1 из ОЗУ блоков 2 и 3 считываются соответственно адреса записи (Аз) и чтения (Ач), где они фиксируются в n регистрах 12. В такт t1 по считанному адресу Ач, поступающему непосредственно с выхода ОЗУ блока 3 на блок 4, и j-му адресу счетчика 1 из j-й зоны ОЗУ считывается бит информации, который записывается в регистр блока 4.

В такт t2 при наличии СС = 1 в j-м КИ ГТ в зону ОЗУ блока 4 по j-му адресу счетчика 1 и адресу Аз блока 2 из j-го КИ ГТ записывается бит информации. В такт t2 при СС = 1 в j-ю ячейку ОЗУ блока 2 записывается следующий адрес - Аз + 1, при СС = 0 - в j-й ячейке ОЗУ блока 3 чтения остается прежний адрес - Аз. Аналогично в такт t2 при сигнале обратной связи блока 11 ОС = 1 в j-ю ячейку ОЗУ блока 3 записывается новый адрес - Ач+1, при ОС= 0-в j-й ячейке ОЗУ остается прежний адрес - Ач. Каждой j-й исходящей линии принадлежит линейка устройств, состоящая из делителя 10-j и регистра 12-j. Информация из блока 4 поступает в регистры 12-1 - 12-n, в которых информационные биты хранятся до момента их выдачи в исходящие линии, после выдачи которых в них записываются следующие биты из блока 4. Коэффициент деления из блока 8 поступает на делители 10-1 - 10-n, которые вырабатывают такты выдачи, следующие с частотой выдачи, поступающие в регистры 12-1 - 12-n соответственно и блок 11, и частоты сопровождения информации - Fл, поступающие в ЛО для приема информации из устройства по стыку С2. Такты выдачи и частота Fл в делителе 10-j вырабатываются при совпадении кодов коэффициента деления и текущего времени, вырабатываемого счетчиком делителя из частоты f счетчика 1.

Процессом записи информации из блока 4 эластичной памяти в регистры 12-1 - 12-n и записью кодов коэффициентов деления из блока 8 в делители 10-1 - 10-n управляют сигналы выдачи путем подачи сигналов обратной связи (ОС) по общему тракту из блока 11 блокировки на блок 3 чтения, дешифратор 9, блок 14 формирования коэффициента коррекции. В блоке 11 блокировки сигнал ОС для j-й исходящей линии фиксируется по переднему фронту j-го сигнала выдачи. Опрос сигналов ОС производится адресами счетчика 1 циклически и синхронно с опросом остальных блоков. Для j-й исходящей линии в j-й временной позиции, определяемой адресом счетчика 1, сигнал ОС фиксируется на выходе блока 11 передним фронтом такта t2 и хранится до опроса следующего (j+1)-го сигнала. В блоке 3 чтения при ОС = 1 во время такта t2 в j-ю ячейку записывается следующий адрес чтения (Ач + 1), в блоке 13 - следующий порядковый номер выданного бита. В дешифраторе 9 при сигнале ОС = 1 на j-м выходе во время такта t2вырабатывается сигнал, равный единице, по заднему фронту которого в j-й делитель 10j записывается коэффициент деления из блока 8, в j-й регистр 12j - информационный бит из блока 4. В блоке 11 блокировки входной триггер 11j обнуляется, т.е. снимается сигнал ОС. Для исключения потери бита скорость опроса блоков устройства выше скорости выдачи информации в исходящие линии.

В ОЗУ блока 8 управления каждой j-й исходящий линии соответствует j-я зона в четыре ячейки, в которые из блока 8 записываются коэффициент деления во время такта t1. В ячейки зоны, определяемые адресами 00 и 11, записывается номинальный коэффициент деления - Кдном, в ячейку зоны, определяемую адресом 01, - минимальный коэффициент деления - Кдмин, в ячейку зоны, определяемую адресом 10, - максимальный коэффициент деления - Кдмакс.

Коэффициент деления определяется из выражений

K ; Кдмин=Кдном-1;

; Кдмин=Кдном-1;

Кдмакс=Кдном+1.

При смене скорости поступления информации в j-м канале ГТ блок 8 управления динамично переключает выходную скорость выдачи в j-ю линию, записывая в j-ю зону ОЗУ блока 8 соответствующие коэффициенты деления. Коэффициенты деления из j-й зоны блока 8 управления считываются сигналами рассогласования СР1 и СР2, вырабатываемыми блоком 5 формирования сигнала рассогласования и блоком 7 памяти сигнала рассогласования, в зависимости от заполнения j-й зоны блока 4 эластичной памяти, определяемой по адресам записи Аз блока 2 и чтения Ач блока 3. Для этого ПЗУ в блоке 5 формирования программируется по точкам заполнения зоны блока 4 -  , К, l-К следующим образом:

, К, l-К следующим образом:

Aз-Ar =

где l - глубина зоны эластичной памяти блока 4;

где l - глубина зоны эластичной памяти блока 4;

К <  ; СЗ - сигнал записи.

; СЗ - сигнал записи.

При абсолютной разности между адресами записи Аз и чтения Ач, равной половине зоны  , в ПЗУ записывается код 11, СЗ=1, что соответствует номинальному коэффициенту деления, записываемому по адресу 11 в зону блока 8 коэффициентов деления, по которому вырабатывается в делителе 10 номинальная частота выдачи Fном. При разности в К ячеек в ПЗУ записывается код 01, СЗ= 1, что соответствует Кдмин, записываемому по адресу 01 в зону блока 8, по которому вырабатывается в делителе 10 Fмакс. При разности в l-К ячеек в ПЗУ записывается код 10, СЗ = 1, что соответствует Кдмакс, записываемому по адресу 10 в зону блока 8, по которому в делителе 10 вырабатывается Fмин.

, в ПЗУ записывается код 11, СЗ=1, что соответствует номинальному коэффициенту деления, записываемому по адресу 11 в зону блока 8 коэффициентов деления, по которому вырабатывается в делителе 10 номинальная частота выдачи Fном. При разности в К ячеек в ПЗУ записывается код 01, СЗ= 1, что соответствует Кдмин, записываемому по адресу 01 в зону блока 8, по которому вырабатывается в делителе 10 Fмакс. При разности в l-К ячеек в ПЗУ записывается код 10, СЗ = 1, что соответствует Кдмакс, записываемому по адресу 10 в зону блока 8, по которому в делителе 10 вырабатывается Fмин.

Сигналы рассогласования циклически переписываются из блока 5 формирования сигнала рассогласования по СЗ=1 в ОЗУ блока 7 памяти сигнала рассогласования по адресам счетчика 1. В ОЗУ блока 7 памяти каждой j-й исходящей линии соответствует j-я ячейка памяти, поэтому по j-му адресу счетчика 1 во время такта t1 из блоков 2 и 3 считываются соответственно адреса записи Аз и чтения Ач. Во время такта t2 из ПЗУ блока 5 по адресам Аз и Ач считываются коды сигналов рассогласования СР1и СР2 и значение СЗ. При СЗ = 1 во время такта t2 в j-ю ячейку ОЗУ блока 7 памяти из ПЗУ блока 5 формирования переписываются сигналы рассогласования СР1 и СР2. В свою очередь ОЗУ блока 7 памяти циклически и синхронно с остальными блоками опрашивается адресами счетчика 1. По j-му адресу счетчика 1 во время такта t1 из ОЗУ блока 7 считываются сигналы рассогласования, по которым из j-й зоны ОЗУ блока 8 управления считываются коэффициенты деления во время такта t2, поступающие в делитель 10j, куда записываются по заднему фронту t2 при наличии j-го сигнала из дешифратора 9.

Полоса синхронизации для каждой исходящей линии 1-n регулируется частотой поступления сигнала коррекции СК из блока 15 сравнения в блок 8 управления. При СК = 0 по j-му адресу счетчика 1 производится обращение к ячейке 00 зоны ОЗУ блока управления, откуда считывается Кдном. При СК = 1, при коде сигнала рассогласования 11 считывается Кдном, при коде 01 - Кдмин, при коде 10 - Кдмакс. Частота поступления СК = 1 или регулирование полосы синхронизации путем считывания из ОЗУ блока 8 Кдминили Кдмакс и соответственно выдача информации по j-й линии на частоте Fмакс или Fмин задаются кодом коэффициента коррекции, записываемым в j-ю ячейку ОЗУ блока 14 по j-му адресу блока 8.

Текущее число битов информации, выдаваемых на частоте Fном, определяется в блоке 13 формирования шага коррекции, вырабатывая текущий код шага коррекции - Кшк для каждой j-й линии устройства, путем суммирования числа выданных битов информации для каждой (1-n)-й линии устройства по сигналам ОС, поступающим из блока 11 блокировки. При равенстве кодов коэффициентов коррекции Кк и текущего шага коррекции Кшк, сравниваемых в блоке 15 сравнения, вырабатывается СК= 1, поступающий в блок 13 и блок 8 управления. В блоке 13 при СК=0 и сигнале ОС = 0 блока 11 Кшк остается прежним, при СК = 0 и ОС = 1 код шага коррекции увеличивается на единицу, т.е. Кшк + 1, при СК = 1 код шага коррекции обнуляется.

Для этого в ОЗУ блоков 14 и 13 формирования коэффициента коррекции и шага коррекции каждой j-й исходящей линии соответствует j-я ячейка памяти, опрос блоков производится циклически и синхронно с остальными блоками устройства адресами счетчика 1. По j-му адресу счетчика 1 во время такта t1 из j-й ячейки ОЗУ блока 13 и j-й ячейки ОЗУ блока 14 считываются соответственно коды Кк и Кшк, поступающие на блок 15 сравнения, где при неравенстве кодов во время такта t2 вырабатывается СК=0, при равенстве кодов - СК = 1. Сигнал ОС из блока 11 блокировки поступает для j-й исходящей линии во время такта t2 в блок 13, где при СК = 0 и ОС = 1 происходит запись в j-ю ячейку ОЗУ блока 13 формирования шага коррекции, увеличенного на единицу, т.е. Кшк + 1, при ОС = 0 в j-й ячейке ОЗУ остается прежний адрес, а при СК = 1 в j-й ячейке ОЗУ независимо от значения сигнала ОС слово обнуляется.

Если в j-ю ячейку ОЗУ блока 7 памяти сигнала рассогласования записан код рассогласования 11, то управляющий сигнал полосу синхронизации не регулирует, т. е. в j-й ячейке ОЗУ блока 13 может находиться любой код коэффициентов коррекции, так как при СК = 0 из j-й зоны ОЗУ по адресу 00 считывается Кдном, при СК = 1 из j-й зоны ОЗУ по адресу 11 считывается также Кдном. Информация выдается в j-ю исходящую линию на номинальной частоте, и заполнение j-й зоны ОЗУ блока 4 эластичной памяти смещается от точки  к К либо к l-К. Регулирование полосы синхронизации осуществляется после записи в j-ю ячейку ОЗУ блока 7 памяти сигнала рассогласования кода рассогласования 01 либо 10, когда заполнение j-й зоны ОЗУ блока 4 достигает соответственно К либо l-К ячеек.

к К либо к l-К. Регулирование полосы синхронизации осуществляется после записи в j-ю ячейку ОЗУ блока 7 памяти сигнала рассогласования кода рассогласования 01 либо 10, когда заполнение j-й зоны ОЗУ блока 4 достигает соответственно К либо l-К ячеек.

Код коэффициентов коррекции, регулирующий полосу синхронизации, зависит от скорости входного потока, нестабильности генератора входного потока и полосы синхронизации линейного оборудования. Для смещения заполнения j-й зоны ОЗУ блока 4 из точки заполнения К либо l-К ячеек в середину зоны  ячеек достаточно, чтобы полоса синхронизации устройства превосходила полосу синхронизации входного потока в 5-10 раз, т.е. ΔFу = (5 - 10) x x ΔFвх, при этом коэффициент коррекции должен иметь пределы изменения от нуля до 1000 раз и иметь десять разрядов. В этом случае полоса синхронизации устройства, определяемая из выражения ΔFу=|ΔFном - -ΔFмин| = |ΔFном - Fмакс | , регулируется от Δ Fу до ΔFу 10-3.

ячеек достаточно, чтобы полоса синхронизации устройства превосходила полосу синхронизации входного потока в 5-10 раз, т.е. ΔFу = (5 - 10) x x ΔFвх, при этом коэффициент коррекции должен иметь пределы изменения от нуля до 1000 раз и иметь десять разрядов. В этом случае полоса синхронизации устройства, определяемая из выражения ΔFу=|ΔFном - -ΔFмин| = |ΔFном - Fмакс | , регулируется от Δ Fу до ΔFу 10-3.

В случае низкой нестабильности генераторов и низкой скорости передачи полосу синхронизации устройства расширяют путем увеличения разности коэффициентов деления ΔКд до 2,3 и т.д. раз. При высокой скорости входного потока, высокой стабильности генераторов и узкой полосе синхронизации ЛО, равной долям герц, полосу синхронизации устройства сужают путем увеличения числа разрядов кода коэффициентов коррекции с 10 до 11, 12 и более разрядов, что соответствует уменьшению полосы синхронизации устройства в 2000, 4000 и менее раз.

Контролируют и динамично регулируют полосу синхронизации устройства посредством считывания из устройства через блок 6 интерфейса кодов адресов записи Аз блока 2, чтения Ач блока 3 и сигналов рассогласования СР блока 7 памяти, для чтения которых выставляют j-й адрес и команду. В блоке 6 при равенстве j-го адреса блока 8 и j-го текущего адреса счетчика 1 фиксируются в регистре адреса Аз, Ач, СР, характеризующие заполнение j-й зоны ОЗУ блока 4.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство коммутации с эластичной памятью | 1988 |

|

SU1647921A1 |

| Устройство коммутации асинхронных цифровых сигналов | 1985 |

|

SU1241522A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ЦИФРОВЫХ СИГНАЛОВ | 1991 |

|

RU2020764C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| УСТРОЙСТВО СОПРОВОЖДЕНИЯ ТРАЕКТОРИИ ДВИЖУЩИХСЯ ОБЪЕКТОВ | 1994 |

|

RU2079150C1 |

| Ультразвуковой дефектоскоп | 1990 |

|

SU1746298A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1991 |

|

RU2077415C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство сопряжения асинхронных разноскоростных цифровых сигналов | 1990 |

|

SU1755386A1 |

Использование: в технике электросвязи, в частности в устройствах передачи и коммутации цифровых систем связи. Сущность изобретения: устройство сопряжения асинхронных разноскоростных дискретных сигналов содержит счетчик 1, блок 2 записи, блок 3 чтения, блок 4 эластичной памяти, блок 5 формирования сигнала рассогласования, блок 6 интерфейса, блок 7 памяти сигнала рассогласования, блок 8 управления коэффициентом деления, дешифратор 9, n делителей 10= 1-10= n частоты, блок 11 блокировки, n регистров 12-1 - 12-n, блоки 13 и 14 формирования шага коррекции и коэффициента коррекции и блок 15 сравнения. Устройство обеспечивает повышение достоверности передачи информации путем динамического перехода с одной скорости выдачи информации на другую и динамического согласования полосы синхронизации для каждого канала индивидуально. 1 ил.

УСТРОЙСТВО СОПРЯЖЕНИЯ АСИНХРОННЫХ РАЗНОСКОРОСТНЫХ ДИСКРЕТНЫХ СИГНАЛОВ, содержащее блок эластичной памяти, выход которого соединен с первыми входами n регистров, вторые входы которых соединены с соответствующими входами блока блокировки и с соответствующими выходами дешифратора, первый вход которого соединен с первыми входами блока записи и блока чтения, с управляющим входом блока блокировки и с первым выходом счетчика, выход блока блокировки соединен с вторым входом блока чтения, первый выход которого соединен с первым входом блока эластичной памяти, второй вход которого соединен с выходом блока записи, а третий и четвертый входы блока эластичной памяти являются соответственно информационным входом и входом сигнала сопровождения, а входы счетчика являются входами сигнала цикловой синхронизации и сигнала высокой частоты, а также блок сравнения, n делителей частоты и блок управления коэффициентом деления, отличающееся тем, что в него введены последовательно соединенные блок формирования сигнала рассогласования, блок памяти сигнала рассогласования и блок интерфейса, а также блок формирования шага коррекции и блок формирования коэффициента коррекции, при этом выход блока записи и второй выход блока чтения соединены с соответствующими входами блока формирования сигнала рассогласования, выход блока памяти сигнала рассогласования через блок управления коэффициентом деления соединен с первыми входами n делителей частоты, выходы которых соединены с третьими входами соответствующих регистров и с соответствующими дополнительными входами блока блокировки, выход которого соединен с вторым входом дешифратора и с первым входом блока формирования шага коррекции, выход которого соединен с первым входом блока сравнения, второй вход которого соединен с выходом блока формирования коэффициента коррекции, а выход блока сравнения соединен с вторым входом блока формирования шага коррекции и с вторым входом блока управления коэффициентом деления, первый выход счетчика соединен с первым входом блока формирования коэффициента коррекции, с третьим входом блока формирования шага коррекции, с вторым входом блока памяти сигнала рассогласования, с третьим входом блока управления коэффициентом деления и с вторым входом блока интерфейса, к двум другим входам которого подключены соответственно второй выход блока чтения и выход блока записи, второй вход которого соединен с четвертым входом блока эластичной памяти, управляющий вход которого соединен с первым выходом счетчика, второй выход которого соединен с вторыми входами n делителей частоты, к третьим входам которых подключены соответствующие выходы дешифратора, причем управляющие входы блока управления коэффициентом деления, блока интерфейса и блока формирования коэффициента коррекции соединены между собой и являются входом управляющего сигнала устройства, выходом управляющего сигнала, первой и второй группами выходов которого являются соответственно выход блока интерфейса, выходы n регистров и дополнительные выходы n делителей частоты.

Авторы

Даты

1994-06-15—Публикация

1991-07-15—Подача