мультиплексор 8 логических условий, элементы ИЛИ 9, 10, коммутатор условия 11, регистр контроля 12, блок сравнения 13, триггер 14 задания режимов работы, элементы И 15, 16 Сущность изобретения состоит в уменьшении времени контроля за счет обеспечения перехода по дополнительным логическим условиям в процессе контроля. 7 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1365082A1 |

| Система для программного управления резервированными объектами и их диагностирования | 1989 |

|

SU1741295A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1649539A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

Изобретение относится к айтЪмйтике и вычислительной технике и может быть использовано при разработке средств контро- ля и отладки сложных программно- технических комплексов

Известно устройство для контроля программ, содержащее блок памяти, регистры, мультиплексоры, счетчик, коммутатор адреса, генератор, триггер, элементы И, ИЛИ.

Недостатком этого устройства является низкая достоверность контроля.

Известно устройство управления с контролем, содержащее блок постоянной памяти, регистры адреса и микроопераций, коммутатор адреса, мультиплексор логических условий, триггер пуска, генератор тактовых импульсов, триггер ошибки, элемент НЕ и элемент ИЛИ.

Недостатком прототипа является большое время контроля, обусловленное отсутствием средств выбора кратчайшего маршрута прохождения программы контроля, что приводит к многократному прохождению линейных участков программы. Данное устройство обладает существенной временной избыточностью при реализации контроля программ

Целью изобретения является повышение оперативности контроля.

Сущность изобретения состоит в уменьшении времени контроля путем введения аппаратных и программных средств, обеспечивающих механизм перехода по дополнительным логическим условиям в процессе контроля

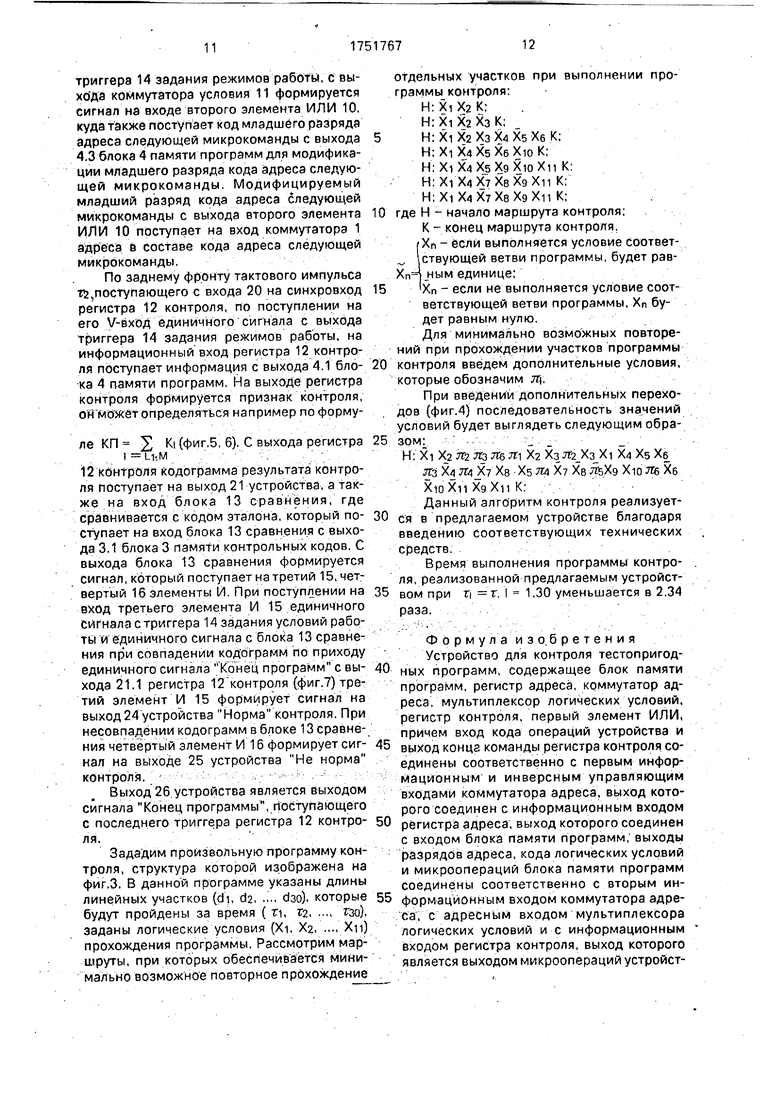

Рассмотрим программу, описываемую следующей ЛСА.

Ai A2Xir1 AsAfiA У Ак4 Ам:

ГА12А13 wf, 4гАаХз13Аэ 13АцА2 со, где А - оператор команд (микрокоманд);

XXi - проверяемые логические условия;

г - переход при невыполнении логического условия (цифра сверху указывает точку перехода к следующей микрокоманде); . со -„..безусловный переход.

Программу контроля для данного алгоритма рвг Тюлном переборе ветвей можно

выполнить за 27 тактов Введем логические условия п, лг Тогда алгоритм выполнения данной программы будет описываться так- Ait A2Xit1 АзА-q |4 X2 +2 АбАеАу л 2

Ав15Хз13АвАю Л т5 3А11аИ

4 Ai2Ai3Ai4;

При задании последовательности условий Х1-1.Х2- 1. ЛП 1,Х2 0 Хз 1, Л1

0 0, лг 1, Хз 0, Xi 0 обеспечивается полный, практически бесповторный перебор всех ветвей программы, что соответствует 14 тактам выполнения программы контроля Реализацию данного способа вы5 полнения программы контроля можно выполнить путем введения дополнительных аппаратных средств, обеспечивающих задание различных логических условий прохождения программы контроля сравнение

0 результатов контроля с эталоном; реализацию двух режимов работы устройства Контроль и Управление, определение результатов контроля путем реализации выходов Норма, Не норма контроля, опре5 деление конца программы контроля для осуществления наладки программ

Сущность изобретения реализуется за счет совокупности следующих конструктивных признаков (новых элементов и новых

0 связей):

введение блока памяти контрольных кодоа позволяет формировать код эталона результатов контроля и код заданных условий,

5 введение первого элемента И позволяет обеспечить запись кода заданных условий поступающего из блока памяти контрольных кодов в сдвигающий регистр по заднему фронту тактового импульса TY,

0 введение второго элемента И позволяет обеспечить сдвиг информации, записанный в сдвигающий регистр по приходу единичного сигнала с первого элемента ИЛИ по заднему фронту тактового импульса п:

введение сдвигающего регистра позволяет формировать единичный или нулевой

сигнал в зависимости от кода задержки условий на вход коммутатора условий,

введение коммутатора условия позволяет формировать единичный или нулевой

сигнал в зависимости от поступающих на его входы сигналов с мультиплексора логических условий, триггера задания режимов работы, первого элемента ИЛИ и сдвигающего регистра;

введение блока сравнения позволяет сравнить код эталона, поступающего с блока памяти контрольных кодов, с кодом результатов контроля, поступающего с регистра контроля;

введение триггера задания режимов ра- , боты устройства позволяет выбрать режим работы устройства Управление или Контроль ;

введение третьего и четвертого элемента И позволяет определить Норму контроля при совпадении кодограмм в блоке сравнения и Не норму контроля при их несовпадении.

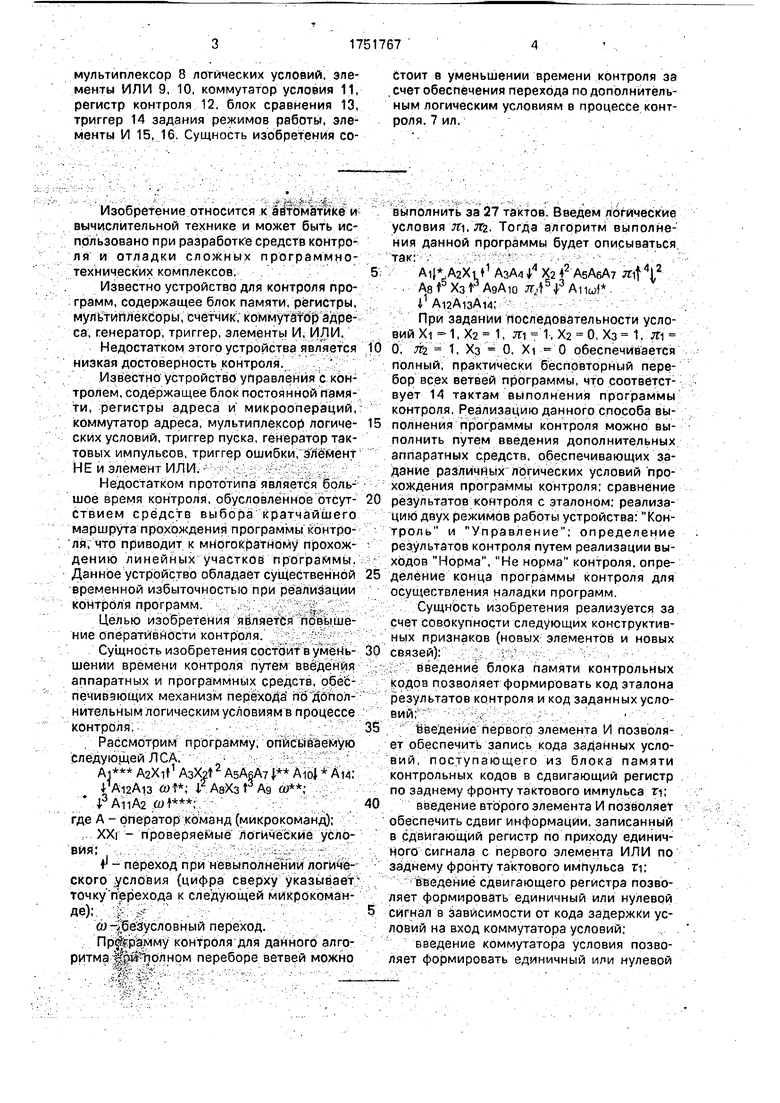

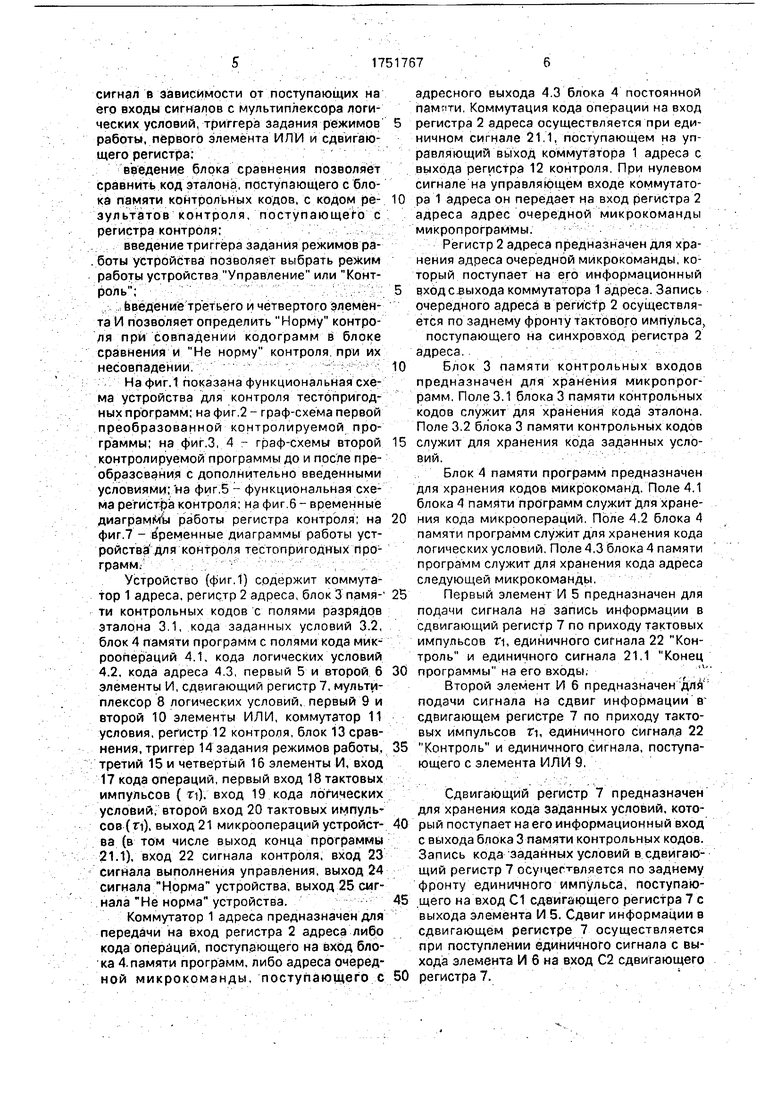

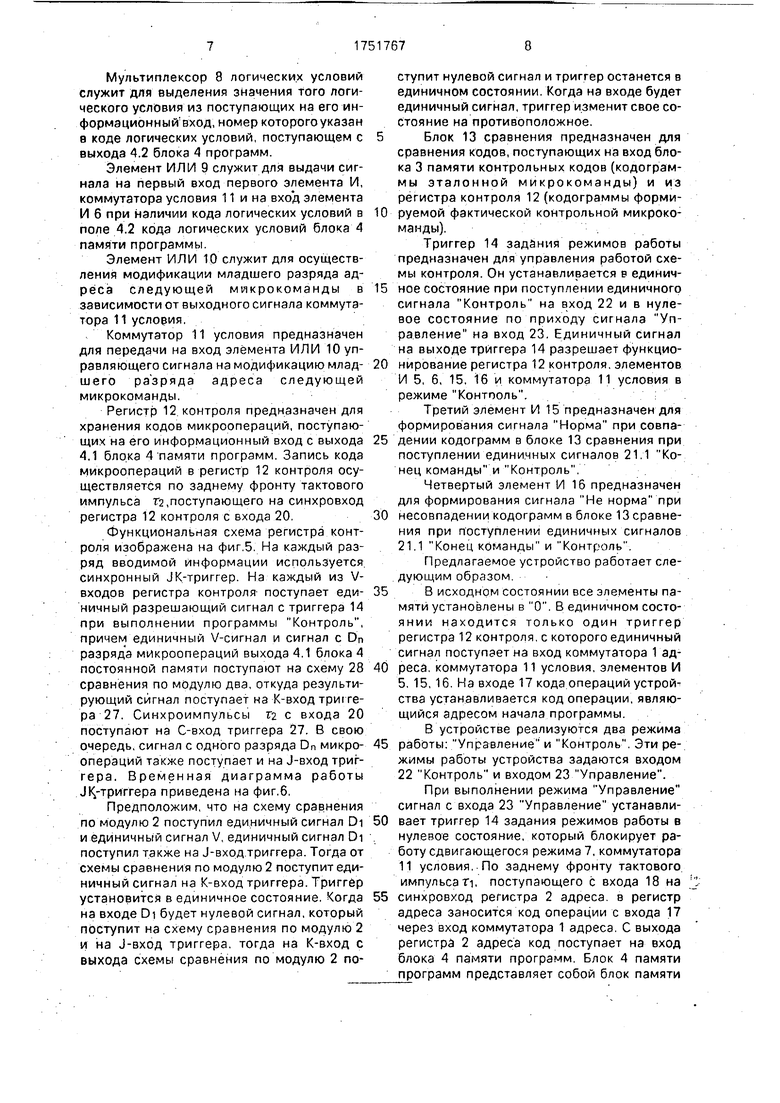

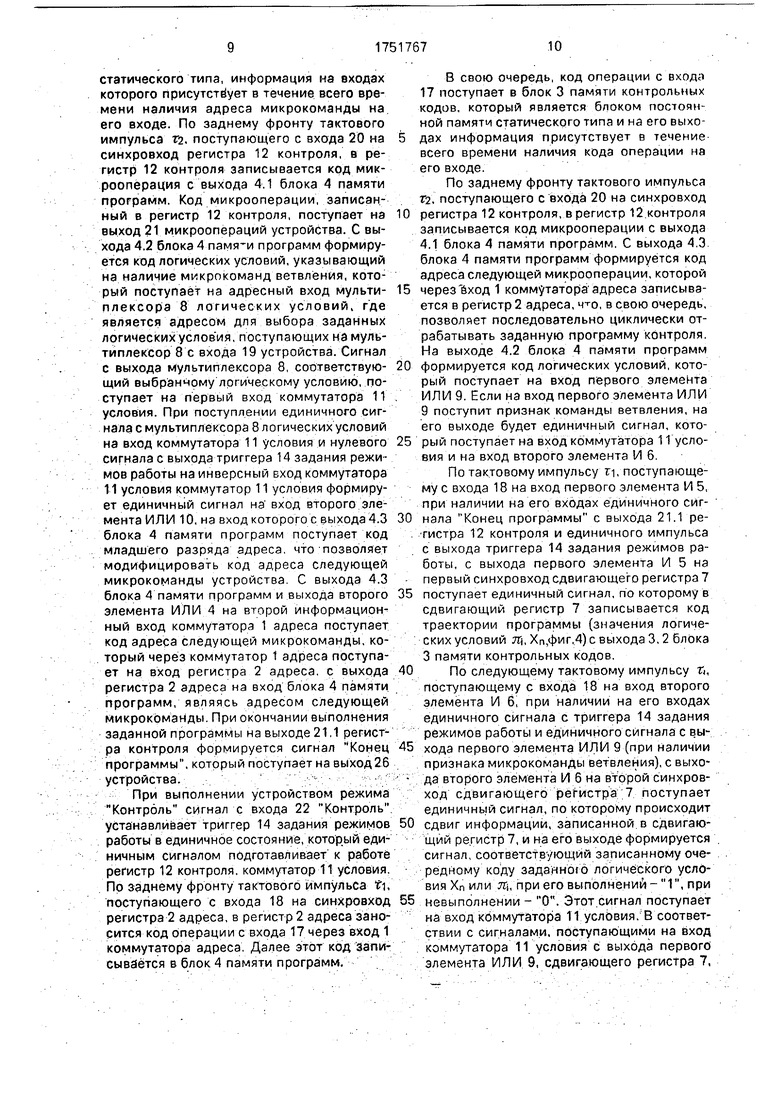

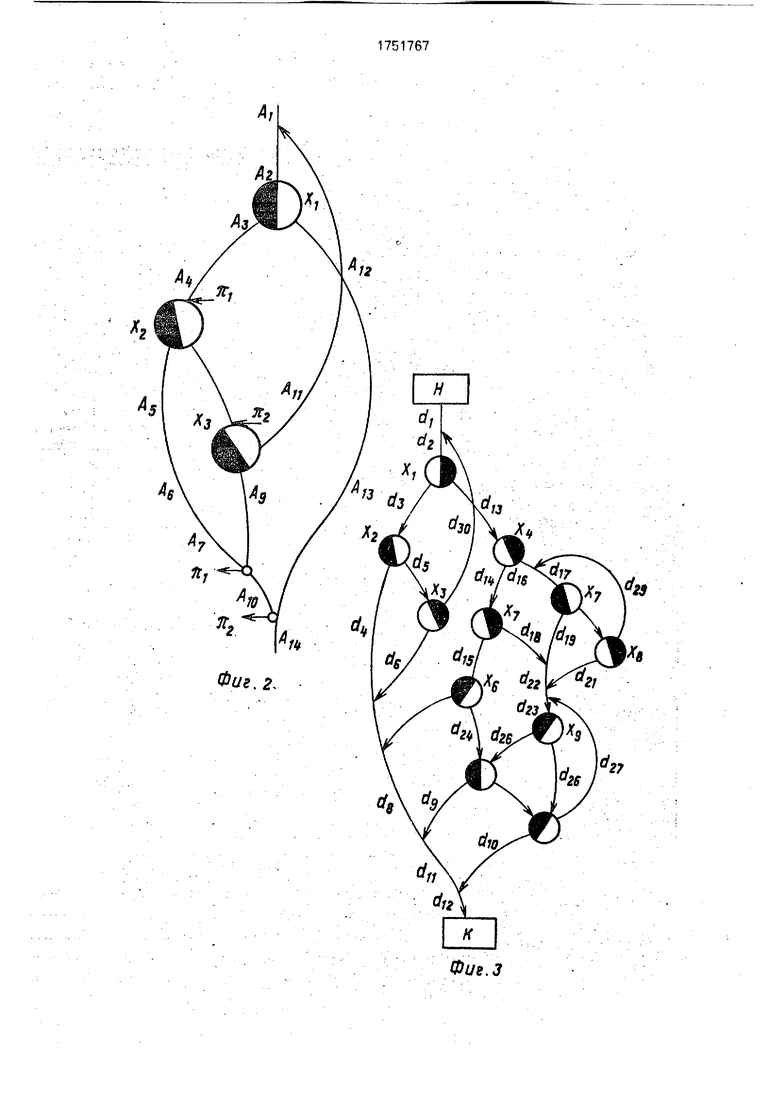

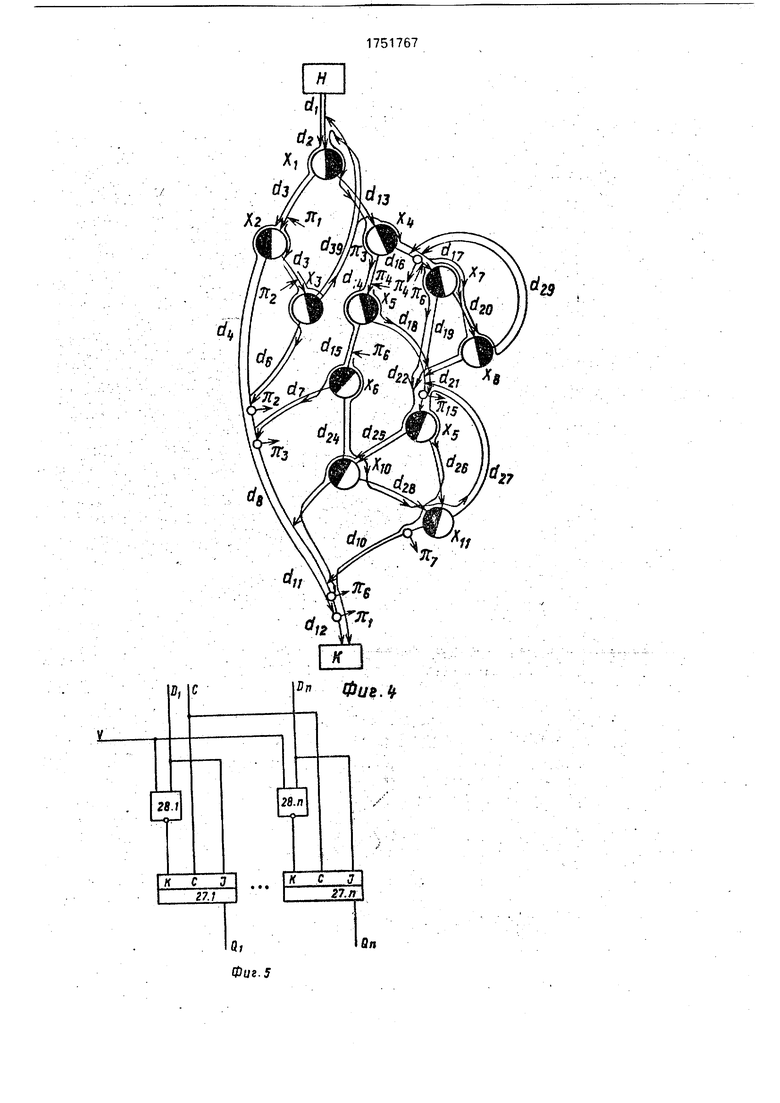

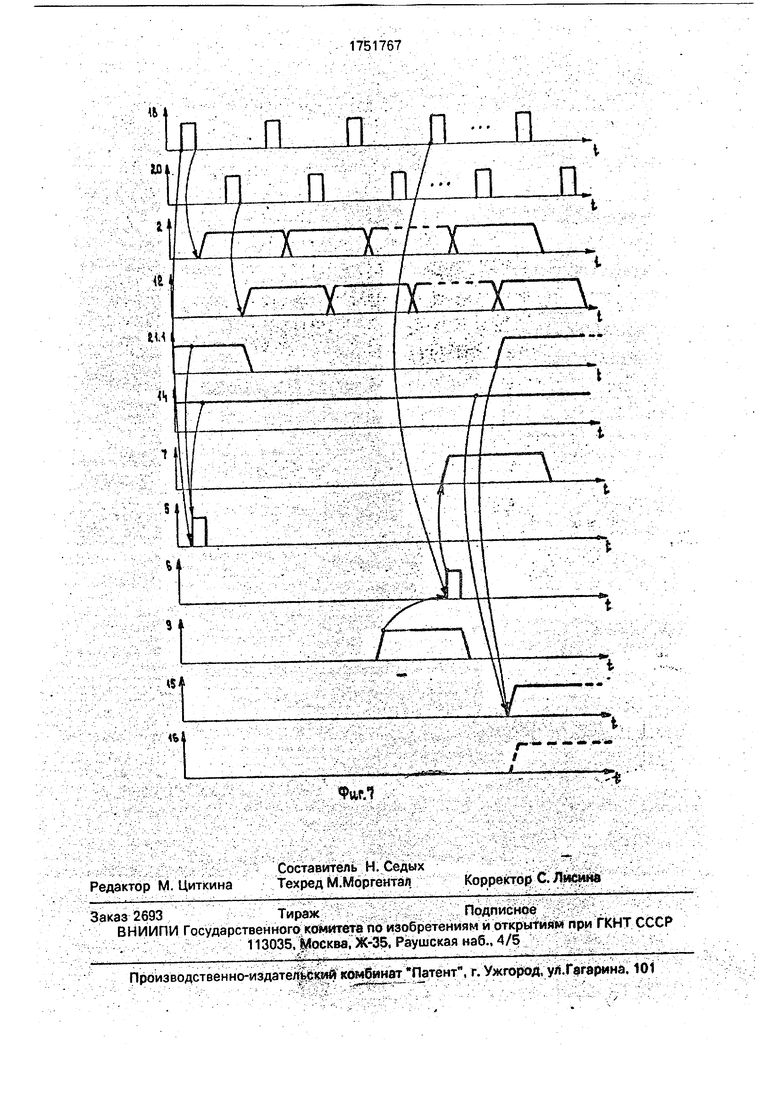

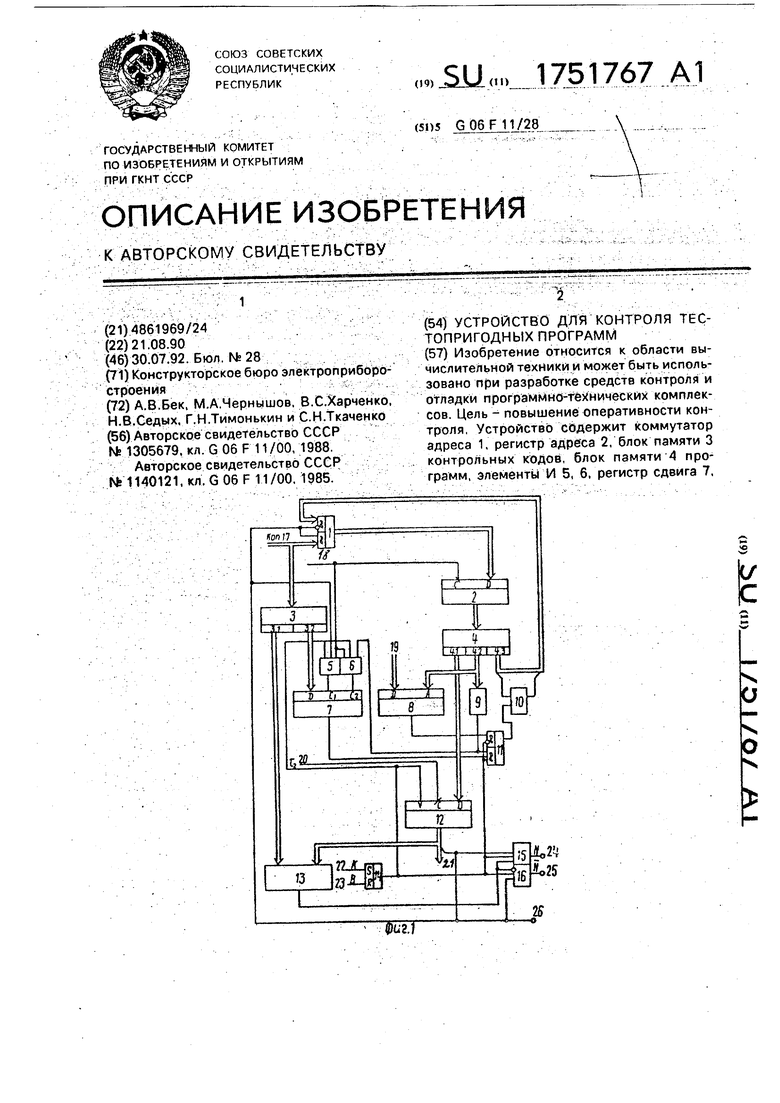

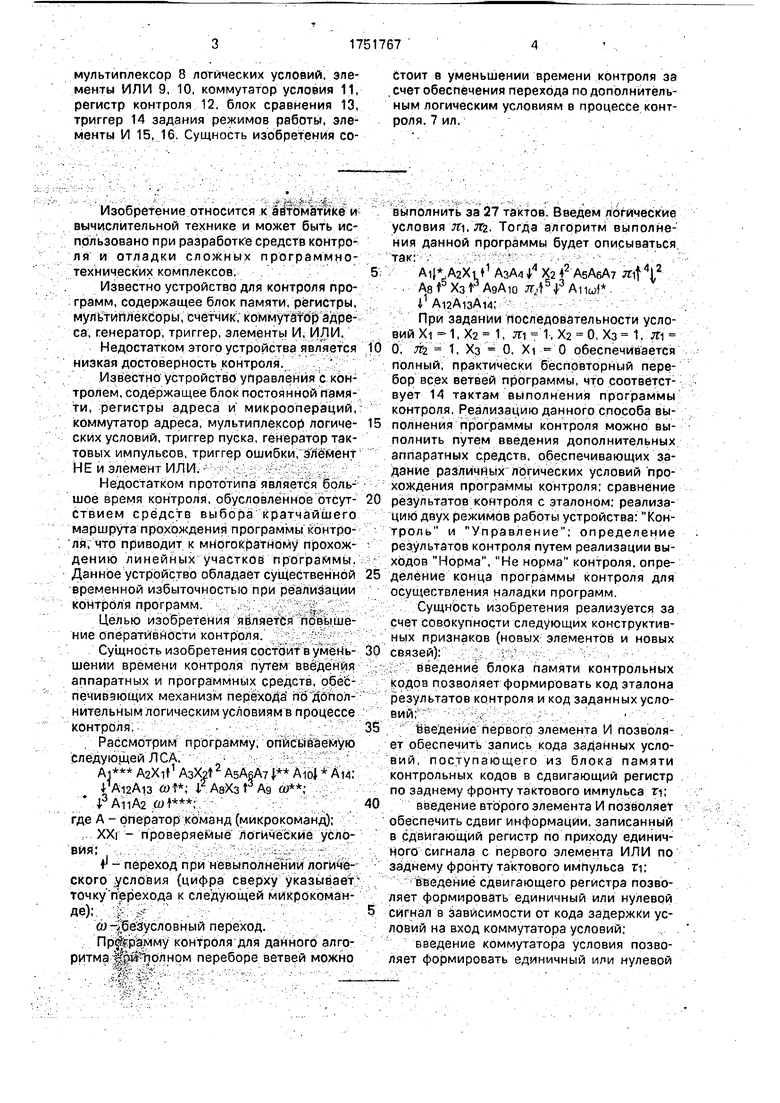

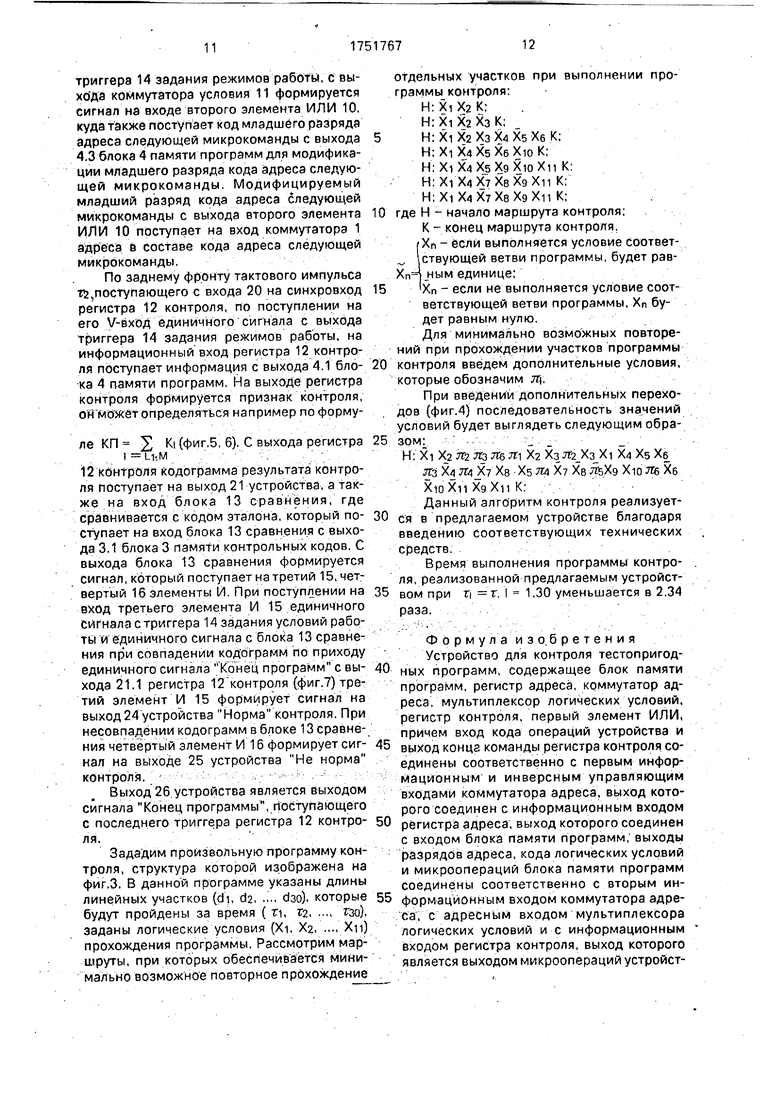

На фиг.1 показана функциональная схема устройства для контроля тестопригод- ных программ; на фиг.2 - граф-схема первой преобразованной контролируемой программы; на фиг.З, 4 - граф-схемы второй контролируемой программы до и после преобразования с дополнительно введенными условиями; на фиг,5 - функциональная схема регистра контроля; на фиг 6 - временные диаграммы работы регистра контроля; на фиг.7 - в ременные диаграммы работы устройства для контроля тестопригодных программ.

Устройство (фиг.1) содержит коммутатор 1 адреса, регистр 2 адреса, блок 3 памя- ти контрольных кодов с полями разрядов эталона 3.1, кода заданных условий 3.2, блок 4 памяти программ с полями кода микроопераций 4.1, кода логических условий 4.2, кода адреса 4.3, первый 5 и второй 6 элементы И, сдвигающий регистр 7, мультиплексор 8 логических условий, первый 9 и второй 10 элементы ИЛИ, коммутатор 11 условия, регистр 12 контроля, блок 13 сравнения, триггер 14 задания режимов работы, третий 15 и четвертый 16 элементы И, вход 17 кода операций, первый вход 18 тактовых импульсов { п). вход 19 кода логических условий, второй вход 20 тактовых импульсов (ri), выход 21 микроопераций устройства (в том числе выход конца программы 21.1). вход 22 сигнала контроля, вход 23 сигнала выполнения управления, выход 24 сигнала Норма устройства, выход 25 сигнала Не норма устройства.

Коммутатор 1 адреса предназначен для передачи на вход регистра 2 адреса либо кода операций, поступающего на вход блока 4.памяти программ, либо адреса очередной микрокоманды, поступающего с

адресного выхода 4.3 блока 4 постоянной пампти. Коммутация кода операции на вход

регистра 2 адреса осуществляется при единичном сигнале 21.1, поступающем на управляющий выход коммутатора 1 адреса с выхода регистра 12 контроля. При нулевом сигнале на управляющем входе коммутатора 1 адреса он передает на вход регистра 2 адреса адрес очередной микрокоманды микропрограммы.

Регистр 2 адреса предназначен для хранения адреса очередной микрокоманды, который поступает на его информационный

вход С-выхода коммутатора 1 адреса. Запись очередного адреса в регистр 2 осуществляется по заднему фронту тактового импульса, поступающего на синхровход регистра 2 адреса.

Блок 3 памяти контрольных входов предназначен для хранения микропрограмм. Поле 3.1 блока 3 памяти контрольных кодов служит для хранения кода эталона. Поле 3.2 блока 3 памяти контрольных кодов

служит для хранения кода заданных условий.

Блок 4 памяти программ предназначен для хранения кодов микрокоманд. Поле 4.1 блока 4 памяти программ служит для хранения кода микроопераций. Поле 4.2 блока 4 памяти программ служит для хранения кода логических условий. Поле 4.3 блока 4 памяти программ служит для хранения кода адреса следующей микрокоманды.

Первый элемент И 5 предназначен для подачи сигнала на запись информации в сдвигающий регистр 7 по приходу тактовых импульсов л, единичного сигнала 22 Контроль и единичного сигнала 21.1 Конец

программы на его входы,ll

Второй элемент И б предназначен для подачи сигнала на сдвиг информации в сдвигающем регистре 7 по приходу тактовых импульсов л, единичного сигнала 22

Контроль и единичного сигнала, поступающего с элемента ИЛИ 9.

Сдвигающий регистр 7 предназначен для хранения кода заданных условий, который поступает на его информационный вход с выхода блока 3 памяти контрольных кодов. Запись кода заданных условий в сдвигающий регистр 7 осуществляется по заднему фронту единичного импульса, поступающего на вход С1 сдвигающего регистра 7 с выхода элемента И 5. Сдвиг информации в сдвигающем регистре 7 осуществляется при поступлении единичного сигнала с выхода элемента И б на вход С2 сдвигающего

регистра 7.

Мультиплексор 8 логических условий служит для выделения значения того логического условия из поступающих на его информационный вход, номер которого указан в коде логических условий, поступающем с выхода 4.2 блока 4 программ.

Элемент ИЛИ 9 служит для выдачи сигнала на первый вход первого элемента И, коммутатора условия 11 и на вход элемента И 6 при наличии кода логических условий в поле 4.2 кода логических условий блока 4 памяти программы.

Элемент ИЛИ 10 служит для осуществления модификации младшего разряда адреса следующей микрокоманды в зависимости от выходного сигнала коммутатора 11 условия.

Коммутатор 11 условия предназначен для передачи на вход элемента ИЛИ 10 управляющего сигнала на модификацию младшего разряда адреса следующей микрокоманды.

Регистр 12 контроля предназначен для хранения кодов микроопераций, поступающих на его информационный вход с выхода 4.1 блока 4 памяти программ. Запись кода микроопераций в регистр 12 контроля осуществляется по заднему фронту тактового импульса Гз,поступающего на синхровход регистра 12 контроля с входа 20.

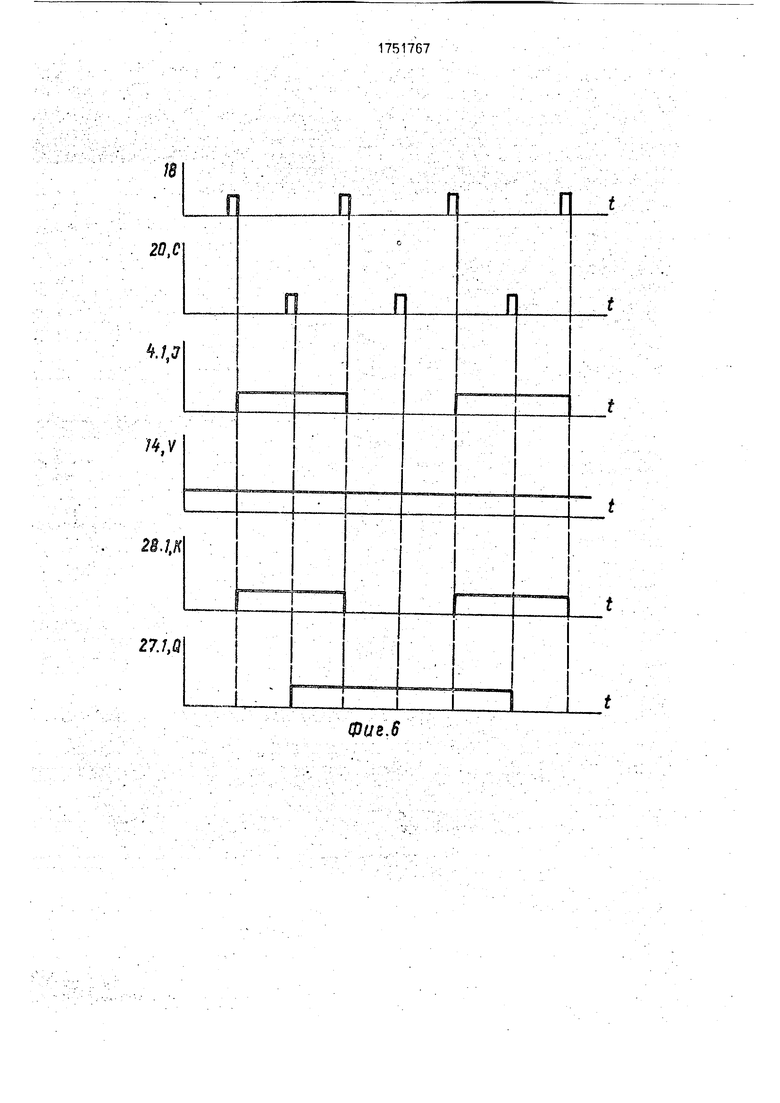

Функциональная схема регистра контроля изображена на фиг.5. На каждый разряд вводимой информации используется синхронный JK-триггер. На каждый из V- входов регистра контроля поступает единичный разрешающий сигнал с триггера 14 при выполнении программы Контроль, причем единичный V-сигнал и сигнал с Dn разряда микроопераций выхода 4.1 блока 4 постоянной памяти поступают на схему 28 сравнения по модулю два, откуда результирующий сигнал поступает на К-вход три ге- ра 27. Синхроимпульсы тг с входа 20 поступают на С-вход триггера 27. В свою очередь, сигнал с одного разряда Dn микроопераций также поступает и на J-вход триггера. Временная диаграмма работы JK/триггера приведена на фиг.6.

Предположим, что на схему сравнения по модулю 2 поступил единичный сигнал DI и единичный сигнал V, единичный сигнал Di поступил также на J-вход триггера. Тогда от схемы сравнения по модулю 2 поступит единичный сигнал на К-вход триггера. Триггер установится в единичное состояние. Когда на входе Di будет нулевой сигнал, который поступит на схему сравнения по модулю 2 и на J-вход триггера, тогда на К-вход с выхода схемы сравнения по модулю 2 поступит нулевой сигнал и триггер останется в единичном состоянии. Когда на входе будет единичный сигнал, триггер изменит свое состояние на противоположное.

Блок 13 сравнения предназначен для

сравнения кодов, поступающих на вход блока 3 памяти контрольных кодов (кодограммы эталонной микрокоманды) и из регистра контроля 12 (кодограммы форми0 руемой фактической контрольной микрокоманды).

Триггер 14 задания режимов работы предназначен для управления работой схемы контроля. Он устанавливается в единич5 ное состояние при поступлении единичного сигнала Контроль на вход 22 и в нулевое состояние по приходу сигнала Управление на вход 23. Единичный сигнал на выходе триггера 14 разрешает функцио0 нирование регистра 12 контроля, элементов И 5, 6, 15, 16 и коммутатора 11 условия в режиме Контполь.

Третий элемент И 15 предназначен для формирования сигнала Норма при совпа5 дении кодограмм в блоке 13 сравнения при поступлении единичных сигналов 21.1 Конец команды и Контроль.

Четвертый элемент И 16 предназначен для формирования сигнала Не норма при

0 несовпадении кодограмм в блоке 13 сравнения при поступлении единичных сигналов 21.1 Конец команды и Контроль.

Предлагаемое устройство работает следующим образом

5В исходном состоянии все элементы памяти установлены в О. В единичном состо- янии находится только один триггер регистра 12 контроля, с которого единичный сигнал поступает на вход коммутатора 1 ад0 реса, коммутатора 11 условия, элементов И 5, 15,16. На входе 17 кода операций устройства устанавливается код операции, являющийся адресом начала программы.

В устройстве реализуются два режима

5 работы: Управление и Контроль. Эти режимы работы устройства задаются входом 22 Контроль и входом 23 Управление.

При выполнении режима Управление сигнал с входа 23 Управление устанавли0 вает триггер 14 задания режимов работы в нулевое состояние, который блокирует работу сдвигающегося режима 7, коммутатора 11 условия. По заднему фронту тактового импульса т-|, поступающего с входа 18 на

5 синхровход регистра 2 адреса в регистр адреса заносится код операции с входа 17 через вход коммутатора 1 адреса. С выхода регистра 2 адреса код поступает на вход блока 4 памяти программ. Блок 4 памяти программ представляет собой блок памяти

статического типа, информация на входах которого присутствует в течение всего времени наличия адреса микрокоманды на его входе. По заднему фронту тактового импульса Г2, поступающего с входа 20 на синхровход регистра 12 контроля, в регистр 12 контроля записывается код микрооперация с выхода 4.1 блока 4 памяти программ. Код микрооперации, записанный в регистр 12 контроля, поступает на выход 21 микроопераций устройства. С выхода 4.2 блока 4 памяти программ формируется код логических условий, указывающий на наличие микрокоманд ветвления, который поступает на адресный вход мульти- плексора 8 логических условий, где является адресом для выбора заданных логических условия, поступающих на мультиплексор 8 с входа 19 устройства. Сигнал с выхода мультиплексора 8, соответствую- щий выбранному логическому условию, поступает на первый вход коммутатора 11 условия. При поступлении единичного сигнала с мультиплексора 8 логических условий на вход коммутатора 11 условия и нулевого сигнала с выхода триггера 14 задания режимов работы на инверсный вход коммутатора 11 условия коммутатор 11 условия формирует единичный сигнал на вход второго элемента ИЛИ 10, на вход которого с выхода 4.3 блока 4 памяти программ поступает код младшего разряда адреса что позволяет модифицировать код адреса следующей микрокоманды устройства С выхода 4.3 блока 4 памяти программ и выхода второго элемента ИЛИ 4 на второй информационный вход коммутатора 1 адреса поступает код адреса следующей микрокоманды, который через коммутатор 1 адреса поступает на вход регистра 2 адреса, с выхода регистра 2 адреса на вход блока 4 памяти программ, являясь адресом следующей микрокоманды При окончании выполнения заданной программы на выходе 21,1 регистра контроля формируется сигнал Конец программы, который поступает на выход26 устройства.

При выполнении устройством режима Контроль сигнал с входа 22 Контроль устанавливает триггер 14 задания режимов работы в единичное состояние, котор.ый единичным сигналом подготавливает к работе регистр 12 контроля, коммутатор 11 условия. По заднему фронту тактового импульса ft, поступающего с входа 18 на синхровход регистра 2 адреса, в регистр 2 адреса заносится код операции с входа 17 через вход 1 коммутатора адреса Далее этот код записывается в блок 4 памяти программ.

В свою очередь, код операции с входа 17 поступает в блок 3 памяти контрольных кодов, который является блоком постоянной памяти статического типа и на его выходах информация присутствует в течение всего времени наличия кода операции на его входе.

По заднему фронту тактового импульса Т2, поступающего с входа 20 на синхровход регистра 12 контроля, в регистр 12 контроля записывается код микрооперации с выхода 4.1 блока 4 памяти программ. С выхода 4 3 блока 4 памяти программ формируется код адреса следующей микрооперации, которой через вход 1 коммутатора адреса записывается в регистр 2 адреса, , в свою очередь, позволяет последовательно циклически отрабатывать заданную программу контроля. На выходе 4.2 блока 4 памяти программ формируется код логических условий, который поступает на вход первого элемента ИЛИ 9. Если на вход первого элемента ИЛИ 9 поступит признак команды ветвления, на его выходе будет единичный сигнал, который поступает на вход коммутатора 11 условия и на вход второго элемента И б

По тактовому импульсу ri, поступающему с входа 18 на вход первого элемента И 5, при наличии на его входах единичного сигнала Конец программы с выхода 21.1 регистра 12 контроля и единичного импульса с выхода триггера 14 задания режимов работы, с выхода первого элемента И 5 на первый синхровход сдвигающего регистра 7 поступает единичный сигнал, по которому в сдвигающий регистр 7 записывается код траектории программы (значения логических условий л}, Хп,фиг,4) с выхода 3,2 блока 3 памяти контрольных кодов.

По следующему тактовому импульсу П, поступающему с входа 18 на вход второго элемента И 6, при наличии на его входах единичного сигнала с триггера 14 задания режимов работы и единичного сигнала с выхода первого элемента ИЛИ 9 (при наличии признака микрокоманды ветвления), с выхо да второго элемента И 6 на второй синхровход сдвигающего регистра 7 поступает единичный сигнал, по которому происходит сдвиг информации, записанной в сдвигающий регистр 7, и на его выходе формируется сигнал, соответствующий записанному оче редному коду заданного логического условия Хп или тг,, при его выполнений-, при невыполнении - О. Этот сигнал поступает на вход коммутатора 11 условия. В соответствии с сигналами, поступающими на вход коммутатора 11 условия с выхода первого элемента ИЛИ 9, сдвигающего регистра 7,

триггера 14 задания режимов работы, с вы- хо дэ коммутатора условия 11 формируется сигнал на входе второго элемента ИЛИ 10, куда также поступает код младшего разряда адреса следующей микрокоманды с выхода 4.3 блока 4 памяти программ для модификации младшего разряда кода адреса следующей микрокоманды. Модифицируемый младший разряд кода адреса следующей микрокоманды с выхода второго элемента ИЛИ 10 поступает на вход коммутатора 1 адреса в составе кода адреса следующей микрокоманды.

По заднему фронту тактового импульса Т2,поступающего с входа 20 на синхровход регистра 12 контроля, по поступлении на его V-вход единичного сигнала с выхода триггера 14 задания режимов работы, на информационный вход регистра 12 контроля поступает информация с выхода 4.1 блока 4 памяти программ. На выходе регистра контроля формируется признак контроля, он может определяться например по формуле КП KI (фиг.5, 6). С выхода регистра

1 L1«M

12 контроля кодограмма результата контроля поступает на выход 21 устройства, а также на вход блока 13 сравнения, где сравнивается с кодом эталона, который поступает на вход блока 13 сравнения с выхода 3.1 блока 3 памяти контрольных кодов. С выхода блока 13 сравнения формируется сигнал, который поступает на третий 15, четвертый 16 элементы И. При поступлении на вход третьего элемента И 15 единичного Сигнала с триггера 14 задания условий работы и единичного сигнала с блока 13 сравнения при совпадении кодограмм по приходу единичного сигнала Конец программ с выхода 21.1 регистра 12 контроля (фиг.7) третий элемент И 15 формирует сигнал на выход 24 устройства Норма контроля. При несовпадении кодограмм в блоке 13 сравнения четвертый элемент И 16 формирует сигнал на выходе 25 устройства Не норма контроля.

Выход 26 устройства является выходом сигнала Конец программы, поступающего с последнего триггера регистра 12 контроля.

Зададим произвольную программу контроля, структура которой изображена на фиг.З. В данной программе указаны длины

линейных участков (di, 62изо), которые

будут пройдены за время ( n, T2 7зо),

заданы логические условия (Хч, XzХп)

прохождения программы. Рассмотрим маршруты, при которых обеспечивается минимально возможное повторное прохождение

отдельных участков при выполнении программы контроля: H:XiX2K; Н: Xi Х2 Хз К;

Н: Xi Х2 Хз Х4 Хб Хб К;

Н:Х1Х4Х5ХбХюК; H;XiX4XsX9XioXn К H:XiX4X7X8X9Xn К; HiXiX-iXrXaXgXn К; где Н - начало маршрута контроля; К - конец маршрута контроля, (Хп - если выполняется условие соответ- ствующей ветви программы, будет рав- ХпЦным единице;

х.п - если не выполняется условие соответствующей ветви программы, Хп будет равным нулю.

Для минимально возможных повторений при прохождении участков программы контроля введем дополнительные условия, которые обозначим л|.

При введении дополнительных переходов (фиг.4) последовательность значений условий будет выглядеть следующим обра- зом:

Н: Xi Я2 лз Лб Я1 Х2 Хз л&Хз Xi X4 Х5 Хе лз Х4 щУл Хв Хб Л4 X Хв лёХд Хю л& Хе ХюХп ХэХц К

Данный алгоритм контроля реализует- ся в предлагаемом устройстве благодаря введению соответствующих технических средств.

Время выполнения программы контроля, реализованной предлагаемым устройст- вом при TI -т, I 1,30 уменьшается в 2.34 раза.

Формула изобретения Устройство для контроля тестопригодных программ, содержащее блок памяти программ, регистр адреса, коммутатор адреса, мультиплексор логических условий, регистр контроля, первый элемент ИЛИ, причем вход кода операций устройства и выход конца команды регистра контроля соединены соответственно с первым информационным и инверсным управляющим входами коммутатора адреса, выход которого соединен с информационным входом

регистра адреса, выход которого соединен с входом блока памяти программ, выходы разрядов адреса, кода логических условий и микроопераций блока памяти программ соединены соответственно с вторым информационным входом коммутатора адреса, с адресным входом мультиплексора логических условий и с информационным входом регистра контроля, выход которого является выходом микроопераций устройст

ва, вход логических условий устройства соединен с информационным входом мультиплексора логических условий, отличающееся тем, что, с целью повышения оперативности контроля, в устройство вве- дены блок памяти контрольных кодов, сдви- гающий регистр,- блок сравнения, коммутатор условия, триггер режима работы, с первого по четвертый элементы И, второй элемент ИЛИ, причем вход кода операций устройства соединен с входом блока памяти контрольных кодов, выходы разрядов эталона и кода заданных условий блока Памяти контрольных кодов соединены соответственно с первым информацией- ным входом блока сравнения и с информационным входом сдвигающего регистра, входы устройства Контроль и Управление соединены соответственно в первым и вторым входами триггера режима работы, выход которого соединен с первыми входами с первого по четвертый элементов И, прямым и инверсным управляющими входами коммутатора условия, с разрешающим входом регистра контроля, выход муль- типлексора логических условий соединен с первым информационным входом коммутатора условий, выход первого элемента ИЛИ соединен с вторым информационным входом коммутатора условия, первый тактовый вход устройства соединен с вторыми входами первого и второго элементов И, третий вход первого элемента И соединен с выходом конца команды регистра контроля, третий вход второго элемента И соединен с выхо/юм первого элемента ИЛИ выход первого элемента И соединен с входом записи сдвигающего регистра, выход второго элемента И соединен с входом сдвига сдвигающего регистра, выход сдвигающего регистра соединен с вторым информационным входом коммутатора условия, выход коммутатора условия соединен с первым входом второго элемента ИЛИ, второй тактовый вход устройства соединен с синхров- ходом регистра контроля, выход которого является выходом микроопераций устройства и сбединен с вторым входом блока сравнения, выход которого соединен с вторым входом третьего элемента И и с вторым инверсным входом четвертого элемента И, выход последнего разряда регистра контроля соединен с третьими входами третьего и четвертого элементов И и является выходом Конец программы устройства, выход третьего элемента И является выходом Норма устройства, выход четвертого элемента И является выходЪм Не норма устройства, выход кода логических условий блока памяти программ соединен с группой входов первого элемента ИЛИ, модифицируемый разряд блока памяти программ соединен с вторым входом второго элемента ИЛИ, выход которого соединен с разрядом второго информационного входа коммутатор э адреса.

Фиг. 2

27

Фие.З

Л2

КС 3

К С J

Z7.)

в

Фиг. 5

г

Фиг.6

4Ъ

%Р.1

Авторы

Даты

1992-07-30—Публикация

1990-08-21—Подача