Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах для формирования элементов конечных полей.

Известен умножитель на два по модулю, содержащий два сумматора, элементы ИЛИ-НЕ и элементы ИЛИ с соответствующими связями. Недостатком этого устройства является низкая скорость вычислений.

Целью изобретения является повышение быстродействия.

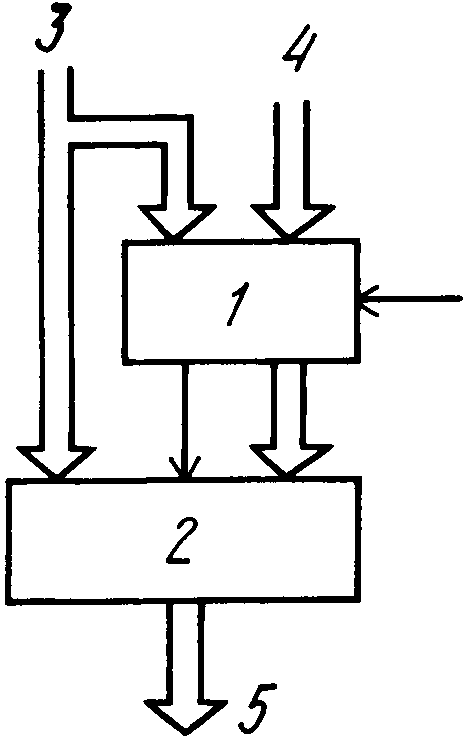

На чертеже показана схема умножителя на два по модулю.

Умножитель содержит сумматор 1 и мультиплексор 2. Входы 3 и 4 служат для подачи кода числа и инверсного кода модуля. Выходы 5 являются информационными.

Умножитель на два по модулю работает следующим образом.

На входы 3 подается код числа из диапазона чисел 0<Х ≅ Р-1, где Х - умножаемое на два число, Р - величина модуля, который поступает в сумматор 1 и мультиплексор 2 сдвинутым в сторону старших разрядов на один разряд. Этим достигается умножение на два числа. Если значение произведения превышает значение модуля, то в сумматоре 1 за счет перевода инверсного кода модуля в дополнительный код происходит вычитание из полученного произведения значения кода модуля, на выходе переноса сумматора 1 появляется управляющий сигнал, переключающий вторые информационные входы мультиплексора 2 на его выходы, и значение остатка с выходов сумматора 1 через вторые входы мультиплексора 2 поступают на информационные выходы 5 умножителя. Если значение произведения не превышает значение модуля, то с выхода переноса сумматора 1 управляющий сигнал на вход мультиплексора 2 не подается, первые его информационные входы остаются скоммутированными на информационные выходы и значение произведения с входов сумматора 1 через мультиплексор 2 поступают на информационные выходы 5 умножителя.

Рассмотрим работу умножителя на два по модулю на конкретном примере.

Пусть Х=1010=010102, Р=1210=011002. Тогда на вторых входах сумматора 1 и первых входах мультиплексора 2 имеют 2Х=2010= 101002. На выходах сумматора 1 образуется число А=2Х+ +1=101002+100112+1= =1010002, на выходе переноса (шестой разряд) образуется единица, которая коммутирует первые пять разрядов сумматора 1 на выходы мультиплексора 2. В результате имеют А=011002= 810=2.1010MOD1210.

+1=101002+100112+1= =1010002, на выходе переноса (шестой разряд) образуется единица, которая коммутирует первые пять разрядов сумматора 1 на выходы мультиплексора 2. В результате имеют А=011002= 810=2.1010MOD1210.

Пусть теперь Х= 510=001012, Р=1210= =011002,  =100112. На входах сумматора 1 имеют 2Х= 010102= 1010, на выходах сумматора 1 имеют А=2Х+

=100112. На входах сумматора 1 имеют 2Х= 010102= 1010, на выходах сумматора 1 имеют А=2Х+ +1= 010102+100112+1= = 111102. Так как на выходе переноса сумматора 1 ноль, то мультиплексор 2 коммутирует со своими выходами входы сумматора 1. В результате на его выходах оказывается код числа 1010. Не трудно также убедиться, что если 2Х=Р, то на выходе мультиплексора будет код нуля.

+1= 010102+100112+1= = 111102. Так как на выходе переноса сумматора 1 ноль, то мультиплексор 2 коммутирует со своими выходами входы сумматора 1. В результате на его выходах оказывается код числа 1010. Не трудно также убедиться, что если 2Х=Р, то на выходе мультиплексора будет код нуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| УМНОЖИТЕЛЬ ПО МОДУЛЮ | 2005 |

|

RU2299461C1 |

| УМНОЖИТЕЛЬ НА ДВА ПО МОДУЛЮ | 2005 |

|

RU2299460C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1992 |

|

RU2012137C1 |

| СУММАТОР ПО МОДУЛЮ P | 1992 |

|

RU2032934C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2025897C1 |

| КОМБИНАЦИОННЫЙ РЕКУРРЕНТНЫЙ ФОРМИРОВАТЕЛЬ ОСТАТКОВ | 1992 |

|

RU2029435C1 |

| РЕКУРРЕНТНЫЙ ФОРМИРОВАТЕЛЬ ОСТАТКОВ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 1991 |

|

RU2007037C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1991 |

|

RU2007033C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1990 |

|

RU2029434C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЭЛЕМЕНТОВ МУЛЬТИПЛИКАТИВНЫХ ГРУПП ПОЛЕЙ ГАЛУА GF (P) | 1991 |

|

RU2007036C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах для формирования элементов конечных полей. Цель изобретения - повышение быстродействия. Умножитель содержит сумматор 1 и мультиплексор 2. 1 ил.

УМНОЖИТЕЛЬ НА ДВА ПО МОДУЛЮ, содержащий сумматор, входы первой группы которого соединены с входами инверсного кода модуля умножителя, входы второй группы - с входами кода умножаемого тела умножителя, сдвинутого на один разряд в сторону старших разрядов, а вход переноса - с входом значения логической единицы умножителя, отличающийся тем, что в умножитель ввелен мультиплексор, информационные входы первой группы которого соединены с входами второй группы сумматора, информационные входы второй группы - с информационными выходами группы сумматора, выход переноса которого соединен с управляющим входом мультиплексора, выходы группы которого являются информационными выходами умножителя.

| Пухальский Т.И., Новосельцева Т.Я | |||

| Проектирование дискретных устройств на интегральных микросхемах.: Справочник | |||

| М.: Радио и связь, 1990, с.205, рис.3.131. |

Авторы

Даты

1994-06-30—Публикация

1991-10-29—Подача