СЛ

О5 О5 СО

- го

6, элемент ИЛИ 7, элементы И 8-13, элемент И-НЕ 14, элемент ИЛИ 15, элемент И 16, элемент 17 запрета, элемент ИЛИ 18, элементы ИЛИ-НЕ 19-21, элемент ИЛИ 22, элементы И 23-26, элементы ИЛИ 27, 28, входы 29, 31 первого слагаемого, входы 32-34 второго слагаемого, выходы 35-37 результата. При подаче на входы устройств слагаемых х и у, каждое из которых не превышает К-1, на его выходах формируется двоичный код числа 7, (х + у) mod 5. 1 ил.(1 .

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство по модулю | 1988 |

|

SU1571583A1 |

| Арифметическое устройство в системе остаточных классов | 1983 |

|

SU1107122A1 |

| Сумматор по модулю тридцать один | 1989 |

|

SU1603373A1 |

| Трехвходовой параллельный сумматор | 1983 |

|

SU1136150A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Сумматор в знакоразрядной позиционно-остаточной системе счисления | 1986 |

|

SU1383349A1 |

| Устройство для контроля информации по модулю | 1989 |

|

SU1751763A1 |

| Трехдекадный преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU943705A1 |

| Сумматор по модулю пятнадцать | 1989 |

|

SU1605225A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения систем передачи и переработки дискретной информации. Цель изобретения - повышение быстродействия сумматора по модулю пять. Сумматор по модулю пять содержит элемент ИЛИ 1, элемент И 2, элемент ИЛИ 3, элементы И 4, 5 и 6, элемент ИЛИ 7, элементы И 8-13, элемент И-НЕ 14, элемент ИЛИ 15, элемент И 16, элемент 17 запрета, элемент ИЛИ 18, элементы ИЛИ-НЕ 19-21, элемент ИЛИ 22, элементы И 23-26, Элементы ИЛИ 27, 28, входы 29, 31 первого слагаемого, входы 32-34 второго слагаемого, выходы 35-37 результата. При подаче на входы устройства слагаемых X и Y каждое из которых не превышает К-1, на его выходах формируется двоичный код числа Z = (X+Y) MOD 5. 1 ил., 1 табл.

Изобретение относится к вычислительной технике и может быть использовано для построения системы пере- дачи и переработки дискретной информации.

0 Цель изобретения - повышение быстродействия сумматора по модулю пять.

Сумматор но модулю пять содержит третий элемент ИЛИ 1, первый элемент И 2, четвертый элемент ИЛИ 3, пятый 4, третий 5 и четвертый 6 элементы И, пятый элемент ИЛИ 7, второй элемент И 8, шестой 9, седьмой 10 и восьмой 11 элементы И, первый элемент ИЛИ 12, девятый элемент И 13, элемент И-НЕ 14, второй элемент ИЛИ 15, десятый элемент И 16, элемент 17 запрета, седьмой элемент ИЛИ 18, вто- рой 19, третий 20 и первый 21 элементы ИЛИ-НЕ, шестой элемент ИЛИ 22, тринадцатый 23, двенадцатый 24, четырнадцатый 25 и одиннадцатью 26 элементы И, восьмой 27 и девятый 28 эле- Менты ИЛИ, входы 29-31 первого, второго и третьего разрядов первого слагаемого, входы 32-34 первого, второго и третьего разрядов второго слагаемого, выходы 35-37 результата.

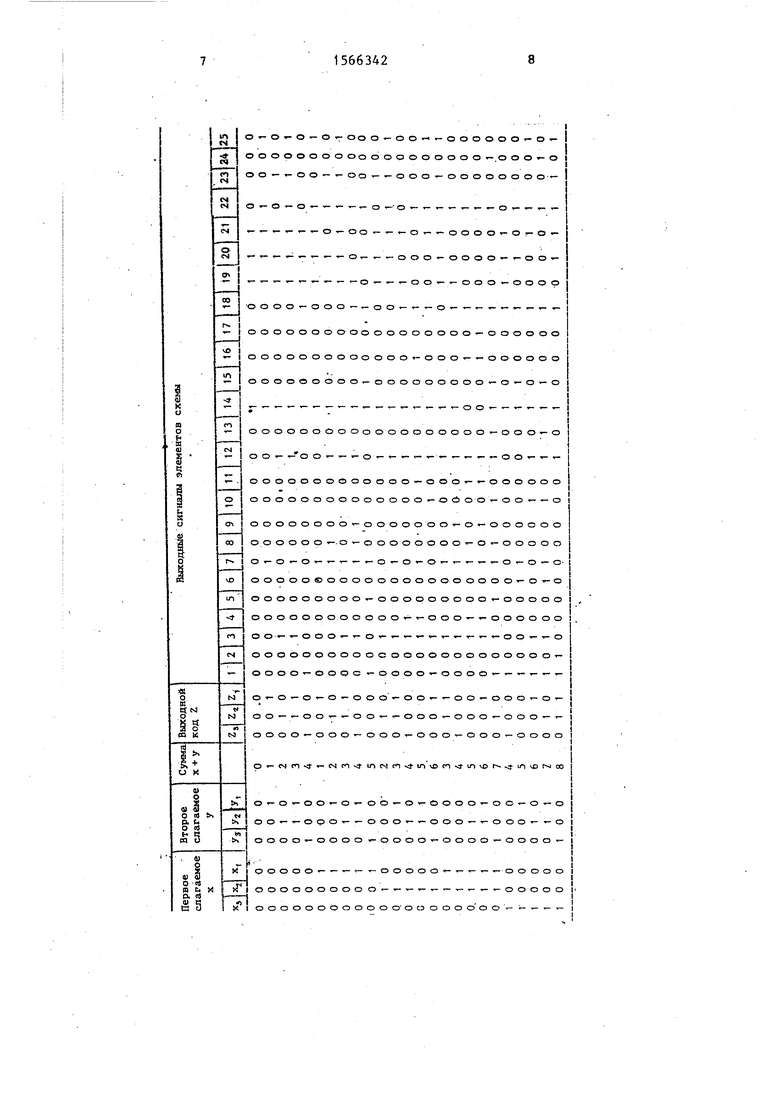

Функционирование сумматора по модулю пять поясняется таблицей, в которой приведены выходные сигналы все элементов схемы для всех разрешающих входных комбинаций слагаемых, значения которых не превышают К-1 4 .

Из таблицы видно, что при подаче на входы устройства слагаемых х и у, на его выходах формируется двоичный код числа (х + у) mod 5.

Формула изобретения

Сумматор по модулю пять, содержащий девять элементов И и два элемента ИЛИ, причем вход третьего разряда первого слагаемого сумматора соединен с первым входом первого элемента И, выход которого соединен с первым

5

0 5 0

0

5

0

5

входом первого элемента ИЛИ, ч горой вход которого соединен с выхгчом тггг - рого элемента И, выходы третьего и четвертого элементов И соединены с первым и вторым входами второго элемента ИЛИ, о т л и ч а ю п, и и с я тем, что, с целью повышения бистро- действия сумматора в него введены пять элементов И, семь элементов ИГИ, три элемента ИЛИ - НЕ, один элемент запрета и один элемент И - НЕ, ттрячег вход третьего разряда первого слагаемого сумматора соединен с первыми входами третьего элемента ИЛИ и четвертого элемента И, вход третьего разряда второго слагаемого сумм;г1ора соединен с первым входом третьего элемента И и вторыми входами третьего элемента ИЛИ и первого элемента И, вход второго разряда первого слагаемого сумматора соединен с первыми входами четвертого элемента ИЛИ и пл- того элемента И, второй вход которого соединен с вторым входом четвертого элемента ИЛИ и входом второго разряда второго слагаемого сумматора, вход первого разряда первого слагаемого которого соединен с первыми входами элемента И-НЕ, второго элемента И и пятого элемента ИЛИ, второй вход которого соединен с входом первого разряда второго слагаемого сумматора, с вторыми входами четвертого элемента И и второго элемента И, выход которого соединен с первым прямым входом элемента запрета, и первыми входами шестого элемента И и первого элемента ИЛИ-НЕ, второй вход которого соединен с выходом второго элемента ИЛИ и первым входом второго элемента ИЛИ-HF, второй вход которого соединен с выходом седьмого элемента И и первыми входами третьего элемента ИЛИ-НЕ и шестого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента ИЛИ и первыми входами восьмого, девятого и десятого элементов И, вы-

515

ход третьего элемент ИЛИ соединен с первыми входами седьмого элемента ИЛИ, седьмого элемента И, вторым входом девятого элемента И и инверсным входом элемента запрета, второй прямой вход которого соединен с выходом пятого элемента И, вторыми входами седьмого элемента ИЛИ, восьмого элемента И, третьего элемента ИЛИ-НП, элемента И-НЕ, десятого элемента И, выход которого соединен с третьим входом первого элемента ИЛИ - НЕ, выход которого соединен с первым вхо «- дом одиннадцатого элемента И, второй вход которого соединен с выходом шестого элемента ИЛИ, третий вход которого соединен с выходом первого элемента И и третьим уходом второго элемента ИЛН-НЕ, четвертый вход которого соединен с выходом восьмого элемента И, выход четвертого элемента ИЛИ сог- линен с вторыми входами шестого и седьмого элементов И и с третьими входами девятого элемента И и нервно элемента ИЛИ, выход которого соединен с первым входом двенадцатого элг.мен

5

0

5

0

5

та И, второй вход которого соединен с выходом третьего элемента ИЛН-НЕ, третий вход которого соединен с пи- ходом шестого элемента И н третьим входом седьмого элемента ИЛИ, выход которого соединен с первым входом тринадцатого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ-НЕ, выходы девятого элемента И н элемента соединены с первым и вторым входами четырнадцатого элемента И, выход которого соединен с первым входом восьмого элемента ИЛИ, второй вход которого сое- с выходом двенадцатого элемента И, выход одиннадцатого элемента II сое- дине с первым входом девятого элемента ИЛИ, второй вход которого соединен с выходом элемента запрета, выходы девятого и восьмого элементов ИЛИ соединены с выходами первого и второго разрядов результата сумматора, выход третьего разряда которого C P;H HL H с выходом тринадцатого элемента И.

| ПаперноБ Л.Л | |||

| Л | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| с; Об ,Ч ИЧССКИ(пип re.viii: 2, с | |||

| Н -) | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-05-23—Публикация

1988-09-28—Подача