Изобретение относится к электросвязи.

Цель изобретения - повышение помехоустойчивости и уменьшение вхождения в связь.

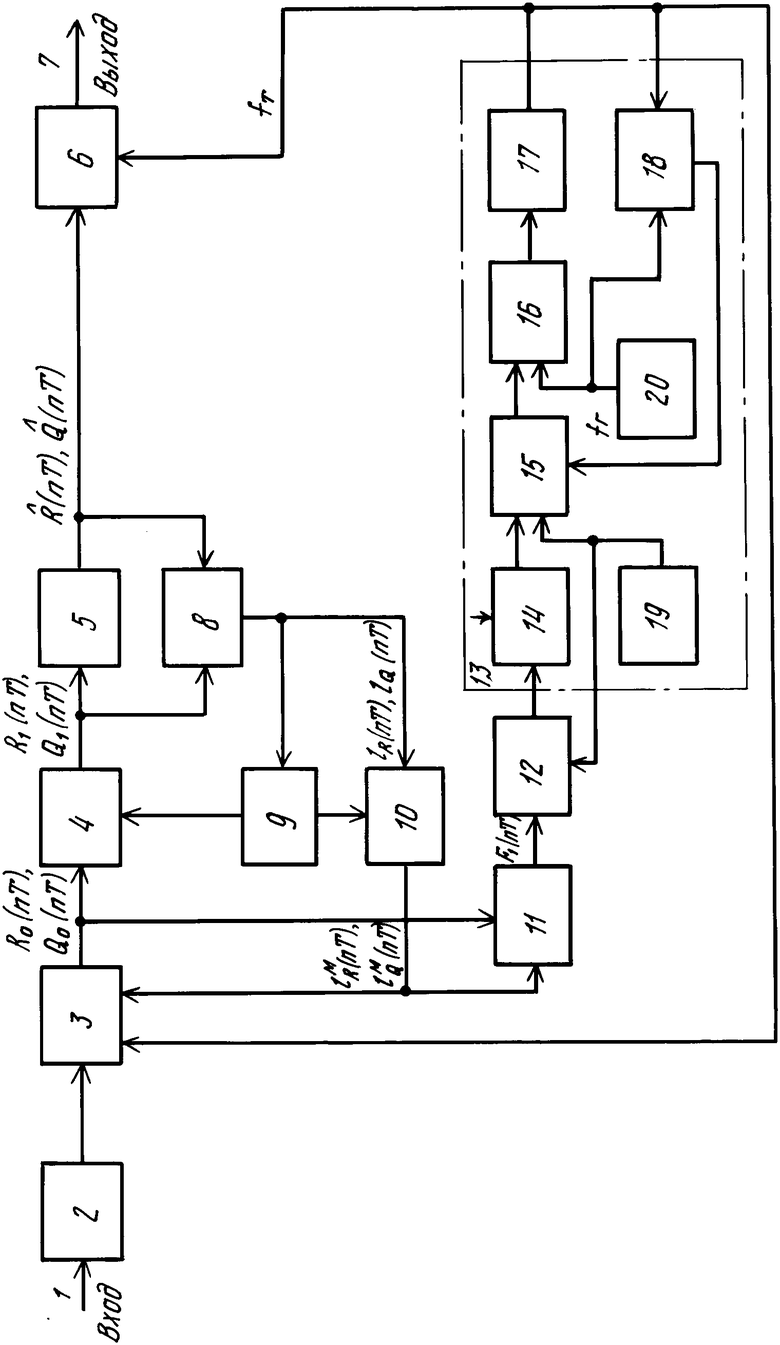

На чертеже изображена структурная электрическая схема предложенного адаптивного приемника.

Адаптивный приемник содержит вход 1, согласующий блок 2, блок 3 линейной обработки сигналов, первый фазовращатель 4, решающий блок 5, декодер 6, выход 7, формирователь 8 ошибок, управляемый генератор 9, фазовращатель 10, блок 11 формирования критерия подстройки, формирователь 12 тактового колебания, исполнительный блок 13, состоящий из регистра 14 памяти, коммутатора 15, управляемого делителя 16 частоты, делителя 17 частоты, триггера 18, блока 19 памяти, генератора 20.

Адаптивный приемник работает следующим образом.

Модулированный сигнал с выхода канала связи с входа 1 через согласующий блок 2 поступает на блок 3 линейной обработки сигналов.

В блоке 3 линейной обработки сигналов осуществляется автоматическая регулировка усиления, демодуляция входного сигнала в каждом из квадратурных подканалов R и Q, аналого-цифровое преобразование, адаптивная коррекция межсимвольной интерференции.

Посредством фазовращателя 4 осуществляется преобразование сигнала с учетом фазы Q(n) несущего колебания для компенсации искажения (сдвига) несущей частоты в канале связи. Сигналы R1 (nT), Q(nT) с выхода фазовращателя 4 поступают на вход решающего блока 5, в котором осуществляется формирование эталонных сигналов  (nT),

(nT),  (nT).. В формирователе 8 ошибок формируются сигналы, соответствующие отклонению сигналов R1(nT), Q(nT) от эталонных сигналов

(nT).. В формирователе 8 ошибок формируются сигналы, соответствующие отклонению сигналов R1(nT), Q(nT) от эталонных сигналов  (nT),

(nT),  (nT) соответственно, по формуле

(nT) соответственно, по формуле

lR(nT)=R1(nT)- (nT),

(nT),

lQ(nT)= Q1(nT)- (nT), (1) где Т - период следования принимаемых элементов сигнала;

(nT), (1) где Т - период следования принимаемых элементов сигнала;

n - порядковый номер принимаемого элемента сигнала.

Сигналы lR(nT) и lQ(nT) с выхода формирователя 8 через фазовращатель 10 поступают на блок 3 линейной обработки сигналов, где на основании этих сигналов реализуются алгоритмы функционирования указанных систем регулирования приемника.

Фазовращатель 10 необходим для правильной работы адаптивного корректора, входящего в состав блока 3 линейной обработки сигналов, при наличии погрешностей фазы несущей. Посредством управляемого генератора 9 осуществляется формирование сигналов Sin θ (nT) и Cos θ (nT).

Сигналы R1(nT) и Q1(nT) формируются по правилу

R1(nT) = Ro(nT)Cos θ (n) + Qo(nT)Sin θ (n)

Q1(nT) = Qo(nT)Cos θ (n) - Ro(nT)Sin θ (n)

(2)

Сигналы lRм(nT) и lQм(nT) на выходе фазовращателя 10 определяются следующим образом:

lRм(nT) = lR(nT)Cos θ (n) - lQ(nT)Sin θ (n)

lQм(nT) = lQ(nT)Cos θ (n) + lR(nT)Sin θ (n)

(3)

В блоке 11 формируется сигнал (критерий) F1(nT), отображающий отклонение по фазе тактового колебания от номинального положения по формуле

F1(nT) = lRм[(n-1)T]{Ro[(n-2)T] - Ro(nT)} +

+lQм[(n-1)T]{Qo[(n-2)T] - Qo(nT)}.

В формирователе 12 тактового колебания осуществляется цифровая фильтрация вычисленного критерия подстройки F1(nT), реализованная на базе рекурсивного фильтра первого порядка согласно следующим уравнениям:

F2(nT) = F2[(n-1)T] + K1K2F1(nT),

F3(nT) = F2(nT) + K1F1(nT) + M, (5) где K1, K2 - постоянные коэффициенты, определяющие характеристику фильтра;

M - постоянная, определяемая блоком 19 памяти.

В исполнительном блоке 13 по сигналу управления F3(nT) осуществляется непосредственно подстройка тактового колебания следующим образом.

Критерий подстройки F3(nT), сформированный в виде m-разрядного кодового числа, записывается в регистр 14 памяти, необходимый для обеспечения возможности конвейерной обработки сигнала.

Кодовое число с выхода регистра 14 памяти поступает через коммутатор 15 для установки начального состояния L управляемого делителя 16 частоты, на тактовый вход которого поступает высокочастотная импульсная последовательности с выхода генератора 20. Пусть номинальный коэффициент деления делителя 16 частоты равен N1. Сигнал с выхода управляемого делителя 16 частоты поступает на делитель 17 частоты с коэффициентом деления N2, на выходе которого формируется подстроенное тактовое колебание fT, частота которого равна линейной скорости передачи сигналов.

Посредством триггера 18 формируется сигнал управления, по которому осуществляется переключение коммутатора 15 таким образом, что на его выход проходит либо код числа с выхода регистра 14 памяти (момент подстройки t = nT), либо код числа М (в течение времени между записью соседних отсчетов критерия подстройки F3(nT).

Коэффициент деления управляемого делителя 16 частоты равен N1-M (за счет цепи установки начального состояния делителя 16, равного L = M). В этом случае частота тактового колебания fTo равна

fTO=  (6)

(6)

При замкнутой цепи управления имеем

fT= fTO/ 1+

1+  , (7) так как начальное состояние управляемого делителя 16 частоты определяется условием

, (7) так как начальное состояние управляемого делителя 16 частоты определяется условием

L=  t=nT,

t=nT, выражение (7) можно аппроксимировать следующим образом:

выражение (7) можно аппроксимировать следующим образом:

fT≈♂f 1-

1-  (8)

(8)

Из (7) и (8) следует, что шаг подстройки зависит от величины рассогласования (увеличивается при увеличении величины рассогласования). Следовательно, суммарное время подстройки тактового колебания, а следовательно, и время вхождения в связь, уменьшаются.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный приемник сигналов данных | 1989 |

|

SU1672580A1 |

| МНОГОЧАСТОТНЫЙ ПРИЕМНИК ДЕЛЬТА-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1993 |

|

RU2090981C1 |

| Устройство преобразования сигналов для передачи данных по первичному сетевому тракту | 1989 |

|

SU1739503A1 |

| УСТРОЙСТВО ТЕЛЕКОНТРОЛЯ РЕГЕНЕРАТОРОВ ЛИНИИ СВЯЗИ | 1991 |

|

RU2007876C1 |

| ЦИФРОВОЙ ПРИЕМНИК ДИСКРЕТНЫХ СИГНАЛОВ С "ВРАЩАЮЩЕЙСЯ ФАЗОЙ" | 1991 |

|

RU2038703C1 |

| СЛЕДЯЩИЙ ПРИЕМНИК ШИРОКОПОЛОСНОГО СИГНАЛА | 1999 |

|

RU2157052C1 |

| ПРИЕМОПЕРЕДАЮЩАЯ АППАРАТУРА ШИРОКОПОЛОСНЫХ ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1979 |

|

SU1840119A1 |

| СИСТЕМА СВЯЗИ | 1985 |

|

SU1840076A1 |

| ОДНОВОЛОКОННАЯ ОПТИЧЕСКАЯ ЛИНИЯ ДУПЛЕКСНОЙ СВЯЗИ | 1995 |

|

RU2096915C1 |

| АДАПТИВНАЯ СИСТЕМА СВЯЗИ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1979 |

|

SU1840451A1 |

Сущность изобретения: адаптивный приемник содержит согласующий блок, блок линейной обработки сигналов, два фазовращателя, решающий блок, декодер, формирователь ошибок, управляемый генератор, блок формирования критерия подстройки, формирователь тактового колебания, исполнительный блок. 1 ил.

АДАПТИВНЫЙ ПРИЕМНИК СИГНАЛОВ ДАННЫХ, содержащий последовательно соединенные согласующий блок, вход которого является входом адаптивного приемника, блок линейной обработки сигналов, первый фазовращатель, решающий блок, декодер, выход которого является выходом адаптивного приемника, выход первого фазовращателя соединен с первым входом формирователя ошибок, второй вход которого соединен с выходом решающего блока, выход формирователя ошибок соединен с входом управляемого генератора и первым входом второго фазовращателя, выход которого соединен с первым входом блока формирования критерия подстройки и с вторым входом блока линейной обработки сигналов, выход которого соединен с вторым входом блока формирования критерия подстройки, выход которого соединен с первым входом формирователя тактового колебания, выход которого соединен с первым входом исполнительного блока, первый выход которого соединен с вторым входом декодера и третьим входом блока линейной обработки сигналов, первый и второй выходы управляемого инвертора соединены с вторыми входами первого и второго фазовращателей соответственно, отличающийся тем, что, с целью повышения помехоустойчивости и уменьшения времени вхождения в связь, второй выход исполнительного блока соединен с вторым входом формирователя тактового колебания, при этом исполнительный блок содержит последовательно соединенные регистр памяти, коммутатор, управляемый делитель частоты, делитель частоты и триггер, а также блок памяти и генератор, выход которого соединен с вторыми входами управляемого делителя частоты и триггера, выход которого соединен с вторым входом коммутатора, третий вход которого соединен с выходом блока памяти, являющимся вторым выходом исполнительного блока, первым выходом и входом которого являются соответственно выход делителя частоты и вход регистра памяти.

| Адаптивный приемник сигналов данных | 1989 |

|

SU1672580A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-08-30—Публикация

1991-04-09—Подача