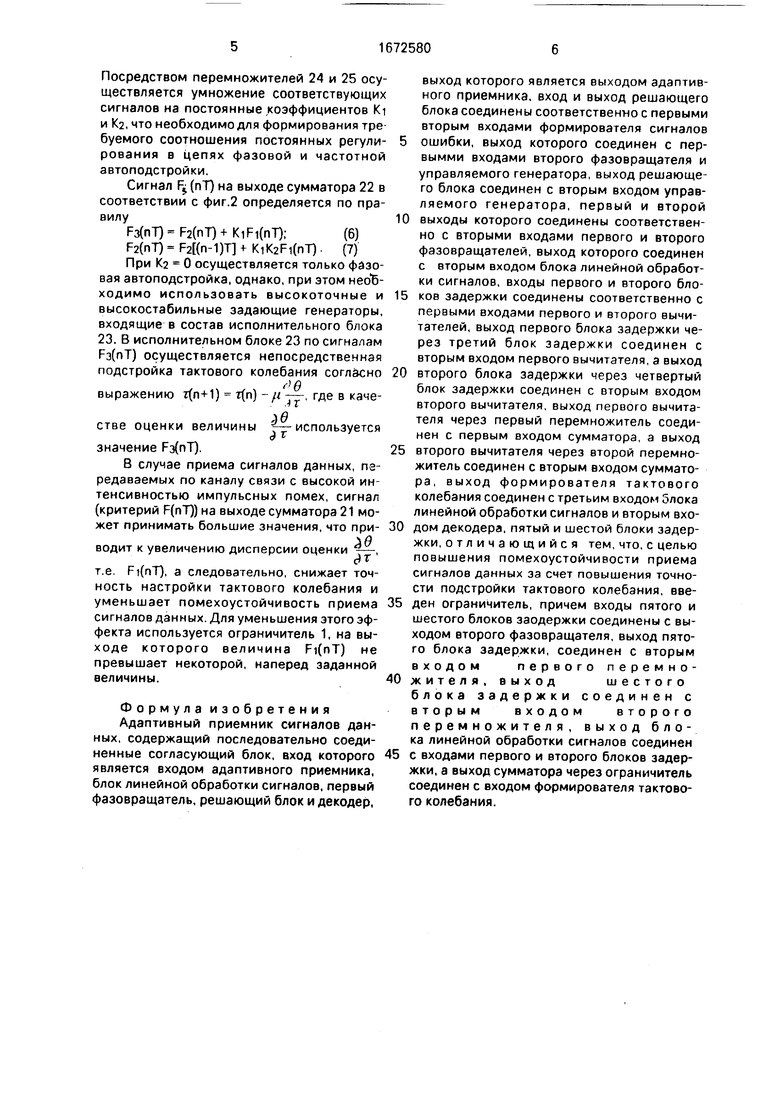

Фиг.1

Изобретение относится к электросвязи и может использоваться для приема сигналов, сформированных многопозиционными методами комбинированной амплитудно- фазовой модуляции.

Цель изобретения - повышение помехоустойчивости приема сигналов данных за счет повышения точности подстройки тактового колебания.

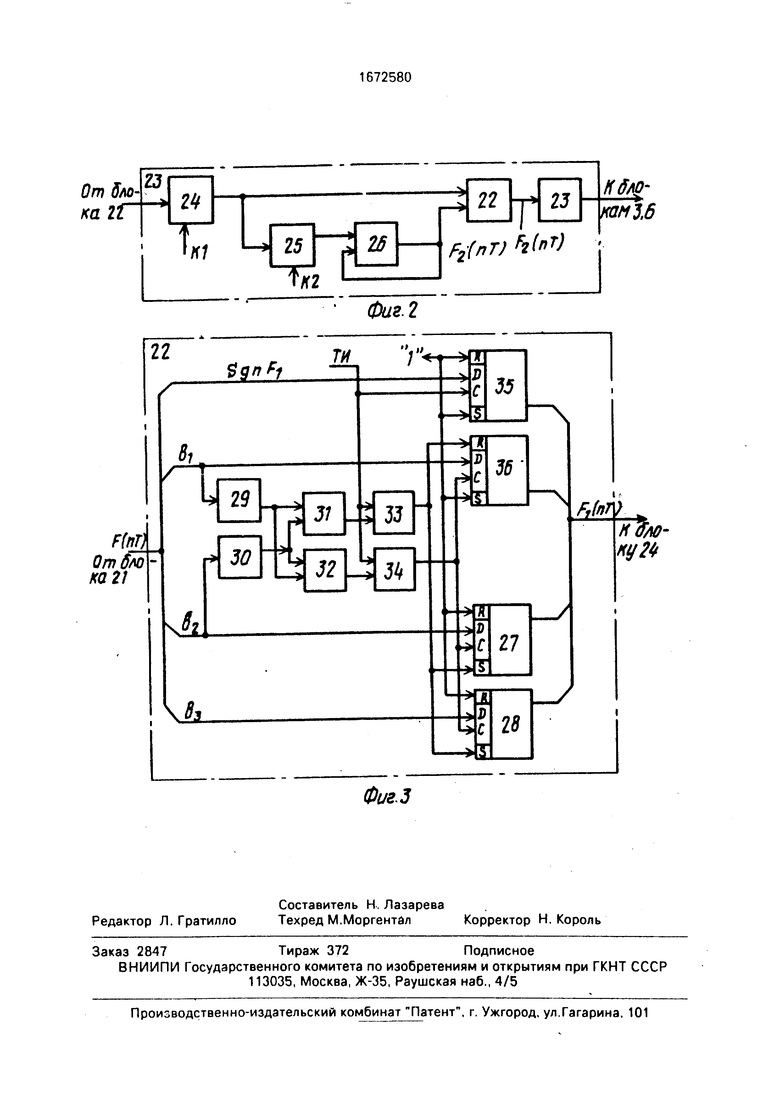

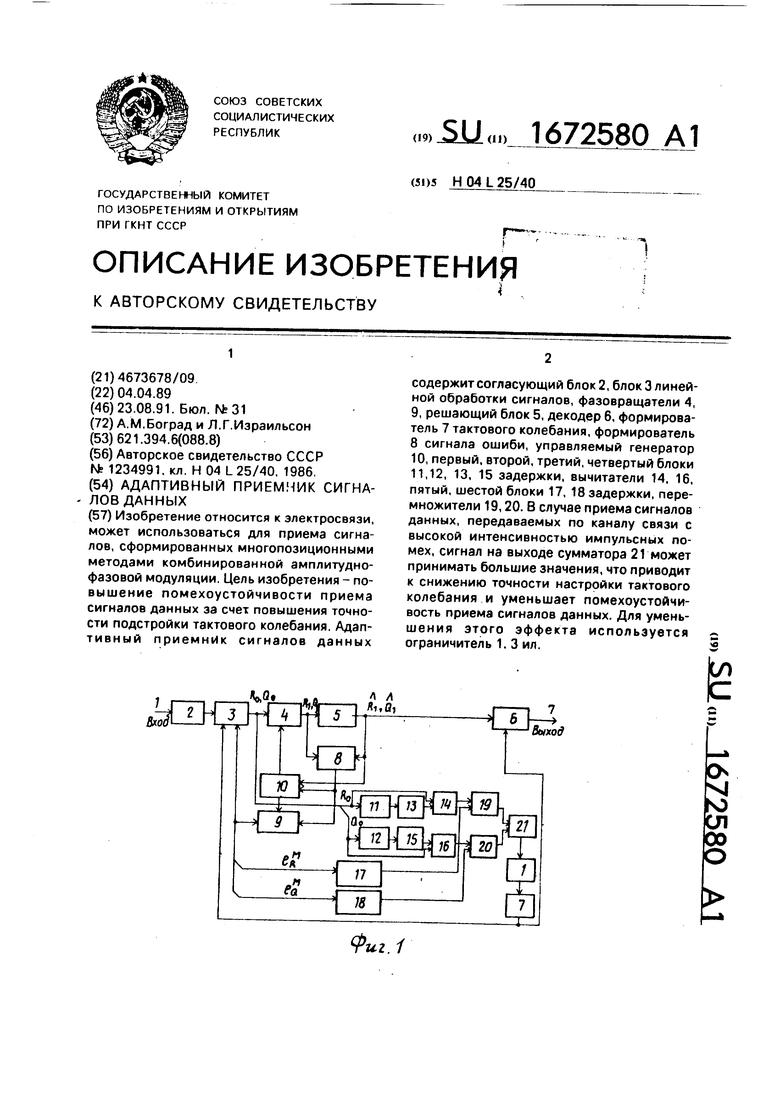

На фиг.1 изображена структурная электрическая схема предложенного адаптивного приемника; на фиг.2 - схема формирования тактового колебания; на фиг.З - схема ограничителя.

Адаптивный приемник содержит ограничитель 1, согласующий блок 2, блок 3 линейной обработки сигналов, первый фазовращатель 4, решающий блок 5, декодер 6, формирователь 7 тактового колебания, формирователь 8 сигнала ошибки, второй фазовращатель 9, управляемый генератор 10, первый, второй и третий блоки 11-13 задержки, первый вычитатель 14, четвертый блок 15 задержки, второй вычитатель 16, пятый и шестой блоки 17 и 18 задержки, первый и второй перемножители 19 и 20, сумматор 21.

Формирователь 7 состоит из сумматора 22, исполнительногс блока 23, перемножителей 24 и 25, сумматора 26. Ограничитель 1 состоит из триггеров 27 и 28, элементов НЕ 29 и 30, элемента И-НЕ 31, элемента И 32, элементов И-НЕ 33 и 34, триггеров 35 иЗб.

Адаптивный приемник работает следующим образом.

Модулированный сигнал с выхода канала связи через согласующий блок 2 поступает на блок 3 линейной обработки сигналов. В блоке 3 линейной обработки сигналов осуществляются автоматическая регулировка усиления, демодуляция входного сигнала в каждом из квадратурных подканалов, R и Q, аналого-цифровое преобразование, адаптивная коррекция межсимвольной интерференции. Посредством фазовращателя 4 осуществляется преобразование сигнала с учетом фазы в(г) несущего колебания для компенсации сдвига несущей частоты в канале связи. Сигналы Ri(n) и Q2(nT) с выхода фазовращателя 4 поступают на вход решающего блока 5, в котором осуществляется формирование эталонных сигналов Ri(nT) и Ui(nT). В формирователе 8 сигналов ошибки формируются сигналы, соответствующие отклонению сигналов Ri(nT) и Qi(nT) соответственно по формуле

fe(nT)--Ri(nT)); . fa(nT)-Q(nT)-Qi(nT),

0)

где Т период следования принимаемых элементов сигнала;

п - порядковый номер принимаемого элемента сигнала.

Сигналы Ip(nT) и lo(nT) с выхода формирователя 8 сигналов ошибки через фазовращатель 9 поступают в блок 3, где на основании этих сигналов реализуются алгоритмы функционирования указанных сис- тем регулирования. Фазовращетель 9 необходим для правильной работы адаптивного корректора, входящего в состав блока 3 при наличии огрешностей фазы несущей. Посредством управляемого генера- тора 10 осуществляется формирование сигналов sin$(n) и cos 6(п).

Сигналы Ri(nT) и Qi(nT) формируются по правилу

Ri(nT) Ro(nT)cos#(n) + + Qo(nT) sln0(n);

Qi(nT) Q0(nT| cos0(n)- -Ro(nT)sln0(n).(2)

Сигналы f2 (nT) и IQ (nT) на выходе формирователя 8 сигналов ошибки определяют- ся следующим образом;

IR (пТ) Гв(пТ) cos 6(n) - - to(nT) sin0(n); 1сПпТ) Ь(пТ) cos ) + + Сн(пТ) sin fln).(3)

Посредством совокупности блоков 1121 осуществляются формирование и подстройка тактового колебания, необходимого для работы блока 3 и декодера 6.

На выходе сумматора 21 формируется Х0

оценка градиента

&. - иг

критерий F подстройки тактового колебания по правилу F - RM t(n-1)T {Ro(n-2)T - R0(nT)} + + fci (n-1)T {Qo{(n-2)T} - Qo(nT)} (4) Необходимые задержки осуществляются посредством блоков 11-13, 15, 17 и 18, каждый из которых задерживает сигнал на один такт. С целью упрощения подстройку тактового колебания можно осуществлять на основании критерия F, определяемого согласно (4) по любому из следующих правил:

F IRM fn-1)T Ro(n-2)T - R0(nT}}; F . QM (n-1)T (Qo(n-2)T - Qo(nT)}. (5) При этом структурная схема предлагаемого устройства также упрощается.

Формулы (4) и (5) можно еще упростить, используя вместо сигналов IM , IQ . Ro, do

только их знаки или комбинации знаков с соответствующими сигналами,

В формирователе 7 посредством цепи, состоящей из перемножителей 24 и 25, сумматоров 26 и 22, осуществляется фазовая и частотная подстройка тактовбго колебания.

Посредством перемножителей 24 и 25 осуществляется умножение соответствующих сигналов на постоянные коэффициентов Кт и «2, что необходимо для формирования требуемого соотношения постоянных регулирования в цепях фазовой и частотной автоподстройки.

Сигнал FJ () на выходе сумматора 22 в соответствии с фиг.2 определяется по правилу

F3(nT)F2(nT)+KiFi(nT);(6)

F2(nT) F2(n-1)T + KiK2Fi(nT). (7) При K2 О осуществляется только фазовая автоподстройка, однако, при этом необходимо использовать высокоточные и высокостабильные задающие генераторы, входящие в состав исполнительного блока 23. В исполнительном блоке 23 по сигналам Рз(пТ) осуществляется непосредственная подстройка тактового колебания согласно

}в выражению z(n+1) т(п) - fi , где в каче4Г

&

д

используется

стве оценки величины

значение Рз(пТ).

В случае приема сигналов данных, передаваемых по каналу связи с высокой интенсивностью импульсных помех, сигнал (критерий F(nT)) на выходе сумматора 21 может принимать большие значения, что

водит к увеличению дисперсии оценки

с

т.е. Ft(nT), а следовательно, снижает точность настройки тактового колебания и уменьшает помехоустойчивость приема сигналов данных. Для уменьшения этого эффекта используется ограничитель 1, на выходе которого величина Fi(nT) не превышает некоторой, наперед заданной величины.

Формула изобретения Адаптивный приемник сигналов данных, содержащий последовательно соединенные согласующий блок, вход которого является входом адаптивного приемника, блок линейной обработки сигналов, первый фазовращатель, решающий блок и декодер,

выход которого является выходом адаптивного приемника, вход и выход решающего блока соединены соответственно с первыми вторым входами формирователя сигналов 5 ошибки, выход которого соединен с пер- вымми входами второго фазовращателя и управляемого генератора, выход решающего блока соединен с вторым входом управляемого генератора, первый и второй

10 выходы которого соединены соответственно с вторыми входами первого и второго фазовращателей, выход которого соединен с вторым входом блока линейной обработки сигналов, входы первого и второго бло15 ков задержки соединены соответственно с первыми входами первого и второго вычи- тателей, выход первого блока задержки через третий блок задержки соединен с вторым входом первого вычитателя, а выход

20 второго блока задержки через четвертый блок задержки соединен с вторым входом второго вычитателя, выход первого вычитателя через первый перемножитель соединен с первым входом сумматора, а выход

25 второго вычитателя через второй перемножитель соединен с вторым входом сумматора, выход формирователя тактового колебания соединен с третьим входом блока линейной обработки сигналов и вторым вхо30 дом декодера, пятый и шестой блоки задержки, отличающийся тем, что, с целью повышения помехоустойчивости приема сигналов данных за счет повышения точности подстройки тактового колебания, вве35 ден ограничитель, причем входы пятого и шестого блоков заодержки соединены с выходом второго фазовращателя, выход пятого блока задержки, соединен с вторым входомпервого перемно40 жителя, выходшестого

блока задержки соединен с вторым входом второго перемножителя, выход б л о - ка линейной обработки сигналов соединен

45 с входами первого и второго блоков задержки, а выход сумматора через ограничитель соединен с входом формирователя тактового колебания.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования сигналов для передачи данных по первичному сетевому тракту | 1989 |

|

SU1739503A1 |

| АДАПТИВНЫЙ ПРИЕМНИК СИГНАЛОВ ДАННЫХ | 1991 |

|

RU2019048C1 |

| Устройство адаптивной коррекции межсимвольных искажений | 1987 |

|

SU1540010A1 |

| Устройство для преобразования сигналов | 1984 |

|

SU1234991A1 |

| Цифровой адаптивный приемник | 1988 |

|

SU1584114A1 |

| Устройство для корреляционного приема фазоманипулированных сигналов | 1984 |

|

SU1197137A1 |

| Устройство адаптивного приема дискретных сигналов с амплитудно-фазовой модуляцией | 1986 |

|

SU1309319A1 |

| Адаптивный приемник сигналов минимальной частотной манипуляции | 1989 |

|

SU1835611A1 |

| Устройство для приема фазоманипулированных сигналов | 1988 |

|

SU1598202A1 |

| Аналого-цифровой приемник сигналов данных | 1989 |

|

SU1635277A1 |

Изобретение относится к электросвязи, может использоваться для приема сигналов, сформированных многопозиционными методами комбинированной амплитудно-фазовой модуляции. Цель изобретения - повышение помехоустойчивости приема сигналов данных за счет повышения точности подстройки тактового колебания. Адаптивный приемник сигналов данных содержит согласующий блок 2, блок 3 линейной обработки сигналов, фазовращатели 4, 9, решающий блок 5, декодер 6, формирователь 7 тактового колебания, формирователь 8 сигнала ошибки, управляемый генератор 10, первый, второй, третий, четвертый блоки 11, 12, 13, 15 задержки, вычитатели 14, 16, пятый, шестой блоки 17, 18 задержки, перемножители 19, 20. В случае приема сигналов данных, передаваемых по каналу связи с высокой интенсивностью импульсных помех, сигнал на выходе сумматора 21 может принимать большие значения, что приводит к снижению точности настройки тактового колебания и уменьшает помехоустойчивость приема сигналов данных. Для уменьшения этого эффекта используется ограничитель 1. 3 ил.

22

Здп

тн

Л

Hj

29

31

30

32

Й2

Г

J5

с

36

FtW

ИЪло- w&

к

Jf

fel

27

D С

SI

25

| Устройство для преобразования сигналов | 1984 |

|

SU1234991A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-08-23—Публикация

1989-04-04—Подача